# Multiplexed Control at Scale for Electrode Arrays in Trapped-Ion Quantum Processors

Ryutaro Ohira\*, Shinichi Morisaka\*<sup>†</sup>, Ippei Nakamura<sup>‡</sup>, Atsushi Noguchi<sup>‡§¶</sup>, and Takefumi Miyoshi<sup>\*†||</sup>

\*QuEL, Inc., Daiwaunyu Building 3F, 2-9-2 Owadamachi, Hachioji, Tokyo, Japan

<sup>†</sup>Center for Quantum Information and Quantum Biology, Osaka University, 1-2 Machikaneyama, Toyonaka, Osaka, Japan

<sup>‡</sup>Komaba Institute for Science (KIS), The University of Tokyo, 3-8-1 Komaba, Meguro, 153-8902, Tokyo, Japan

§RIKEN Center for Quantum Computing (RQC), 2-1 Hirosawa, Wako, 351-0198, Saitama, Japan

¶Inamori Research Institute for Science (InaRIS), 620 Suiginya, Kyoto, 600-8411, Kyoto, Japan

e-trees. Japan, Inc., Daiwaunyu Building 2F, 2-9-2 Owadamachi, Hachioji, Tokyo, Japan

ohira@quel-inc.com, morisaka@quel-inc.com, ippei-nakamura@g.ecc.u-tokyo.ac.jp,

u-atsushi@g.ecc.u-tokyo.ac.jp, miyoshi@quel-inc.com

Abstract—The scaling up of trapped-ion quantum processors based on the quantum charge-coupled device (QCCD) architecture is difficult owing to the extensive electronics and high-density wiring required to control numerous trap electrodes. In conventional OCCD architectures, each trap electrode is controlled via a dedicated digital-to-analog converter (DAC). The conventional approach places an overwhelming demand on electronic resources and wiring complexity. This is because the number of trap electrodes typically exceeds the number of trapped-ion qubits. This study proposes a method that leverages a high-speed DAC to generate time-division multiplexed signals to control a large-scale QCCD trapped-ion quantum processor. The proposed method replaces conventional DACs with a single high-speed DAC that generates the complete voltage waveforms required to control the trap electrodes, thereby significantly reducing the wiring complexity and overall resource requirements. Based on realistic parameters and commercially available electronics, our analysis demonstrates that a QCCD trapped-ion quantum computer with 10,000 trap electrodes can be controlled using only 13 field-programmable gate arrays and 104 high-speed DACs. This is in stark contrast to the 10,000 dedicated DACs required by conventional control methods. Consequently, employing this approach, we developed a proof-of-concept electronic system and evaluated its analog output performance.

Index Terms—quantum computing, trapped-ion qubits, fieldprogrammable gate array, control system

# I. INTRODUCTION

Recent developments that incorporate tens of trapped-ion qubits [1]–[3] have demonstrated that the quantum chargecoupled device (QCCD) architecture offers a route for scalable trapped-ion quantum computers [4]–[7]. In the QCCD architecture, trapped-ion qubits are physically shuttled between distinct functional areas, such as state preparation, measurement, and gate operations, to perform quantum computations.

In a typical trapped-ion QCCD system, ion shuttling is achieved by dynamically controlling the trap potentials via time-varying voltages applied to the trap electrodes. Conventionally, each electrode is controlled by a dedicated digitalto-analog converter (DAC) operating at voltage update rates ranging from several hundred kHz to a few MHz [8]–[12].

However, this approach poses significant challenges in terms of scaling up the system. In a typical QCCD architecture, a single trapped-ion qubit requires multiple trap electrodes, with current estimates indicating the need for approximately 10 electrodes per qubit [1], [10], [13]. This one-to-one correspondence between the DACs and trap electrodes increases wiring complexity that scales approximately tenfold with the number of qubits. These challenges are further exacerbated by the need to interface vacuum or cryogenic systems with room-temperature control electronics. Several strategies have been proposed to address these issues, including the use of in-vacuum [14] or chip-integrated [15] electronics, switching networks [13], electrode co-wiring techniques [2], and novel transport operation methods that reduce the number of required analog signals [16].

This study proposes an alternative strategy to decrease both the number of DACs and the wiring complexity in large-scale QCCD trapped-ion quantum processors. The proposed method employs a high-speed DAC that has been configured to generate time-division multiplexed signals capable of replicating the outputs of multiple conventional DACs. Subsequently, these signals are distributed across individual channels to generate the voltage waveforms required to control the trap electrodes.

Our analysis demonstrates that a QCCD quantum computer with 10,000 trap electrodes can be controlled with only 13 field-programmable gate arrays (FPGAs) and 104 highspeed DACs, based on realistic parameters and commercially available components. This significantly reduces hardware demands compared to 10,000 dedicated DACs required by conventional control methods. Furthermore, we developed a proof-of-concept (PoC) electronic system and evaluated the quality of its analog output signals.

# II. GENERAL CONCEPT

This section elucidates the proposed control scheme and describes a detailed implementation of the proposed approach.

This work has been submitted to the IEEE for possible publication. Copyright may be transferred without notice, after which this version may no longer be accessible.

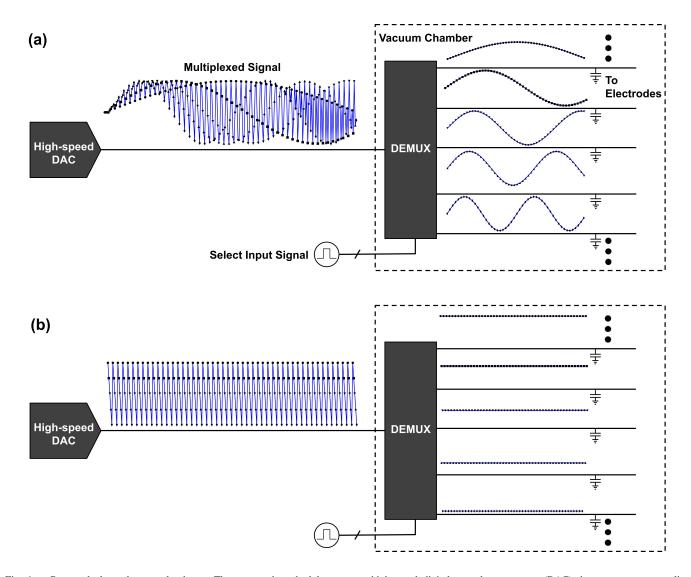

Fig. 1. Proposed electrode control scheme. The proposed method leverages a high-speed digital-to-analog converter (DAC) that operates at sampling rates considering exceeding those of conventional DACs typically used for ion shuttling operations. The high-speed DAC facilitates time-division multiplexing across multiple channels by generating complete voltage waveforms, thereby eliminating the requirement of a dedicated DAC for each electrode. The generated waveform is then routed through a demultiplexing network (denoted as DEMUX), which distributes the signal to each output channel, where a capacitor holds the voltage until the next update cycle. (a) Time-multiplexed signal composed of sinusoidal waves at different frequencies. This waveform demonstrates that our system can generate the time-dependent signals required for the dynamic control of the trapped-ion qubits. (b) Static voltage signal suitable for ion trapping.

Notably this study develops a control method for trapping electrodes within a large-scale QCCD architecture. The precision of this approach in terms of controlling the quantum states of trapped-ion qubits will be examined in future research. In addition, shuttling ions on a timescale shorter than their motional period requires the use of DACs with voltage update rates on the order of tens of MHz [17]–[22]. However, this study focuses on adiabatic transport and does not consider such high-speed ion shuttling operations.

# A. Proposed System Architecture

Figures 1(a) and (b) present an overview of the proposed method. The proposed method is based on a high-speed DAC that operates at a sampling rate significantly higher than several mega samples per second (Msps) typically used for ion shuttling. This high-speed DAC generates the complete voltage waveforms required to control all the responsible electrodes, enabling time-division multiplexing across multiple channels. The output of the DAC is routed through a demultiplexing network, which distributes the generated waveforms to individual electrode channels. Each channel includes a capacitor that is charged to maintain the desired voltage.

Figure 1(a) shows a time-multiplexed signal composed of sinusoidal waves at different frequencies. Figure 1(a) serves as an illustrative example, demonstrating that our scheme can encode arbitrary time-dependent signals required for the dynamic control of trapped-ion qubits. In contrast, when ions are held statically in a trap, a signal like that depicted in

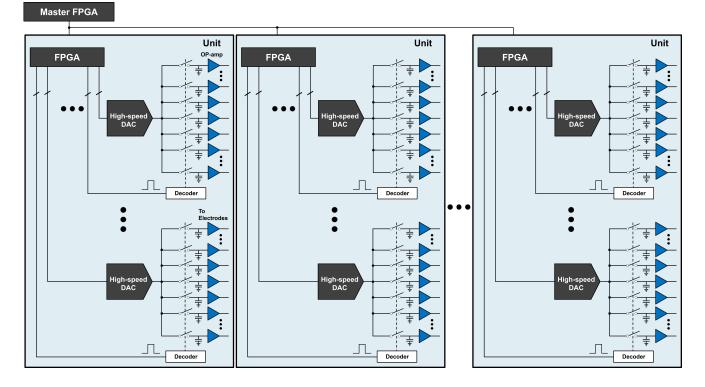

Fig. 2. Practical implementation of the proposed scheme. High-speed switches and a digital decoder (denoted as Decoder) sequentially charge the capacitors positioned before each electrode. Upon charging, the operational amplifier (denoted as OP-amp) boosts the voltage to the desired level. The limited number of field-programmable gate arrays (FPGA) input and output (I/O) ports restricts the number of DACs that can be controlled and the available digital signals for demultiplexing. Thus, each control unit is designed as a modular element, and synchronization signals are distributed among them to enable the modules to operate together as a unified control system. In our implementation, a master FPGA coordinates all the control units, thereby ensuring synchronized operation under a common clock signal.

Fig. 1(b) is generated. Note that in a typical trapped-ion setup, the DAC output must be low-pass filtered to suppress the electrical noise that could excite the ions' motional state. For simplicity, the low-pass filters are omitted from the depiction in this study.

In principle, the proposed control method can also be applied to static ion trapping. However, as described later, the voltage drop and recharging cycle may induce the motional excitation of the ions or affect the stability of their motional frequencies during gate operations, thereby degrading the quantum gate fidelity [13]. These issues warrant further theoretical and experimental investigation.

Figure 2 illustrates a practical implementation of the proposed scheme. An FPGA generates a time-multiplexed signal and then sends it to a high-speed DAC. The time-multiplexed signal is demultiplexed employing high-speed switches and a digital decoder (denoted as Decoder in Fig. 2). Each highspeed switch is activated at the appropriate moment to charge the associated capacitor. Upon the charging of the capacitor, the switch turns off, and the next switch is turned on to charge the adjacent capacitor. Subsequently, the voltage stored in each capacitor is amplified via an operational amplifier (OP-amp) to achieve the desired level.

This operational principle is partially inspired by the voltage distribution scheme for static ion control, as proposed by Malinowski et al. [13]. However, the proposed approach is distinctly different from that of Malinowski et al. [13]. In their scheme, the ion qubits are dynamically controlled through the combination of DAC outputs that operate at update rates of a few MHz with an integrated switch network. Meanwhile, the quasi-static control employs a sample-and-hold circuit and a demultiplexer to control the electrodes using a limited number of DACs. In contrast, the proposed approach consolidates both dynamic and quasi-static control using a small number of highspeed DACs to directly generate all necessary voltage waveforms, which are then demultiplexed to individually address the electrodes.

Both the number of DACs that can be controlled and the number of digital signals that can be sent to the digital decoder are restricted due to the limited number of input and output (I/O) ports on an FPGA. To address this issue, each control unit is designed as a modular element, as illustrated in Fig. 2, and synchronization signals are distributed among them, enabling the units to collectively function as a single control system. Synchronization between individual control units can be achieved using methods such as those described in Refs. [23]–[25]. For example, all control units can be connected to a master FPGA via 10 GbE and controlled using a shared common clock [23]–[25].

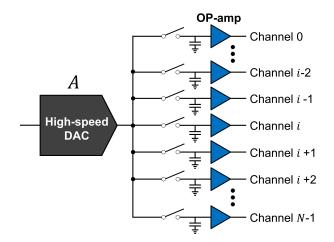

Fig. 3. Multiplexing factor is the number of electrodes that are controlled using a single high-speed DAC. For example, if a high-speed DAC operating at A distributes voltage to N channels, the multiplexing factor is N.

# B. Estimation of Multiplexing Factor of Proposed Method

Now, we estimate the achievable multiplexing factor and overall scalability of our the proposed method. Here, the multiplexing factor is the number of electrodes that can be controlled using a single high-speed DAC. Figure 3 shows a schematic of a high-speed DAC operating at rate A distributing voltage to N channels (Channel 0 to N-1). In this configuration, the multiplexing factor is defined as N.

Two primary factors limit this multiplexing factor. (1) The time required to fully charge the capacitor. (2) The voltage drop owing to the capacitor discharge. Here, we examine the impact of each factor on the achievable multiplexing factor.

1) Capacitor charging time : First, we describe the effect of the time required to charge the capacitor on the achievable multiplexing factor. Consider a situation wherein a high-speed DAC operating at A distributes voltage to N channels (Channel 0 to N-1), as illustrated in Fig. 3. At this operating rate, the time allocated to each channel is

$$\Delta t = 1/A.$$

Within this interval, the capacitor associated with each channel must be completely charged.

- Two key parameters affect this process:

- The settling time of the high-speed DAC

- The charging time of the capacitor.

The settling time is the duration between the setting of an input code and the output stabilization at its final value. If charging begins prior to the settling of the output of the high-speed DAC, the capacitor may reach an incorrect voltage. Therefore, the high-speed DAC output must first be allowed to stabilize before turning on the switch to charge the capacitor. We denote the high-speed DAC settling time as  $\Delta t_s$  and the capacitor charging time as  $\Delta t_c$ . Consequently, the sum  $\Delta t_s + \Delta t_c$  must be less than the available time per channel,  $\Delta t$ .

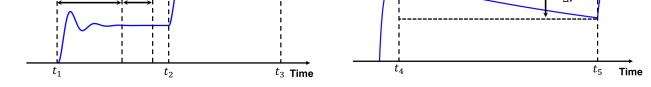

Figure 4(a) illustrates the effects. The vertical and horizontal axes represent the voltage delivered to the capacitors of each

channel and time (marked at specific instants  $t_1$ ,  $t_2$ , and  $t_3$ ), respectively. At time  $t_1$ , the system switches from Channel i-1 to *i*. This causes the high-speed DAC output to transition from the target voltage for Channel i-1 to that of Channel *i*. The high-speed DAC output requires a settling time  $\Delta t_s$  to stabilize at the new target voltage, followed by an additional time  $\Delta t_c$  for the capacitor to fully charge. If

$$\Delta t_s + \Delta t_c < \Delta t,$$

the capacitor can achieve the desired voltage.

This combined time,  $\Delta t_s + \Delta t_c$ , effectively limits the maximum sampling rate of the high-speed DAC that can be used with this control scheme. A high-speed DAC must operate at a rate no greater than

$$\frac{1}{\Delta t_s + \Delta t_c}$$

to ensure proper charging of the capacitor. Notably, the finite rise and fall times of the switches also affect the capacitor charging time  $\Delta t_c$ . In practice,  $\Delta t_c$  is determined by the sum of the switching times (both turn-on and turn-off) of the switch and the on duration of the switch.

2) Capacitor discharge-induced voltage drop : We examine the impact of the voltage drop due to the capacitor discharge between successive charging events. The voltage evolution of the capacitor in Channel i over time is schematically shown in Fig. 4(b). At time  $t_4$ , the capacitor in Channel i is fully charged. Over time, the voltage decreases until the next charging event occurs at time  $t_5$ . The interval between the completion of one charging cycle and the subsequent recharge is given by

$$\Delta T = N\Delta t = N/A.$$

To minimize the voltage variations from the capacitor discharge, the discharge time constant should be designed to be as long as possible. One straightforward approach is to use a capacitor with a larger capacitance. However, increasing the capacitance also prolongs the charging time. Furthermore, if the multiplexing factor N is too high, the charging cycle becomes longer, leading to a more pronounced voltage drop.

After identifying the factors limiting the multiplexing factor, we then estimate it by defining the target signal quality. In this study, we consider multiplexing a DAC with a 0.5 MHz voltage update rate. To establish concrete circuit parameters, we assume the following:

- A high-speed DAC with a settling time of  $\Delta t_s = 10$  ns.

- High-speed switches with a rise/fall time of  $\tau_{sw} = 1$  ns and an on-resistance of  $R_{sw} = 10 \ \Omega$ .

- A C = 150 pF capacitor for each channel.

- An OP-amp with suitable gain and an input impedance of R<sub>amp</sub> = 10 MΩ.

First, the capacitor charging time is determined based on the RC time constant as  $\tau_c = CR_{\rm sw} = 1.5$  ns. Typically, approximately 5 times this RC constant is required by the capacitor to charge nearly to its final value. Thus, the charging time is approximately  $5\tau_c = 7.5$  ns. Including the 1-ns rise

Fig. 4. (a) The vertical and horizontal axes show the voltage delivered to each channel's capacitor and time (marked at  $t_1$ ,  $t_2$ , and  $t_3$ ), respectively. At  $t_1$ , the system switches from Channel i-1 to Channel i. This causes the DAC output to transition from the target voltage of Channel i-1 to that of Channel i. The high-speed DAC output necessitates a settling time  $\Delta t_s$  for stabilization at the new target voltage, followed by a capacitor charging time  $\Delta t_c$ . Assuming the sum of the settling time  $\Delta t_s$  and capacitor charging time  $\Delta t_c$  to be less than the total time available per channel  $\Delta t$ , the capacitor reaches the desired voltage. (b) Voltage profile of the capacitor in Channel i over time. At  $t_4$ , the capacitor in Channel i reaches full charge; however, its voltage begins to decay until the next charging event at  $t_5$ . The duration between these charging events is  $\Delta T = N\Delta t = N/A$ .

and 1-ns fall times of the switch, we set the effective capacitor charging time to  $\Delta t_c = 1 + 7.5 + 1 = 9.5$  ns. Thus, the total time required to charge the capacitor for each channel is  $\Delta t_s + \Delta t_c = 10 + 9.5 = 19.5$  ns. This corresponds to the maximum sampling rate for high-speed DAC of approximately  $1/(\Delta t_s + \Delta t_c) \approx 51.3$  Msps. Assuming the high-speed DAC operates at a sampling rate of A = 50 Msps and targeting a voltage update rate of 0.5 MHz for individual output channels, the multiplexing factor is obtained as N = 50/0.5 = 100.

Meanwhile, the time interval between successive charging events for a particular channel is  $\Delta T = N/A = 2 \ \mu s$ . The discharge time constant of the capacitor is  $\tau_d = CR_{\text{amp}} =$ 1.5 ms. Using the exponential decay model  $V_0 e^{-t/\tau_d}$ , after 2  $\mu s$  the voltage decreases by approximately 0.13% relative to the initial voltage  $V_0$ .

Several strategies can be employed to further enhance the multiplexing factor. The above estimates are based on the performance of off-the-shelf electronics. If higher-performance electrical components are used, further improvements in multiplexing capability can be achieved. For example, from the viewpoint of high-speed DACs, using a DAC with a shorter settling time would enable faster operation. In addition, from the viewpoint of capacitor charging, replacing the switch with a lower on-resistance would allow for even faster charging.

## C. Scalability

Finally, we examine the scalability of the proposed control method, considering the limited number of FPGA I/O ports. As a target scenario, we consider controlling 10,000 electrodes (corresponding to 1,000 qubits, assuming 10 electrodes per qubit). Suppose we use a typical FPGA with 200 I/O ports; however, FPGAs with more than 200 I/O ports are commonly available for IO-intensive applications. These I/O ports must support both the interface between the FPGA and the DAC and the digital signals sent to the digital decoder, where the number of decoder signals scales as  $\lceil \log_2 N \rceil$  for N channels.

We consider the usage of a 16-bit parallel data transfer interface for the high-speed DAC, which requires 16 data lines. In addition, one I/O port is required for the FPGAprovided clock signal, resulting in 17 I/O ports for the FPGA-DAC interface. With a multiplexing factor of 100 (i.e., one high-speed DAC controls 100 electrodes), the digital decoder requires approximately  $\lceil \log_2 100 \rceil \approx 7$  FPGA I/O ports. Thus, each high-speed DAC and decoder module uses 24 FPGA I/O ports.

Given an FPGA with 200 I/O ports, one FPGA can support approximately 8 modules. Since each module controls 100 electrodes, one FPGA can manage approximately  $8 \times 100 =$ 800 electrodes. Therefore, controlling 10,000 electrodes would require  $\lceil 10,000/800 \rceil \approx 13$  FPGAs. The total number of highspeed DACs needed is  $13 \times 8 = 104$ . Note that synchronization signals between control units are necessary, as shown in Fig. 2, these are provided via the high-speed transceivers of the FPGA and do not consume dedicated FPGA I/O ports.

#### **III.** System Characterization

Based on the concept proposed in Sec. II, we developed a proof-of-concept (PoC) system. Herein, we elucidate the PoC system and present the results of our evaluation of its analog output signals.

# A. Development of PoC System

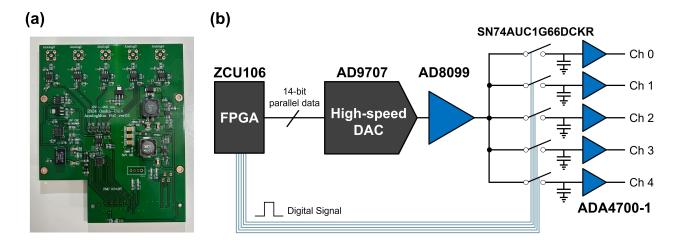

Figure 5(a) illustrates the developed system, which is capable of multiplexing five output channels. The system employs a 14-bit high-speed DAC (AD9707), whose output signal is amplified using an OP-amp (AD8099) before being distributed to each channel. Each channel is equipped with a high-speed switch (SN74AUC1G66DCKR), 30-pF charging capacitor, and subsequent OP-amp (ADA4700-1). This facilitates the system in outputting signals ranging from –50 to +50 V.

Notably, the developed board does not include a dedicated digital decoder. In contrast, demultiplexing is implemented through the direct routing of digital signals to each switch.

Fig. 5. (a) Developed proof-of-concept (PoC) System. The FPGA used to control the high-speed DAC is not shown herein. (b) Developed system used to multiplex five output signals. The design uses a 14-bit high-speed DAC (AD9707) with amplified output (AD8099) distributed to each channel. Each channel includes a high-speed switch (SN74AUC1G66DCKR), a 30-pF capacitor, and an OP-amp (ADA4700-1) that produces signals from -50 to +50 V. Note that for this PoC, the board does not include a dedicated digital decoder. Here, demultiplexing is achieved by directly routing digital signals to each switch. The high-speed DAC is controlled using the AMD ZCU106 Evaluation Board employing a 14-bit parallel interface. Further, the FPGA also generates the digital control signals for the switches.

Although this approach requires N digital signals for a multiplexing factor of N, it is sufficient for this PoC.

The high-speed DAC on the board was controlled using an AMD ZCU106 Evaluation Board [26]. The interface between the FPGA and DAC was implemented as a 14-bit parallel data interface comprising 14 data lines and 2 differential clock lines, all generated via the FPGA. The high-speed DAC operated at 30 Msps, resulting in a voltage update rate of 6 Msps for each output channel.

# B. Operational Tests

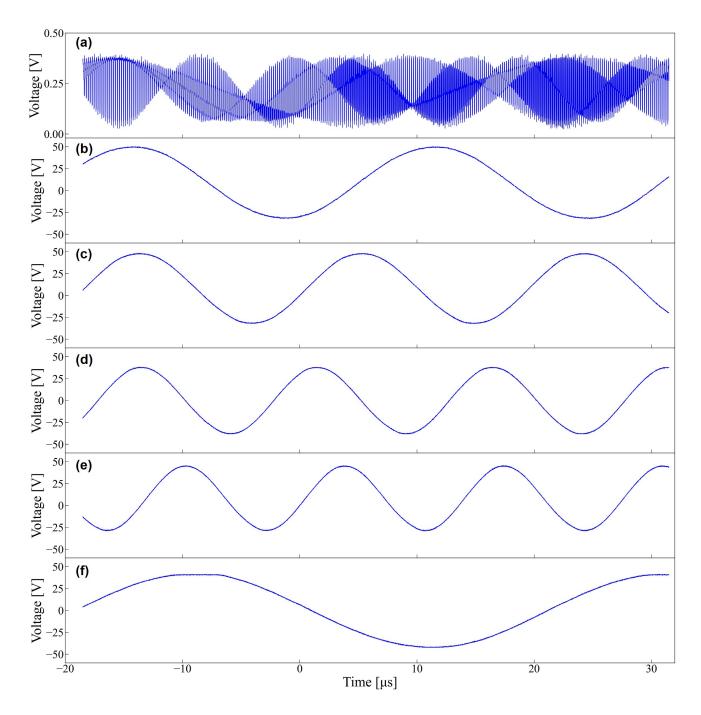

We conducted operational tests using the developed system to assess its signal output performance. As an example, we generated a multiplexed signal composed of five sinusoidal waves. Figure 6 shows both the time-multiplexed signal and the corresponding outputs from each channel: Fig. 6(a) shows the multiplexed signal, while Figs. 6(b) through 6(f) display the sinusoidal outputs from each channel.

The multiplexed signal shown in Fig. 6(a) was acquired by connecting a coaxial cable with a 270  $\Omega$  resistor to the output of AD8099 and measuring it with an oscilloscope set to a 50  $\Omega$  input impedance. Consequently, the amplitude is reduced by a voltage divider factor of  $50/(270+50) \approx 0.156$ relative to the original output voltage. Note that the phases of the multiplexed signal and individual channel outputs are not aligned because each signal is measured independently. The results demonstrate that individual sinusoidal waveforms can be extracted successfully from the multiplexed signal.

# C. Evaluation of the Settling Time of the High-speed DAC and the Capacitor Discharge-induced Voltage Drop

We measured the settling time of the high-speed DAC by evaluating the rise and fall times when varying output voltages between its minimum and maximum code values. The measured settling time was approximately 20 ns compared with the 11 ns specified in the AD9707 datasheet [27]. This discrepancy may be attributed to the limited slew rate of the subsequent OP-amp, which extended the overall settling time.

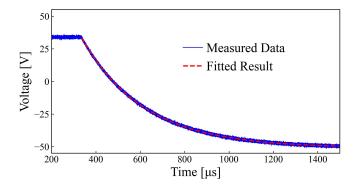

The capacitor discharge behavior was evaluated. After charging the capacitor in Channel 0, the switch was released and its discharge was observed. The observed discharge of the capacitor is shown in Fig. 7. We obtained a discharge time constant of 282.6  $\mu$ s by fitting the data to an exponential decay model.

In our experiment, the high-speed DAC operated at 30 Msps, thereby allocating approximately 33.3 ns to each channel. Because we are multiplexing five output channels, the recharge cycle occurs approximately every 166.6 ns. Within this interval, the voltage drop was approximately 0.06% of the initial voltage.

To further extend the discharge time constant, one could increase the capacitance. However, this would result in a longer charging time, resulting in a trade-off that must be carefully balanced. Alternatively, the voltage drop can be controlled using a buffer or an OP-amp with a higher input impedance in the final stage.

# D. Evaluation of Crosstalk Between Channels

Finally, we evaluated the interchannel crosstalk. In this experiment, a sinusoidal wave was output from Channel 4, and the signals from the other channels were measured. To mitigate the high-frequency noise likely originating from the switching process, a fifth-order Butterworth low-pass filter with a cutoff frequency of 70 kHz was applied to the outputs of each channel before analysis. The crosstalk was quantified by comparing the amplitude of each channel with that of Channel 4.

Fig. 6. (a) Time-multiplexed signal comprising five sinusoidal waves, and (b-f) the corresponding output signals from Channels 0-4.

Table I summarizes the crosstalk measurements obtained in these experiments. In all channels, crosstalk was below 60 dB. The crosstalk between channels 0 and 4 was slightly higher than that observed in the other channels. This could be due to the circuit configuration, in which Channel 0 is the first channel to be charged immediately after Channel 4, causing Channel 0's output to be influenced by the DAC code value of Channel 4.

TABLE I

Measured Crosstalk between Channel 4 and Channels 0–3

| Channel   | Crosstalk [dB] |

|-----------|----------------|

| Channel 0 | -62.8          |

| Channel 1 | -67.6          |

| Channel 2 | -67.7          |

| Channel 3 | -67.2          |

Fig. 7. Measured capacitor discharge behavior in Channel 0. The red dashed curve indicates the exponential decay with a discharge constant of  $282.6 \ \mu s$ .

#### IV. CONCLUSION AND FUTURE WORK

This study proposed a scalable control scheme for largescale QCCD trapped-ion quantum processors by leveraging a high-speed DAC. By generating complete voltage waveforms with a single high-speed DAC and sharing them among multiple electrodes, the proposed method significantly reduced the wiring complexity and overall resource requirements compared to conventional methods, which require one dedicated DAC per electrode. Based on realistic parameters and commercially available components, our analysis demonstrated that a QCCD system with 10,000 trap electrodes was controllable using only 13 FPGAs and 104 high-speed DACs. In addition, we developed a PoC electronic system based on this approach and evaluated its analog output performance. Consequently, we confirmed the ability of the system to effectively generate the voltage waveforms required for trap electrode control.

In future research, we will focus on the following objectives. We will integrate our control architecture with roomtemperature trapped-ion setups. Further, we will optimize the digital and analog subsystems of the control architecture to improve resource efficiency and overall system robustness. Although this study primarily addresses ion shuttling and trapping, in principle, our control method is extendable to other operations required for QCCD architectures, such as split/combine [1], [2], [10], [28]–[31] and physical swap [1], [2], [10], [32]–[34]. These operations can be implemented by appropriately scheduling the electrode control sequences. Finally, considering the increased interest in the operation of trapped-ion quantum computers under cryogenic conditions [35]–[39], we aim to investigate the feasibility of the proposed scheme at low temperatures.

#### ACKNOWLEDGMENT

This work was supported by MEXT Q-LEAP (Grant Numbers JPMXS0120319794, JPMXS0118068682), JST (Grant Number JPMJPF2014), and JST Moonshot R&D (Grant Numbers JPMJMS226A, JPMJMS2063).

### REFERENCES

- J. M. Pino, J. M. Dreiling, C. Figgatt, J. P. Gaebler, S. A. Moses, M. Allman, C. Baldwin, M. Foss-Feig, D. Hayes, K. Mayer *et al.*, "Demonstration of the trapped-ion quantum ccd computer architecture," *Nature*, vol. 592, no. 7853, pp. 209–213, 2021.

- [2] S. A. Moses, C. H. Baldwin, M. S. Allman, R. Ancona, L. Ascarrunz, C. Barnes, J. Bartolotta, B. Bjork, P. Blanchard, M. Bohn *et al.*, "A race-track trapped-ion quantum processor," *Physical Review X*, vol. 13, no. 4, p. 041052, 2023.

- [3] M. DeCross, R. Haghshenas, M. Liu, E. Rinaldi, J. Gray, Y. Alexeev, C. H. Baldwin, J. P. Bartolotta, M. Bohn, E. Chertkov *et al.*, "The computational power of random quantum circuits in arbitrary geometries," *arXiv preprint arXiv:2406.02501*, 2024.

- [4] D. J. Wineland, C. Monroe, W. M. Itano, D. Leibfried, B. E. King, and D. M. Meekhof, "Experimental issues in coherent quantum-state manipulation of trapped atomic ions," *Journal of research of the National Institute of Standards and Technology*, vol. 103, no. 3, p. 259, 1998.

- [5] D. Kielpinski, C. Monroe, and D. J. Wineland, "Architecture for a largescale ion-trap quantum computer," *Nature*, vol. 417, no. 6890, pp. 709– 711, 2002.

- [6] B. Lekitsch, S. Weidt, A. G. Fowler, K. Mølmer, S. J. Devitt, C. Wunderlich, and W. K. Hensinger, "Blueprint for a microwave trapped ion quantum computer," *Science Advances*, vol. 3, no. 2, p. e1601540, 2017.

- [7] C. Löschnauer, J. M. Toba, A. Hughes, S. King, M. Weber, R. Srinivas, R. Matt, R. Nourshargh, D. Allcock, C. Ballance *et al.*, "Scalable, high-fidelity all-electronic control of trapped-ion qubits," *arXiv preprint arXiv*:2407.07694, 2024.

- [8] R. B. Blakestad, "Transport of trapped-ion qubits within a scalable quantum processor," Ph.D. dissertation, University of Colorado at Boulder, 2010.

- [9] R. Blakestad, C. Ospelkaus, A. VanDevender, J. Wesenberg, M. Biercuk, D. Leibfried, and D. J. Wineland, "Near-ground-state transport of trapped-ion qubits through a multidimensional array," *Physical Review A—Atomic, Molecular, and Optical Physics*, vol. 84, no. 3, p. 032314, 2011.

- [10] V. Kaushal, B. Lekitsch, A. Stahl, J. Hilder, D. Pijn, C. Schmiegelow, A. Bermudez, M. Müller, F. Schmidt-Kaler, and U. Poschinger, "Shuttling-based trapped-ion quantum information processing," AVS Quantum Science, vol. 2, no. 1, 2020.

- [11] M. Akhtar, F. Bonus, F. Lebrun-Gallagher, N. Johnson, M. Siegele-Brown, S. Hong, S. Hile, S. Kulmiya, S. Weidt, and W. Hensinger, "A high-fidelity quantum matter-link between ion-trap microchip modules," *Nature communications*, vol. 14, no. 1, p. 531, 2023.

- [12] C. Mordini, A. Ricci Vasquez, Y. Motohashi, M. Müller, M. Malinowski, C. Zhang, K. K. Mehta, D. Kienzler, and J. P. Home, "Multizone trapped-ion qubit control in an integrated photonics qccd device," *Physical Review X*, vol. 15, no. 1, p. 011040, 2025.

- [13] M. Malinowski, D. Allcock, and C. Ballance, "How to wire a 1000qubit trapped-ion quantum computer," *PRX Quantum*, vol. 4, no. 4, p. 040313, 2023.

- [14] N. D. Guise, S. D. Fallek, H. Hayden, C. Pai, C. Volin, K. Brown, J. Merrill, A. W. Harter, J. M. Amini, L. M. Lust *et al.*, "In-vacuum active electronics for microfabricated ion traps," *Review of Scientific Instruments*, vol. 85, no. 6, 2014.

- [15] J. Stuart, R. Panock, C. Bruzewicz, J. Sedlacek, R. McConnell, I. Chuang, J. Sage, and J. Chiaverini, "Chip-integrated voltage sources for control of trapped ions," *Physical Review Applied*, vol. 11, no. 2, p. 024010, 2019.

- [16] R. D. Delaney, L. R. Sletten, M. J. Cich, B. Estey, M. I. Fabrikant, D. Hayes, I. M. Hoffman, J. Hostetter, C. Langer, S. A. Moses *et al.*, "Scalable multispecies ion transport in a grid-based surface-electrode trap," *Physical Review X*, vol. 14, no. 4, p. 041028, 2024.

- [17] A. Walther, F. Ziesel, T. Ruster, S. T. Dawkins, K. Ott, M. Hettrich, K. Singer, F. Schmidt-Kaler, and U. Poschinger, "Controlling fast transport of cold trapped ions," *Physical review letters*, vol. 109, no. 8, p. 080501, 2012.

- [18] R. Bowler, J. Gaebler, Y. Lin, T. R. Tan, D. Hanneke, J. D. Jost, J. Home, D. Leibfried, and D. J. Wineland, "Coherent diabatic ion transport and separation in a multizone trap array," *Physical review letters*, vol. 109, no. 8, p. 080502, 2012.

- [19] R. Bowler, U. Warring, J. W. Britton, B. Sawyer, and J. Amini, "Arbitrary waveform generator for quantum information processing with trapped ions," *Review of Scientific Instruments*, vol. 84, no. 3, 2013.

- [20] M. T. Baig, M. Johanning, A. Wiese, S. Heidbrink, M. Ziolkowski, and C. Wunderlich, "A scalable, fast, and multichannel arbitrary waveform generator," *Review of Scientific Instruments*, vol. 84, no. 12, 2013.

- [21] J. D. Sterk, H. Coakley, J. Goldberg, V. Hietala, J. Lechtenberg, H. McGuinness, D. McMurtrey, L. P. Parazzoli, J. Van Der Wall, and D. Stick, "Closed-loop optimization of fast trapped-ion shuttling with sub-quanta excitation," *npj Quantum Information*, vol. 8, no. 1, p. 68, 2022.

- [22] C. R. Clark, C. D. Herold, J. T. Merrill, H. N. Tinkey, W. Rellergert, R. Clark, R. Brown, W. D. Robertson, C. Volin, K. Maller *et al.*, "Characterization of fast ion transport via position-dependent optical deshelving," *Physical Review A*, vol. 107, no. 4, p. 043119, 2023.

- [23] T. Miyoshi, K. Koike, S. Morisaka, H. Shiomi, K. Ogawa, Y. Tabuchi, and M. Negoro, "Fpl demo: A flexible and scalable quantum-classical interface based on fpgas," in 2022 32nd International Conference on Field-Programmable Logic and Applications (FPL). IEEE, 2022, pp. 473–473.

- [24] T. Miyoshi, K. Koike, S. Morisaka, T. Sumida, M. Negoro, A. Noguchi, and R. Ohira, "A microwave-based qccd trapped-ion quantum computer with scalable control system," in 2024 IEEE International Conference on Quantum Computing and Engineering (QCE), vol. 2. IEEE, 2024, pp. 470–471.

- [25] T. Miyoshi, K. Koike, S. Morisaka, Y. Sugita, T. Sumida, Y. Tabuchi, M. Negoro, H. Shiomi, I. Nakamura, T. Tomita *et al.*, "Toward scalable heterogeneous controller system for various quantum computer by using multiple fpgas," in 2025 IEEE International Conference on Consumer Electronics (ICCE). IEEE, 2025, pp. 1–5.

- [26] AMD, "AMD Zynq UltraScale+ MPSoC ZCU106 Evaluation Kit," https://www.amd.com/en/products/adaptive-socs-and-fpgas/ evaluation-boards/zcu106.html, accessed: 2025-03-07.

- [27] Analog Devices, "AD9707 Data Sheet (Rev. G)," https: //www.analog.com/media/en/technical-documentation/data-sheets/ ad9704\_9705\_9706\_9707.pdf, accessed: 2025-03-07.

- [28] J. Home, "Electrode configurations for fast separation of trapped ions," arXiv preprint quant-ph/0411102, 2004.

- [29] T. Ruster, C. Warschburger, H. Kaufmann, C. T. Schmiegelow, A. Walther, M. Hettrich, A. Pfister, V. Kaushal, F. Schmidt-Kaler, and U. G. Poschinger, "Experimental realization of fast ion separation in segmented paul traps," *Physical Review A*, vol. 90, no. 3, p. 033410, 2014.

- [30] H. Kaufmann, T. Ruster, C. Schmiegelow, F. Schmidt-Kaler, and U. Poschinger, "Dynamics and control of fast ion crystal splitting in segmented paul traps," *New Journal of Physics*, vol. 16, no. 7, p. 073012, 2014.

- [31] S. D. Fallek, V. S. Sandhu, R. A. McGill, J. M. Gray, H. N. Tinkey, C. R. Clark, and K. R. Brown, "Rapid exchange cooling with trapped ions," *Nature Communications*, vol. 15, no. 1, p. 1089, 2024.

- [32] F. Splatt, M. Harlander, M. Brownnutt, F. Zähringer, R. Blatt, and W. Hänsel, "Deterministic reordering of 40ca+ ions in a linear segmented paul trap," *New journal of Physics*, vol. 11, no. 10, p. 103008, 2009.

- [33] H. Kaufmann, T. Ruster, C. T. Schmiegelow, M. A. Luda, V. Kaushal, J. Schulz, D. von Lindenfels, F. Schmidt-Kaler, and U. G. Poschinger, "Fast ion swapping for quantum-information processing," *Physical Review A*, vol. 95, no. 5, p. 052319, 2017.

- [34] M. W. van Mourik, E. A. Martinez, L. Gerster, P. Hrmo, T. Monz, P. Schindler, and R. Blatt, "Coherent rotations of qubits within a surface ion-trap quantum computer," *Physical Review A*, vol. 102, no. 2, p. 022611, 2020.

- [35] J. Labaziewicz, Y. Ge, P. Antohi, D. Leibrandt, K. R. Brown, and I. L. Chuang, "Suppression of heating rates in cryogenic surface-electrode ion traps," *Physical review letters*, vol. 100, no. 1, p. 013001, 2008.

- [36] J. Chiaverini and J. Sage, "Insensitivity of the rate of ion motional heating to trap-electrode material over a large temperature range," *Physical Review A*, vol. 89, no. 1, p. 012318, 2014.

- [37] M. Brandl, M. Van Mourik, L. Postler, A. Nolf, K. Lakhmanskiy, R. Paiva, S. Möller, N. Daniilidis, H. Häffner, V. Kaushal *et al.*, "Cryogenic setup for trapped ion quantum computing," *Review of Scientific Instruments*, vol. 87, no. 11, 2016.

- [38] G. Pagano, P. Hess, H. Kaplan, W. Tan, P. Richerme, P. Becker, A. Kyprianidis, J. Zhang, E. Birckelbaw, M. Hernandez *et al.*, "Cryogenic trapped-ion system for large scale quantum simulation," *Quantum Science and Technology*, vol. 4, no. 1, p. 014004, 2018.

- [39] M. Weber, C. Löschnauer, J. Wolf, M. Gely, R. Hanley, J. Goodwin, C. Ballance, T. Harty, and D. Lucas, "Cryogenic ion trap system

for high-fidelity near-field microwave-driven quantum logic," *Quantum Science and Technology*, vol. 9, no. 1, p. 015007, 2023.