# A flexible framework for early power and timing comparison of time-multiplexed CGRA kernel executions

Maxime Henri Aspros<sup>1</sup>, Juan Sapriza<sup>2</sup>, Giovanni Ansaloni<sup>2</sup>, David Atienza<sup>2</sup>

<sup>1</sup> Polytechnique Montreal, Montreal, Canada - maxime.aspros@polymtl.ca,

<sup>2</sup>EPFL, Lausanne, Switzerland - {name.surname}@epfl.ch

# ABSTRACT

At the intersection between traditional CPU architectures and more specialized options such as FPGAs or ASICs lies the family of reconfigurable hardware architectures, termed Coarse-Grained Reconfigurable Arrays (CGRAs). CGRAs are composed of a 2-dimensional array of processing elements (PE), tightly integrated with each other, each capable of performing arithmetic and logic operations. The vast design space of CGRA implementations poses a challenge, which calls for fast exploration tools to prune it in advance of time-consuming syntheses. The proposed tool aims to simplify this process by simulating kernel execution and providing a characterization framework. The estimator returns energy and latency values otherwise only available through a time-consuming post-synthesis simulation, allowing for instantaneous comparative analysis between different kernels and hardware configurations.

## CCS CONCEPTS

• Computer systems organization → Embedded software. KEYWORDS

CGRA, Design Space Exploration, Simulator

#### **ACM Reference Format:**

Maxime Henri Aspros<sup>1</sup>, Juan Sapriza<sup>2</sup>, Giovanni Ansaloni<sup>2</sup>, David Atienza<sup>2</sup>. 2025. A flexible framework for early power and timing comparison of timemultiplexed CGRA kernel executions. In 22nd ACM International Conference on Computing Frontiers (CF Companion '25), May 28–30, 2025, Cagliari, Italy. ACM, New York, NY, USA, 4 pages. https://doi.org/10.1145/3706594.3726977

# **1 INTRODUCTION**

While CPU-based architectures have long dominated edge computing, their efficiency has been shown to be short when executing tasks that could benefit from parallelization, such as those widely present in edge-AI applications. Several efforts have been made to provide parallelization and task-specific capabilities to MCU, such as clusters of CPUs [1, 2] and task-specific accelerators [3]. The first provide great flexibility at the cost of area and power overhead. The latter offer high efficiency at the expense of versatility to accelerate other tasks that might be required during the application. Coarse-Grained Reconfigurable Arrays (CGRAs) [4] have gained attention as meet-in-the-middle solutions that provide parallelization through an array of simple Processing Elements (PEs), which are capable of executing a limited set of arithmetic and logic operations, providing flexibility at a low overhead. CGRAs are

CF Companion '25, May 28-30, 2025, Cagliari, Italy

© 2025 Copyright held by the owner/author(s).

ACM ISBN 979-8-4007-1393-4/2025/05.

https://doi.org/10.1145/3706594.3726977

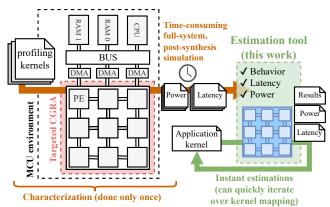

Figure 1: Workflow of the estimation tool. Profiling kernels are used to obtain a characterization in power and latency of the targeted CGRA (as part of a broader MCU environment). These one-time-results are used to create a model over which application kernels can be simulated to obtain accurate and instant power and timing results.

typically classified into two categories based on how they manage processing capabilities and scheduling. Spatial models, in which the configuration of each PE remains unchanged until the execution of a kernel finishes, only requiring a static compilation [5]. CGRAs that are time-multiplexed differ in that they support different PE configurations (CGRA instructions) during execution.

In time-multiplexed CGRAs such as [6-9], compute-intensive loops (kernels) are mapped across a range of PEs and time (instructions). At each iteration, the CGRA executes one instruction, which consists of a unique operation for each of its PEs. The execution of the whole kernel depends on the coordination of neighboring PEs, and therefore they all share a common program counter (PC) and will advance to the next instruction simultaneously once all PEs have finished. Each PE can execute an operation from the CGRA's ISA and take arguments either from immediate values, their own set of registers, or neighboring PEs. CGRAs are usually not instantiated standalone, but rather are used as an accelerator of a broader system encompassing CPU, memory and other peripherals. If the CGRA does not have its own dedicated memory, it must share the access to memory with other elements in the system. This complex structure makes mapping kernels to time-multiplexed CGRAs a challenge due to spatial, temporal, and system-dependent considerations and the need to manage various levels of freedom. Large efforts have been made to develop compilers that facilitate this task [10-13], but they still fall short of considering the effect of the whole system on the CGRA's execution. Additionally, simulating the execution of a

Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for third-party components of this work must be honored. For all other uses, contact the owner/author(s).

Table 1: Considered non-idealities and their corresponding cases

| Assumption                                  | Cases      |

|---------------------------------------------|------------|

| 1cc per operation                           | (i)        |

| Fixed duration per operation                | (ii)       |

| Accounts for latency of memory accesses     | (iii)-(vi) |

| Fixed power (of a NOP)                      | (i)-(iii)  |

| Fixed power per operation                   | (iv)       |

| Accounts for idle power                     | (v)        |

| Accounts for power of changing the datapath | (vi)       |

kernel usually requires a time-consuming RTL simulation, and obtaining power estimates even requires slower post-synthesis simulations. Previous estimators include CGRA-EAM [14], which proposes an energy and area estimation framework for space-multiplexed CGRAs. However, this model is data agnostic and therefore cannot leverage run-time information, instead relying on an execution trace.

Recognizing this challenge, this work streamlines the analysis process by introducing a behavioral simulation tool, combined with a customizable estimator. The estimator's workflow allows for an incremental adjustment of precision, according to the number of accounted non-idealities. For example, an initial run can focus mainly on latency, with a power consumption that scales linearly with the duration of an instruction. The precision of the estimation can then be further enhanced with specifications such as the chosen bus type or even certain properties at the PE level, including the datapath switch and register choice.

The estimation tool presented in this work (green in Figure 1) is open-source<sup>1</sup>, and is entirely Python-based. A model of the target CGRA and its ISA is built as a set of modular Python functions (blue in Figure 1), which allows for behavioral simulation. The state of each PE and its internal registers in each cycle can be observed to debug the application kernel. To include power and latency estimations, a characterization model needs to be provided. The target CGRA is to be profiled using custom kernels to obtain power and latency values for different non-idealities that want to be modeled (red in Figure 1). Using the characterization, our tool is able to estimate the power and latency for each PE and cycle, providing a full profiling of the application kernel without incurring in any more time-consuming post-synthesis simulations. Due to the instantaneous result, this work allows for rapid iterations over software and hardware. Once satisfied with the result, the final instructions are encoded into a bitstream to be deployed into the CGRA. In this work, we model the OpenEdgeCGRA [6], an open-hardware low-power CGRA to validate the model's performance, but handle other instruction-based CGRAs given sufficient characterization information.

### 2 VALIDATION

The quality of the estimation depends on the level of detail provided by the user in the characterization profile. A basic version of the model (case (i) from Table 1), using a uniform latency and power

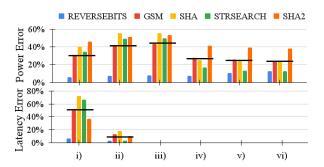

Figure 2: Impact of non-idealities on estimator precision. Absolute error obtained from executing five benchmark kernels on the tool of this work vs results obtained from postsynthesis simulation. The average of each case is marked in black.

value for each operation, presents a significant discrepancy between behavioral analysis and expected values. This is showcased in Figure 2, comparing post-synthesis simulations of the OpenEdgeCGRA in TSMC 65nm LP process against the results from our tool. By progressively including non-idealities, the user can help strengthen the subsequent models (ii-vi). This requires writing specific test kernels to characterize the CGRA's profile. Table 1 lists the parameters used for the sample explorations, while Figure 2 illustrates the decrease in latency and power error after including each non-ideality.

The first three iterations represent the step-by-step refinement of latency estimation. As the tool incorporates additional parameters from the characterization file, precision improves. Step (ii) considers a unique latency value for each operation, obtained from the characterization file. In the case of OpenEdgeCGRA, all logic and arithmetic operations take 1 clock cycle (cc), with the exception of multiplication (3 cc) and memory accesses, which vary drastically depending on the state of the rest of the system. The next step (iii) considers in addition this delay incurred while waiting for memory accesses. The following three iterations focus on power estimation. Step (i) begins with a basic approach, applying the same consumption to all operations (in this case, the power of executing a NOP operation). Step (iv) considers a fixed power per operation, disregarding a consumption profile across the execution of the instruction (similar to step (ii)). Step (v) is analogous to step (iii), as it considers the idle power consumed by a PE after executing its operation and while waiting for other PEs on the CGRA to finish their execution. Step (vi) considers changes in the datapath, i.e. the cost of switching muxes if the operation of a PE changes from one instruction to the next, and the cost different arguments may require (e.g. distinguishes between multiplying by 0 and other values, or if the arguments are fetched from an immediate, a register or a neighbouring PE).

Although this example uses values specific to OpenEdgeCGRA, the estimator remains flexible and allows multiple variations with different CGRAs. These variations can be supported by updating the characterization file with values obtained through testing or customizing the ISA by modifying the behavior of the operation functions in the Python model.

<sup>&</sup>lt;sup>1</sup>Available at: anonymous.4open.science

A flexible framework for early power and timing comparison of time-multiplexed CGRA kernel executions

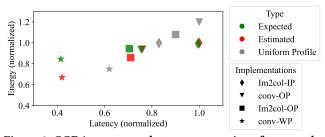

Figure 3: CGRA energy vs. latency comparison for convolution mappings. Values are normalized to the expected (postsynthesis) values for Im2col-IP.

Upon recording values taken from the test kernels, the model was validated on five kernels from the MiBench benchmark suite [15], obtaining the results shown in Figure 2. It ultimately achieves a 22% final error in power consumption, while the latency error decreases from to 46% to 9% with the first non-ideality and reaches the expected value by the third. This performance indicates that the profile accurately models latency and allows for comparative studies of power consumption. More importantly, as Section 3 will address, our approach handles comparative explorations of different implementations in both software and hardware.

# 3 USE CASES

This section presents applications of the estimator through two studies. The first study highlights the tool's potential for software exploration, with an example featuring several mappings of a same function. We then examine a second application, this time aimed towards exploring different hardware configurations. All simulations are carried out considering the most non-idealities as in case (vi).

# 3.1 Software exploration: Same hardware, same function, different instructions

Figure 3 presents an experiment that considers multiple convolutional mappings explored in [16]: Weight Parallelism (conv-WP), Input-Channel Parallelism (Im2col-IP), Output-Channel Parallelism (Im2col-OP), and Channel Output Parallelism (conv-OP). These various implementations use different strategies to compute a convolution and produce the same result. In [16], time-consuming post-synthesis simulations were run for each in order to evaluate behavior correctness and obtain latency and energy estimations to choose the most convenient approach. We replicated these results (green in Figure 3) and compared them with the results obtained from our tool (red in Figure 3). The close correlation between the obtained values shows how our tool can be used to choose the most convenient instruction mappings without incurring in timeconsuming simulations. For reference, Figure 3 also shows in gray the results that would have been obtained in case (i) of Table 1, which highlights the relevance of a proper characterization in order to draw relevant conclusions.

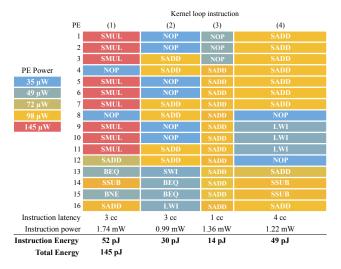

In addition to reduced runtime, our tool can also offer a finegrained breakdown of power and latency consumption. For the four instructions in the loop of the conv-WP convolution, the power and latency of each PE in a  $4 \times 4$  OpenEdgeCGRA is shown in Figure 4. For instance, it can be observed how the average power of instructions such as the NOP decreases over time as the power required during instruction decoding is much greater than the power

Figure 4: Power Consumption heatmap for the four instructions conforming the kernel loop of the WP convolution

consumed waiting for other PEs. This means that clustering timeconsuming operations in a single, long instruction helps reduce energy consumption vs. having several shorter instructions. It can also be observed how the largest contribution to overall energy is not operation power, but instead operation latency. Although CGRA instruction (1) is the most power hungry due to 9 signed multiplication (SMUL) operations, its overall energy is comparable to CGRA instruction (4), where most instructions are power-light, but waiting for memory accesses (LWI) drastically increases instruction energy. In the following study we will compare the effect on energy of reducing the latency of SMUL and memory access instructions through architectural changes and reinforce this observation.

# 3.2 Hardware exploration: Same function, same instructions, different hardware

In this study, only the conv-WP implementation is analyzed, but different hardware architectures are varying for the CGRA and its connection to the overall MCU system. In the state-of-the-art, similar architectural changes, such as memory bus modifications, MAC units, and operand reuse, currently require an extensive manual configuration prior to execution. [16–18]. In this scenario, the compared models contain structural modifications that involve changes in the RTL. In addition to the time required for a standard post-synthesis, these deeper changes habitually require rebuilding the model and must be entered by the user, extending the workflow even more. Using the estimator, the user can enter the changes and immediately execute the program afterwards.

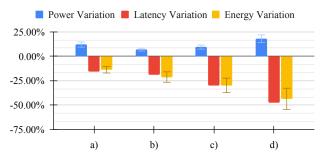

The percentage reduction in Figure 5 is measured relative to the baseline architecture used in previous analysis. The error bars featured in the chart account for the 22% error obtained for the power estimation (see Figure 2). The first modification (a) considers a multiplication operation that completes in one cc instead of three. To adjust for this reduced delay, the operation's power is increased threefold. The second modification (b) changes the bus type from 1-to-M to an N-to-M, thus allowing for parallel memory accesses (given they target different memory banks). The third modification (c) chooses to use an interleaved bus, while, the last CF Companion '25, May 28-30, 2025, Cagliari, Italy

Table 2: Hardware topology explorations and their corresponding cases

| Modification                         | Cases |

|--------------------------------------|-------|

| Accelerated SMUL (1 CC instead of 3) | (a)   |

| N-to-M bus type                      | (b)   |

| Interleaved memory banks             | (c)   |

| One DMA per cell                     | (d)   |

modification (d) simulates an architecture with one DMA per PE instead of one per column, and an N-to-M bus. This bus type must be selected in order to obtain the gains from adding more DMA ports.

In modification (a), the accelerated multiplication naturally leads to a decrease in total latency. However, because of the updated multiplication consumption, the overall power usage increases proportionally and the energy gains are marginal. Conversely, all changes relative to memory accesses (b-d) significantly reduce delays. As a result, the program waits less and executes more power-intensive instructions, increasing average power consumption. These cases confirm the role of accelerated memory accesses in decreasing energy, thus aligning with the analysis in subsection 3.1. Modification (d) lowers latency the most, as it can potentially remove any delay caused by multiple memory accesses in one instruction. Note that our estimation focuses only on the PE matrix, so the cost of additional DMA ports is not considered.

# 4 CONCLUSIONS

This work has featured a new and flexible framework to estimate CGRA kernel execution times, and has illustrated the underlying factors required to build an appropriate characterization profile for multi-objective application optimization (e.g., latency, power, etc.). We established how an iterative process of non-ideality inclusion maximizes the quality of the tool's performance, achieving an average error in power consumption of 22% for the benchmark kernels with no error in latency, and a 10% power consumption error with a 0.4% error in latency for the convolutions. Our comparisons across the convolution kernels reveal how the tool characterizes mappings across both energy and latency metrics, while hardware exploration highlighted the performance gains made apparent from testing different topologies. In combination, these features derived actionable insights across both co-design dimensions in an iterative process.

### ACKNOWLEDGEMENTS

This work was supported in part by the the Swiss NSF Edge-Companions project (GA No. 10002812); in part by the EC H2020 FVLLMONTI Project under Grant 101016776; in part by the AC-CESS—AI Chip Center for Emerging Smart Systems, sponsored by InnoHK funding, Hong Kong, SAR; and in part by the Swiss State Secretariat for Education, Research, and Innovation (SERI) through the SwissChips Research Project.

### REFERENCES

[1] Eric Flamand, Davide Rossi, Francesco Conti, Igor Loi, Antonio Pullini, Florent Rotenberg, and Luca Benini. GAP-8: A RISC-V SoC for AI at the Edge of the IoT. In 2018 IEEE 29th International Conference on Application-specific Systems, Architectures and Processors (ASAP), pages 1–4. IEEE, 2018.

Figure 5: Evaluating Hardware Topology Impact on Optimization

- [2] Angelo Garofalo et al. PULP-NN: Accelerating Quantized Neural Networks on Parallel Ultra-Low-Power RISC-V Processors. *Phil. Trans. of the Royal Society A*, 378(2164):20190155, 2020.

- [3] GreenWaves Technologies. GAP9. https://greenwaves-technologies.com/gap8\_ mcu\_ai/, 2024.

- [4] Artur Podobas et al. A Survey on Coarse-Grained Reconfigurable Architectures From a Performance Perspective. IEEE Access, 8:146719–146743, 2020.

- [5] Daniel Vazquez, Jose Miranda, Alfonso Rodriguez, Andres Otero, Pascuale Davide Schiavone, and David Atienza. STRELA: STReaming ELAstic CGRA Accelerator for Embedded Systems, 2024.

- [6] Rubén Rodríguez Álvarez et al. An Open-Hardware Coarse-Grained Reconfigurable Array for Edge Computing. In Proc. of the 20th ACM CF, pages 391–392, 2023.

- [7] Loris Gérard Duch et al. HEAL-WEAR: an Ultra-Low Power Heterogeneous System for Bio-Signal Analysis. IEEE Transactions on Circuits and Systems I: Regular Papers, 64(9):14. 2448–2461, 2017.

- [8] Satyajit Das, Davide Rossi, Kevin Martin, Philippe Coussy, and Luca Benini. A 142MOPS/mW Integrated Programmable Array accelerator for Smart Visual Processing. In *IEEE International Symposium on Circuits & Systems*, Baltimore, United States, May 2017.

- [9] Thilini Kaushalya Bandara, Dhananjaya Wijerathne, Tulika Mitra, and Li-Shiuan Peh. REVAMP: A Systematic Framework for Heterogeneous CGRA Realization. In Proceedings of the 27th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, page 918–932, New York, NY, USA, 2022. Association for Computing Machinery.

- [10] Cristian Tirelli et al. SAT-based Exact Modulo Scheduling Mapping for Resource-Constrained CGRAs. ACM Journal on Emerging Technologies in Computing Systems, 2024.

- [11] Yuxuan Wang, Cristian Tirelli, Lara Orlandic, Juan Sapriza, Rubén Rodríguez Álvarez, Giovanni Ansaloni, Laura Pozzi, and David Atienza Alonso. An mlir-based compilation framework for cgra application deployment. *Applied Reconfigurable Computing. Architectures, Tools, and Applications*, 2025.

- [12] Bingfeng Mei et al. Exploiting Loop-Level Parallelism on Coarse-Grained Reconfigurable Architectures Using Modulo Scheduling. *IEE Proceedings-Computers* and Digital Techniques, 150(5):255-261, 2003.

- [13] Dhananjaya Wijerathne et al. HiMap: Fast and Scalable High-Quality Mapping on CGRA via Hierarchical Abstraction. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 41(10):3290–3303, 2021.

- [14] Mark Wijtvliet, Henk Corporaal, and Akash Kumar. CGRA-EAM–Rapid Energy and Area Estimation for Coarse-grained Reconfigurable Architectures. ACM Transactions on Reconfigurable Technology and Systems, 14(4):19:1–19:28, September 2021.

- [15] Matthew R Guthaus, Jeffrey S Ringenberg, David Ernst, Todd M Austin, Trevor Mudge, and Richard B Brown. MiBench: A free, commercially representative embedded benchmark suite. In *Proceedings of the Fourth IEEE International Workshop on Workload Characterization*, pages 3–14. IEEE, 2001.

- [16] Nicolo Carpentieri, Juan Sapriza, Davide Schiavone, Daniele Jahier Pagliari, David Atienza, Maurizio Martina, and Alessio Burrello. Performance evaluation of acceleration of convolutional layers on OpenEdgeCGRA. In Workshop on Open-Source Hardware, pages 1–4. ACM, 2024.

- [17] Jungi Lee and Jongeun Lee. Specializing CGRAs for Light-Weight Convolutional Neural Networks. IEEE TCAD, 41(10):3387–3399, 2021.

- [18] Christian Heidorn et al. Design Space Exploration for Layer-parallel Execution of Convolutional Neural Networks on CGRAs. In Proc. of the 23th SCOPES, pages 26–31, 2020.