# SparseZipper: Enhancing Matrix Extensions to Accelerate SpGEMM on CPUs

Tuan Ta<sup>1</sup>, Joshua Randall<sup>2</sup>, and Christopher Batten<sup>1</sup>

<sup>1</sup> Cornell University, Ithaca, NY {qtt2,cbatten}@cornell.edu

<sup>2</sup> Arm Inc., Austin, TX Joshua.Randall@arm.com

Abstract—The importance of general matrix multiplication (GEMM) is motivating new instruction set extensions for multiplying dense matrices in almost all contemporary ISAs, and these extensions are often implemented using high-performance systolic arrays. However, matrices in emerging workloads are not always dense, and sparse matrices where the vast majority of values are zeros are becoming more common. Existing matrix extensions and micro-architectures cannot efficiently process highly sparse matrices due to two reasons: (1) wasted work when one or both input values are zero; and (2) incompatibility with sparse matrix formats. This work proposes SparseZipper that minimally modifies existing matrix extensions and systolic-array-based micro-architectures specialized for dense-dense GEMM to accelerate sparse-sparse GEMM operating on highly sparse matrices with unstructured sparsity structures. Our performance evaluation shows SparseZipper achieves 5.98× and 2.61× speedup over a scalar hash-based implementation of SpGEMM and a state-of-the-art vectorized SpGEMM version, respectively. Our component-level area evaluation shows SparseZipper increases the area of a baseline 16×16 systolic array by only 12.7% resulting in an area overhead for an entire system-on-chip of just a few percent.

#### I. INTRODUCTION

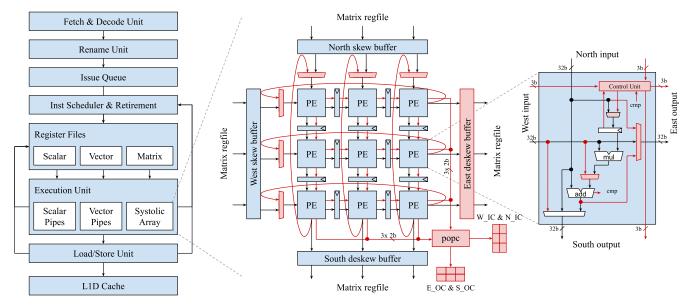

General matrix multiply (GEMM) is a key building block in many different domains including machine learning, graph analytics, and scientific computing. Therefore, numerous domain-specific architectures have been proposed to accelerate dense-dense GEMM (i.e., most values in both input matrices are non-zeros) with various trade-offs in programmability, performance, and energy efficiency [8,9,31,32,52]. In addition to coarse-grain accelerators, CPU vendors have recently introduced matrix extensions (e.g., Intel's Advanced Matrix Extension (AMX) [26, 29, 37], Arm's Scalable Matrix Extension (SME) [2], RISC-V's matrix extension proposal [47]. and IBM's Matrix-Multiply Assist (MMA) [25]) to their ISAs for dense-dense GEMM acceleration. Such matrix extensions attempt to strike a balance between programmability and efficiency, and they are often implemented using systolic-arraybased micro-architectures [26, 37].

However, matrices in workloads are not always dense. In fact, many recent neural network models [21, 32, 38, 45, 54], real-world graph analytics [13, 24, 49], and scientific simulations [6, 17] operate on sparse matrices where the majority of values are zeros. In addition, matrix densities (i.e., the percentage of non-zero values in a matrix) vary dramatically across domains (e.g., from  $10^{-6}$ % density in matrices representing social graphs to 50% density in matrices used in neural network models [23]). Such low matrix densities prevent computing GEMM for sparse matrices efficiently on CPUs

using the recently introduced matrix extensions since most multiplications will involve at least one input value which is zero. Moreover, sparse matrices are typically stored in compact formats with metadata indicating positions of non-zero values for space efficiency, so they are not directly compatible with existing built-in matrix engines specialized for processing matrices stored in a dense format.

In addition to numerous domain-specific sparse-sparse GEMM (SpGEMM) accelerators [23, 42, 50, 57, 58], previous work has proposed several ISA extensions to accelerate sparse computations. SparseCore [44] is a streambased ISA extension designed specifically for sparse computations at the cost of extra hardware for stream registers and stream processing units without efficiently supporting dense-dense GEMM. VEGETA extends a matrix extension to accelerate sparse-dense matrix-matrix multiplication (SpMM) in addition to dense computations [28]. However, VEGETA is limited to SpMM and DNN-specific sparsity structures, so it is not efficient when multiplying two highly sparse (i.e., less than 1% density) matrices with unstructured sparsity structures, which is critical in various workload domains including graph analytics (e.g., multi-source breadthfirst search, peer pressure clustering, cycle detection, triangle counting, etc.) [4,11,43,48], hybrid linear solvers (e.g., Schur complement method and algebraic multi-grid methods) [55], context-free grammar parsing [40], molecular dynamics simulatio [27], and interior point methods [33].

In this work, we propose SparseZipper that minimally extends existing matrix ISAs and systolic-array-based microarchitecture specialized for dense-dense GEMM to accelerate SpGEMM operating on highly sparse matrices with unstructured sparsity structures. SparseZipper targets a conventional row-wise dataflow SpGEMM algorithm (i.e., Gustayson algorithm) with sparse matrices represented in commonly used compressed sparse row/column (CSR/CSC) formats. The abstraction and micro-architecture of SparseZipper are specialized for accelerating the algorithm's main performance bottleneck which involves merging multiple sparse vectors represented as streams of indices (i.e., keys) and data (i.e., values). By leveraging existing matrix registers for storing key-value streams and a systolic array for merging multiple streams, SparseZipper incurs minimal area overhead. Our performance evaluation shows SparseZipper achieves 5.98× and  $2.61 \times$  speedup over a scalar hash-based implementation of SpGEMM and a state-of-the-art vectorized SpGEMM version, respectively. Our component-level area evaluation shows SparseZipper increases the area of a baseline  $16 \times 16$  systolic array by only 12.7%. This overhead would be much lower when considering an entire processor and its caches.

**Contributions** – Our key contributions include: (1) a SparseZipper ISA extension that enhances an existing matrix ISA to efficiently support merging multiple key-value streams, the main performance bottleneck in the conventional row-wise dataflow SpGEMM algorithm; (2) a minimal set of micro-architectural changes to a systolic array to support the new SparseZipper instructions; and (3) a detailed cycle-level evaluation demonstrating the performance benefits of SparseZipper and a first-order area evaluation demonstrating the minimal additional hardware needed for SparseZipper.

## II. BACKGROUND

This section provides background on recent matrix ISA extensions and common SpGEMM algorithms.

#### A. Matrix ISA Extensions for Dense GEMM

The importance of GEMM has led to an emergence of matrix extensions in contemporary ISAs. Arm recently released its SME extension that introduces a new instruction performing an outer product of two vectors and accumulating its results into a new two-dimensional accumulator register [2]. IBM took a similar approach in its MMA extension for the Power ISA [25]. Intel introduced a new AMX extension that adds several matrix registers called tile registers and a new matrix-matrix multiply instruction on two tile registers [26, 37]. The RISC-V community recently proposed a matrix extension that is similar to Intel AMX's approach [47]. One common micro-architecture for accelerating dense-dense GEMM is a systolic array, a grid of multiply-add processing elements (PEs) connected in a mesh network [29, 32, 37]. A systolic array can support either input-, weight-, or outputstationary dataflows, depending on which input or output matrix stays inside the array throughout the computation.

## B. SpGEMM Dataflows

The inner-product dataflow computes each element in the output matrix by performing a dot product between a row in the first input matrix and a corresponding column in the second input matrix. Multiple dot product operations for different output elements can happen in parallel. For highly sparse matrices, one major downside of this dataflow is that a dot product of two highly sparse vectors is likely to produce a zero, which is wasted.

The outer-product dataflow performs an outer product between a column in the first input matrix and a corresponding row in the second input matrix to produce a partial output matrix. Multiple partial output matrices are then merged into a single matrix. This dataflow avoids the wasted computation incurred in the inner-product dataflow at the cost of highly complex merging operation of multiple matrices and potentially significant memory space for storing partial matrices.

The row-wise-product dataflow (Gustavson algorithm) computes each row of an output matrix by multiplying a row

Figure 1. Multiple Steps to Compute One Output Row – Each tuple includes a column index (key) and a value.

| Step 1: two sorted partitions to be merged                                               |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 0,15 1,7 2,5 3,18 7,1 8,5                                                                |  |  |  |  |  |  |  |

| 0,13 4,1 6,7 8,3                                                                         |  |  |  |  |  |  |  |

| Step 2: merge 4-tuple chunks from input partitions & generate 4 output tuples            |  |  |  |  |  |  |  |

| 0,15 1,7 2,5 3,18 7,1 8,5                                                                |  |  |  |  |  |  |  |

| 0,13 4,1 6,7 8,3                                                                         |  |  |  |  |  |  |  |

| Step 3: merge the remaining tuples from input partitions & generate 4 more output tuples |  |  |  |  |  |  |  |

| 0,15 1,7 2,5 3,18 7,1 8,5                                                                |  |  |  |  |  |  |  |

| 0,13 4,1 6,7 8,3                                                                         |  |  |  |  |  |  |  |

Figure 2. Merging Two Sorted Key-Value Partitions in Chunks – e.g., merging the last two key-value partitions in Figure 1.

in the first input matrix with the entire second input matrix (vector-matrix multiplication). Similar to the outer-product dataflow, this row-wise-product dataflow is work-efficient for highly sparse matrices since it processes only non-zero input elements that contribute to non-zero output elements. The vector-matrix multiplication involves merging multiple sparse vectors into a single vector, which is less complex than merging multiple sparse matrices as in the outer-product dataflow. In addition, unlike both inner-product and outer-product dataflows, the row-wise-product dataflow does not require two input matrices to be stored in two different formats: CSR and CSC. All input and output matrices can be consistently stored in CSR, so there is no need for converting between different sparse matrix formats. In this work, we target the row-wise-product dataflow.

## **III. SPARSEZIPPER INSTRUCTION SET EXTENSION**

In this section, we first describe a merge-based implementation of the row-wise-product SpGEMM algorithm to motivate key designs in our SparseZipper ISA extension. We then present details of SparseZipper abstraction.

#### A. Merge-Based Row-Wise-Product SpGEMM

Figure 1 shows an example of the row-wise-product dataflow in multiplying two sparse matrices. Partial results for an *i-th* row in the output matrix are generated by multiplying each non-zero element A[i][j] in the first matrix with all non-zero elements B[j][k] in a *j-th* row of the second matrix. After generating partial results, for each row of the output matrix, we get a list of tuples, each consisting of a column index (key) and a value. To generate an output row, this list, which is called a key-value stream, is then sorted by keys, and tuples with duplicate keys are accumulated. The

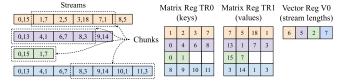

Figure 3. Mapping Between Key-Value Streams and Matrix Registers – Only chunks of key-value tuples with dashed borders are held in the two matrix registers.

final sorted stream of unique key-value tuples represents nonzeros in the *i-th* row of the output matrix.

Merging partial tuples into the final list can be done in multiple steps. The expanded list is split into equally sized partitions. Tuples in each partition are then sorted by their keys. Finally, adjacent partitions are merged together in multiple reduction steps to form a final sorted streams of tuples, as shown in Figure 1. This merging procedure is similar to the conventional merge sort algorithm except that tuples with duplicate keys are accumulated.

In order to merge two long sorted partitions of key-value tuples, we break them in chunks fitting in registers (e.g., vector registers) and repeatedly merge two N-element chunks (i.e., one from each tuple) at a time as shown in Figure 2. It is important to note that we may not be able to move all N tuples from each partition in one step. For example, in the first two chunks (in Figure 2), three tuples (4, 1), (6, 7), and (8, 3) from the second partition cannot be moved to the output partition since their keys are greater than every key from the current chunk in the first partition. Instead, those tuples need to be merged in the next step. Therefore, the number of tuples that we can advance at the end of a step in each partition is data-dependent.

#### **B.** Architectural States

SparseZipper leverages both vector and matrix registers in the base vector and matrix ISAs to store key-value streams and their metadata. Without the loss of generality, in this work, we use the RISC-V vector extension [46] as the base vector ISA and a baseline matrix ISA inspired by Intel AMX [26] and the RISC-V matrix extension proposal [47].

**Matrix registers** – The base matrix ISA supports eight general-purpose two-dimensional matrix registers (tile registers) named from TR0 to TR7. The length in bits for a row in a matrix register is the same as the number of bits in a single vector register (VLEN) as defined in the RISC-V vector extension. In this work, we limit the size in bits of each element (i.e., ELEN) in a vector register to 32 bits to simplify our description of SparseZipper. A complete matrix instruction set may support other element bit widths such as 16 and 64 bits. There are R = VLEN/ELEN elements in a row of a matrix register. We assume that each matrix register has the same number of rows as the number of elements in a row.

**Mapping streams to matrix and vector registers** – SparseZipper enables processing multiple key-value streams by mapping them to different rows of a matrix register. Figure 3 shows an example of this stream-register mapping. Matrix registers TRO and TR1 store keys and values respectively. Each row of a matrix register is mapped to a stream, and it stores a chunk of keys or values in the stream. SparseZipper uses existing vector registers to store metadata about a current set of streams (e.g., vector register V0 in Figure 3 stores the number of tuples in each stream).

**Special-purpose counter vector registers** – SparseZipper introduces a set of four light-weight special-purpose counter vector registers. ICO and IC1 are used for counting processed elements per input matrix row. OCO and OC1 are used for counting output elements per output matrix row. More details regarding the use of those registers are specified in the following instruction set specification. Since each counter in a counter vector register counts up to the max number of elements (i.e., R) in a row of a matrix register, each counter is  $\log_2 R$ -bit wide. Therefore, each counter vector register has  $R \times \log_2 R$  bits in total.

## C. Instruction Set Specification

Table I shows a list of SparseZipper instructions including (1) indexed matrix load and store, (2) stream sorting, (3) stream merging, and (4) counter vector move instructions.

Indexed matrix load and store instructions – SparseZipper introduces two memory instructions: mlxe.t and msxe.t to move key-value chunks from multiple streams between matrix registers and memory. Multiple key-value streams may have different lengths, and their chunks are located at arbitrary locations. Therefore, in addition to the base address (rs1) and matrix register (td1), mlxe.t and msxe.t take two vector operands: vs2 specifying memory locations (i.e., byte offsets to a base address) and vs3 holding stream lengths.

Stream sorting instructions – SparseZipper introduces two instructions called mssortk.tt and mssortv.tt to sort multiple chunks of key-value tuples by keys. The two instructions work together by first sorting keys and then shuffling values based on the key reordering. Duplicate keys are combined, and their corresponding values are accumulated. In order to transfer the key reordering information between mssortk.tt and mssortv.tt instructions, SparseZipper adds an abstract special-purpose architectural state that captures how input keys are reordered per key-value chunk. This state is intentionally left abstract in the ISA specification so that a micro-architecture can freely choose how to implement it. Section IV later discusses an implementation of this state using a systolic array. Since an output chunk may be shorter than its input chunk (i.e., due to duplicate keys), mssortk.tt updates the special-purpose output counter vector registers (OCO and OC1) with the lengths of output chunks.

**Stream merging instructions** – SparseZipper provides two instructions called mszipk.tt and mszipv.tt to merge sorted key-value partitions of a stream. Similar to mssortk.tt and mssortv.tt, the two stream merging instructions work together by first merging keys and then shuffling values. Duplicate keys are combined, and their corresponding values are accumulated. The key reordering is also captured by an abstract special-purpose architectural state that is produced by mszipk.tt and then used by mszipv.tt to shuffle and accumulate values. Instruction mszipk.tt updates input counter vector registers (ICO and IC1) with the number of tuples that have been merged per input partition.

TABLE I. LIST OF SPARSEZIPPER INSTRUCTIONS

| Instructions                  | Description                                                                                                  |  |  |

|-------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|

| mlxe.t td1, 0(rs1), vs2, vs3  | Load data into td1 using indices in vs2; rs1 is the base address; vs3 are stream lengths.                    |  |  |

| msxe.t ts1, 0(rs1), vs2, vs3  | Store data from $ts1$ using indices in $vs2$ ; $rs1$ is the base address; $vs3$ are stream lengths.          |  |  |

| mssortk.tt td1, td2, vs1, vs2 | Sort keys in td1 and td2; vs1 and vs2 are input lengths.                                                     |  |  |

| mssortv.tt td1, td2, vs1, vs2 | Shuffle & accumulate values in td1 and td2 based on last key sorting results; vs1 and vs2 are input lengths. |  |  |

| mszipk.tt td1, td2, vs1, vs2  | Merge keys in td1 and td2; vs1 and vs2 are input lengths.                                                    |  |  |

| mszipv.tt td1, td2, vs1, vs2  | Shuffle & accumulate values in td1 and td2 based on last key merging results; vs1 and vs2 are input lengths  |  |  |

| mmv.vi vd, cimm               | Move values from an input counter vector IC[cimm] to vd                                                      |  |  |

| mmv.vo vd, cimm               | Move values from an output counter vector OC[cimm] to vd                                                     |  |  |

The output counter vector registers (OCO and OC1) are updated with the number of elements per merged output partition.

**Counter vector move instructions** – SparseZipper provides two move instructions mmv.vi and mmv.vo that copy values from special-purpose input and output counter vector registers respectively into general-purpose vector registers. These values are typically used to update pointers and stream lengths through vector instructions.

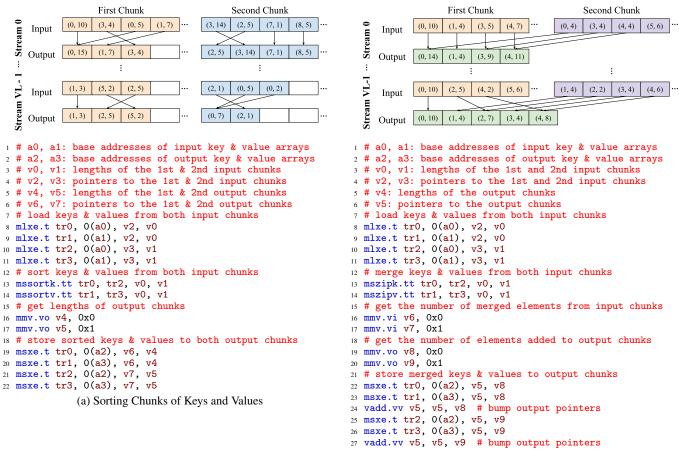

## D. Code Examples

Sorting key-value chunks – Figure 4(a) shows a RISC-V assembly code snippet of sorting key-value chunks from VLEN number of streams. Keys and values of current chunks are loaded into matrix registers using mlxe.tt in lines 8-11. Register tr0 and tr2 hold input keys while register tr1 and tr3 store corresponding input values. In line 13, mssortk.tt sorts per-chunk keys in an ascending order and writes the sorted keys in the same matrix registers (tr0 and tr2). In line 14, mssortv.tt shuffles and accumulates values based on the reordering of keys. Lines 16-17 move lengths of output chunks from the special-purpose output counter vectors into general-purpose vector registers for updating the lengths of output streams. Finally, keys and values in output chunks are written back to memory in lines 19-22.

Merging key-value chunks - Figure 4(b) shows a RISC-V assembly code snippet of merging key-value chunks from adjacent partitions across VLEN number of streams. Similar to the sorting code, keys and values of current chunks are loaded into matrix registers using mlxe.tt in lines 8-11, and register tr0 and tr2 hold input keys while register tr1 and tr3 store corresponding input values. In lines 13-14, mszipk.tt merges pairs of key-value chunks across VLEN streams, and mszipv.tt shuffles corresponding values based on the key reordering. Duplicate keys are combined, and their values are accumulated. Merged and sorted output keys are stored in the same tr0 and then tr1 in an ascending order. Lines 16-17 move per-input-chunk numbers of merged keys from specialpurpose counter registers ICO and IC1 into general-purpose vector registers for updating input pointers. Lines 19-20 extract lengths of output chunks from counter vector registers 0C0 and 0C1. In lines 22-27, merged keys and values are written back to memory per output streams using msxe.t.

#### IV. SPARSEZIPPER MICRO-ARCHITECTURE

This section describes SparseZipper micro-architecture that extends a baseline systolic array specialized for densedense GEMM to support the proposed instructions for sparsesparse GEMM presented in Section III. Each sorting/zipping instruction is decomposed into micro-operations. Each input matrix row corresponding to a data stream is processed in one micro-operation going through the systolic array in two passes: (1) sorting/zipping and (2) compressing. The execution of one micro-operation is explained in Section IV-A and IV-B. In Section IV-C, we then explain how pipelining happens across micro-operations of a single instruction and multiple instructions. Finally, in Section IV-D, we discuss hardware changes needed to support SparseZipper.

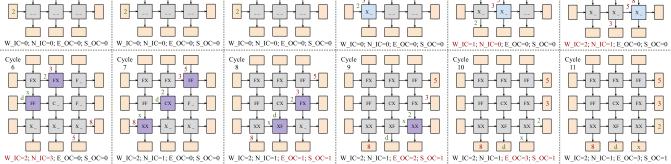

## A. Systolic Execution of Sorting Key-Value Chunks in a Single Stream

Figure 5(a) shows a  $3 \times 3$  systolic array executing mssortk instruction to sort two unsorted chunks of keys over multiple cycles. Initially, the two input chunks are located in the west and north sides of the array. Similar to a typical systolic execution of dense-dense GEMM, inputs are staggered into the array. Outputs come out from the east and south sides. The dataflow through the array is the same as in dense-dense GEMM. Each PE receives inputs from the west and north sides and south sides.

Input keys flow through the array in two passes: sorting and compressing. In the sorting pass, keys in a chunk are sorted in an ascending order. If a chunk contains duplicates, the sorting pass combines them into one valid output key, and the rest become invalid outputs to be excluded. The invalid outputs may exist in between valid outputs after the sorting pass, so the compressing pass places valid outputs consecutively starting from the first position of an output chunk and moves invalid outputs to the end. For example, in Figure 5(a), after the sorting pass, the north-side inputs  $\{5, 8, 5\}$  come out in the east side as  $\{5, d, 8\}$  (i.e., d indicates excluded duplicated key(s)). In the compressing pass, the partial output chunk is pushed into the array from the west side, and the final output chunk  $\{5, 8, d\}$  comes out from the south side.

When sorting keys, we need to store the key reordering so that their values can be shuffled to correct positions later. In each PE, we encode and store the direction in which westside and north-side keys are routed towards and whether the keys are duplicate. Given a pair of input keys, there are four possible states: (1) initial (no data routing), (2) forwarding, (3) switching, and (4) combining. The forwarding state encodes a PE routes west-side and north-side keys to the east and south sides respectively. The switching state encodes a PE routes west-side and north-side keys to the south and east sides respectively. The combining state encodes that two input keys are duplicate and that they are combined into one

(b) Merging Chunks of Keys and Values

Figure 4. Examples of Using SparseZipper Instructions to Sort and Merge Key-Value Streams –  $a{0..3}$  = scalar registers;  $v{0..9}$  = vector registers;  $tr{0..3}$  = matrix registers.

valid key routed to the south side. Each PE needs to store the states for both sorting and compressing passes.

The west- and north-side input keys are sorted independently using the bottom-left and top-right half of the systolic array. PEs on the main diagonal are hard-coded to always switch inputs so that data from two input chunks are not intermixed. In other PEs, two input keys are compared. The larger key is routed to the east, and the smaller key is routed to the south (e.g., cycle 2 in Figure 5(a)). If keys are duplicate (e.g., cycle 5 in Figure 5(a)), a single combined valid key is sent to the south port, and the east output is tagged as invalid key. In subsequent PEs, the invalid key is considered larger than any valid key, so it is always forwarded to the east.

Instruction mssortk updates special-purpose input and output counter vector registers:  $W_IC$  (for the west input),  $N_IC$  (for the north input),  $E_OC$  (for the east output) and  $S_OC$  (for the south output) as keys come out from the array as shown in Figure 5(a) to count the number of processed input keys and valid output keys. Input counters ( $W_IC$  and  $N_IC$ ) are updated in the sorting pass while output counters ( $E_OC$  and  $S_OC$ ) are updated in the compressing pass.

Instruction mssortv shuffles values based on a key reordering produced by mssortk. Values are also passed through the array in two passes and directed based on the states captured in each PE during the execution of mssortk. If the state is combining, two values are accumulated, and the accumulated value is forwarded to a PE's south side. Instruction mssortv does not update the input and output counters.

## B. Systolic Execution of Merging Key-Value Chunks in a Single Stream

Figure 5(b) shows the systolic execution of mszipk instruction in a  $3 \times 3$  array to merge two sorted key-value chunks from a single stream. Initially, the two input chunks are placed in the west and north sides. Keys in the west side are ordered from bottom to top in an ascending order while keys in the north side are ordered from left to right. The final output chunk is stored in two parts. For example, the part with smaller keys  $\{2, 3, 5\}$  is located in the east side while the second part with larger keys  $\{8\}$  is stored in the south side.

Keys flow through the systolic array in two passes: merging and compressing. The merging pass generates a merged list of sorted keys with invalid outputs (i.e., caused by duplicate keys) potentially located in between valid output keys. The compressing pass then places valid output keys consecutively. Unlike the sorting pass, the merging pass intermixes keys from both input chunks, so PEs on the main diagonal work the same as other PEs instead of being hard-coded to

(b) Systolic Execution of mszipk Instruction.

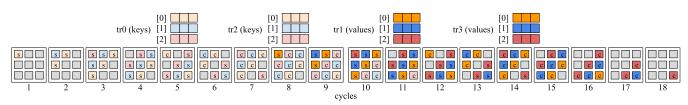

Figure 5. Cycle-by-Cycle Systolic Execution of mssortk in a  $3 \times 3$  Systolic Array for Two Unsorted Lists of Keys – PE states: F = forward, X = switch, C = combine; W\_IC = west input counter; N\_IC = north input counter; E\_OC = east output counter; S\_OC = south output counter; d = duplicate key that is excluded; x = unmergeable key; Counters in red indicate they are being updated. PEs in gray are inactive. PEs in blue are merging keys. PEs in purple are compressing valid output keys. Keys in red come from the north input. Keys in green come from the west input. Keys in west and east sides are ordered from bottom to top. Keys in north and south sides are ordered from left to right.

Figure 6. Cycle-by-Cycle Systolic Execution of Sorting Multiple Key-Value Lists in a  $3 \times 3$  Systolic Array – PEs performing key-value sorting are annotated with letter s. PEs performing key-value compression are annotated with letter c. PEs in gray color are idle. Otherwise, the color of a PE refers to a set of rows in matrix registers that the PE is processing.

always switch inputs. Similarly, larger keys flow to the east while smaller keys flow to the south side. The compressing pass works exactly the same as in the sorting operation.

Not all input keys can be merged into the output chunk. Keys from an input chunk that are greater than all keys from the other chunk need to be excluded since we do not know yet their positions in the output stream as discussed in Section III-A. For example, in Figure 5(b), the key 9 in the west input chunk is excluded from the output chunk (x in cycle 4) since it is greater than every key from the north-side chunk. To detect keys to be excluded, each key is tagged with two extra bits to track (1) from which input side the key comes from (source bit) and (2) whether the key has been compared with another larger or equal key from the other input chunk yet (merge bit). The merge bit of a key is initially set to false and flipped to true when a PE detects a larger or equal key from the other input side. After the merging pass, if the merge bit is still false, the key is excluded from the output chunk.

Input and output counters are updated in the same way as in the sorting operation. W\_IC and N\_IC count the numbers of merged keys for the west-side and north-side input chunks respectively. E\_OC and S\_OC count the numbers of valid output keys in the east-side and south-side output chunks respectively. Instruction mszipv.tt shuffles values based on the reordering of their corresponding keys.

#### C. Merging and Sorting Key-Value Chunks across Multiple Streams

The execution of multiple micro-operations mapping to different streams can overlap in SparseZipper's systolic array. Figure 6 shows the cycle-by-cycle systolic execution of sorting key-value chunks from multiple streams. Keys and values from multiple streams are mapped to different rows in matrix registers. Input keys and values from adjacent matrix register rows enter the systolic array back-to-back in consecutive cycles since there is no data dependency between micro-operations of an instruction. There are one-cycle stalls in cycle 4 and cycle 11 since the systolic array takes one extra cycle to route data from the west and south sides at the end of a sorting pass to the east and north sides at the beginning of a compressing pass. The execution of mssortk/mszipk and mssortk/mszipv instructions in a pair can overlap. Since the latency of a micro-operation through the systolic array is fixed (i.e., 2N+1 where N is the number of PEs in a row/column of the array), the array can schedule to start the following mssortv/mszipv as soon as the top-left-corner PE finishes its last key-compressing operation (e.g., in cycle 8 in Figure 6). However, the execution of different key-value instruction pairs processing different input matrices of keyvalue data streams do not overlap to avoid overwriting the array's output counters. The counters must be read out to a vector register before the array can start executing a new keyvalue instruction pair.

## D. Hardware Changes to the Baseline Systolic Array

Figure 7 shows micro-architectural changes to support SparseZipper in the baseline systolic array specialized for dense-dense GEMM. We add a second write port to the matrix register file as the sorting and merging instructions have two output operands. Since each physical matrix register is quite large (e.g., 1KB for a  $16 \times 16$  32-bit-element matrix register), the matrix register file may consist of multiple SRAM banks, one for each physical matrix register. Therefore, adding an additional write port to the register file simply requires an extra crossbar instead of adding an extra write port to each SRAM bank which would incur significant area overheads. In order to retrieve the east-side output data from the systolic array, we add a second deskew buffer.

Additional control bits (i.e., source, duplicate, and merge bits) are tagged along with data flowing through the systolic array as described in Section IV-B. We add a three-bit control between any two PEs to the existing data paths. For routing data between a sorting/merging pass and a compressing pass,

TABLE II. BASELINE SYSTEM CONFIGURATION

| CPU         | <ul> <li>RISC-V ISA (RV64GC)</li> <li>8-way out-of-order issue</li> <li>72-entry LQ, 56-entry SQ, 96-entry IQ &amp; 224-entry ROB</li> <li>180 physical integer, 168 physical floating-point &amp; 128 physical 512-bit vector registers</li> <li>Two 512-bit-wide SIMD execution units</li> </ul> |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Matrix Unit | <ul> <li>A systolic array with 16×16 processing elements (PEs)</li> <li>Each PE has a single-precision MAC unit</li> <li>16 physical matrix registers</li> </ul>                                                                                                                                   |

| Caches      | <ul> <li>L1I cache: 8-way, 32KB &amp; 2-cycle hit latency</li> <li>L1D cache: 8-way, 32KB &amp; 2-cycle hit latency</li> <li>L2 cache: 4-way, 4-bank, 256KB &amp; 8-cycle hit latency</li> <li>LLC: 8-way, 8-bank, 512KB &amp; 8-cycle hit latency</li> </ul>                                      |

| Memory      | DDR4-2400                                                                                                                                                                                                                                                                                          |

LQ = Load queue; SQ = Store queue; IQ = Issue queue; ROB = Reorder buffer; LLC = Last-level cache; MAC = multiply-accumulate unit.

two loop-back paths are added to connect east and south output sides to the west and north input sides respectively. Each path is pipelined via an extra register to account for its long distance between two sides of the systolic array.

Four input and output vectors of N counters are added to track the number of valid input and output elements for N rows of matrix registers. Each counter counts up to N (i.e., the number of elements in a row), so a vector of N counters is  $N \times \log_2 N$  bit wide. The population counting logic uses output control signals from the systolic array and increments corresponding input/output counters.

In each PE, we slightly modify the existing adder to support comparison of input keys. An additional control unit uses the comparison outcome to make routing decisions (i.e., forwarding, switching, and combining) and route data from input to output ports by controlling the two output multiplexers. The control unit also updates the duplicate and merge bits based on the source bit and the comparison outcome. We use the same adder for adding up values for mssortv and mszipv instructions in case of combining inputs. We repurpose the weight register in each PE to store routing states. Each state requires two bits to encode. Each pair of rows from two input matrix registers needs to store two states for their sorting/merging and compressing passes. Therefore, for N pairs of rows, we need a total of  $N \times 4$  bits for all the routing states (e.g., 64 bits for a hardware vector length of 16 elements).

## V. EVALUATION METHODOLOGY

In this section, we describe our simulated systems, cyclelevel modeling methodology, and matrix datasets used to evaluate the performance of SparseZipper.

#### A. Simulated Systems

We use gem5 [5, 36, 51] to evaluate the performance of SparseZipper. We use gem5's out-of-order core and configure it to model an aggressive high-performance out-of-order Intel CPU with state-of-the-art SIMD extensions (see Table II for baseline configuration). We model two 512-bit-wide SIMD execution units integrated into the CPU pipeline with support for speculative out-of-order execution of vector instructions.

Figure 7. SparseZipper Systolic Array Micro-architecture – Components and wires added to support sparse computation are in red; popc = population counting logic;  $W_IC \& N_IC =$  west & north input counters;  $E_OC \& S_OC =$  east & south output counters.

|          | # Rows | NNZs  | Density  | Per Row     |                | Per 16 Rows |             |

|----------|--------|-------|----------|-------------|----------------|-------------|-------------|

| Matrix   |        |       |          | Avg<br>Work | Avg Out<br>NNZ | Avg<br>Work | Work<br>Var |

| p2p      | 63K    | 148K  | 3.78E-05 | 8.60        | 8.59           | 0.14K       | 2.26        |

| wiki     | 8K     | 104K  | 1.51E-03 | 547.52      | 220.70         | 8.76K       | 2.06        |

| soc      | 76K    | 509K  | 8.84E-05 | 526.09      | 271.20         | 8.48K       | 1.43        |

| ca-cm    | 23K    | 187K  | 3.49E-04 | 178.66      | 101.82         | 2.86K       | 1.35        |

| ndwww    | 326K   | 930K  | 8.76E-06 | 29.42       | 12.63          | 0.78K       | 1.30        |

| patents  | 241K   | 561K  | 9.69E-06 | 10.83       | 9.48           | 0.20K       | 1.29        |

| ca-cs    | 227K   | 1628K | 3.15E-05 | 164.38      | 72.68          | 2.63K       | 0.98        |

| email    | 37K    | 184K  | 1.37E-04 | 163.04      | 89.30          | 2.64K       | 0.88        |

| scircuit | 171K   | 959K  | 3.28E-05 | 50.74       | 30.54          | 0.81K       | 0.48        |

| bcsstk17 | 11K    | 220K  | 1.83E-03 | 445.71      | 56.58          | 7.13K       | 0.38        |

| usroads  | 129K   | 331K  | 1.98E-05 | 7.18        | 5.45           | 0.11K       | 0.31        |

| p3d      | 14K    | 353K  | 1.93E-03 | 870.85      | 218.85         | 13.93K      | 0.24        |

| cage11   | 39K    | 560K  | 3.66E-04 | 225.13      | 97.59          | 3.60K       | 0.08        |

| m133-b3  | 200K   | 800K  | 2.00E-05 | 16.00       | 15.90          | 0.26K       | 0.00        |

TABLE III. EVALUATED DATASETS

Var = coefficient variation, ratio of the standard deviation to the mean; Density = ratio of non-zero values to all values in a matrix; NNZ = number of non-zero values; Avg Out NNZ = average number of non-zero values in an output matrix row; Work = number of multiplications needed to compute one output row or one group of 16 consecutive output rows.

The simulated cache subsystem is based on the Arm AMBA 5 CHI cache model provided in gem5 [18].

**Baseline systolic array for dense-dense GEMM** – As in previous work [29], we model a systolic array with  $16 \times 16$ PEs similar in spirit to an implementation of Intel AMX in Intel Saphhire Rapids [37]. Each PE consists of a singleprecision multiply-accumulate (MAC) unit with a latency of four CPU cycles. There are 16 physical matrix registers, each storing  $16 \times 16$  32-bit data. The baseline matrix register file supports two read ports and one write port. Since matrix registers are quite large, a reasonably area-efficient physical implementation would include per-matrix-register 1r1w SRAMs and enough crossbars for supporting two concurrent read and write accesses to two different matrix registers. **Extended systolic array for SparseZipper** – We model non-speculative execution of stream sorting and merging instructions to simplify the hardware implementation. These instructions wait until they are at the head of the ROB before they are issued to the systolic array for execution. Once issued, those instructions are placed into a retirement queue and subsequent instructions can continue to commit. We model extending the matrix register file's crossbar to support the second write port. We model a latency of one CPU cycle in each PE to process one pair of input data when the PE executes the sorting and merging instructions since those instructions do not use the PE's long-latency floating-point multipler. Indexed matrix load and store instructions are broken into rowwise micro-ops that are executed by the core's load-store unit.

## **B.** SpGEMM Implementations

**Scalar SpGEMM** – We evaluate two scalar row-wise implementations of SpGEMM: *scl-array* using dense arrays [19] and *scl-hash* using a hash table with linear probing [1, 15] for accumulating intermediate non-zero values in each output matrix row. After all intermediate non-zeros are accumulated for each output row, they are sorted using a quick sort algorithm.

**Vectorized Expand-Sort-Compress (ESC) SpGEMM** – We ported a vectorized ESC implementation of SpGEMM, called *vec-radix*, from prior work [16]. The ESC algorithm was initially proposed for performing SpGEMM on GPUs [12, 53] and later adopted to vector architectures [16, 34]. In ESC, multiple output rows are processed together to increase the amount of parallelism, and the computation happens in three steps. First, in the expansion step, results of multiplications are expanded in triples of row index, column index, and value. Second, The list of triples are sorted by their row and then column indices. This sorting step is often vectorized using a fast radix sort [56]. Third, triples with duplicate keys (i.e., same row and column indices) are compressed into one entry by accumulating the values. In *vec-radix*, there is a preprocessing step that calculates the amount of work per block of output rows, determines the best block size, and allocates enough temporary space for all intermediate results in a block. Smaller block sizes limit the amount of parallelism, while larger block sizes can lead to thrashing the caches. We sweep the block size for each input matrix and report the best performing configuration.

Merge-based SpGEMM using SparseZipper - We implemented two versions of the merge-based row-wise dataflow SpGEMM using the SparseZipper ISA extension: spz and spz-rsort. In both versions, a preprocessing step calculates the amount of work for each output row to allocate enough temporary memory space for intermediate results. spz-rsort additionally sorts row indices by the amount of work calculated in the preprocessing step so that output rows with similar amount of work can be processed together. Only row indices are sorted, and the underlying matrix data is unchanged. Once all output rows are computed, they are re-ordered by their row indices. The sorting is done using a quick sort routine from the C++ standard library. In both spz and spz-rsort, the expansion phase is vectorized using the RISC-V vector extension while the merge phase is implemented using the proposed SparseZipper instructions.

## C. Matrix Datasets

We evaluate SparseZipper using matrices from SuiteSparse [14] across multiple domains such as road networks, scientific simulations, and social networks (see Table III). This collection of matrices represents a variety of sparsity levels and patterns. As in prior work [39, 50, 57], we multiply each matrix with itself. Table III reports the amount of work (i.e., the number of multiplications needed) for each output row and for each group of 16 output rows. The table also shows the avarage number of non-zeros in output matrices. The ratio of avarage work to the number of non-zeros per row shows the degree in which duplicates in a stream of intermediate non-zero values are compressed into a final stream of unique non-zero values per output row.

## VI. EVALUATION

In this section, we discuss cycle-level performance and first-order area analyses of SparseZipper architecture.

## A. Performance Evaluation

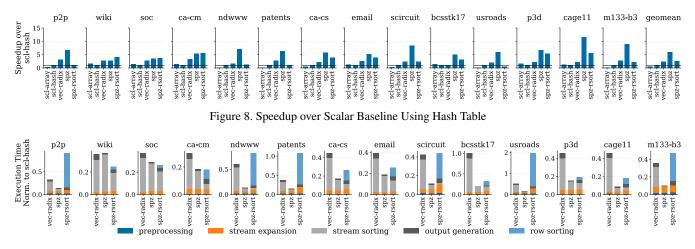

Figure 8 shows the relative performance of all SpGEMM implementations evaluated in this work. On average, *spz* achieves  $12.13 \times$ ,  $5.98 \times$ ,  $2.61 \times$  speedup over the three base-line versions *scl-array*, *scl-hash* and *vec-radix* respectively.

Scalar SpGEMM implementations – On average, *scl*hash is  $2.03 \times$  faster than *scl*-array. For matrices that have relatively sparse outputs (e.g., *p2p*, *patents*, *usroads*, and *ndwww*), using a hash table to accumulate sparse non-zero values is significantly more efficient than using dense arrays since each output matrix row has a few non-zero values (i.e., shown in the average output NNZ column in Table III). In *scl-array*, accesses to the dense array are scattered randomly, which leads to low L1 data cache hit rates (e.g., less than 20% for *ndwww*, *patents*, and *usroads*). In contrast, *scl-hash* uses much smaller hash tables that help improve significantly L1 data cache hit rates (e.g., close to 100% for *ndwww*, *patents*, and *usroads*). A hash table's size is based on the amount of work per output matrix row calculated in a preprocessing step. For matrices that have relatively dense outputs (e.g., *wiki*, *soc*, *bcsstk17*, and *p3d*), *scl-array* performs better than *scl-hash*. The main reason is that accesses to a hash table for a relatively dense output matrix cause frequent hash collisions that incur extra overheads. In addition, those relatively dense matrices are typically smaller in sizes, which helps improve the L1 cache hit rates.

**Vectorized SpGEMM implementation** – On average, *vec-radix* is  $4.65 \times$  and  $2.29 \times$  faster than *scl-array* and *scl-hash* respectively. Figure 9 shows the execution time breakdown of *vec-radix* in multiple steps. Across all matrices, the combination of stream sorting and output generation, which combines adjacent tuples with duplicate keys and generates final output matrix rows, dominates the total execution time of *vec-radix*. For *bcsstk17*, *vec-radix* is slightly worse than *scl-hash*. The main reason is that *bcsstk17* has a high ratio of per-row work to the per-row number of output non-zeros, which indicates a high number of tuples with duplicate keys finally compressed into a few non-zero values. It is relatively inefficient to sort uncompressed key-value tuples with many duplicate keys in the stream sorting step.

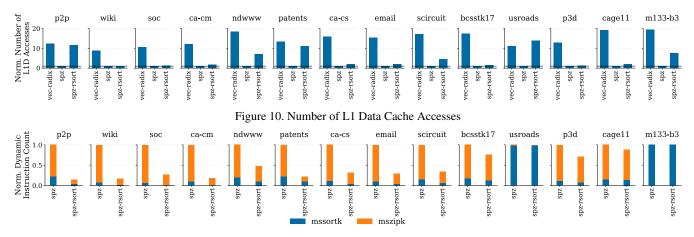

**Merge-based SpGEMM using SparseZipper** – The *spz* version is  $2.60 \times$  faster than the *vec-radix* implementation. Figure 9 shows the execution time breakdown of *spz* in multiple steps. The preprocessing and stream expansion steps in *spz* are similar to the ones in *vec-radix*. The proposed sorting and merging instructions targets to reduce the execution time of the stream sorting step which dominates the execution time of *vec-radix*. This reduction is shown in Figure 9 in almost all matrices except *wiki*. It is important to note that the execution time for output generation is decreased as well since *spz* combines tuples with duplicate keys while performing a merge sort on those tuples. This avoids a separate compression step which is part of the output generation in *vec-radix*.

One key reason for the higher performance is that *spz* loads and stores chunks of consecutive data using the proposed indexed matrix load-store instructions. Each row of a matrix register is loaded and stored using a unit-stride vector memory micro-operation that minimizes the number of cache line accesses per key-value chunk. In contrast, *vec-radix* uses a vectorized radix sort algorithm that performs both long-stride and indexed vector memory accesses that span across multiple cache lines, which results in multiple cache line accesses per vector memory instruction. Figure 10 shows the significant reduction in the number of L1 data cache accesses between *vec-radix* and *spz* across all matrices.

Since *spz* processes a group of multiple streams in lock step, any variation in lengths of those streams could impact its performance which is determined by the processing time of the longest stream in the group. Table III shows the work variation, a ratio of the work standard deviation to the work

Figure 9. Execution Time Breakdown – The *preprocessing* phase calculates per-row amount of work, divides the work into multiple row blocks (i.e., only in vec-radix), and allocates memory space for intermediate results. The *stream expansion* phase performs all multiplications and generates intermediate outputs. The *stream sorting* phase sorts and compresses the intermediate outputs (i.e., only in spz-\*).

mean, within a group of 16 consecutive matrix rows. The higher the work variation is, the more unbalanced the stream lengths of adjacent matrix rows in a group are. The relatively high work variation in *wiki* and *soc* explains the relatively low performance of *spz* compared to *vec-radix*. Although matrix p2p has the highest work variation, *spz* performs well for this matrix since the average per-row work is low. This low per-row amount of work minimizes the performance impact of high work variation since it takes, on average, one iteration to finish processing one key-value stream in p2p.

To further demonstrate the performance impact of high work variation, we sort matrix row indices by per-row amount of work in spz-rsort. It is important to note that we do not actually shuffle an input matrix's data but simply sort row indices. Rows with similar amount of work are then processed together. At the end, it is necessary to shuffle the output matrix's data based on row indices so that the final output data are sorted by their row indices. Figure 9 shows the execution breakdown of spz-rsort. By processing rows with similar amount of work together, the stream sorting time in spz-rsort is significantly reduced for matrices that have high work variation (e.g., *wiki*, *soc*, *ndww*, and *ca-cmd*). Figure 11 shows the reduction in dynamic instruction counts of mssortk and mszipk across matrices with high work variation. This reduction correlates to less number of iterations required to sort and merge key-value streams due to more balanced work across rows in a group. For cage11, spz-rsort results in a minimal reduction in the stream sorting time since it has low work variation. For usroads and m133-b3, since their average amount of work per row is less than the vector length (i.e., 16), spz and spz-rsort finish sorting each stream in one iteration on average (i.e., only a few dynamic mszipk instructions).

The row sorting and output data shuffling cause significant overheads in *spz-rsort*. Row indices are sorted by a serial quick-sort routine provided in the standard C++ library, which explains its high execution time. Future work may extend SparseZipper to include instructions that are similar to the stream merging and sorting for accelerating a standard

TABLE IV. POST-SYNTHESIS AREA ESTIMATES OF  $16 \times 16$ SparseZipper Systolic Array with 512-bit Datapath

| Component                                   | Area<br>(k µm <sup>2</sup> ) | Baseline     | Sparse<br>Zipper        |

|---------------------------------------------|------------------------------|--------------|-------------------------|

| Baseline PE (with a 32-bit MAC unit)        | 0.45                         | $\times 256$ |                         |

| SparseZipper PE (with a 32-bit MAC unit)    | 0.51                         |              | $\times 256$            |

| Skew buffer (16-lane)                       | 3.16                         | $\times 2$   | imes 2                  |

| Deskew buffer (16-lane)                     | 3.16                         | $\times 1$   | imes 2                  |

| Matrix register $(16 \times 512b)$          | 0.96                         | $\times 16$  | $\times 16$             |

| Popcount logic                              | 0.45                         |              | $\times 1$              |

| Total<br>SparseZipper vs. baseline overhead |                              | 140.16       | 158.00<br><b>12.72%</b> |

merge-sort routine that could potentially lower the row index sorting overhead. In addition, processing rows in an order different from how their data are laid out in memory causes a slight increase in the stream expansion time (e.g., in *patents* and *scircuit*) due to poor spatial locality between rows.

## B. Area Evaluation

Methodology – We use a post-synthesis component-level area modeling methodology to evaluate area overheads of hardware added to a baseline 16×16 systolic array for SparseZipper. We implement area-significant components of the systolic array in RTL and synthesize them using a 12nm standard-cell library. Each PE includes a 32-bit singleprecision floating-point MAC unit. We model control logic added to a PE to support for the stream sorting and merging operations. Each skew/deskew buffer is used to stagger input and output data coming in and going out of the systolic array. We model each skew/deskew buffer as an array of 16 shift registers using flip-flops with their sizes ranging from one to 16 entries. We model 16 rows, each is 512-bit wide ( $16 \times$ 32-bit data elements), in a SRAM-based matrix register and a total of 16 physical matrix registers. Regarding the popcount logic, we implemented an array of 16 five-bit counters (counting up to 16) and a list of counter vector registers (16  $\times$  5 bits per register).

**Area overheads of SparseZipper** – Table IV shows the detailed area comparison between SparseZipper and the base-

Figure 11. Number of Dynamic mssortk and mszipk Instructions

line using our first-order component-based area modeling methodology. In overall, a  $16 \times 16$  SparseZipper implementation adds around 12.72% area overhead compared to the baseline implementation with the same systolic array's dimensions. When considering a complete system including an out-of-order core, its vector engine, and its caches, we expect the percentage of extra area added to the baseline systolic array for supporting SparseZipper to be much lower.

#### VII. RELATED WORK

Extending systolic arrays for sparse computation -NVIDIA introduced sparse tensor cores that accelerate sparse-dense GEMM with one matrix having a specific 2:4 sparsity pattern (two zeros out of four contiguous elements) [10, 41]. VEGETA supports more flexible sparsity structure (i.e., N:4 and N:M) on a systolic array [28]. When performing sparse-dense GEMM, VEGETA keeps the sparse matrix stationary and streams the dense matrix into a systolic array. Each PE performs index matching to either skip or multiply two input values. The output matrix is stored in the dense format. Similar to SparseZipper, VEGETA is a finegrain GEMM accelerator using a matrix ISA extension. Unlike NVIDIA sparse tensor cores and VEGETA, SparseZipper targets sparse-sparse GEMM on highly sparse matrices with unstructured sparsity structures. Processing such sparsesparse GEMM using the sparse tensor core and VEGETA would require several orders of magnitude more multiplications than using a row-wise dataflow SpGEMM since matrices are highly sparse. SparseZipper complements the sparse tensor core and VEGETA by enabling efficient execution of higher unstructured sparsity.

Sparse-TPU [22] proposed an offline column packing algorithm that merges sparse columns in a matrix to minimize the number of zeros mapped to a systolic array. Sparse-TPU supports conditional execution to skip multiplications for values that do not have matching indices. However, Sparse-TPU targets only sparse-matrix dense-vector multiplication, not sparse-sparse GEMM. STA [35] proposed a new block-sparse format that targets matrices with an upper limit on the number of non-zeros in a block of elements. In contrast, SparseZipper can support unstructured sparsity structures. **Software-only proposal to accelerate SpGEMM on a systolic array** – Guo et al. proposed a software-only tiling optimization for DNN-specific SpGEMM on a systolic array [20]. Their pruning algorithm enforces a particular tilewise sparsity pattern so that dense tiles can be mapped directly to an underlying systolic array without any hardware support. However, this pruning algorithm is specific to DNN and only works for sparse matrices generated from pruned DNN models. In contrast, SparseZipper targets more general sparse matrices from various domains (e.g., graph analytics) that may not have a particular sparsity pattern.

**Coarse-grain GEMM accelerators** – Google TPU [30– 32, 52], Eyeriss [7] and Amazon AWS neuron core [3] are some examples of coarse-grain dense-dense GEMM accelerators that are highly inefficient when performing sparsesparse GEMM due to their lack of sparse format support and ability to skip ineffectual multiplications. Previous work has proposed various coarse-grain SpGEMM accelerators mainly based on three different dataflows: inner product (e.g., SIGMA [42] and Extensor [23]), outer product (e.g., OuterSparse [39] and SpArch [58]), and row-wise product (e.g., MatRaptor [50] and Gamma [57]). SparseZipper takes a more programmable approach that extends an existing matrix ISA to support both dense-dense and sparse-sparse GEMM without adding significant hardware area overhead.

**Fine-grain GEMM accelerators** – Intel AMX [26, 37], Arm SME [2], and RISC-V matrix extension proposal [47] are examples of matrix ISA extensions for accelerating densedense GEMM. RASA is an academic proposal for integrating a systolic array into an out-of-order processor for densedense GEMM [29]. SparseZipper extends such ISAs and micro-architectures to efficiently support SpGEMM. SparseCore proposed an ISA extension for sparse tensor computation by introducing stream registers and merging/intersecting instructions [44]. Unlike SparseCore adding stream registers, SparseZipper leverages existing matrix registers to store keyvalue streams. Instead of adding dedicated sparse processing units for merging key-value streams, SparseZipper minimally modifies an existing systolic array.

## VIII. CONCLUSION

This paper has demonstrated performance benefits of minimally extending a matrix ISA and a systolic array micro-architecture originally designed for dense GEMM to support SpGEMM. The SparseZipper ISA introduces new stream sorting and merging instructions to enable sorting and merging key-value streams representing sparse vectors in SpGEMM computation. SparseZipper leverages existing matrix registers to store parts of key-value streams and minimally extends a systolic array to implement the stream sorting and merging instructions. Future research can explore opportunities to add instructions specialized for certain sparsity structures (e.g., structured sparsity in deep learning workloads) and to improve the utilization of a systolic array when it performs the sorting or merging instructions.

#### REFERENCES

- P. N. Q. Anh, R. Fan, and Y. Wen. Balanced Hashing and Efficient GPU Sparse General Matrix-Matrix Multiplication. *Int'l Symp. on Supercomputing (ICS)*, Jun 2016.

- [2] Introducing the Scalable Matrix Extension for the Armv9-A Architecture. Online Webpage, 2021 (accessed Apr 2023).

- [3] NeuronCore-v2 Architecture. AWS Neuron Technical Reference Manual, 2023.

- [4] A. Azad, A. Buluç, and J. Gilbert. Parallel Triangle Counting and Enumeration Using Matrix Algebra. pages 804–811, 2015.

- [5] N. Binkert, B. M. Beckmann, G. Black, S. K. Reinhardt, A. Saidi, A. Basu, J. Hestness, D. R. Hower, T. Krishna, S. Sardashti, R. Sen, K. Sewell, M. Shoaib, N. Vaish, M. D. Hill, and D. A. Wood. The gem5 Simulator. *SIGARCH Computer Architecture News (CAN)*, 39(2):1–7, Aug 2011.

- [6] A. Canning, G. Galli, F. Mauri, A. De Vita, and R. Car. O(N) Tight-binding Molecular Dynamics on Massively Parallel Computers: an Orbital Decomposition Approach. *Computer Physics Communications*, 94(2-3):89–102, 1996.

- [7] Y.-H. Chen, T. Krishna, J. Emer, and V. Sze. Eyeriss: An Energy-Efficient Reconfigurable Accelerator for Deep Convolutional Neural Networks. *Int'l Solid-State Circuits Conf. (ISSCC)*, Feb 2016.

- [8] Y.-H. Chen, T.-J. Yang, J. Emer, and V. Sze. Eyeriss v2: A Flexible Accelerator for Emerging Deep Neural Networks on Mobile Devices. *IEEE Journal on Emerging and Selected Topics in Circuits and Systems (JETCAS)*, 9:292–308, Jun 2019.

- [9] J. Choquette, W. Gandhi, O. Giroux, N. Stam, and R. Krashinsky. Nvidia A100 Tensor Core GPU: Performance and Innovation. *IEEE Micro*, 41(2):29–35, 2021.

- [10] J. Choquette, W. Gandhi, O. Giroux, N. Stam, and R. Krashinsky. Nvidia a100 Tensor Core GPU: Performance and Innovation. *IEEE Micro*, 41(2):29–35, 2021.

- [11] P. D'alberto and A. Nicolau. R-Kleene: A High-Performance Divide-and-Conquer Algorithm for the All-Pair Shortest Path for Densely Connected Networks. *Algorithmica*, 47:203–213, 2007.

- [12] S. Dalton, L. Olson, and N. Bell. Optimizing Sparse Matrix—Matrix Multiplication for the GPU. ACM Trans. on Mathematical Software (TOMS), 41(4):1–20, 2015.

- [13] T. A. Davis. Algorithm 1000: SuiteSparse: GraphBLAS: Graph Algorithms in the Language of Sparse Linear Algebra. ACM Trans. Math. Softw., 45(4), 2019.

- [14] T. A. Davis and Y. Hu. The University of Florida Sparse Matrix Collection. ACM Trans. Math. Softw., 38(1):1:1–1:25, Dec 2011.

- [15] M. Deveci, C. Trott, and S. Rajamanickam. Multithreaded Sparse Matrix-Matrix Multiplication for Many-Core and GPU Architectures. *Parallel Computing*, 78:33–46, 2018.

- [16] V. L. Fèvre and M. Casas. Optimization of SpGEMM with RISCV-V Vector Instructions. *Computing Research Repository (CoRR)*, Mar 2023.

- [17] G. Galli. Linear Scaling Methods for Electronic Structure Calculations and Quantum Molecular Dynamics Simulations. *Current Opinion in Solid State and Materials Science*, 1(6):864–874, 1996.

- [18] Arm's AMBA 5 CHI Ruby Model in gem5. Online Webpage, accessed Nov 20, 2021.

- [19] J. R. Gilbert, C. Moler, and R. Schreiber. Sparse Matrices in MATLAB: Design and Implementation. *SIAM Journal on Matrix Analysis and Applications*, 13(1):333–356, 1992.

- [20] C. Guo, B. Y. Hsueh, J. Leng, Y. Qiu, Y. Guan, Z. Wang, X. Jia, X. Li, M. Guo, and Y. Zhu. Accelerating Sparse DNN Models Without Hardware-Support via Tile-Wise Sparsity. *Int'l Conf. on High Performance Networking and Computing (Supercomputing)*, Nov 2020.

- [21] S. Han, H. Mao, and W. J. Dally. Deep Compression: Compressing Deep Neural Networks with Pruning, Trained Quantization and Huffman Coding. *Computing Research Repository (CoRR)*, Oct 2015.

- [22] X. He, S. Pal, A. Amarnath, S. Feng, D.-H. Park, A. Rovinski, H. Ye, Y. Chen, R. Dreslinski, and T. Mudge. Sparse-TPU: Adapting Systolic Arrays for Sparse Matrices. *Int'l Symp. on Supercomputing* (*ICS*), Jun 2020.

- [23] K. Hegde, H. Asghari-Moghaddam, M. Pellauer, N. Crago, A. Jaleel, E. Solomonik, J. Emer, and C. W. Fletcher. Extensor: An accelerator for sparse tensor algebra. *Int'l Symp. on Microarchitecture (MICRO)*, Oct 2019.

- [24] T. Hoefler and M. Snir. Generic Topology Mapping Strategies for Large-scale Parallel Architectures. *Int'l Symp. on Supercomputing* (*ICS*), May 2011.

- [25] Matrix-Multiply Assist Best Practices Guide. Online Webpage, 2021 (accessed Apr 2023).

- [26] Intel Advanced Matrix Extensions Overview. Online Webpage, (accessed Apr 2023).

- [27] S. Itoh, P. Ordejón, and R. M. Martin. Order-N Tight-binding Molecular Dynamics on Parallel Computers. *Computer Physics Communications*, 88(2-3):173–185, 1995.

- [28] G. Jeong, S. Damani, A. R. Bambhaniya, E. Qin, C. J. Hughes, S. Subramoney, H. Kim, and T. Krishna. VEGETA: Vertically-Integrated Extensions for Sparse/Dense GEMM Tile Acceleration on CPUs. *Int'l Symp. on High-Performance Computer Architecture (HPCA)*, Mar 2023.

- [29] G. Jeong, E. Qin, A. Samajdar, C. J. Hughes, S. Subramoney, H. Kim, and T. Krishna. RASA: Efficient Register-Aware Systolic Array Matrix Engine for CPU. *Design Automation Conf. (DAC)*, Nov 2021.

- [30] N. Jouppi, G. Kurian, S. Li, P. Ma, R. Nagarajan, L. Nai, N. Patil, S. Subramanian, A. Swing, B. Towles, et al. TPU v4: An Optically Reconfigurable Supercomputer for Machine Learning with Hardware Support for Embeddings. *Int'l Symp. on Computer Architecture* (ISCA), Jun 2023.

- [31] N. P. Jouppi, D. H. Yoon, G. Kurian, S. Li, N. Patil, J. Laudon, C. Young, and D. Patterson. A Domain-Specific Supercomputer for Training Deep Neural Networks. *Communications of the ACM*, 63(7):67–78, Jul 2020.

- [32] N. P. Jouppi, C. Young, N. Patil, D. Patterson, G. Agrawal, R. Bajwa, S. Bates, S. Bhatia, N. Boden, A. Borchers, et al. In-datacenter Performance Analysis of a Tensor Processing Unit. *Int'l Symp. on Computer Architecture (ISCA)*, Jun 2017.

- [33] G. Karypis, A. Gupta, and V. Kumar. A Parallel Formulation of Interior Point Algorithms. pages 204–213, 1994.

- [34] J. Li, F. Wang, T. Araki, and J. Qiu. Generalized Sparse Matrix-matrix Multiplication for Vector Engines and Graph Applications. *IEEE/ACM Workshop on Memory Centric High Performance Computing (MCHPC)*, Nov 2019.

- [35] Z.-G. Liu, P. N. Whatmough, and M. Mattina. Systolic Tensor Array: An Efficient Structured-Sparse GEMM Accelerator for Mobile CNN Inference. *Computer Architecture Letters (CAL)*, 19(1):34–37, 2020.

- [36] J. Lowe-Power, A. M. Ahmad, A. Akram, M. Alian, R. Amslinger, M. Andreozzi, A. Armejach, N. Asmussen, B. Beckmann, S. Bharadwaj, G. Black, G. Bloom, B. R. Bruce, D. R. Carvalho, J. Castrillon, L. Chen, N. Derumigny, S. Diestelhorst, W. Elsasser, C. Escuin, M. Fariborz, A. Farmahini-Farahani, P. Fotouhi, R. Gambord, J. Gandhi, D. Gope, T. Grass, A. Gutierrez, B. Hanindhito, A. Hansson, S. Haria, A. Harris, T. Hayes, A. Herrera, M. Horsnell, S. A. R. Jafri, R. Jagtap, H. Jang, R. Jeyapaul, T. M. Jones, M. Jung, S. Kannoth, H. Khaleghzadeh, Y. Kodama, T. Krishna, T. Marinelli, C. Menard, A. Mondelli, M. Moreto, T. Mück, O. Naji, K. Nathella, H. Nguyen, N. Nikoleris, L. E. Olson, M. Orr, B. Pham, P. Prieto, T. Reddy, A. Roelke, M. Samani, A. Sandberg, J. Setoain, B. Shingarov, M. D. Sinclair, T. Ta, R. Thakur, G. Travaglini, M. Upton, N. Vaish, I. Vougioukas, W. Wang, Z. Wang, N. Wehn, C. Weis, D. A. Wood, H. Yoon, and Éder F. Zulian. The gem5 Simulator: Version 20.0+. arXiv preprint

- [37] N. Nassif, A. O. Munch, C. L. Molnar, G. Pasdast, S. V. Lyer, Z. Yang, O. Mendoza, M. Huddart, S. Venkataraman, S. Kandula, et al. Sapphire Rapids: The Next-generation Intel Xeon Scalable Processor. *Int'l Solid-State Circuits Conf. (ISSCC)*, Feb 2022.

arXiv:2007.03152, 2020.

- [38] M. Naumov, D. Mudigere, H.-J. M. Shi, J. Huang, N. Sundaraman, J. Park, X. Wang, U. Gupta, C.-J. Wu, A. G. Azzolini, et al. Deep Learning Recommendation Model for Personalization and Recommendation Systems. *Computing Research Repository (CoRR)*, May 2019.

- [39] S. Pal, J. Beaumont, D.-H. Park, A. Amarnath, S. Feng, C. Chakrabarti, H.-S. Kim, D. Blaauw, T. Mudge, and R. Dreslinski. OuterSPACE: An Outer Product Based Sparse Matrix Multiplication Accelerator. Int'l Symp. on High-Performance Computer Architecture (HPCA), Feb 2018.

- [40] G. Penn. Efficient Transitive Closure of Sparse Matrices over Closed Semirings. *Theoretical Computer Science*, 354(1):72–81, 2006.

- [41] J. Pool, A. Sawarkar, and J. Rodge. Accelerating Inference with Sparsity Using the NVIDIA Ampere Architecture and NVIDIA TensorRT. NVIDIA Technical Report, 2021.

- [42] E. Qin, A. Samajdar, H. Kwon, V. Nadella, S. Srinivasan, D. Das, B. Kaul, and T. Krishna. SIGMA: A Sparse and Irregular GEMM Accelerator with Flexible Interconnects for DNN Training. *Int'l Symp. on High-Performance Computer Architecture (HPCA)*, Feb 2020.

- [43] M. O. Rabin and V. V. Vazirani. Maximum Matchings in General Graphs through Randomization. *Journal of algorithms*, 10(4):557–567, 1989.

- [44] G. Rao, J. Chen, J. Yik, and X. Qian. SparseCore: Stream ISA and Processor Specialization for Sparse Computation. Int'l Conf. on

Architectural Support for Programming Languages and Operating Systems (ASPLOS), Feb 2022.

- [45] V. J. Reddi, C. Cheng, D. Kanter, P. Mattson, G. Schmuelling, C.-J. Wu, B. Anderson, M. Breughe, M. Charlebois, W. Chou, et al. MLPerf Inference Benchmark. *Int'l Symp. on Computer Architecture* (ISCA), Jun 2020.

- [46] RISC-V Vector Extension (Version 0.10). Online Webpage, 2021.

- [47] RISC-V Matrix Extension Specification Proposal. Online Webpage, (accessed Apr 2023).

- [48] V. B. Shah. An Interactive System for Combinatorial Scientific Computing with an Emphasis on Programmer Productivity. University of California, Santa Barbara, 2007.

- [49] J. Shun and K. Tangwongsan. Multicore triangle computations without tuning. Int'l Conf. on Data Engineering (ICDE), Apr 2015.

- [50] N. Srivastava, H. Jin, J. Liu, D. Albonesi, and Z. Zhang. MatRaptor: A Sparse-Sparse Matrix Multiplication Accelerator Based on Row-Wise Product. *Int'l Symp. on Microarchitecture (MICRO)*, Oct 2020.

- [51] T. Ta, L. Cheng, and C. Batten. Simulating Multi-Core RISC-V Systems in gem5. Workshop on Computer Architecture Research with RISC-V, 2018.

- [52] P. Tiech. Under the Hood of Google's TPU2 Machine Learning Clusters. Online Article, May 2017 (accessed Feb 2020).

- [53] M. Winter, D. Mlakar, R. Zayer, H.-P. Seidel, and M. Steinberger. Adaptive Sparse Matrix-matrix Multiplication on the GPU. *Symp. on Principles and practice of Parallel Programming (PPoPP)*, Feb 2019.

- [54] C.-J. Wu, D. Brooks, K. Chen, D. Chen, S. Choudhury, M. Dukhan, K. Hazelwood, E. Isaac, Y. Jia, B. Jia, et al. Machine Learning at Facebook: Understanding Inference at the Edge. *Int'l Symp. on High-Performance Computer Architecture (HPCA)*, Mar 2019.

- [55] I. Yamazaki and X. S. Li. On Techniques to Improve Robustness and Scalability of a Parallel Hybrid Linear Solver. pages 421–434, 2010.

- [56] M. Zagha and G. E. Blelloch. Radix Sort for Vector Multiprocessors. Int'l Conf. on High Performance Networking and Computing (Supercomputing), 1991.

- [57] G. Zhang, N. Attaluri, J. S. Emer, and D. Sanchez. Gamma: Leveraging Gustavson's Algorithm to Accelerate Sparse Matrix Multiplication. *Int'l Conf. on Architectural Support for Programming Languages and Operating Systems (ASPLOS)*, Apr 2021.

- [58] Z. Zhang, H. Wang, S. Han, and W. J. Dally. SpArch: Efficient Architecture for Sparse Matrix Multiplication. *Int'l Symp. on High-Performance Computer Architecture (HPCA)*, Feb 2020.