# Fat-Tree QRAM: A High-Bandwidth Shared Quantum Random Access Memory for Parallel Queries

## Shifan Xu

Yale Quantum Institute Yale University New Haven, CT, USA shifan.xu@yale.edu

## Alvin Lu

Yale Quantum Institute Yale University New Haven, CT, USA alvin.lu@yale.edu

# Yongshan Ding

Yale Quantum Institute Yale University New Haven, CT, USA yongshan.ding@yale.edu

## **Abstract**

Quantum Random Access Memory (QRAM) is a crucial architectural component for querying classical or quantum data in superposition, enabling algorithms with wide-ranging applications in quantum arithmetic, quantum chemistry, machine learning, and quantum cryptography. In this work, we introduce Fat-Tree QRAM, a novel query architecture capable of pipelining multiple quantum queries simultaneously while maintaining desirable scalings in query speed and fidelity. Specifically, Fat-Tree QRAM performs  $O(\log(N))$ independent queries in  $O(\log(N))$  time using O(N) qubits, offering immense parallelism benefits over traditional QRAM architectures. To demonstrate its experimental feasibility, we propose modular and on-chip implementations of Fat-Tree ORAM based on superconducting circuits and analyze their performance and fidelity under realistic parameters. Furthermore, a query scheduling protocol is presented to maximize hardware utilization and access the underlying data at an optimal rate. These results suggest that Fat-Tree QRAM is an attractive architecture in a shared memory system for practical quantum computing.

CCS Concepts: • Computer systems organization  $\rightarrow$  Quantum computing; • Hardware  $\rightarrow$  Quantum technologies.

*Keywords:* Quantum Computing, Quantum Random Access Memory

#### **ACM Reference Format:**

Shifan Xu, Alvin Lu, and Yongshan Ding. 2025. Fat-Tree QRAM: A High-Bandwidth Shared Quantum Random Access Memory for Parallel Queries. In Proceedings of the 30th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 2 (ASPLOS '25), March 30–April 3, 2025, Rotterdam, Netherlands. ACM, New York, NY, USA, 17 pages. https://doi.org/10.1145/3676641.3716256

This work is licensed under a Creative Commons Attribution-NonCommercial 4.0 International License.

ASPLOS '25, Rotterdam, Netherlands.

© 2025 Copyright held by the owner/author(s). ACM ISBN 979-8-4007-1079-7/2025/03

https://doi.org/10.1145/3676641.3716256

#### 1 Introduction

Many quantum algorithms for solving classically intractable problems assume that a large classical or quantum memory can be queried in superposition. Bucket-Brigade Quantum Random Access Memory (BB QRAM) [20] is a promising candidate for realizing such queries efficiently, achieving desirable (poly-)logarithmic scalings in query latency and infidelity relative to the memory size [22]. Recent resource estimates have revealed that QRAM's utility in quantum algorithms varies depending on the input data size and algorithmic speedup. For instance, a quadratic speedup in Grover's algorithm [21] for database search is insufficient to realize a practical quantum advantage [26, 28]. However, ORAM remains central to enabling quantum advantages in many algorithms like the qubitization algorithm for chemistry simulation [4, 32, 55], Harrow-Hassidim-Lloyd algorithm for solving systems of equations and machine learning [6, 25], and variants of Shor's algorithm for prime factorization [18, 54].

Running these quantum algorithms is challenging due to their demanding resource requirements, including large numbers of qubits with long coherence times. Specifically, these algorithms are inherently sequential—they make serial QRAM queries and consequently require deep circuits. These challenges can be alleviated through a parallel processing approach. Motivated by the ubiquitous use of parallelism in classical computation, numerous parallel quantum algorithms have recently emerged. Examples include distributed variational quantum eigensolver (VQE) [49], distributed Shor's algorithm [42], distributed quantum phase estimation (QPE) [3, 38], parallel quantum walk [64], and parallel quantum signal processing (QSP) [40]. The success of many parallel algorithms critically depends on high-bandwidth QRAM capable of supporting simultaneous queries.

In tandem with algorithmic advances, tremendous hardware progress has been made towards realizing QRAM. Multiple platforms have successfully demonstrated fast and high-fidelity controlled-SWAP (CSWAP) gates, a critical native operation in QRAM [17, 33, 60]. Experimental QRAM prototypes have been proposed based on quantum optics [29], Rydberg atoms [51], photonics [11], and circuit quantum acoustodynamics [24], and superconducting cavities [56]. Yet, one of the most substantial limitations of QRAM is the

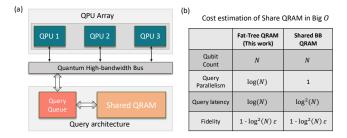

**Figure 1.** (a) Architectural schematics of a shared QRAM that is concurrently accessed by multiple QPUs. (b) Cost comparison between Fat-Tree and Bucket-Brigade (BB) QRAMs for executing  $O(\log(N))$  independent queries. The proposed Fat-Tree QRAM allows  $O(\log(N))$  queries to be executed in parallel while maintaining desirable asymptotic scalings, including O(N) qubit count,  $O(\log(N))$  total latency (i.e., circuit depth), and  $O(\log^2(N)\varepsilon)$  infidelity.

large number of qubits required for practically relevant problems, typically O(N) qubits for a size-N memory. This issue can be mitigated by a shared memory approach, where multiple quantum processing units (QPUs) share QRAM resources to improve utilization, as illustrated schematically in Fig. 1(a). For example, recent proposals for quantum data centers (QDC) [35-37] have highlighted the utility of a shared QRAM system for quantum applications including multiparty private communication and quantum sensing [35]. This shared ORAM model [1] also aligns well with the technology trends towards distributed or multi-core quantum computing, where multiple users can access shared quantum systems via cloud. Meanwhile, the emerging modular approach of building complex quantum systems from smaller modules also provides hardware support for such large-scale quantum computing architectures [7, 30, 44]. However, existing QRAM architectures, such as the BB QRAM, have extremely poor performances under contention. That is, a single query occupies all O(N) quantum routers for the entire duration of the query. Consequently, queries must be queued and executed sequentially.

In this work, we introduce a novel shared QRAM architecture that pipelines multiple independent queries simultaneously while preserving the qubit number and query fidelity scalings of a BB QRAM. We term this design "Fat-Tree QRAM," as the organization of the quantum routers resembles a Fat-Tree [34] that is commonly seen in classical computing and networking systems.

Fat-Tree QRAM architecture pipelines O(log(N)) independent queries to a size-N memory in O(log(N)) time using O(N) qubits (Fig. 1(b)). This approach provides a scalable path towards building a hardware-efficient, high-bandwidth quantum shared memory system.

- We consider both modular and on-chip implementations of the Fat-Tree QRAM architecture using superconducting cavities. While our QRAM design can be generalized to any technology platform that supports native CSWAP operations, we demonstrate that Fat-Tree QRAM can be efficiently implemented despite restrictive connectivity constraints in superconducting platforms

- We analyze the optimal query scheduling/pipelining protocol that resolves resource contention and maximizes utilization and throughput for parallel queries.

We discuss the benefits of such parallelism in the context of parallel quantum algorithms and parallel execution of multiple quantum algorithms.

- Of great interests from an experimental standpoint are the new metrics we introduced to benchmark shared QRAM architectures, including QRAM bandwidth, spacetime volume per query, hardware utilization, and memory access rate.

Our paper is organized as follows. Sec. 2 reviews current noisy intermediate-scale quantum (NISQ) machines and state-of-the-art quantum random access memory architectures. In Sec. 3 and Sec. 4, we explore quantum shared memory systems by introducing the hardware architecture of Fat-Tree QRAM with detailed implementations based on superconducting circuits. In Sec. 5, we provide a scheduling protocol to maximize the utilization of Fat-Tree QRAM. In Sec. 6 and Sec. 7, we evaluate the performance of the Fat-Tree QRAM for both real-world parallel quantum algorithms and synthetic algorithms. We conclude with a brief discussion on the implication of these results for large-scale quantum computing.

## 2 Background

## 2.1 Emerging Quantum Hardware and Software

Quantum algorithms have been shown to provide polynomial or super-polynomial speedups against their best-known classical counterparts on special computational tasks, ranging from quantum chemistry simulations [4, 32, 55] to quantum cryptography [18, 54]. Many of these algorithms, however, rely on the existence of a quantum random access memory (QRAM) device to efficiently query classical or quantum data in superposition, coupled with a quantum processing unit (QPU) with sufficient system size to process the queried data efficiently and fault tolerantly. For example, a classically intractable problem of scientific or industry interests is expected to require hundreds of thousands of high-fidelity qubits [5, 18].

In recent years, many physical architecture platforms have demonstrated high-quality control over tens or hundreds of qubits. Due to various constraints including connectivity, power, and wiring, it is challenging to scale up these systems as a single monolithic quantum processor. These constraints

**Figure 2.** (a) Querying a Bucket-Brigade (BB) QRAM with capacity N = 8 takes 25 circuit layers. A detailed step-by-step procedure can be found in Appendix A.1. The circuit layer number indicates the *finishing* time of each stage. (b) Each quantum router in the BB QRAM involves CSWAP operations between the router qubit and the data qubits. (c) H-tree layout of a BB QRAM. Quantum routers are organized in a binary tree structure, where classical data are located at the leaves. Dashed lines indicate external address and bus qubits that are used to query the QRAM. Figure (c) represents the QRAM state after all address qubits have been loaded, corresponding to circuit layer 15 in (a).

can be mitigated by a *modular* approach, where small units of special-purpose devices are linked together to form a single quantum processor [1, 41, 44, 46]. This modular approach (both in hardware and software) can also simplify manufacturing, control, and maintenance. For example, in superconducting quantum computers, tunable couplers can be connected to bendable cryogenic microwave cables to mediate cross-chip interactions between remote qubits from separate modules. The flexibility of the microwave links allows the system's connectivity to extend beyond planar layouts. More compact on-chip designs have also been demonstrated, but typically have stricter topology constraints to avoid crossing inter-connecting wires. Multi-layer die stacks can alleviate this challenge but require vertical connection using Through-Silicon-Vias (TSVs) [8, 15, 53, 62].

The rapid increment of available qubits and advances in scalable architectures also facilitate the development of quantum algorithms. For example, running multiple algorithms in shared hardware makes it possible for IBM's 1000+ qubit machine to increase hardware utilization [14]. Meanwhile, many quantum algorithms benefit from the novel distributed or multi-core quantum computing architectures, dramatically improving resource efficiency and overall performance [9, 57].

## 2.2 Quantum Queries

A quantum random access memory implements a quantum query by accessing (classical) memory at multiple addresses in superposition. It realizes the following unitary operation:

$$\sum_{i=0}^{N-1} \alpha_i |i\rangle_{\mathcal{A}} |0\rangle_{\mathcal{B}} \xrightarrow{\text{Query}} \sum_{i=0}^{N-1} \alpha_i |i\rangle_{\mathcal{A}} |x_i\rangle_{\mathcal{B}}$$

(1)

where  $|\cdot\rangle_A$   $(|\cdot\rangle_B)$  is the address (bus) qubit register storing the input (output),  $x_i$  is the data value stored at address i, and  $\alpha_i$  is the superposition amplitude of address i. N is the size of the memory (or QRAM capacity). The number of address and bus qubits, |A| and |B| respectively, are termed the *address*

width and bus width. For the remainder of the paper, we will assume  $|A| = \log(N)$  and |B| = 1.

**2.2.1 Overview of Bucket-Brigade QRAM.** We consider BB QRAM, one of the leading quantum query architectures, proposed by Giovannetti et al. in 2008 [19, 20]. BB QRAM implements a quantum query to a memory of size N in  $O(\log(N))$  time (i.e., circuit layer [2], which is defined as one logical circuit step where all quantum gates inside the same layer are executed in parallel). BB QRAM is also proven to exhibit superior noise resilience than other architectures, including Fanout QRAM [47] and Select-Swap QRAM [39].

The basic building block of a BB QRAM is a *quantum router*. Shown in Fig. 2(b), a quantum router consists of two CSWAP gates acting on four qubits. The two CSWAP gates route an input qubit to either the left or right output qubits in a superposition based on the quantum state of the router qubit which takes one of three states:  $|W\rangle$  inactive "wait" state routes trivially,  $|0\rangle$  routes left, and  $|1\rangle$  routes right. BB QRAM recursively concatenates quantum routers initialized to  $|W\rangle$  in a binary tree structure. Fig. 2(c) shows BB QRAM in a 2D H-Tree layout [19, 59].

**2.2.2 Query Procedure in BB QRAM.** We define four main operations for BB QRAM routers: LOAD (L) qubit through escape, TRANSPORT (T) to next router, ROUTE (R) in current router, and STORE (S) into router qubit. Detailed definitions for each can be found in Appendix A.1.

Using the four operations, BB QRAM realizes quantum queries in three stages: address loading, data retrieval, and address unloading. In address loading, each  $i^{\rm th}$  address qubit is LOADed through the escape and then routed to the  $i^{\rm th}$  level of the tree by a series of alternating ROUTE and TRANSPORT operations. The specific path is controlled by the previously routed address qubits stored in higher levels of the tree. Once an address qubit is at the right level, it is STOREd into the routers. Note that each address qubit can be loaded and begin routing before the previous address qubit has been stored

since the beginning of the path is independent of the last address qubit; this "bit-level pipelining" (to distinguish from "query-level pipelining" introduced by this paper in later sections) reduces the total latency through quantum parallelism. After address loading, the fully loaded QRAM stores a superposition of different addresses, where each address activates a distinct root-to-leaf path that is unentangled with the other routers in the  $|W\rangle$  state (important for maintaining fidelity).

In the data retrieval stage, the bus qubit is routed to the leaves of the QRAM tree in a procedure similar to address loading (also as part of the "bit-level pipeline", i.e., loaded before the last address qubit is stored). All classical memory are copied in parallel to modify the "delocalized bus qubit" at the leaves of the QRAM tree. Finally, the bus qubit is routed out of the tree, and the routers are reverted to an all- $|W\rangle$  state through uncomputation, which follows the same steps as address loading but in reverse. A step-by-step description and instruction set can be found in Appendix A.1.

The inherent parallelism in executing both quantum gates and classical queries ensures the BB QRAM has an  $O(\log(N))$  latency for address loading (4 circuit layers for storing each address qubit and routing the bus), an O(1) latency for data retrieval (though also a single circuit layer, it is much faster than other gates in practice), and an overall  $O(\log(N))$  query latency. We provide a visual description of the query procedure of BB QRAM in Fig. 2(a) and a more detailed version in Appendix A.1.

It has been shown that BB QRAM has intrinsic noise resilience, due to limited entanglement among different paths and restricted propagation of errors. The infidelity of a query is proven to be upper bounded by  $O(\epsilon \log^2(N))$ , where  $\epsilon$  is the error rate of each operation and N is the size of the memory [23]. Such superior infidelity scaling makes BB QRAM a particularly attractive candidate for implementation before the era of fault tolerance.

## 3 Challenges and Motivation

Despite its speed and fidelity advantages for completing a single query, BB QRAM is not capable of processing multiple queries in parallel. This limitation is intrinsic to the binary tree structure of the QRAM architecture. For example, the 0<sup>th</sup> address qubit is routed into the tree and occupies the root node for the entire duration of the query. In a binary tree structure, the root node serves as the sole escape route (i.e., external interface) through which every address qubit must pass. Consequently, all queries must be queued and executed sequentially.

In a shared memory system, as illustrated in Fig. 1, a BB QRAM inevitably leads to *resource contention*. When p parallel processes attempt to query the shared memory, BB QRAM must to execute them sequentially. This lack of query parallelism leads to a total query latency of  $O(p\log(N))$ , potentially causing a slowdown in quantum algorithms. Motivated

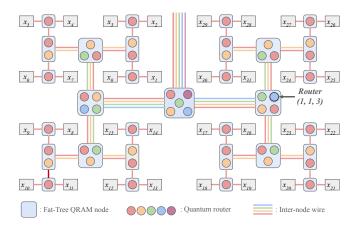

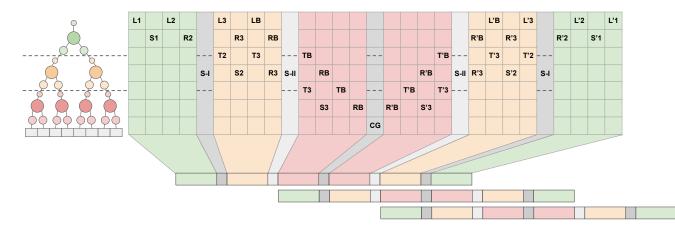

**Figure 3.** Layout of a Fat-Tree QRAM with capacity N=32 (Similar H-tree layout for BB QRAM appeared in [59]). Classical data are located at the leaves and the internal nodes contain multiplexed quantum routers. Colors of the routers and wires are used to indicate connection. The size of an internal node (i.e., number of qubits) increases *linearly* as we go up the tree.

by advancements in parallel computing and networking in classical literature, we propose an alternative router-based QRAM architecture based on a Fat-Tree structure, similar to the Fat-Tree network initially proposed by Charles Leiserson in 1985 [34]. Indeed, Fat-Tree QRAM routes differently than a classical Fat-Tree network [34], despite their similarity in geometry. A useful conceptual picture is that qubits are routed from root to leaf in QRAM, as opposed to communicating among leaf memory cells. With only a moderate (i.e., small constant factor) increase in the number of qubits in quantum routers at the higher levels of the tree, we can pipeline multiple queries simultaneously, offering immense parallelism benefits to a shared memory system.

## 4 Shared QRAM Architecture

We introduce the new Fat-Tree QRAM architecture in the following three subsections: Sec. 4.1 describes a Fat-Tree architecture to increase the query parallelism. Sec. 4.2 provides both modular and on-chip hardware demonstrations of Fat-Tree QRAM using well-established techniques in NISQ systems. Finally, operations within the architecture and the query pipeline diagram are presented in Sec. 4.3.

#### 4.1 Fat-Tree Architecture

Fat-Tree QRAM is built on a complete binary tree, where N leaf nodes connect to size-N classical memory. Each tree level consists of quantum routers, with the  $i^{\rm th}$  level (indexed from 0) containing  $2^i$  routers, as in BB QRAM. To pipeline  $n = \log(N)$  queries with address width n, routers at level i are duplicated n-i-1 times. Thus, Fat-Tree QRAM adopts a 2D H-tree layout similar to BB QRAM, replacing each router

at level i with a Fat-Tree node containing n-i routers. Fig. 3 illustrates this structure, where circles inside square nodes denote quantum routers.

We use a 3-tuple (i, j, k) to index routers and qubits:  $i \in [0, n-1]$  represents the level,  $j \in [0, 2^i-1]$  denotes the node index, and  $k \in [0, n-i-1]$  identifies the router copy in node (i, j). In BB QRAM, routers correspond to (i, j, n-1). The parameter k determines multiplexing, extending BB QRAM into the Fat-Tree model. Individual qubits within each router are categorized as input, router, and L/R output qubits (e.g., the input qubit of router (1, 1, 3) in Fig. 3).

Increased router duplication raises inter-node connectivity. BB QRAM links parent-child nodes with a single wire (Fig. 2), whereas Fat-Tree QRAM connects nodes with k wires per node. Starting with n wires at the root, the count decreases by 1 per level until reaching a single wire at the leaves, matching BB QRAM. This enhanced connectivity enables higher-bandwidth inter-node communication and multiple parallel gates between nodes.

As discussed in Sec. 3, the resource overhead from duplicating higher BB QRAM levels remains moderate. The qubit count per Fat-Tree node scales *linearly* with its height. The router count follows  $\sum_{i=0}^{n-1} (n-i)2^i = 2N-2-n$ , only doubling that of BB QRAM. The following sections demonstrate that Fat-Tree QRAM significantly improves parallel query latency over sequential BB QRAM queries, with minimal qubit and connectivity overhead.

#### 4.2 Implementing Fat-Tree QRAM Nodes

When choosing a hardware platform for implementing QRAM, we need to consider several essential requirements: (i) efficient encoding of quantum router (e.g.,  $|W\rangle$ ,  $|0\rangle$ ,  $|1\rangle$ ), (ii) parallel routing operations (e.g., SWAP and CSWAP gates), (iii) parallel writing of classical data into the state of the bus.

In this section, we consider implementing a multiplexed Fat-Tree node (i, j) based on superconducting cavities. With rapid advances in superconducting devices, the key elements required in Fat-Tree QRAM have already been proposed, e.g., CSWAP operations between superconducting cavities [17, 60] and transmon devices [43]. These advances in hardware enable two possible hardware implementations of QRAM, using well-established encodings of qubits (i.e., transmons and cavities), beam-splitters, wires, and tunable couplers.

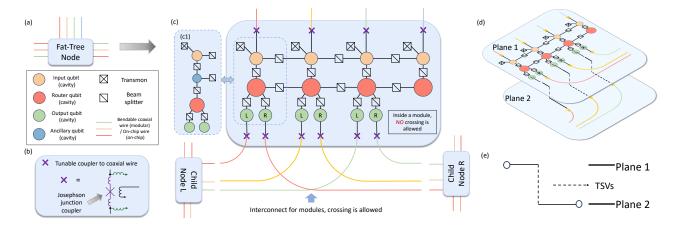

For Fat-Tree QRAM, it is important to also consider the intra- and inter-node connectivity caused by the extra routers. For example, in Fig. 4(c), we provide the internal structure of node (1, j) in a capacity-N = 32 Fat-Tree QRAM from Fig. 3. In this node, there are four routers, each with four input wires and two sets of three output wires allocated to both child nodes, denoted as L and R. When multiple routers are positioned in a Fat-Tree node, the two output qubits from each router must be routed towards the two external output interfaces (i.e., L and R directions), resulting in possible wire crossings. However, the connectivity constraint

for Fat-Tree QRAM is *not* all-to-all. Instead, we show that a *bi-planar nearest-neighbor* connectivity is sufficient. This important observation leads to the efficient implementations of Fat-Tree QRAM using readily available technologies in superconducting circuits, one of the platforms with the most restrictive connectivity constraints. We illustrate this by introducing modular and on-chip architectures for Fat-Tree nodes.

4.2.1 Fat-Tree Node: Modular Implementation. The modular implementation allows us to manufacture all the nodes as independent modules and link them with superconducting coaxial cables [65]. Fig. 4 proposes a possible implementation consisting of two fundamental components: (1) tunable couplers with coaxial wires to provide inter-node connectivity and (2) quantum routers inside the module for executing CSWAP gates. Within the module, routers are arranged side by side, with the last router lacking output qubits and serving as a transient storage for queries, resulting in one fewer output wires compared to inputs. Within each quantum router, qubits are constructed by cavities, featuring a transmon coupled to the input cavity for native CSWAP gates implementation [10, 56]. Additionally, horizontal nearestneighbour connectivity among routers is implemented by beam splitters, enabling swap gates between adjacent routers within Fat-Tree nodes via manipulation of nearest-neighbor coupled qubits along the line. Since the router qubit having four beam splitters attached may cause hardware manufacturing challenges, we provide an alternative implementation to reduce connectivity requirements by adding one extra cavity in Fig. 4(c1).

The tunable couplers are aligned to the top and bottom of the chip, coupled with the input and output qubits as ports to inter-node wires. Since the coaxial wires can be twisted to any shape, the crossing of routings inside a node is reduced to the crossing of wires connecting different nodes, with no crossings inside the module, as shown in Fig. 4.

4.2.2 Fat-Tree Node: On-chip Implementation. In contrast to modular designs, an on-chip implementation of shared ORAM integrates all components onto a single chip, resulting in a significantly reduced size. This approach offers multiple advantages, including faster cooling, reduced energy dissipation, and enhanced fidelity, at the expense of connectivity constraints [16]. Instead, qubits and wires must be arranged in a planar layout without overlapping. While achieving this in a single-layer chip poses challenges, we demonstrate that the connectivity graph of a Fat-Tree QRAM can be effectively decomposed into two planar subgraphs. Consequently, a thickness-2 chip, consisting of two edge-disjoint layers, can be implemented, as shown in Fig. 4(d). Although a singlelayer chip is preferable for hardware simplicity, employing two layers may still be feasible, as couplers and their control lines can be attached to the top and bottom of the chip. The

**Figure 4.** Internal structure of a Fat-Tree node. (a) An example node (i = 1, j = 0) in a capacity-32 Fat-Tree QRAM, containing 4 routers, 4 incoming wires from the top, and two sets of 3 outgoing wires to its left and right children. (b) A tunable coupler to coaxial wire for inter-node connections in modular design (Sec. 4.2.1). (c) The internal structure of a multiplexed router based on superconducting cavities. Transmon-attached input qubit and router qubit ensure native (cavity-controlled) CSWAP gate implementation [56]. Beam splitters between routers provide intra-node connectivity for local swapping operations. (Sec. 4.3) Inset (c1) is an alternative implementation of the router unit enclosed in dashed box that uses more cavities to reduce the connectivity requirement. (d) On-chip two-layer architecture for Fat-Tree QRAM. (Sec. 4.2.2) (e) Sectional view of on-chip design in (d). Inter-plane connection is achieved by the Through-Substrate-Vias (TSVs) technology.

**Figure 5.** An alternative conceptual interpretation of Fat-Tree QRAM as a composition of multiple BB QRAMs of variable size (Sec. 4.3).

connection between the two planes can be facilitated with the TSVs technique introduced in Sec. 2.

Fig. 4(e) depicts a sectional view of the on-chip TSVs implementation with the vertical dashed line between the two planes. A single node, implemented by the routers and couplers discussed in the modular design, resides fully in a single plane. However, only one of its child nodes resides in the same plane, while the other resides in the opposite, as the L/R output qubits of quantum routers direct to the chip's opposite/same plane respectively. This alternating plane configuration ensures that wires do not intersect within any single plane, providing an efficient two-plane decomposition.

#### 4.3 Operations in Fat-Tree QRAM

With the hardware architecture defined, we now describe the efficient operations in Fat-Tree QRAM to implement quantum queries. In this section, we specify the step-by-step inter- and intra-node operations in Fat-Tree QRAM to realize  $O(\log(N))$  quantum queries in  $O(\log^2(N))$  circuit depth.

To appreciate the benefits of the proposed architecture, it is useful to consider an alternative interpretation of Fat-Tree QRAM. As shown in Fig. 5, if we look at the routers of different colors in isolation, a Fat-Tree QRAM is equivalent to a composition of multiple "sub-component QRAMs" of varying sizes (each with address width ranging from n to 1, which we denote by parameter k). Fig. 5 shows the largest QRAM corresponding to k = n - 1, while the smallest is parameterized by k = 0. In the Fat-Tree, we index routers belonging to QRAM k as (i, j, k), where each node (i, j) in Fat-Tree incorporates exactly one router from QRAM k if  $i \le k$ , and no router if i > k.

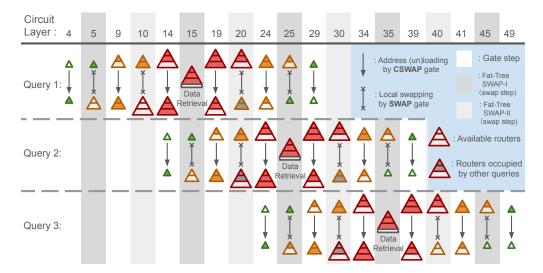

Each quantum query involves routing and swapping among the sub-component QRAMs: starting from the smallest-size QRAM at the initial step of the query, we transition to the QRAM larger by one size every time a level of routers is loaded. This can be realized by introducing a *swap step* between consecutive *gate steps* within the original QRAM circuit, as illustrated in Fig. 6.

In Fig. 6, the gate steps, highlighted in a white background, load/unload a single layer in the QRAM through a series of CSWAPs, the same as those in a conventional BB QRAM address loading circuit, taking 4 circuit layers each. Meanwhile, the newly introduced swap steps, on a gray background, perform two distinct functions: (i) During the address loading (unloading) stage, the entire query is swapped to a larger (smaller) sub-component QRAM, taking a single circuit layer. All swap gates can be performed in parallel within a Fat-Tree node. (ii) Data retrieval operations are executed during a swap step as well. Data retrieval, similar to in BB QRAM,

takes 1 circuit layer for the classically controlled gates. However, in practice, each circuit layer in a swap step takes only a fraction of the time as other circuit layers since intra-node and classical gates are much faster.

For Fat-Tree QRAM, additional time for swapping classical memory might be required for executing multiple distinct queries. We quantify the time budget for classical memory swap without causing query slowdown in Sec. 7.

**4.3.1 Pipelining Details.** Fat-Tree QRAM introduces *query-level pipelining*, unlike the bit-level pipelining of BB QRAMs, enabling greater parallelism without additional resources. We illustrate this pipelining process by integrating circuit gates with additional swap operations in Fig. 6.

QRAM swapping, while seemingly complex, is efficiently executed via *local swapping*, where each node independently swaps internal qubits. Since quantum queries involve all QRAM branches in superposition, local swapping provides a constant-depth solution by performing swaps within each node (i, j) rather than requiring inter-node communication. Specifically, swapping QRAMs k and k+1 involves each node (i, j) swapping router (i, j, k)'s input and router qubits with those in (i, j, k+1).

Fig. 6 defines two local swapping types: - SWAP-I: Evenindexed routers  $(i, j, k) \Leftrightarrow (i, j, k + 1)$  for even k. - SWAP-II: Odd-indexed routers  $(i, j, k) \Leftrightarrow (i, j, k + 1)$  for odd k.

The smallest QRAM (k=0) does not undergo Type-II swaps, and the largest QRAM (k=n-1) swaps only once, depending on the parity of n. Alternating SWAP-I and SWAP-II enables seamless query movement across QRAM sizes, facilitating both loading and unloading. Additionally, local swapping maintains sequential qubit allocation with only nearest-neighbor connectivity, simplifying hardware design (Fig. 4(c)).

Local swapping requires only a single circuit layer and can run concurrently with classical data retrieval(note that only one type of local swapping will be associated with data retrieval, with the type depending on the parity of n). The pipeline interval spans 10 circuit layers, structured as: gate step (4) + SWAP-I (1) + gate step (4) + SWAP-II (1), ensuring efficient scheduling regardless of n's parity.

We summarize the  $\log(N)$ -pipelined query procedure in Alg. 1 and visualize it in Fig. 6. A detailed breakdown with elementary operations appears in Appendix Fig. 12. The key conceptual steps are as follows:

- (a) Start a new query and execute one gate step of address loading/unloading for all existing queries.

- (b) Apply Type-I swap step, together with classical data retrieval for the leaves of Fat-Tree QRAM if address loading is finished for one of the ongoing queries.

- (c) Apply one gate step of address loading/unloading for existing queries.

- (d) Apply swap step Type-II, with data retrieval if needed.

- (e) Repeat (a-d) until all the query requests are served.

**Algorithm 1** Pipeline  $\log(N)$  Quantum Queries with size-N Fat-Tree Shared QRAM.

```

1: Require: |\psi_A^j\rangle = \sum_{i=0}^{N-1} \alpha_i^j |i\rangle > address of the jth query 2: Require: 0 \le j \le n-1 > query index

3: Require: n = log(N) \ge 1 \triangleright QRAM \text{ height/total queries}

4: Ensure: |\psi_{AB}^{j}\rangle = \sum_{i=0}^{N-1} \alpha_{i}^{j} |i\rangle_{A} |x_{i}^{j}\rangle_{B}

5: for t = 1, 2, ... until queries are finished do

if t is odd then

\begin{array}{l} \textbf{if} \ t \equiv 1 \mod 4 \ \textbf{then} \\ \text{Start next query} \ |\psi_A^{(t-1)/4}\rangle \end{array}

7:

8:

9:

Load/Unload Layer (Alg. 2 & 3) ∀ existing queries

10:

else

11:

if t \equiv 2 \mod 4 then

12:

SWAP-I: (i, j, k) \Leftrightarrow (i, j, k+1) \forall even k

13:

if n is odd then

14:

CLASSICAL-GATES

15:

▶ Data retrieval for fully loaded query

16:

17:

end if

else

18:

SWAP-II: (i, j, k) \Leftrightarrow (i, j, k + 1) \forall \text{ odd } k

19:

if n is even then

20:

CLASSICAL-GATES

21:

22:

▶ Data retrieval for fully loaded query

end if

23:

end if

24:

end if

25:

26: end for

```

## 5 Scheduling Quantum Queries

The previous section examined the architectural design and hardware implementation of Fat-Tree QRAM. Optimizing query performance, however, also depends on efficient QPU-QRAM collaboration at the compiler level, particularly in scheduling query requests. This section introduces a latency-optimal scheduling algorithm for Fat-Tree QRAM and explores its full utilization by analyzing intrinsic quantum algorithm structures.

## 5.1 Increasing Utilization of a Shared QRAM

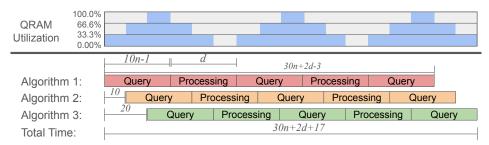

Fig. 6 illustrates that  $\log(N)$  queries can be efficiently pipelined in  $O(\log(N))$  circuit layers if executed consecutively. However, real algorithms may not issue queries uniformly, as seen in Fig. 7, which incorporates processing stages occupying d circuit layers between queries. If queries occur at regular intervals of depth d, QRAM utilization will sometimes be below 1.

State-of-the-art QRAMs serve requests sequentially, yielding binary utilization (0 or 1). In contrast, a capacity-N Fat-Tree QRAM pipelines  $\log(N)$  queries, allowing utilization to vary between 0 and 1, enabling additional queries during QPU processing intervals. This suggests Fat-Tree QRAM

**Figure 6.** Pipeline schedule of a capacity-8 Fat-Tree QRAM running 3 concurrent queries. Colors indicate which conceptual QRAM k in Fig. 5 is being used at the hardware level. No conflicting colors in the same layer ensures no concurrent access to the same quantum routers. The latency overhead for each single query of Fat-Tree QRAM compared to the original BB QRAM (query latency 29:25 in the case n = 3) comes from additional swap steps except the one coinciding with data retrieval, as it is included in BB QRAM's latency.

can accommodate  $\log(N) + d$  distributed QPUs rather than just  $\log(N)$ . Understanding algorithmic structures is key to maximizing QRAM utilization, especially in shared QRAM architectures interacting with multiple QPUs, further explored in Sec. 7.

## 5.2 Offline and Online Query Scheduling

The above discussion considers offline scheduling, where query intervals are predetermined. In practice, shared QRAM must handle online query requests, making scheduling more complex as QRAM lacks prior knowledge of QPU activity, and queries arrive at random intervals.

Using a greedy exchange proof, we demonstrate that First-In-First-Out (FIFO) scheduling minimizes total query latency for both offline and online cases (proof in Sec. A.2). Assume an optimal schedule deviating from FIFO, where a later-requested query is processed first. Swapping these queries to align with the request order does not worsen latency. Repeatedly applying this swap to all out-of-order query pairs transforms the schedule into FIFO while maintaining non-increasing latency. Thus, FIFO scheduling is optimal, ensuring minimal total latency.

## 6 Evaluation Methodology

#### 6.1 Baseline Architectures

In this paper, we analyze the performance of Fat-Tree QRAM, Distributed Fat-Tree QRAM (D-Fat-Tree), BB QRAM[19], Distributed Bucket-Brigade QRAM (D-BB), and Virtual QRAM (Virtual) [59]. For Fat-Tree and BB, we assume a single QRAM of capacity N is used as a shared memory. For D-Fat-Tree,

we assume  $\log(N)$  distributed BB QRAMs of capacity N are used. For D-BB, we assume  $\log(N)$  distributed BB QRAMs of capacity N are used. For Virtual QRAM, we create  $\log(N)$  virtual QRAMs, each using  $O(N/\log(N))$  qubits to access a large address space (N) at the expense of increased latency. More concretely, it divides the capacity N into K pages with size M = N/K for each page and constructs a QRAM with  $O(K\log(M))$  query latency and  $O(M+\log(K))$  qubit counts. For a fair comparison, the Virtual baseline uses the same total number of qubits as Fat-Tree. In the subsequent results, the baselines are organized into two groups: the first group, comprising Fat-tree, BB, and Virtual, utilizes (O(N)) qubits, while the second group, including D-Fat-Tree and D-BB, requires  $(O(N\log(N)))$  qubits—an asymptotically greater quantity than the first group.

#### 6.2 Quantitative Performance Metrics for QRAM

To quantify the performance of QRAM, especially under a parallel query setting, we define several important metrics: (i) query parallelism, (ii) max query rate, (iii) QRAM bandwidth. Query parallelism is the maximum number of parallel queries a QRAM can execute simultaneously. We say a QRAM is under utilized if it is executing queries fewer than the allowed query parallelism. Max query rate (in units of queries per sec) is defined as the maximum number of queries completed per unit time. In our pipelined Fat-Tree QRAM, this is calculated by inverting the amortized time of a single query. Finally, we define QRAM bandwidth (in units of qubits per second) as the rate at which data are queried and written into bus qubits, which can be calculated by the product of max query

**Figure 7.** Algorithm execution and query scheduling diagram with Fat-Tree QRAM. Every single query requires 10n - 1 circuit layers to finish for address width n, followed by d circuit layers of QPU processing before the next query. In this example, QRAM is underutilized; that is, additional queries can be pipelined.

rate and bus width (i.e., number of data qubits returned per query). We focus on results with bus width = 1 in Sec. 7.

To assess QRAM performance, it is useful to isolate hard-ware capabilities by using device-independent metrics like *circuit layers*. A circuit layer is one logical step where all quantum gates within the same layer are executed in parallel. It can be further combined with the device clock speed, e.g., Circuit Layer Operations Per Second (CLOPS) [2], to quantify the actual hardware performance.

### 6.3 Benchmarks and Applications

A shared QRAM can facilitate running multiple algorithms in parallel or running a parallel quantum algorithm. We benchmark the benefits of Fat-Tree QRAM for both synthetic and real-world algorithms:

Synthetic algorithms: We define a family of circuits, each with alternating processing (for time d) and query (for time  $t_1$ ). We test ratios of  $d/t_0$  ranging from 0 to 2. Section 7.4 presents benchmarking results of synthetic algorithms, each repeating querying and processing 10 times with capacity N=1024. These algorithms enable the comparison of QRAM utilization and overall algorithm depth between different QRAM architectures.

Parallel Grover's search: Grover's algorithm can be applied in parallel to p segments of the database [63], where each segment is queried  $O\left(\sqrt{N/p}\right)$  times.

*Parallel k-Sum:* By implementing p-parallelized queries to create modified states for the quantum walk, the parallel k-Sum algorithm improves the query complexity from  $O(N^{k/k+1})$  to  $O((N/p)^{k/k+1})$ .

*Parallel Hamiltonian Simulation*: Some structured Hamiltonian simulations can be implemented by parallel quantum walks [64].

Parallel Quantum Signal Processing (QSP): By factoring degree-d polynomials to the product of p smaller polynomials of degree O(d/p) [40], the parallel QSP improves the query complexity from O(d) to O(d/p).

#### 7 Results

## 7.1 Resource Estimation and Comparison

Table 1 presents a comprehensive comparison of different shared QRAM implementations with various parameters, including qubit count, query parallelism, and query latency. All numbers in the table are precise counts for a QRAM with capacity N. Baseline BB is a sequential query architecture suffering from  $O(\log^2(N))$  overhead in query latency. Comparing Fat-Tree QRAM to the same-qubit-count baseline, Virtual, the overall query latency for parallel queries is asymptotically slower than Fat-Tree QRAM, due to the large single query latency in Virtual, namely  $O(\log^2(N))$ for Virtual QRAM vs  $O(\log(N))$  for BB. In particular, the Virtual architecture decomposes the total address space *N* into  $K = \log(N)/2$  pages, where each page has size M = $N/\log(N)$  and requires a native Multi-Control-X (MCX) gate to implement. Baseline D-BB has low query latency while requiring asymptotically more resources. It is asymptotically slower in multiple-query tasks compared to the same-qubitcount baseline D-Fat-Tree QRAM. Consequently, under the same resource constraints, the Fat-Tree QRAM asymptotically outperforms state-of-the-art QRAM architectures regarding overall query latency for parallel query requests. All our resource estimation in Table 1 based on realistic hardware parameters under the recent improvement in the implementation of native CSWAP gates, offering a  $\tau = 1\mu s$  gate time [56], or equivalently clock speed  $1/\tau = 10^6$  CLOPS [2]. The intra-node SWAP gate is even faster with gate time  $T_{\text{SWAP}} = 125ns [37, 56].$

#### 7.2 ORAM Bandwidth

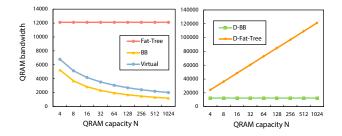

Table 2 includes a comparison of QRAM bandwidth for all the QRAM architectures. Recall that in Sec. 6, we define bandwidth as the rate at which data qubits can be provided to the QPUs. Fig. 8 provides a fine-grained, accurate scaling of QRAM bandwidth and space-time comparison under the same gate parameters in resource estimation.

As shown in Table 2, Fat-Tree QRAM achieves a *constant* bandwidth (i.e., independent of the QRAM size *N*), giving it an asymptotic advantage compared to all other architectures

|                                                           | Fat-Tree              | D-Fat-Tree                       | BB [19]                                                                                                                       | D-BB                        | Virtual [59]                                                 |

|-----------------------------------------------------------|-----------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------|

| Qubits                                                    | 16 <i>N</i>           | $16N\log(N)$                     | 8 <i>N</i>                                                                                                                    | $8N\log(N)$                 | 16 <i>N</i>                                                  |

| Query parallelism m                                       | $\log(N)$             | $\log^2(N)$                      | 1                                                                                                                             | $\log(N)$                   | $\log(N)$                                                    |

| Query latency for                                         | $8.25\log(N)$         | $8.25\log(N)$                    | $8\log(N) + 0.125$                                                                                                            | $8\log(N) + 0.125$          | $4\log^2(N) + 4.0625\log(N)$                                 |

| single query $t_1$                                        | -0.125                | -0.125                           | $\begin{array}{c c} 25 & \begin{array}{c c} 8 \log(N) + 0.125 \end{array} & \begin{array}{c c} 8 \log(N) + 0.125 \end{array}$ | 0 log(1V) + 0.123           | $-4\log(N)\log(\log(N))$                                     |

| Query latency for $log(N)$ -parallel queries $t_{log(N)}$ | 16.5 log(N)<br>-8.375 | $16.5 - \frac{8.375}{\log(N)} *$ | $8 \log^2(N) \\ +0.125 \log(N)$                                                                                               | $8\log(N) + 0.125$          | $ 4 \log^{2}(N) + 4.0625 \log(N)  -4 \log(N) \log(\log(N)) $ |

| Amortized Single<br>Query Latency                         | 8.25                  | $\frac{8.25}{\log(N)}$           | $8\log(N) + 0.125$                                                                                                            | $8 + \frac{0.125}{\log(N)}$ | $4 \log(N) + 4.0625$<br>$-4 \log(\log(N))$                   |

**Table 1.** Space (i.e., qubit number) and time (i.e., query latency) resource comparison across different shared QRAM models with classical memory size N. Latency is calculated with intra-node and classical gates, taking only an eighth of the time as a standard circuit layer. Compared to BB QRAM, Fat-Tree QRAM achieves an asymptotic reduction in query latencies for  $\log(N)$  parallel queries at the cost of constant overhead (i.e., doubling) in qubits. Note that  $t_{\log(N)}$  for D-Fat-Tree is the amortized time for  $\log(N)$  queries since D-Fat-Tree has a higher parallelism than  $\log(N)$  queries (i.e.  $\log(N)$ ) queries is insufficient to fully utilize D-Fat-Tree).

|                                                  | Fat-Tree             | D-Fat-Tree              | BB [19]                                            | D-BB                                     | Virtual [59]                                      |

|--------------------------------------------------|----------------------|-------------------------|----------------------------------------------------|------------------------------------------|---------------------------------------------------|

| QRAM bandwidth (qubit/sec)                       | $1.21 \times 10^{5}$ | $1.21\log(N)\times10^5$ | $\frac{1.25 \times 10^5}{\log(N)} + 8 \times 10^6$ | $\frac{10^6 \log(N)}{8 \log(N) + 0.125}$ | $\frac{10^6}{4\log(N) + 4.0625 - 4\log(\log(N))}$ |

| Space-time Volume per query                      | 132 <i>N</i>         | 132 <i>N</i>            | $64N\log(N) + N$                                   | $64N\log(N) + N$                         | $64N \log(N) + 65N$ $-64N \log(\log(N))$          |

| Time budget for classical memory swap ( $\mu$ s) | 8.25                 | 8.25                    | $8\log(N) + 0.125$                                 | $8\log(N) + 0.125$                       | $4\log^{2}(N) + 4.0625\log(N) - 4\log(\log(N))$   |

**Table 2.** Bandwidth, memory access rate, and space-time volume comparison across different shared QRAM models with classical memory size N. The CSWAP gate time is estimated at  $1\mu s$  [56], which leads to QRAM clock speed at  $1 \times 10^6$  circuit layer operations per second (CLOPS) [2]. Fat-Tree QRAM achieves a high bandwidth and memory access rate that is independent of the memory size N, and requires asymptotically less space-time volume than other QRAM models.

that use the same resources. Though the bandwidth of Baseline D-BB is also constant, it achieves constant scaling at the price of  $\log(N)$  copies of the hardware. The bandwidth is also related with *quantum volume per query*, defined as the amortized qubit · circuit depth per query, quantifying the cost of implementing a single query. Fat-Tree QRAM, under the same resource constraints, asymptotically outperforms BB and Virtual QRAM.

Another related metric is *memory access rate* which quantifies the rate at which classical data is read by the QRAM hardware. While this rate is consistent with the bus qubit throughput quantified by bandwidth, the duty rate of shared QRAMs can be simply calculated by (bandwidth  $\cdot$  N).

Finally, we estimate the time budget for classical memory swap using the time interval between two separate queries' data retrieval. While classical memory changes were neglected in previous analyses, large memory shifts can introduce delays in practice if the swap time budget is insufficient. We observed that different architectures pose different classical memory challenges: Fat-Tree requires rapid swapping with constant intervals; in contrast, D-BB requires parallel memory swapping, as the classical memory cells are also copied and distributed for D-BB QRAM.

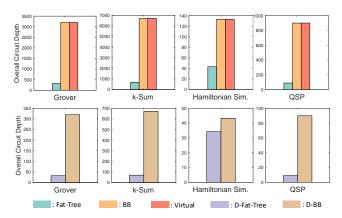

#### 7.3 Enabling Parallel Algorithms

One of the most significant applications for Fat-Tree QRAM is supporting parallel quantum algorithms requiring parallel queries. In particular, we removed all the dependencies on other parameters by setting them as constant values, such as deviation  $\epsilon$  and Hamiltonian sparsity d. Hence, the resulting asymptotic scaling only depends on problem size N (capacity of QRAM). Compared to Baselines BB and Virtual, Fat-Tree QRAM achieves the following asymptotic reduction in circuit depth:

- Grover's algorithm:  $O(\log^2(N)\sqrt{N})$  to  $O(\log(N)\sqrt{N})$

- k-sum algorithm:  $O(\log^2(N)(N/\log(N))^{k/k+1})$  to  $O(\log(N)(N/\log(N))^{k/k+1})$

- Hamiltonian sim.:  $O(\log(N) \log(\log((N)) + \log^2(N))$ to  $O(\log(N) \log(\log((N)) + \log(N))$ .

- Quantum Signal Processing (QSP): O(poly(d)) to O(poly(d)/log(N)), where d is the degree of polynomial encoded in the unitary transformed by QSP.

To put the savings into context, Fig. 9 presents concrete examples of overall algorithmic circuit depth reduction (by up to a factor 10) on practical problems with medium-scale memory  $N=2^{10}$ .

**Figure 8.** Bandwidth comparison for different QRAM architectures. Fat-Tree achieves a capacity-independent constant bandwidth.

**Figure 9.** Overall circuit depth for running parallel algorithms, assuming memory size  $N = 2^{10}$ . For QSP, we assume d = 30 and  $poly(d) = d^2$ . Fat-Tree QRAM achieves up to a factor of 10 reduction compared to baselines BB and Virtual.

#### 7.4 QRAM Hardware Utilization

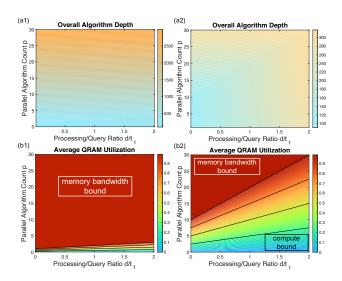

As discussed in Sec. 5, to maximize the utilization without queries bottlenecking, an ideal strategy is to allocate a proper number of parallel algorithms to one Fat-Tree QRAM. Fig. 10 presents the result of the synthetic algorithms introduced in Sec. 6 and compares the performance of BB with Fat-Tree QRAM on the dependency of processing/query ratio and parallel algorithm count. The BB QRAM meets the memory bandwidth bound even with a small increment in parallel algorithm count, resulting in a large overhead in the overall algorithm depth. Our Fat-Tree QRAM, however, is capable of balancing parallel algorithm count and the processing/query ratio, which significantly decreases the depth of synthetic algorithms.

## 8 Error Robustness of Fat-Tree QRAM

In this section, we show that Fat-Tree QRAM maintains BB QRAM's error resilience [23, 59] and requires fewer quantum resources for error correction to reach a desired circuit fidelity. Moreover, its capacity for additional queries can enhance query fidelity through virtual distillation [27] and support error correction. Thus, Fat-Tree QRAM achieves high

**Figure 10.** (a1/2) Overall algorithm depth of synthetic algorithm in BB/Fat-Tree QRAM. (b1/2) QRAM utilization of synthetic algorithm in BB/Fat-Tree QRAM. Fat-Tree QRAM balances processing/query ratio and parallel algorithms count, significantly reducing the overall algorithm depth.

query fidelity by combining error robustness and mitigation strategies, while remaining compatible with low-overhead QEC techniques for fault-tolerant quantum computing.

## 8.1 Noise Resilience of Fat-Tree QRAM

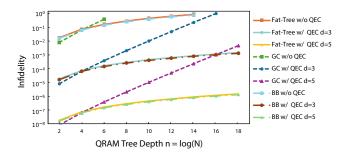

We show that Fat-Tree QRAM maintains the same intrinsic error-resilience and logarithmic infidelity scaling as BB QRAM [23, 59]. Following [23], we define query fidelity for a single query  $|\psi_{in}\rangle$  as  $F = \langle \psi_{out} | \rho_{out} | \psi_{out} \rangle$  where  $\rho_{out}$  is the actual output density matrix under noisy channel, and  $\psi_{out}$ is the ideal expected output state. For the noise model, we assume that each qubit is subjected to a generic error channel when a gate is applied:  $\mathcal{E}(\rho) = (1 - \epsilon)\rho + \epsilon K \rho K^{\dagger}$ , where  $\epsilon$  is the error probability and *K* denotes the error Kraus operator. We show that in the presence of this error channel, the Fat-Tree QRAM has the asymptotic lower bound in query fidelity  $F \ge 1 - 2 \cdot \log^2 N \cdot (\epsilon_0 + \epsilon_1 + \epsilon_2)$  where  $\epsilon_0, \epsilon_1, \epsilon_2$  correspond to the three types of gates introduced in Sec. 4: a total of  $\log^2(N)$  number of (intra-node) CSWAP gates each with error rate  $\epsilon_0$ ,  $\log^2(N)$  (inter-node) SWAP gates with error rate  $\epsilon_1$ , and  $\log^2(N)$  local (intra-node) SWAP gates with error rate  $\epsilon_2$ . Thus, the total fidelity is  $F \geq (2 \cdot \prod_i (1 - \epsilon_i)^{G_i} - 1)^2 \geq$  $1-2 \cdot \log^2 N \cdot (\epsilon_0 + \epsilon_1 + \epsilon_2)$ . Compared to BB QRAM's infidelity lower bound of  $F \ge 1 - 2 \cdot \log^2 N \cdot (\epsilon_0 + \epsilon_1)$  [23], Fat-Tree QRAM achieves parallelism with only a moderate decrease

Fig. 11 provides a query infidelity comparison between Fat-Tree and BB, where the error rates for the three types of gates are set to experimentally realistic values:  $\epsilon_0=0.002, \epsilon_1=0.002, \epsilon_2=0.001$  [48, 56, 65]. The infidelity scaling of Fat-Tree

| Capacity N | $\epsilon_0 = 10^{-3}$ | $\epsilon_0 = 10^{-4}$ | $\epsilon_0 = 10^{-5}$ (with |

|------------|------------------------|------------------------|------------------------------|

| - '        |                        |                        | post-selection)              |

| 8          | 0.045                  | 0.0045                 | 0.00045                      |

| 16         | 0.08                   | 0.008                  | 0.0008                       |

| 32         | 0.125                  | 0.0125                 | 0.00125                      |

| 64         | 0.18                   | 0.018                  | 0.0018                       |

**Table 3.** Query infidelity of QRAM with capacity N, given different input gate error rates  $\epsilon_0$  from [56]. The desirable scaling comes from QRAM's intrinsic noise resilience.

|                                              | Fat-Tree | 2 BB  |

|----------------------------------------------|----------|-------|

| Resource state prepared for distillation     | 4        | 2     |

| Fidelity of single query before distillation | 0.84     | 0.872 |

| Fidelity after distillation                  | 0.9994   | 0.984 |

**Table 4.** Fidelity comparison of capacity-4 Fat-Tree and two BB QRAMs (same-qubit-count baseline) before and after virtual distillation. Details are included in Sec. 8.2.

QRAM is only a constant factor (0.25x) worse compared to BB, due to intra-node SWAP gates implemented using beam-splitters, which is fast and high fidelity compared to the other two types of gates described above [10, 56]. As hardware continues to improve, QRAM of larger capacity will become practical. This is illustrated in Table 3, for different baseline error rates  $\epsilon_0$  with realistic parameters from [56].

#### 8.2 Virtual Distillation using Fat-Tree QRAM

In this section, we show how to leverage parallel queries provided by Fat-Tree QRAM to boost query fidelity. Virtual distillation is a quantum error mitigation technique that "distills" a higher-fidelity state from multiple noisy copies [27]. Let an *n*-qubit noisy quantum state be  $\rho = (1 - \epsilon)\rho_0 + \epsilon \rho_{error}$ where  $\rho_0$  is the ideal (error-free) state,  $\rho_{\rm error}$  is the error component, and  $\epsilon$  is the error rate. As for Fat-Tree QRAM, we prepare k identical copies of the noisy QRAM query state  $\rho$  in parallel, leading to the combined state  $\rho^{\otimes k}.$  The objective is to approximate a "distilled" state, defined as  $\rho_{\text{distilled}} = \frac{\rho^k}{\text{Tr}(\rho^k)}$ . Here,  $\rho^k$  represents the k-th power of  $\rho$ . To measure an observable O with reduced error, we calculate the expectation value using the distilled state:  $\langle O \rangle_{\text{distilled}} = \text{Tr}\left(\frac{\rho^k}{\text{Tr}(\rho^k)}O\right)$ . This approach effectively amplifies the ideal component  $\rho_0$ 's contribution to  $\rho$  while suppressing the erroneous content in noisy queries  $\rho_{\rm error}$ .

Both using 256 qubits, one Fat-Tree (N=16) and two BB QRAMs (N=16) can perform four parallel queries and two parallel queries, respectively. Under independent stochastic errors, Fat-Tree achieves an exponentially higher fidelity after distillation, shown in table 4.

In general, Fat-Tree QRAM can group k copies for distillation and still provide  $\log(N)/k$  parallel queries, thus presenting a trade-off between query parallelism and fidelity.

#### 8.3 Error Correction in Fat-Tree QRAM

# 8.3.1 Error-corrected query using encoded QRAM. The intrinsic noise resilience of Fat-Tree QRAM mentioned in Section 8.1 also helps reduce quantum error correction (QEC) overhead in the fault-tolerant era. We assume each qubit is encoded in an [[m, 1, d]] code (m for the number of d)physical qubits, d for the code distance), along with faulttolerant SWAP and CSWAP gates. Notably, although this gate set includes a non-Clifford gate, it can still be implemented using transversal non-Clifford gates while circumventing the constraints of the Eastin-Knill theorem [13]. This is because the limited gates in QRAM circuits do not form a universal set. For instance, the color code supports a transversal CCZ gate [31]. Beyond transversal gates, alternative methods exist that are more efficient than magic state distillation for implementing non-Clifford operations. One such approach is pieceable fault-tolerant gates [61], which perform intermediate error checks during gate execution. For example, [5,1,3] code implements a fault-tolerant Toffoli gate this way. This

technique could serve as a strong candidate for implementing

fault-tolerant CSWAP gates.

Notably, using different error correction architectures for QRAM and QPU may introduce extra code-switching overhead. However, only a moderate amount of code-switching is necessary, because only the *n* input address qubits (and 1 bus qubit) from the QPU need to be converted to the QEC code for QRAM. This is a relatively small fraction of all qubits involved, e.g., there are  $N = 2^n$  qubits within the QRAM. For instance, a well-studied code teleportation approach converts between two QEC codes of distance  $d_1$  and  $d_2$ , respectively. The procedure requires the  $d_1 * d_2$  ancilla qubits per query and O(1) circuit depth to transfer each of the n address qubits and the bus qubit sequentially [58]. Because Fat-Tree ORAM implements queries in a pipeline fashion, the ancilla qubits can be reused for the parallel queries. A similar claim also applies to state-of-the-art quantum low density parity check (LDPC) codes, with a linear number of ancilla qubits and a linear-depth circuit [12].

As a result, we can correct any (d-1)/2 bit-flip or phase-flip errors at the expense of  $O(m \cdot N)$  total qubits. Here we compare with a generic circuit (GC) whose worst-case infidelity scales *linearly* with its circuit size, which is a standard assumption in formal fault tolerance analyses. As shown in Figure 11, the intrinsic noise resilience protects BB/Fat-Tree QRAM from exponentially decaying fidelity for circuit of growing QRAM tree depth, when compared to a generic circuit. For example, to maintain same infidelity below  $5 \times 10^{-4}$ , QEC with distance 3 allows us to run a GC of tree-depth  $n \approx 6$  or a QRAM of tree-depth n = 10. At the same QEC cost, we can execute a QRAM circuit of larger size than a GC. Conversely, QRAM circuit (of the same size compared to GC) requires a lower QEC code distance to achieve the same fidelity.

**Figure 11.** Infidelity of a Fat-Tree QRAM, a BB QRAM, and a generic quantum circuit (GC) as a function of circuit size N (or QRAM tree depth  $n = \log(N)$ ) and QEC code distance d, assuming physical gate error rate  $\epsilon_0 = 10^{-3}$ . Fat-Tree and BB differ only slightly by a small constant factor, while GC performs exponentially worse than QRAM circuits.

When compared to BB QRAM, the infidelity of Fat-Tree QRAM differs by a small constant factor, due to its additional (Clifford) gates. The efficiency of QEC resources for QRAM circuits indicates that Fat-Tree QRAM's robustness could also benefit future fault-tolerant architectures.

**8.3.2** Error-corrected query using noisy QRAM. Experimental implementations of encoded QRAM can be challenging due to the  $O(m \cdot N)$  qubit cost. We further propose a novel scheme that leverages parallel queries on encoded addresses for error protection, without replacing every physical qubit in the QRAM with an encoded logical qubit. Specifically, we assume QRAM qubits are noisy but address/bus qubits are encoded using a QEC code. Finding a QRAM-tailored code is beyond the scope of this work, but we present a resource estimate (in Table 5) for QEC code with parameters [[m, 1, d]] and syndrome extraction circuit of depth D.

Fat-Tree enables the encoded address qubits to be routed into the QRAM in parallel. Specifically, due to the fault-tolerant implementation of CSWAP, we can route each of the m physical qubits in an encoded logical address qubit as m pipelined queries. If  $m \leq \log(N)$ , then  $\lfloor \log(N)/m \rfloor$  logical queries can be pipelined. Within each logical query, we can interleave syndrome extraction circuit on qubits from different physical queries reaching the same positions in the QRAM, resulting in a total logical query of depth  $O(D\log(N) + m)$ . Table 5 provides a comparison of this pipelined QEC scheme with an encoded BB QRAM.

#### 9 Discussion

#### 9.1 Beyond Superconducting Platforms

In Section 4, we proposed a hybrid cavity-transmon implementation of Fat-tree QRAM, demonstrating that Fat-tree QRAM can be realized even under the stringent connectivity constraints inherent to superconducting architectures. Another promising candidate for this implementation is the

|                           | Fat-Tree                    | BB                |

|---------------------------|-----------------------------|-------------------|

| Physical Qubits           | N                           | $m \cdot N$       |

| Logical Query Parallelism | $\lfloor \log(N)/m \rfloor$ | 1                 |

| Logical Query Latency     | $D \cdot \log(N) + m$       | $D \cdot \log(N)$ |

**Table 5.** Cost of the error-corrected query (in Big O) using (noisy) Fat-Tree QRAM and (encoded) BB QRAM. We assume an [[m, 1, d]] ( $m \le \log(N)$ ) QEC code with transversal CSWAP gate and D syndrome extraction circuit depth. Detailed analysis is included in Sec. 8.3.

trapped-ion platform, which benefits from all-to-all connectivity. By substituting each module in our design with a trapped-ion chip and linking chips through quantum charge-coupled devices (QCCDs), we achieve a scalable Fat-tree QRAM architecture [52]. Recent advancements in QCCD technology enable multiple operational zones within a single trapped-ion chip, further enhancing the feasibility and practicality of Fat-Tree QRAM deployment at scale [45].

#### 9.2 Related Work

In [50], Paler et al. introduced a "parallel query Bucket Brigade QRAM" based on different query definitions. Their parallel queries refer to classical queries to classical memory, reducing the depth of a single query (quantum query defined in this paper) from O(N) to  $O(\log(N))$  by parallelizing Clifford + T gates in the data retrieval stage. This improvement is accounted for and further enhanced by the O(1) data retrieval in Sec. 2. However, serving multiple *quantum* queries in a single QRAM remains a highly non-trivial problem and is resolved by our work.

#### 10 Conclusion

We presented a blueprint for a shared QRAM architecture based on multiplexed quantum routers in a Fat-Tree structure. It is capable of pipelining multiple quantum queries in parallel, while preserving the space, time, and fidelity scalings as a Bucket-Brigade QRAM. We demonstrate that the hardware architecture can be efficiently implemented on platforms such as superconducting cavities with native CSWAP gates and limited connectivity. Our results suggest Fat-Tree QRAM as a promising architecture for implementing high-bandwidth, noise-resilient quantum queries.

### Acknowledgments

We would like to thank Steven M. Girvin, Liang Jiang, Connor T. Hann, Daniel Weiss, Xuntao Wu, Rohan Mehta, Kevin Gui, Gideon Lee, Allen Zang, and Zhiding Liang for fruitful discussions. This project was supported by the National Science Foundation (under awards CCF-2312754 and CCF-2338063). External interest disclosure: YD is a scientific advisor to, and receives consulting fees from Quantum Circuits, Inc.

# Supplemental Material for 'Fat-Tree QRAM: A High-Bandwidth Shared Quantum Random Access Memory for Parallel Queries'

# A Appendix

## A.1 Step-by-step Query Procedure

We formally define the elementary QRAM instructions as follows with Figure 13 providing a visual representation of the operations

- LOAD (L): Load operation involves loading a new qubit through the escape to the input qubit of a root router in Fat-Tree QRAM. This operation only happens in the root node of QRAM.

- 2. TRANSPORT (*T*): Transport operation uses a SWAP gate to move a qubit from a router's output qubit to the next level's input qubit

- 3. ROUTE (R): Route uses CSWAP gates to route a qubit from the router's input to the outputs according to the state of router qubit. Generally, it is implemented using two CSWAP gates (controlled on the router qubit being 0 and 1), but our computations assume it costs a single circuit layer to simplify complexity and fidelity calculations. Regardless of the implementation, the asymptotic results will remain the same.

- 4. STORE (S): Store operation refers to storing an input qubit by swapping it from the quantum router's input qubit to the router qubit. This operation only happens at the highest unloaded layer of a QRAM, and increases the depth of the loaded tree by one.

- 5. CLASSICAL-GATES (*CG*): Performs classically controlled gates to modify the output qubits of the last QRAM level according to values in the classical database.

Similarly, we define the inverse of the operations as UNLOAD (L'), UNTRANSPORT (T'), UNROUTE (R'), and UNSTORE (S') respectively. Note that the gates for the last three operations are identical to their reversed counterparts (e.g. TRANSPORT and UNTRANSPORT are both a SWAP gate), but are conceptually different in their role.

Using these instructions, we provide step-by-step algorithmic descriptions of the query procedure. We decompose it into into the following subroutines: Alg. 1 for the overall Fat-Tree QRAM procedure, Alg. 2 for address loading and Alg. 3 for address unloading. The latter two can also be applied to BB QRAM, and are referenced by Alg. 1.

#### A.2 Proof of FIFO Scheduling Optimality

Using a greedy exchange proof, we show that for Fat-Tree QRAM, FIFO scheduling is optimal regarding overall query latency for both offline and online cases.

Consider a scheduling of queries  $q_1, q_2, ..., q_n$  which are all requested at times  $t_1, t_2, ..., t_n$  respectively. Let  $s_i$  also denote the time that  $q_i$  begins computing ( $t_i \le s_i$  since we can only start a query after it is requested and  $s_i < s_j$  for all  $i \le j$ )

## Algorithm 2 Load Layer

```

1: Require: loaded as number of address qubits loaded

2: Require: s as next address depth to be stored

3: Require: k as the current QRAM copy being used

4: Initialize: loaded \leftarrow 0, s \leftarrow 0, k \leftarrow 0 \forall new queries

5: Parallel

TRANSPORT (i, j, k) \ \forall \ i \in [\max(1, loaded - n), s]

6:

if loaded \le n then

7:

8:

LOAD

end if

10: EndParallel

11: loaded \leftarrow loaded + 1

12: Parallel

13:

ROUTE (i, j, k) \ \forall \ i \in [\max(0, loaded - n - 1), s - 1]

STORE (s, j, k)

15: EndParallel

16: Parallel

17:

TRANSPORT (i, j, k) \ \forall \ i \in [\max(1, loaded - n), s]

if loaded \le n then

18:

LOAD

end if

21: EndParallel

22: loaded \leftarrow loaded + 1

23: Parallel

ROUTE (i, j, k) \ \forall \ i \in [\max(0, loaded - n - 1), s]

25: EndParallel

26: s \leftarrow s + 1

```

and  $L_i = (s_i + T) - t_i$  denote the latency of  $q_i$  where T is the amount of time it takes to process a query (constant across all queries).

Suppose there is some optimal solution that does not follow our greedy FIFO scheduling. That is, there must exist two consecutive queries  $q_x$  and  $q_{x+1}$  such that  $t_{x+1} \le t_x$  (i.e. we schedule  $q_x$  before  $q_{x+1}$  even though it is requested later). We show that swapping  $q_x$  and  $q_{x+1}$  so they are scheduled in the order of their request times will result in a latency L' no worse than the optimal (i.e.  $L' \le L$ ). We have that the total latency in the optimal scheduling is  $L = \sum_i L_i = L_x + L_{x+1} + \sum_{i \ne x, x+1} L_i$ .

If we swap  $q_x$  and  $q_{x+1}$ , the other queries' latencies will not change meaning  $\sum_{i \neq x, x+1} L_i' = \sum_{i \neq x, x+1} L_i$ . We can start  $q_x$  at time  $s_{x+1}$  and  $q_{x+1}$  at time  $s_x$  as the QRAM is available during both those times (otherwise it would not be available in the original scheduling) and the queries are still only started after being requested  $(t_{x+1} \leq t_x \leq s_x < s_{x+1})$ . This results in new latencies of  $L_x' = (s_{x+1} + T) - t_x$  and  $L_{x+1}' = (s_x + T) - t_{x+1}$ . It is easy to show that  $L_x' + L_{x+1}' = L_x + L_{x+1}$  by rearranging

**Figure 12.** A step-by-step pipelining diagram for three capacity-8 queries using the instruction set defined in Sec. A.1. Numbers in the operations refer to the information being moved by the operation with address qubits numbered 1 to 3 and *B* denoting the bus (e.g. *S*1 represents storing the first address qubit). Columns indicate the circuit layer of the operation and rows denote the qubit in which the operation occurs. Similar to Fig. 6, colors indicate the conceptual QRAM *k* being used and the type of SWAP-I/II. Note that the query pipelines all align and there is no conflicting usage of qubits.

**Figure 13.** Diagram depicting the effects of the first four fundamental operations: LOAD, TRANSPORT, ROUTE, STORE. The router highlighted in green denotes the router the operation is performed on. The orange qubit depicts where the information is and how the operation moves it while the blue router qubit simply indicates that an address is loaded inside the router.

the terms. Thus,

$$L = (L_x + L_{x+1}) + \sum_{i \neq x, x+1} L_i = (L'_x + L'_{x+1}) + \sum_{i \neq x, x+1} L'_i = L'$$

.

If we continually swap all pairs of such  $q_x$  and  $q_{x+1}$  where  $t_{x+1} \leq t_x$ , we can incrementally transform the optimal solution into our greedy FIFO scheduling. Since at each step our latency is no worse than before, the final latency of our FIFO scheduling is no worse than the optimal solution, making it another optimal solution as well. This completes the proof that a FIFO scheduling always minimizes the total latency.

#### Algorithm 3 Unload Layer

```

1: Require: loaded as number of address qubits loaded

2: Require: s as next address depth to be stored

3: Require: k as the current QRAM copy being used

4: Ensure: runs only after data retrieval

5: s \leftarrow s - 1

6: Parallel

UNROUTE (i, j, k) \ \forall \ i \in [\max(0, loaded - n - 1), s]

8: EndParallel

9: loaded \leftarrow loaded - 1

10: Parallel

UNTRANSPORT (i, j, k) \ \forall \ i \in [\max(1, loaded - n), s]

11:

if loaded \le n then

12:

UNLOAD

13:

end if

15: EndParallel

16: Parallel

UNROUTE (i, j, k) \ \forall \ i \in [\max(0, loaded - n - 1), s - 1]

UNSTORE (s, j, k)

19: EndParallel

20: loaded \leftarrow loaded - 1

21: Parallel

UNTRANSPORT (i, j, k) \ \forall \ i \in [\max(1, loaded - n), s]

22:

if loaded \le n then

23:

UNLOAD

24:

end if

26: EndParallel

```

#### References

- [1] Yuri Alexeev, Dave Bacon, Kenneth R Brown, Robert Calderbank, Lincoln D Carr, Frederic T Chong, Brian DeMarco, Dirk Englund, Edward Farhi, Bill Fefferman, et al. 2021. Quantum computer systems for scientific discovery. PRX quantum 2, 1 (2021), 017001.

- [2] Mirko Amico, Helena Zhang, Petar Jurcevic, Lev S Bishop, Paul Nation, Andrew Wack, and David C McKay. 2023. Defining standard strategies for quantum benchmarks. arXiv preprint arXiv:2303.02108 (2023).

- [3] James Ang, Gabriella Carini, Yanzhu Chen, Isaac Chuang, Michael Austin DeMarco, Sophia E. Economou, Alec Eickbusch, Andrei Faraon, Kai-Mei Fu, Steven M. Girvin, Michael Hatridge, Andrew Houck, Paul Hilaire, Kevin Krsulich, Ang Li, Chenxu Liu, Yuan Liu, Margaret Martonosi, David C. McKay, James Misewich, Mark Ritter, Robert J. Schoelkopf, Samuel A. Stein, Sara Sussman, Hong X. Tang, Wei Tang, Teague Tomesh, Norm M. Tubman, Chen Wang, Nathan Wiebe, Yong-Xin Yao, Dillon C. Yost, and Yiyu Zhou. 2022. Architectures for Multinode Superconducting Quantum Computers. arXiv:2212.06167 [quant-ph]

- [4] Dominic W Berry, Craig Gidney, Mario Motta, Jarrod R McClean, and Ryan Babbush. 2019. Qubitization of arbitrary basis quantum chemistry leveraging sparsity and low rank factorization. *Quantum* 3 (2019), 208.

- [5] Michael E Beverland, Prakash Murali, Matthias Troyer, Krysta M Svore, Torsten Hoefler, Vadym Kliuchnikov, Guang Hao Low, Mathias Soeken, Aarthi Sundaram, and Alexander Vaschillo. 2022. Assessing requirements to scale to practical quantum advantage. arXiv preprint arXiv:2211.07629 (2022).

- [6] Jacob Biamonte, Peter Wittek, Nicola Pancotti, Patrick Rebentrost, Nathan Wiebe, and Seth Lloyd. 2017. Quantum machine learning. *Nature* 549, 7671 (2017), 195–202.

- [7] Hector Bombin, Isaac H Kim, Daniel Litinski, Naomi Nickerson, Mihir Pant, Fernando Pastawski, Sam Roberts, and Terry Rudolph. 2021. Interleaving: Modular architectures for fault-tolerant photonic quantum computing. arXiv preprint arXiv:2103.08612 (2021).

- [8] Teresa Brecht, Wolfgang Pfaff, Chen Wang, Yiwen Chu, Luigi Frunzio, Michel H Devoret, and Robert J Schoelkopf. 2016. Multilayer microwave integrated quantum circuits for scalable quantum computing. npj Quantum Information 2, 1 (2016), 1–4.

- [9] Marcello Caleffi, Michele Amoretti, Davide Ferrari, Daniele Cuomo, Jessica Illiano, Antonio Manzalini, and Angela Sara Cacciapuoti. 2022. Distributed quantum computing: a survey. arXiv preprint arXiv:2212.10609 (2022).

- [10] Benjamin J Chapman, Stijn J de Graaf, Sophia H Xue, Yaxing Zhang, James Teoh, Jacob C Curtis, Takahiro Tsunoda, Alec Eickbusch, Alexander P Read, Akshay Koottandavida, et al. 2023. High-on-off-ratio beam-splitter interaction for gates on bosonically encoded qubits. PRX Quantum 4, 2 (2023), 020355.

- [11] Kevin C Chen, Wenhan Dai, Carlos Errando-Herranz, Seth Lloyd, and Dirk Englund. 2021. Scalable and high-fidelity quantum random access memory in spin-photon networks. PRX Quantum 2, 3 (2021), 030319.

- [12] Andrew Cross, Zhiyang He, Patrick Rall, and Theodore Yoder. 2024. Improved QLDPC Surgery: Logical Measurements and Bridging Codes. arXiv preprint arXiv:2407.18393 (2024).

- [13] Bryan Eastin and Emanuel Knill. 2009. Restrictions on transversal encoded quantum gate sets. *Physical review letters* 102, 11 (2009), 110502.

- [14] Jay Gambetta. 2020. IBM's roadmap for scaling quantum technology. IBM Research Blog (September 2020) (2020).

- [15] Jeffrey P Gambino, Shawn A Adderly, and John U Knickerbocker. 2015. An overview of through-silicon-via technology and manufacturing challenges. *Microelectronic Engineering* 135 (2015), 73–106.

- [16] Suhas Ganjam, Yanhao Wang, Yao Lu, Archan Banerjee, Chan U Lei, Lev Krayzman, Kim Kisslinger, Chenyu Zhou, Ruoshui Li, Yichen Jia, et al. 2024. Surpassing millisecond coherence in on chip superconducting quantum memories by optimizing materials and circuit design.

- Nature Communications 15, 1 (2024), 3687.

- [17] Yvonne Y Gao, Brian J Lester, Kevin S Chou, Luigi Frunzio, Michel H Devoret, Liang Jiang, SM Girvin, and Robert J Schoelkopf. 2019. Entanglement of bosonic modes through an engineered exchange interaction. *Nature* 566, 7745 (2019), 509–512.

- [18] Craig Gidney and Martin Ekerå. 2021. How to factor 2048 bit RSA integers in 8 hours using 20 million noisy qubits. *Quantum* 5 (2021), 433.

- [19] Vittorio Giovannetti, Seth Lloyd, and Lorenzo Maccone. 2008. Architectures for a quantum random access memory. *Physical Review A* 78, 5 (2008), 052310.

- [20] Vittorio Giovannetti, Seth Lloyd, and Lorenzo Maccone. 2008. Quantum random access memory. Physical review letters 100, 16 (2008), 160501