# Schemato – An LLM for Netlist-to-Schematic Conversion

Ryoga Matsuo<sup>2,3</sup>, Stefan Uhlich<sup>3</sup>, Arun Venkitaraman<sup>1</sup>, Andrea Bonetti<sup>1</sup>, Chia-Yu Hsieh<sup>1</sup>, Ali Momeni<sup>1,2</sup>

Lukas Mauch<sup>3</sup>, Augusto Capone<sup>3</sup>, Eisaku Ohbuchi<sup>4</sup>, Lorenzo Servadei<sup>1</sup>

<sup>1</sup>SonyAI, Switzerland <sup>2</sup>EPFL, Switzerland <sup>3</sup>Sony Semiconductor Solutions Europe, Germany <sup>4</sup>Sony Semiconductor Solutions, Japan

Abstract-Machine learning models are advancing circuit design, particularly in analog circuits. They typically generate netlists that lack human interpretability. This is a problem as human designers heavily rely on the interpretability of circuit diagrams or schematics to intuitively understand, troubleshoot, and develop designs. Hence, to integrate domain knowledge effectively, it is crucial to translate MLgenerated netlists into interpretable schematics quickly and accurately. We propose Schemato, a large language model (LLM) for netlist-toschematic conversion. In particular, we consider our approach in the two settings of converting netlists to .asc files for LTSpice and LATEX files for CircuiTikz schematics. Experiments on our circuit dataset show that Schemato achieves up to 93% compilation success rate for the netlist-to-LATEX conversion task, surpassing the 26% rate scored by the state-of-theart LLMs. Furthermore, our experiments show that Schemato generates schematics with a mean structural similarity index measure that is  $3 \times$ higher than the best performing LLMs, therefore closer to the reference human design.

Index Terms—Netlist to Schematic, Large language models (LLMs), Electronic design automation (EDA), Fine-tuning.

#### I. INTRODUCTION

Recent years have seen a rapid increase in the number of machine learning (ML)-based solutions that address different aspects of analog design, specially towards both topology and sizing [1]-[5]. The netlist representation of the analog circuit forms a central part of all these approaches, since they all operate by either encoding the information in the netlist or generating a netlist as a part of an end-to-end ML model. However, often such circuits, while they may maximize a certain objective function and, hence, are feasible in the eyes of an ML practician, might not result in a practical design in the eyes of an analog designer. An analog designer usually views and assesses a circuit through the circuit diagram or schematics and not a netlist. This means that having a schematic or circuit diagram corresponding to a netlist is crucial for the ML models engineer to benefit from the domain knowledge of the designer's feedback. This is specially the case when the circuits become large in size and when one considers problems such as synthesizing circuits [6], [7], where the designer must spend considerable resource in drawing a schematic by hand each time to be able to give feedback the ML models more effectively. Thus, it is highly desirable to be able to efficiently and automatically translate netlists into circuit diagrams or schematics.

Circuit schematics are manually generated using conventional electronic design automation (EDA) tools by analog designers and visualized with associated viewing tools, such as LTSpice which processes text-based structured schematic files, .asc to produce circuit diagrams. An alternative approach is to use the TikZ library in LaTeX, where circuits are represented by code [8]. Both methods rely on structured programs with specific semantics or "languages". Similarly, netlists adhere to well-defined semantics for circuit representation, making the task of conversion to a schematic or diagram analogous to a language translation task. This analogy highlights the potential of leveraging large language models (LLMs), which excel at understanding and predicting semantic structures [9], [10]. LLMs have also recently shown great potential in different aspects of EDA, particularly, in digital and logic synthesis [4], [11]–[15] wherein

the models learn to understand, abstract, and build upon the design process of human designers. This motivates us to propose an LLMbased solution for translating netlists to circuit schematics/diagrams.

The earliest works on automated netlist to schematic generation have mostly been in the domain of digital ICs [16], [17]. Some of the early works for analog circuit include [18] that introduced a symmetry-based placement algorithm that identifies symmetrical structures within a netlist, and the work of [19] that concentrated on schematic routing aimed at minimizing net crossings. The more recent work of [20] presents a ML-based approach that combines identification of subblocks with an RL block that generates the schematic by optimizing for a reward based on the building block compliance rate that measures aesthetic of the generated schematic based on topological and heuristic constraints.

While these approaches have been shown to perform well on different circuit topologies, they rely on either the explicit use of heuristic rules or an understanding of the underlying topology/hierarchy of its subblocks or subcircuits or on the use of specific aesthetic reward functions. Schemato overcomes these limitations by developing an automated netlist to schematic conversion system that is independent of the circuit type or functionality, enabling broad applicability across diverse designs without requiring prior knowledge of specific circuit characteristics, while maintaining as faithfully as possible the aesthetics of a human design. This is because our approach learns from human-designed circuit examples and therefore does not require an explicit aesthetics measure. We also note that due to the universal nature of the framework, we are not limited to specific schematic templates or the choice of the SPICE solver; although we have used LTSpice with .asc format in our experiments, our approach is equally valid with the use of other EDA tools with their schematic formats.

In particular, our contributions are:

- We propose Schemato, an LLM for automatic translation of netlists to text-based schematic representations, fine-tuned on human-created design examples.

- We consider two types of netlist to schematic conversion, namely, netlist-to-asc files for use with LTSpice, and netlistto-LATEX for use with the CircuiTikz library for schematic generation, respectively.

- We perform exhaustive experiments on publicly available circuit and evaluate the performance of our approach using various metrics such as bilingual evaluation understudy (BLEU), compilation success rate (CSR), and mean structural similarity index measure (MSSIM).

- Experiments show that *Schemato* outperforms state-of-the-art LLMs with a CSR of 93.75% in the netlist-to-LATEX conversion task and a 3× higher average MSSIM over the test set.

To the best of our knowledge, no prior work exists that addresses this specific and important problem using LLMs, and given the increasing influence of LLMs, we believe our contribution is both timely and valuable for advancing ML-based approaches for analog design.

Fig. 1: Use case of Schemato: AI conversion of SPICE netlists into human-readable schematics.

## **II. PRELIMINARIES**

# A. Review of LLMs

Large Language Models (LLMs) are sophisticated AI systems designed to process and generate human-like text by leveraging vast datasets and advanced neural architectures [9], [10]. They excel in a range of linguistic and cognitive tasks, including translation, summarization, and complex reasoning. A key factor for effectiveness is prompt engineering — the crafting of precise and contextualized instructions to maximize accuracy and relevance of LLM responses. By utilizing advanced techniques such as Chain-of-Thought (CoT) prompting for multi-step reasoning and few-shot prompting for taskspecific adaptation, LLMs can be made to handle nuanced tasks with remarkable efficiency [21]. Despite their versatility, state-of-the-art LLMs are typically trained on broad, general-purpose datasets. As a result, their performance in specialized domains, such as EDA, may fall short due to the lack of task-specific optimization [11]-[13], [15]. Addressing these limitations often requires fine-tuning or targeted prompt strategies to align LLM capabilities with the unique demands of EDA applications.

In our work, we consider different combinations of prompt design, few-shot examples, and fine-tuning of LLMs to translate netlists into circuit diagrams/schematics. Our experiments demonstrate that while both prompt engineering and the incorporation of few-shot examples are crucial for improving the output of the original LLM, fine-tuning yields a substantially enhanced LLM, called *Schemato*.

# B. Review of LTSpice-specific .asc format

We next shortly review the key terms in the LTSpice .asc file<sup>1</sup> As we discuss later, this will also motivate some of the prompts used in our experiments. In the .asc file, each line starts with one of the following keywords accompanied by the corresponding input arguments

- "Version index" defines the LTSpice version.

- "SHEET index height width": defines the sheet index and size on the LTSpice application.

- "WIRE  $x_{start} y_{start} x_{end} y_{end}$ ": creates a wire that extends from position ( $x_{start}, y_{start}$ ) to ( $x_{end}, y_{end}$ ).

- "SYMBOL component  $x_{comp} y_{comp} \theta$ ": instantiates a circuit component (e.g. nmos, pmos, resistor, opamp, inverter) at the specified position  $(x_{comp}, y_{comp})$  and orientation  $\theta$ , where  $\theta = R90$  corresponds to  $90^{\circ}$  anti-clockwise rotation and  $\theta = M270$  for  $270^{\circ}$  anti-clockwise rotation combined with mirroring. This line is followed by one of these lines that sets a symbol attribute:

- "SYMATTR InstName component\_name": assigns the component's name.

<sup>1</sup>More details may be found in the documentation of LTSpice [22].

- "SYMATTR SpiceModel model\_name": assigns the component's spice model.

- "SYMATTR ModelFile model\_file": assigns the component's spice model path.

# C. Review of ETEX format

We next shortly review the key terms in the  $L^{ATE}X$  .tex file, tailored to the use of CircuitTikz library. As with the .asc files, we shall see how this information is valuable in improving the generated schematics through prompts shown in Fig. 2. The following are the keywords that characterize a .tex file.

- "\documentclass{}": Defines the type of document (e.g., article, report, book) and sets the document's overall format.

- "\usepackage{}": Imports additional packages to extend LaTeX's functionality, such as graphics, fonts, or TikZ for diagrams.

- "\usetikzlibrary{}": Includes specific TikZ libraries to enable advanced features like shapes, positioning, and circuit diagrams.

- "\begin{}" and "\end{}": Define environments, such as "document" for the main content or "tikzpicture" for TikZ diagrams.

- "\draw{}": Specifies drawing commands within a "tikzpicture" environment to create shapes, lines, and other visual elements.

- "\node{}": Places text or shapes at specific locations in a diagram, often used within TikZ.

- "\section{}" and "\subsection{}": Create structured headings for organizing content hierarchically.

# III. PROPOSED APPROACH: Schemato

In Fig. 1, we present an illustration of the *Schemato*-based circuit design workflow. The left half illustrates the fully data-driven model, while the right half integrates domain knowledge contributions from analog designers.

As discussed in Sec. I, *Schemato* addresses the task of automating circuit schematic generation from netlists. At its core, *Schemato* is an LLM fine-tuned using a curated dataset of human-created netlist-to-schematic pairs. Its development focuses on three key components:

- Task Definition: Constructing prompts that define the netlist-toschematic conversion task.

- Guidance via Context: Incorporating few-shot or in-context examples within prompts to guide the model.

- Fine-Tuning: Adapting the model using a specialized dataset of netlist-schematic pairs.

Schemato supports two distinct formats for schematic generation:

- LTSpice (.asc): Scripts compatible with LTSpice schematic generation tools. While our experiments focus on LTSpice due to its data availability, the approach generalizes to any text-based solver or schematic script format.

- CircuitTikz (LATEX): Code to generate schematics using the CircuitTikz library for LATEX documents [8].

| Zero-shot                                                                                                                                                                                                                             | One-shot                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Prompt 1: Simply instruct the LLM for the task</b><br>Convert the following netlist to a .asc file, a text-based circuit schematic file for<br>LTSpice / a LaTeX code using CircuiTikZ. Only output the code and contain it in "". | <b>Prompt 4: Provide an example of conversion</b><br>Convert the following netlist to a .asc file, a text-based circuit schematic file<br>for LTSpice / a LaTeX code using CircuiTikZ. Only output the code and<br>contain it in "". |

| Input: "'Netlist"                                                                                                                                                                                                                     | Here is an example:                                                                                                                                                                                                                  |

| <br>Output:                                                                                                                                                                                                                           | <b>Input:</b> "Example netlist of a low-pass filter (LPF)"                                                                                                                                                                           |

| ·                                                                                                                                                                                                                                     | Output: "Example .asc / LaTeX file of the LPF"                                                                                                                                                                                       |

| <b>Prompt 2: Specify the types of keywords to start each line of the output</b><br>Convert the following netlist to a .asc file, a text-based circuit schematic file                                                                  | Input: "Netlist"                                                                                                                                                                                                                     |

| for LTSpice / a LaTeX code using CircuiTikZ. Start each line with keywords<br>such as 'Version', 'SHEET', 'WIRE', 'FLAG', 'SYMBOL', and 'SYMATTR'<br>/ '\documentclass', '\usepackage', '\usetikzlibrary', '\begin',                  | <br>Output:                                                                                                                                                                                                                          |

| '\draw', and '\end'. Only output the code and contain it in "'.                                                                                                                                                                       | Prompt 5: Combination of Prompt 3 and 4                                                                                                                                                                                              |

| Input: "Netlist"<br>                                                                                                                                                                                                                  | Convert the following netlist to a .asc file, a text-based circuit schematic file for LTSpice / a LaTeX code using CircuiTikZ. Start your answer with "Version 4                                                                     |

|                                                                                                                                                                                                                                       | <pre>SHEET "'/ "'% automatically generated document using</pre>                                                                                                                                                                      |

| <b>Prompt 3: Specify the first few lines that the LLM should output</b><br>Convert the following netlist to a .asc file, a text-based circuit schematic file for                                                                      | lt2circuiTikz<br>\documentclass[tikz,margin={2pt 2pt 2pt                                                                                                                                                                             |

| LTSpice / a LaTeX code using CircuiTikZ. Start your answer with<br>"Version 4<br>SHEET "' /                                                                                                                                           | <pre>2pt}]{standalone} \usepackage[compatibility, siunitx,". Only output the code and contain it in ".</pre>                                                                                                                         |

| "% automatically generated document using lt2circuiTikz                                                                                                                                                                               | Here is an example:                                                                                                                                                                                                                  |

| <pre>\documentclass[tikz,margin={2pt 2pt 2pt 2pt]}{standalone}<br/>\usepackage[compatibility,siunitx,". Only output the code and</pre>                                                                                                | <b>Input:</b> "Example netlist of a LPF"                                                                                                                                                                                             |

| contain it in "".                                                                                                                                                                                                                     | Output: "Example .asc / LaTeX file of the LPF"                                                                                                                                                                                       |

| Input: "'Netlist"                                                                                                                                                                                                                     | Input: "Netlist"                                                                                                                                                                                                                     |

| <br>Output:                                                                                                                                                                                                                           | —<br>Output:                                                                                                                                                                                                                         |

Fig. 2: Prompt 1-5 for netlist-to-schematic conversion. The red and blue portions refer to the netlist-to-asc and netlist-to-LATEX conversion settings, respectively.

## A. Task definition and guidance via context

We consider the following tasks to evaluate the different models:

- Task 1: Translate netlist to LTSpice text-based schematic

- Task 2: Translate netlist to LATEX code using CircuiTikz

Furthermore, to develop and refine *Schemato*, we consider different prompting techniques to guide the LLM effectively. The summary of these prompt variants are provided in Fig. 2. As shown in the figure, prompt 1 is a simple, task-oriented description that serves as the baseline for comparison. Prompt 2 introduces syntax-specific keywords relevant to the target format, such as LTSpice symbols (Sec. II-B) or LATEX libraries and structure (Sec. II-C). Prompt 3 enhances guidance by including initial lines of the expected output, providing a stronger contextual foundation. Prompts 4 incorporate specific netlist-to-schematic conversion examples, offering the model concrete patterns for improved accuracy. Finally, Prompt 5 is merely a combination of prompt 3 and 4. Prompts 1–3 utilize zero-shot learning, while Prompts 4–5 employ one-shot learning.

# B. Fine-tuning

Schemato is developed by fine-tuning state-of-the-art LLMs using human-generated netlist-schematic data pairs. To address the limited availability of such data, we employ data augmentation techniques to expand the dataset, ensuring better coverage of diverse scenarios. To select the optimal base model, we first evaluate various LLMs using all proposed prompts. The combination of prompt and model yielding the highest performance is then fine-tuned resulting in *Schemato*. The comprehensive details on fine-tuning methodology, data preprocessing, and augmentation strategies are provided in Section IV.

#### IV. EXPERIMENTAL SETUP

In our experiments, we use LTSpice schematics from GitHub. These schematics contain circuits with diverse features. We use this set for training and validation. In addition, we also consider the publicly available LTSpice circuit files packaged with LTSpice XVII (examples in folders, Eduational & Applications [22]) for testing. In all the cases, we start from the available .asc files. These are then processed through LTSpice to create the corresponding netlists. Similarly, the .asc files are used to generate the LATEX scripts using the open-source python library  $lt2circuiTikz^2$ . Thus, for each .asc file, we create both the netlist and .tex files. Some .asc files cannot be compiled into netlist or converted into .tex files due to missing symbols in the default libraries of LTSpice and lt2circuiTikz. These .asc files are omitted from our dataset. We next describe the details of data preprocessing and filtering.

## A. Preprocessing and filtering datasets

To facilitate *Schemato* to learn the translation task, we preprocess the dataset by removing unnecessary information for the schematic visualizations in LTSpice. This includes spice simulation commands, spice model definitions, user annotations, comments, etc. In contrary, we do not preprocess the LATEX files as they do not contain unnecessary information for the schematic visualizations. We explain how we preprocess LTSpice compatible files below.

# LTSpice-specific .asc files:

• Replace SpiceModel and ModelFile with InstName while using the original model\_name and model\_file for component\_name. This allows for any line with SYMATTR to be compiled and component\_name can be set arbitrarily.

<sup>2</sup>https://github.com/ckuhlmann/lt2circuitikz

- Remove the lines starting with \*, TEXT, RECTANGLE, WINDOW, LINE, and CIRCLE.

- Remove the user annotations/comments since they are not needed for the schematic visualization by LTSpice.

- Discard .asc files with symbols that are not defined in *lt2circuitikz* as they cannot be converted into LaTeX.

- Discard .asc files that do not contain SYMBOL-SYMATTR pair as this type of example is not composed of meaningful circuit components except for wires.

Netlists: The file format we use for netlist is .net. We remove the lines with commands such as .backanno, .lib, and .model as they are not required for the schematic visualizations.

We next consider the augmentation strategy used to increase the effective dataset size.

## B. Data augmentation

For *Schemato* to be agnostic to the line ordering of .asc files, we create an augmented data example by swapping the lines of the .asc files. Specifically, .asc files can have different orders of SYMBOL-SYMATTR pairs resulting in the same schematic representations. Therefore, we randomly shuffle their line ordering and generate five different augmentations for .asc files with more than three SYMBOL-SYMATTR pairs. For .asc files with two SYMBOL-SYMATTR pairs, we swap their order to generate two samples and we leave the files with one SYMBOL-SYMATTR pair unmodified. After the generation of these augmented .asc file samples, we convert them into netlists and LATEX scripts to create the dataset as described in Sec. IV-A. The changes of the line ordering in .asc files are reflected in the line ordering of both netlists and LATEX scripts without any modifications in the schematic representation of the circuits.

Initially, the self-prepared dataset contains 22,045 publicly available .asc circuit files. After filtering, especially discarding files that cannot be converted by *lt2circuitikz*, it is reduced to 2,886 different circuit files. This filtered dataset is split into 2,712 training and 174 validation circuit files, which after augmenting each circuit file into up to 5 samples, result in total of 12,974 and 857 samples for training and validation, respectively. For testing, we use the 3,946 circuit examples from LTSpice XVII [22]. After the data filtering, we end up with 133 schematics. Furthermore, removing samples that are part of our training set, we yield a test set of 49 circuits. All of these circuit files are converted into netlists and LATEX

## C. Inference and fine-tuning

We start with Llama 3.1 base & instruct versions with 8 billion parameters (Llama-3.1-8B) [10] to develop *Schemato*. The tasks are first executed on the raw models to select the best performing prompts that are then used for fine-tuning. We use the recently proposed Torchtune [23] framework for LLM fine-tuning. We first discuss the details of inference and fine-tuning of the models.

During inference, Schemato generates schematics in an autoregressive way. Here, we used no special techniques to save memory or compute except for KV-caches. We apply greedy search, where the LLM selects the most probable next samples. Decoding terminates either if maximum number of tokens ( $N_{\text{tokens}}$ ) are reached or the stop-token is sampled. We choose  $N_{\text{tokens}} = 8192$  as this is the maximum number of tokens that can fit in a single NVIDIA Ada-6000 GPU. This limits the length of our test samples since some of the LATEX codes exceed 8192 tokens. For simplicity, we omit these long samples for the performance evaluation. With this setup, the inference on Schemato achieved approximately 23 tokens/sec on a single NVIDIA Ada-6000. To adapt the LLM to our specific task of translating netlists into schematics, we employed supervised instruction tuning on a paired dataset containing prompts with netlists and corresponding reference schematics as responses. However, fine-tuning LLMs like *Schemato* with 8 billion parameters requires a significant amount of GPU memory. To address this issue, we utilized fully-sharded data parallel (FSDP) training [24], which enables the distribution of the model's parameters across multi-GPUs while minimizing communication overhead. To further reduce memory consumption during training, we applied several additional techniques:

- We used bfloat16 representation for model parameters to decrease the memory usage compared to float32.

- Activation checkpointing was employed to compute gradients in a more memory-efficient manner.

- Low-rank adaptation (LoRA) with rank r = 8 and scaling factor  $\alpha = 16$  was applied to reduce the memory requirements of the trainable weights.

- Cross entropy with chunked output loss [23] is used to measure the difference between the generated token and the ground truth.

By combining these techniques, we fine-tune *Schemato* over 9 epochs (in each epoch, *Schemato* goes through the entire training set). The number of weight updates per epoch is then computed as:

$$\frac{N_{\text{train}} \times N_{\text{tasks}}}{N_{\text{iter}} \times N_{\text{GPU}} \times N_{\text{batch}}} = \frac{12,974 \times 2}{8 \times 8 \times 1} \approx 405$$

where  $N_{\text{train}}$  is the number of training samples,  $N_{\text{tasks}}$  is the number of conversion tasks,  $N_{\text{iter}}$  is the number of iterations per accumulation step,  $N_{\text{GPU}}$  is the number of NVIDIA Ada-6000 GPUs used for finetuning, and  $N_{\text{batch}}$  is the per-GPU batch size. This setup achieved a throughput of approximately 563 tokens/sec per GPU, allowing us to efficiently adapt the model to our specific task within a reasonable timeframe. We next discuss the different performance metrics used to evaluate the performance of the models.

# D. Performance metrics

We use the following three metrics to evaluate the samples generated by the different models: (a) BLEU that measures an Ngram similarity, (b) CSR that measures syntatic correctness, and (c) MSSIM that measures similarity with human generated design. We describe these metrics next.

1) Text-based metric: The bilingual evaluation understudy (BLEU) compares N-grams of the generated text and the reference translation and counts the number of matches independently of the positions [25]. With this measure, we compare the N-gram similarity between the reference and generated text-based schematics. While BLEU is not perfectly suited for our tasks due to the syntactical nature of .asc and LaTeX files, it can indicate the extent to which the pre-trained models already understand their language syntax. Furthermore, we selected the standard BLEU as our metric over CodeBLEU [26] specialized to capture syntactic and semantic features of codes since this measure does not support .asc and LATEX formats. We compare the performance of the models by computing BLEU, that is the average BLEU score across all test samples.

2) Compilation-based metric: The compilation success rate (CSR) measures the syntactical correctness of the generated .asc and LATEX scripts and is defined as

$$\mathrm{CSR} = \frac{N_{\mathrm{compilable}}}{N_{\mathrm{ref}}}$$

where  $N_{\text{compilable}}$  is the total number of compilable generated codes in the test set and  $N_{\text{ref}}$  is the total number of reference samples. 3) Image-based metric: The structural similarity index measure (SSIM) is a metric that computes the structural similarity of two image signals based on the statistical comparisons in luminance, contrast, and structure [27]. For a given pair of image patches x and y, SSIM is defined as

$$SSIM(x,y) = \frac{(2\mu_x\mu_y + C_1)(2\sigma_{xy} + C_2)}{(\mu_x^2 + \mu_y^2 + C_1)(\sigma_x^2 + \sigma_y^2 + C_2)}$$

where  $\mu_p$  and  $\sigma_p$  are the average and the standard deviation of an image patch p, respectively,  $\sigma_{xy}$  is the square-root of the crosscorrelation between the two image patches x and y,  $C_1$  and  $C_2$  are constants added to avoid computational instability. To evaluate the overall similarity between an image pair X and Y, a sliding local window is applied over the entire images and SSIM is computed at each pixel step within this window. The mean SSIM (MSSIM) between two images X and Y is then given by

$$\text{MSSIM}(X,Y) = \frac{1}{M} \sum_{i=1}^{M} \text{SSIM}(x_i, y_i)$$

where  $x_i$  and  $y_i$  are the image signals in the *i*-th local window and M is the number of local windows applied on the images. We use this metric to derive the similarities between the reference schematics in the test set and the schematics generated by LLMs from netlists. To obtain the images of generated and reference schematics, we load each .asc file with LTSpice and take a screenshot. These images are subsequently cropped to eliminate the artifacts from the graphical user interface. For the case of LATEX codes, the .tex files are converted into PDF files using pdflatex. These are then converted into images with pdf2image<sup>3</sup>. For cases where the generated codes do not successfully compile into an image, we set the MSSIM to be equal to 0. We then compare the performance of the models using <u>MSSIM</u>, that is the MSSIM score averaged over all test samples.

## V. RESULTS & DISCUSSION

In order to select the starting model for Schemato, we evaluated the performance of Llama-3.1-8B raw models across various configurations. Table I shows the performance of the different models for the netlist-to-.asc conversion task. We note that the MSSIM values are normalized by the maximum MSSIM value of 0.0228 achieved by Schemato fine-tuned on prompt 4. As can be seen, the performance did not vary significantly across different settings. Notably, moving from zero-shot to one-shot prompting had negligible impact on the performance for this task. In contrast, Table II highlights a key observation for the netlist-to-LATEX conversion task. Again, we note that the MSSIM values are normalized by the maximum MSSIM value of 0.0217 achieved by Schemato fine-tuned on prompt 4 for the corresponding task. Here, Llama-3.1-8B instruct with prompt 2 achieved a CSR of 25% for LATEX generation, while all other raw configurations failed to produce any compilable outputs. Based on these observations, we selected Llama-3.1-8B instruct with prompt 2 as the starting configuration. Additionally, we fine-tune Llama-3.1-8B instruct with prompt 4 to investigate the effect of one-shot prompting.

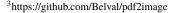

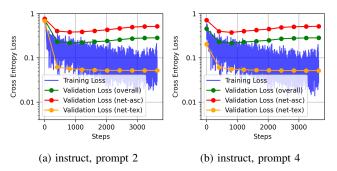

During fine-tuning, training and validation losses (Fig. 3) revealed overfitting for the netlist-to-.asc conversion after epoch 2 (since the validation loss increased with training epochs), while netlist-to-LATEX validation loss stabilized after several epochs. Since the cross entropy loss does not directly help quantify the correctness of the code and the generated schematics, we use CSR, and MSSIM metrics discussed in Section IV-D to evaluate the model performance during training epochs as shown in Fig. 4. We then choose the model weights that gave the best pair of CSR and MSSIM scores for further evaluation.

Fig. 3: Training and validation losses of *Schemato* fine-tuned on zero-shot and one-shot prompting. Validations losses are measured at each epoch.

Fig. 4: CSR and  $\overline{\text{MSSIM}}$  of *Schemato* fine-tuned with zero-shot and one-shot prompting for netlist-to-LATEX conversion.

We compare the performance of Schemato with the Llama-3.1-8B baselines. We further include GPT-4o, the latest and most powerful model from OpenAI. Table I shows that Schemato achieves significantly higher MSSIM scores in the netlist-to-.asc conversion task, while GPT-40 performs better in BLEU and CSR metrics. This outcome is expected, as the .asc syntax is relatively simple (Sec. II-B), allowing larger models like GPT-40 to excel. However, MSSIM, which measures visual similarity between reference and generated schematics, is unaffected by syntactic simplicity. We also note that Schemato initialized with Llama-3.1-8B instruct fine-tuned with prompt 2 using weights from epoch 3 results in the second-best performance in CSR and MSSIM, while the model fine-tuned with prompt 4 using weights from epoch 2 achieves the highest MSSIM score. We further note that Table II demonstrates Schemato's clear superiority in the netlist-to-LATEX conversion task, outperforming state-of-the-art models across all metrics. The best performing configuration was initialized with Llama-3.1-8B instruct, fine-tuned with prompt 4 using weights from epoch 9. This Schemato model achieves up to 93% for CSR, whereas the baseline models do not exceed a maximum of 26%. Moreover, the same Schemato provides a  $\overline{\text{MSSIM}}$  that is 3× higher than the best score achieved by the baseline LLMs.

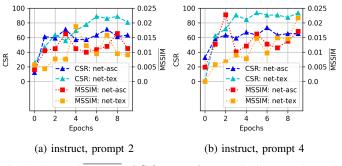

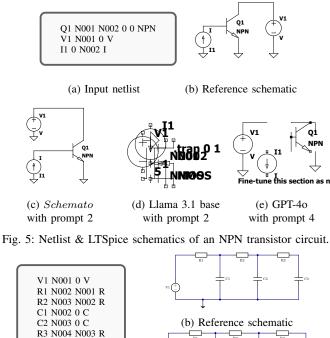

For the netlist-to-asc conversion task, we show the reference and generated schematics for a circuit example of an NPN bipolar transistor circuit from *Schemato* in Fig. 5 for the different models. Similarly, for the netlist-to-LATEX conversion task, we show the schematics obtained for the example of an RC phase shift network in Fig. 6. We note that the raw models of Llama-3.1-8B failed to produce a compilable code for the second example. Although *Schemato*'s schematics differ geometrically from the reference, they maintain identical topological features, demonstrating successful netlist-to-schematic conversion. GPT-40 with prompt 5 produced

Fig. 6: Netlist & LATEX schematics of an RC phase shift network.

the correct RC network topology but with overlapping components, whereas *Schemato* generated a clean schematic with well-spaced components, adhering to human design principles. These examples underscore *Schemato*'s ability to produce interpretable and accurate schematics, even without geometrical guidance, surpassing Llama-3.1-8B and GPT-40 in performance.

## VI. CONCLUSIONS & FUTURE WORK

In this paper, we introduced and evaluated *Schemato*, a fine-tuned LLM designed for converting circuit netlists into interpretable visual schematics. Our experimental results demonstrate that *Schemato* significantly outperforms state-of-the-art LLMs, including Llama-3.1-8B and GPT-4o, across all the text-based, compilation-based, and image-based metrics in the netlist-to-LaTeX conversion task. Similarly, for the netlist-to-.asc conversion tasks, *Schemato* outperforms all the other models in the image-based score (MSSIM). These findings underscore the potential of *Schemato* in reliably generating human-intuitive schematics from netlists, paving the way for enhanced interpretability and utility in ML-based analog circuit synthesis.

Our experiments show that for more complex examples, such as a NAND2 and a transistor-level OpAmp, *Schemato* struggles to generate accurate schematics. This is expected as our training dataset with 2,712 different circuits lacks structural diversity. This highlights the need for a larger dataset to better capture the nuances of such designs. To address this challenge, future improvements to *Schemato* will focus on enriching the dataset using additional circuits and advanced data augmentation techniques. For instance,

TABLE I: Test Performance for netlist-to-.asc conversion. The best and second best metrics are highlighted in red and blue, respectively. MSSIM values are normalized by the maximum of 0.0228.

| Model        | Version  | Prompt    | $\overline{\mathbf{BLEU}}$ | CSR (%)       | $\overline{\mathbf{MSSIM}}$ | $\mathbf{N}_{re}$ |

|--------------|----------|-----------|----------------------------|---------------|-----------------------------|-------------------|

|              | Wi       | thout Fir | ne-tuning: 1               | Zero shot     |                             |                   |

| Llama-3.1-8B | base     | 1         | 0.00                       | 4.08 (2/49)   | 0.0395                      | 49                |

| Llama-3.1-8B | instruct | 1         | 0.00                       | 0.00 (0/49)   | 0.0000                      | 49                |

| GPT          | 40       | 1         | 8.40                       | 16.33 (8/49)  | 0.1140                      | 49                |

| Llama-3.1-8B | base     | 2         | 0.00                       | 20.41 (10/49) | 0.1798                      | 49                |

| Llama-3.1-8B | instruct | 2         | 1.51                       | 12.24 (6/49)  | 0.1754                      | 49                |

| GPT          | 40       | 2         | 10.87                      | 32.65 (16/49) | 0.2237                      | 49                |

| Llama-3.1-8B | base     | 3         | 0.00                       | 20.41 (10/49) | 0.1711                      | 49                |

| Llama-3.1-8B | instruct | 3         | 0.00                       | 10.20 (5/49)  | 0.1535                      | 49                |

| GPT          | 40       | 3         | 9.97                       | 24.49 (12/49) | 0.1798                      | 49                |

|              | W        | ithout Fi | ne-tuning:                 | One-shot      |                             |                   |

| Llama-3.1-8B | base     | 4         | 0.00                       | 20.41 (10/49) | 0.1711                      | 49                |

| Llama-3.1-8B | instruct | 4         | 5.08                       | 32.65 (16/49) | 0.2158                      | 49                |

| GPT          | 4o       | 4         | 13.65                      | 48.98 (24/49) | 0.3772                      | 49                |

| Llama-3.1-8B | base     | 5         | 0.00                       | 24.49 (12/49) | 0.1974                      | 49                |

| Llama-3.1-8B | instruct | 5         | 1.18                       | 20.41 (10/49) | 0.1272                      | 49                |

| GPT          | 40       | 5         | 14.46                      | 73.47 (36/49) | 0.5833                      | 49                |

|              | Fine-    | tuned: ep | och 3 & 2,                 | respectively  |                             |                   |

| Schemato     | instruct | 2         | 12.33                      | 71.43 (35/49) | 0.7158                      | 49                |

| Schemato     | instruct | 4         | 13.43                      | 63.27 (31/49) | 1.0000                      | 49                |

TABLE II: Test Performance for netlist-to-LATEX conversion. The best and second best metrics are highlighted in red and blue, respectively. MSSIM values are normalized by the maximum of 0.0217.

| Model                          | Version                               | Prompt | $\overline{\mathbf{BLEU}}$ | <b>CSR</b> (%) | $\overline{\mathbf{MSSIM}}$ | $\mathbf{N}_{ref}$ |  |  |  |

|--------------------------------|---------------------------------------|--------|----------------------------|----------------|-----------------------------|--------------------|--|--|--|

| Without Fine-tuning: Zero shot |                                       |        |                            |                |                             |                    |  |  |  |

| Llama-3.1-8B                   | base                                  | 1      | 0.16                       | 0.00 (0/36)    | 0.0000                      | 36                 |  |  |  |

| Llama-3.1-8B                   | instruct                              | 1      | 0.00                       | 0.00 (0/36)    | 0.0000                      | 36                 |  |  |  |

| GPT                            | 40                                    | 1      | 0.01                       | 0.00 (0/49)    | 0.0000                      | 49                 |  |  |  |

| Llama-3.1-8B                   | base                                  | 2      | 0.00                       | 0.00 (0/36)    | 0.0000                      | 36                 |  |  |  |

| Llama-3.1-8B                   | instruct                              | 2      | 3.08                       | 25.00 (9/36)   | 0.2622                      | 36                 |  |  |  |

| GPT                            | 40                                    | 2      | 0.00                       | 0.00 (0/49)    | 0.0000                      | 49                 |  |  |  |

| Llama-3.1-8B                   | base                                  | 3      | 0.93                       | 0.00 (0/36)    | 0.0000                      | 36                 |  |  |  |

| Llama-3.1-8B                   | instruct                              | 3      | 4.79                       | 0.00 (0/36)    | 0.0000                      | 36                 |  |  |  |

| GPT                            | 40                                    | 3      | 0.05                       | 0.00 (0/49)    | 0.0000                      | 49                 |  |  |  |

|                                | Without Fine-tuning: One-shot         |        |                            |                |                             |                    |  |  |  |

| Llama-3.1-8B                   | base                                  | 4      | 9.08                       | 0.00 (0/32)    | 0.0000                      | 32                 |  |  |  |

| Llama-3.1-8B                   | instruct                              | 4      | 47.55                      | 0.00 (0/32)    | 0.0000                      | 32                 |  |  |  |

| GPT                            | 40                                    | 4      | 16.18                      | 24.49 (12/49)  | 0.3221                      | 49                 |  |  |  |

| Llama-3.1-8B                   | base                                  | 5      | 7.55                       | 0.00 (0/32)    | 0.0000                      | 32                 |  |  |  |

| Llama-3.1-8B                   | instruct                              | 5      | 48.99                      | 0.00 (0/32)    | 0.0000                      | 32                 |  |  |  |

| GPT                            | 40                                    | 5      | 21.96                      | 26.53 (13/49)  | 0.1751                      | 49                 |  |  |  |

|                                | Fine-tuned: epoch 7 & 9, respectively |        |                            |                |                             |                    |  |  |  |

| Schemato                       | instruct                              | 2      | 69.90                      | 86.11 (31/36)  | 0.7272                      | 36                 |  |  |  |

| Schemato                       | instruct                              | 4      | 65.04                      | 93.75 (30/32)  | 1.0000                      | 32                 |  |  |  |

we could combine two schematics into a new one using a technique similar to mixup used in vision [28]. To improve the generalizability of *Schemato* to large and unseen circuit classes, we plan to investigate the decomposition of larger circuits into smaller, more manageable subcircuits, thereby enhancing the ability of the model to learn hierarchical structures and the interplay between subcircuits. A second limitation of our current work is that the image-based evaluation metric does not consider the circuits' topological structure and is highly sensitive to absolute locations of circuit components in the image. This resulted in the very small maximum MSSIM values and may lead to an unfair comparison between the reference and generated schematics. A possible direction to address this is to investigate the use of graph representations and graph-based metrics that capture the topological information from the generated schematic. We intend to pursue these directions in the future.

#### REFERENCES

- [1] K. Kunal, T. Dhar, M. Madhusudan, J. Poojary, A. K. Sharma, W. Xu, S. M. Burns, J. Hu, R. Harjani, and S. S. Sapatnekar, "GANA: graph convolutional network based automated netlist annotation for analog circuits," in 2020 Design, Automation & Test in Europe Conference & Exhibition, DATE 2020, Grenoble, France, March 9-13, 2020. IEEE, 2020, pp. 55–60. [Online]. Available: https://doi.org/10.23919/DATE48585.2020.9116329

- [2] W. Cao, M. Benosman, X. Zhang, and R. Ma, "Domain knowledgeinfused deep learning for automated analog/radio-frequency circuit parameter optimization," in *Proceedings of the 59th ACM/IEEE Design Automation Conference*, ser. DAC '22. New York, NY, USA: Association for Computing Machinery, 2022, p. 1015–1020. [Online]. Available: https://doi.org/10.1145/3489517.3530501

- [3] K. Kunal, M. Madhusudan, A. K. Sharma, W. Xu, S. M. Burns, R. Harjani, J. Hu, D. A. Kirkpatrick, and S. S. Sapatnekar, "Invited: Align – open-source analog layout automation from the ground up," in 2019 56th ACM/IEEE Design Automation Conference (DAC), 2019, pp. 1–4.

- [4] Y. Yin, Y. Wang, B. Xu, and P. Li, "Ado-Ilm: Analog design bayesian optimization with in-context learning of large language models," *ArXiv*, vol. abs/2406.18770, 2024. [Online]. Available: https://api.semanticscholar.org/CorpusID:270765055

- [5] W. Cao, M. Benosman, X. Zhang, and R. Ma, "Domain knowledgeinfused deep learning for automated analog/radio-frequency circuit parameter optimization," in *Proceedings of the 59th ACM/IEEE Design Automation Conference*, ser. DAC '22. New York, NY, USA: Association for Computing Machinery, 2022, p. 1015–1020. [Online]. Available: https://doi.org/10.1145/3489517.3530501

- [6] K. Settaluri, A. Haj-Ali, Q. Huang, K. Hakhamaneshi, and B. Nikolic, "Autockt: Deep reinforcement learning of analog circuit designs," in 2020 Design, Automation & Test in Europe Conference & Exhibition, DATE 2020, Grenoble, France, March 9-13, 2020. IEEE, 2020, pp. 490–495. [Online]. Available: https://doi.org/10.23919/DATE48585. 2020.9116200

- [7] Z. Zhao and L. Zhang, "Analog integrated circuit topology synthesis with deep reinforcement learning," *IEEE Trans. Comput. Aided Des. Integr. Circuits Syst.*, vol. 41, no. 12, pp. 5138–5151, 2022. [Online]. Available: https://doi.org/10.1109/TCAD.2022.3153437

- [8] T. C. Project, "Circuitikz a tikz library to draw electrical networks," https://github.com/circuitikz/circuitikz, 2023, version 1.5.1. [Online]. Available: https://github.com/circuitikz/circuitikz

- [9] OpenAI and et al., "Gpt-4 technical report," 2024. [Online]. Available: https://arxiv.org/abs/2303.08774

- [10] A. Dubey and et al., "The llama 3 herd of models," 2024. [Online]. Available: https://arxiv.org/abs/2407.21783

- [11] R. Qiu, G. L. Zhang, R. Drechsler, U. Schlichtmann, and B. Li, "Autobench: Automatic testbench generation and evaluation using llms for HDL design," in *Proceedings of the 2024 ACM/IEEE International Symposium on Machine Learning for CAD, MLCAD 2024, Salt Lake City, UT, USA, September 9-11, 2024,* H. Amrouch, J. Hu, S. Garg, and Y. Lin, Eds. ACM, 2024, pp. 18:1–18:10. [Online]. Available: https://doi.org/10.1145/3670474.3685956

- [12] P. Vijayaraghavan, A. Nitsure, C. Mackin, L. Shi, S. Ambrogio, A. Haran, V. Paruthi, A. Elzein, D. Coops, D. Beymer, T. Baldwin, and E. Degan, "Chain-of-descriptions: Improving code llms for vhdl code generation and summarization," in 2024 ACM/IEEE 6th Symposium on Machine Learning for CAD (MLCAD), 2024, pp. 1–10.

- [13] A. Ayalasomayajula, R. Guo, J. Zhou, S. K. Saha, and F. Farahmandi, "Lasp: Llm assisted security property generation for soc verification," in 2024 ACM/IEEE 6th Symposium on Machine Learning for CAD (MLCAD), 2024, pp. 1–7.

- [14] C. Chang, Y. Shen, S. Fan, J. Li, S. Zhang, N. Cao, Y. Chen, and X. Zhang, "Lamagic: Language-model-based topology generation for analog integrated circuits," in *Forty-first International Conference* on Machine Learning, ICML 2024, Vienna, Austria, July 21-27, 2024. OpenReview.net, 2024. [Online]. Available: https://openreview. net/forum?id=MjGCD8wk1k

- [15] Y. Lai, S. Lee, G. Chen, S. Poddar, M. Hu, D. Z. Pan, and P. Luo, "Analogcoder: Analog circuit design via training-free code generation," 2024.

- [16] B. Naveen and K. Raghunathan, "An automatic netlist-to-schematic generator," *IEEE Design & Test of Computers*, vol. 10, no. 1, pp. 36–41, 1993.

- [17] C. Lageweg, "Designing an automatic schematic generator for a netlist description," *Delft University of Technology, Delft, Netherlands, Tech. Rep*, 1998.

- [18] B. Arsintescu, "A method for analog circuits visualization," in *Proceedings of the International Conference on Computer Design (ICCD)*, 1996, pp. 454–459.

- [19] Lee and McNamee, "Aesthetic routing for transistor schematics," in 1992 IEEE/ACM International Conference on Computer-Aided Design. IEEE, 1992, pp. 35–38.

- [20] H.-Y. Hsu and M. P.-H. Lin, "Automatic analog schematic diagram generation based on building block classification and reinforcement learning," in *Proceedings of the 2022 ACM/IEEE Workshop on Machine Learning for CAD*, 2022, pp. 43–48.

- [21] J. Wei and X. al., "Chain of thought prompting elicits reasoning in large language models," *CoRR*, vol. abs/2201.11903, 2022. [Online]. Available: https://arxiv.org/abs/2201.11903

- [22] A. Devices, "Ltspice simulator," accessed November 15, 2024. [Online]. Available: https://www.analog.com/en/resources/ design-tools-and-calculators/ltspice-simulator.html

- [23] torchtune maintainers and contributors, "torchtune: Pytorch's finetuning library," Apr. 2024. [Online]. Available: https//github.com/pytorch/ torchtune

- [24] Y. Zhao, A. Gu, R. Varma, L. Luo, C.-C. Huang, M. Xu, L. Wright, H. Shojanazeri, M. Ott, S. Shleifer, A. Desmaison, C. Balioglu, P. Damania, B. Nguyen, G. Chauhan, Y. Hao, A. Mathews, and S. Li, "Pytorch fsdp: Experiences on scaling fully sharded data parallel," 2023. [Online]. Available: https://arxiv.org/abs/2304.11277

- [25] K. Papineni, S. Roukos, T. Ward, and W.-J. Zhu, "Bleu: a method for automatic evaluation of machine translation," in *Proceedings of the* 40th Annual Meeting on Association for Computational Linguistics, ser. ACL '02. USA: Association for Computational Linguistics, 2002, p. 311–318. [Online]. Available: https://doi.org/10.3115/1073083.1073135

- [26] S. Ren, D. Guo, S. Lu, L. Zhou, S. Liu, D. Tang, N. Sundaresan, M. Zhou, A. Blanco, and S. Ma, "Codebleu: a method for automatic evaluation of code synthesis," 2020. [Online]. Available: https://arxiv.org/abs/2009.10297

- [27] Z. Wang, A. Bovik, H. Sheikh, and E. Simoncelli, "Image quality assessment: from error visibility to structural similarity," *IEEE Transactions* on *Image Processing*, vol. 13, no. 4, pp. 600–612, 2004.

- [28] H. Zhang, M. Cisse, Y. N. Dauphin, and D. Lopez-Paz, "mixup: Beyond empirical risk minimization," 2018. [Online]. Available: https://arxiv.org/abs/1710.09412