# AICircuit: A Multi-Level Dataset and Benchmark for AI-Driven Analog Integrated Circuit Design

Asal Mehradfar<sup>1</sup> Xuzhe Zhao<sup>2</sup> Yue Niu<sup>1</sup> Sara Babakniya<sup>1</sup> Mahdi Alesheikh<sup>2</sup> Hamidreza Aghasi<sup>2</sup> Salman Avestimehr<sup>1</sup>

<sup>1</sup> University of Southern California <sup>2</sup> University of California, Irvine

#### **Abstract**

Analog and radio-frequency circuit design requires extensive exploration of both circuit topology and parameters to meet specific design criteria like power consumption and bandwidth. Designers must review state-of-the-art topology configurations in the literature and sweep various circuit parameters within each configuration. This design process is highly specialized and time-intensive, particularly as the number of circuit parameters increases and the circuit becomes more complex. Prior research has explored the potential of machine learning to enhance circuit design procedures. However, these studies primarily focus on simple circuits, overlooking the more practical and complex analog and radio-frequency systems. A major obstacle for bearing the power of machine learning in circuit design is the availability of a generic and diverse dataset, along with robust metrics, which are essential for thoroughly evaluating and improving machine learning algorithms in the analog and radio-frequency circuit domain. We present AICircuit, a comprehensive multi-level dataset and benchmark for developing and evaluating ML algorithms in analog and radio-frequency circuit design. AlCircuit comprises seven commonly used basic circuits and two complex wireless transceiver systems composed of multiple circuit blocks, encompassing a wide array of design scenarios encountered in real-world applications. We extensively evaluate various ML algorithms on the dataset, revealing the potential of ML algorithms in learning the mapping from the design specifications to the desired circuit parameters. The data and codebase are open-sourced to advance the development of machine learning in the analog and radio-frequency circuit design domain in the following link: https://github.com/AvestimehrResearchGroup/AICircuit.

# 1 Introduction

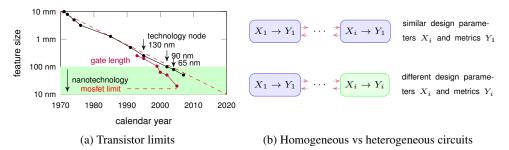

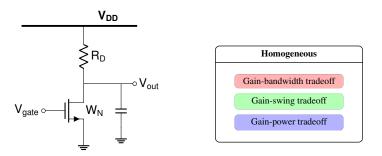

By reaching the limits of Moore's Law [21] in early 2020 (Figure 1a), the exponential scaling of transistors, the core elements in circuit design, has become increasingly difficult, thereby slowing down the pace of advancements in semiconductor technologies. Unlike digital circuits, where scaling can often lead to straightforward performance improvements, analog and radio-frequency circuits should be custom-designed for emerging applications, e.g., mm-wave cellular communications, radar systems, and antenna systems, making their design both time-consuming and resource-intensive [17, 4, 9, 16, 1]. Moreover, the volume of the market for analog integrated circuits is surpassing all other sectors and readily it is the major driving force for the development of semiconductors. By transitioning into the analog domain, two major types of circuits are envisioned: i) homogeneous circuits with constituent sub-circuits with similar functions; and ii) heterogeneous circuits where the constituent elements behave differently and have non-identical performance metrics. Most mm-wave systems of interest are heterogeneous, and their constituent circuit blocks of various functionalities should be combined to achieve *system level* performance metrics that meet the thresholds. It is challenging to obtain the optimal design points due to two fundamental reasons: 1) the performance

of a circuit block, when operated individually, is different from when it is inside a system due to interaction among the circuit blocks; 2) various system-level metrics rely on the metrics of individual circuits in different ways, causing trade-off among the metrics.

Figure 1: The advances in analog and mm-wave circuit design. (a) The limits of transistor scaling predicted by Moore's law; (b) Comparison between homogeneous and heterogeneous circuits.

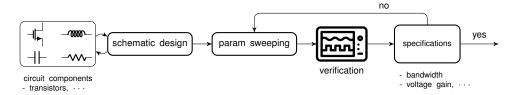

Conventional analog circuit design typically requires considerable effort and human involvement when searching the design space, including circuit topology and each circuit's parameters. Given a set of design specifications (e.g., power consumption, bandwidth, etc.), designers usually need first to decide the circuit topology and then conduct *circuit sizing* (i.e., parameter sweeping on each individual component), as shown in Figure 2. The process is extremely time-consuming when the circuit comprises a large number of components. Among all the phases within the design of analog circuits, the complete schematic-level design is the most time-consuming part which is currently handled by human experts in industry and academia in a temporally inefficient manner.

A few prior works investigate machine learning algorithms to automate analog circuit design [22, 11, 5, 15, 25, 6, 7]. In general, these methods train an ML model to learn the mapping between design specifications and actual circuit parameters. [11] shows that a standard neural network trained with carefully filtered design parameters can effectively predict the circuit parameters given design specifications. Methods such as AutoCkt [22] and L2DC [26] further adopt reinforcement learning framework to train neural networks for effective circuit sizing given design specifications. Furthermore, GNN-based methods [25, 27] propose to use a graph neural network to better capture the circuit topology and improve the accuracy of circuit sizing. Methods such as AnGeL [5] try to use neural networks on a homogeneous combination of circuits with identical functions by breaking them down into stages of sub-circuits, thereby shrinking the design space and reducing the training complexity.

Despite progress in the prior works, the current ML-driven design is still in its early stages. In particular, current methods mainly show a proof of concept on homogeneous circuits and systems such as two-stage voltage amplifiers. It still remains unclear how to scale current NN-based solutions on real-world analog systems with different components. In particular, a real-world system usually consists of heterogeneous components that perform different functions, such as a transmitter with an oscillator followed by a power amplifier. Such systems introduce more complex mapping from inputs to outputs and exhibit high non-linearity. Furthermore, a high-quality dataset, that includes various complex circuits, is indispensable as a pivotal element in the ML-assisted circuit design. However, such a dataset is still not developed and accessible in the current ML-assisted circuit design field. Additionally, given the nascent state of ML-assisted circuit design, effective and universal metrics are highly anticipated to assess different ML-assisted solutions.

In this work, we first introduce AICircuit, a multi-level circuit dataset and benchmark for training ML algorithms to assist various types of analog circuit design. In particular, the dataset consists of seven pivotal analog and radio-frequency circuits: common-source voltage amplifier, two-stage voltage amplifier, cascode voltage amplifier, low-noise amplifier, power amplifier, voltage-controlled oscillator, and mixer. In addition, the dataset also consists of complex heterogeneous systems with multiple cascaded circuit components, which has not been investigated in prior works. AICircuit is a comprehensive collection of circuit parameters and simulated performance metrics from an accurate commercial simulator, including advanced metrics not seen in any prior works. Hence, it can serve as a foundation for developing robust ML models for analog and radio-frequency circuit design. In addition to the dataset, we also conduct comprehensive evaluations on the benchmark dataset using

Figure 2: Conventional procedure of analog circuit design, which involves tremendous efforts to sweep in the parameter space to find the optimal design given design specifications. The design space contains possible parameters such as transistors, resistors, etc. Design specifications contain power consumption, bandwidth, etc.

various models. The models evaluated range from conventional machine learning algorithms, such as random forest, to modern neural networks. The evaluations show that on the benchmark dataset, ML algorithms have the potential to learn circuit design with relatively small errors compared to design specifications.

# 2 Problem Statement

In this work, we investigate the capabilities of machine learning algorithms in automating analog and radio-frequency circuit design. In particular, we evaluate machine learning algorithms on *homogeneous* and *heterogeneous* circuits. We define homogeneous circuits that compromise multiple circuits with identical functions. For instance, a two-stage voltage amplifier can be seen as a homogeneous circuit with two cascaded single-stage voltage amplifiers (Fig 15). On the other hand, we define heterogeneous circuits that compromise multiple circuit blocks with different functions, such as a transmitter with a voltage-controlled oscillator and a power amplifier (Fig 4a).

Machine Learning-Assisted Design. ML-assisted design usually adopts a reversed design flow compared to conventional circuit design. In particular, ML-assisted design takes a performance metric vector, y, as inputs and uses a machine learning model  $\mathcal{M}$  to predict a set of circuit parameters x as

$$x = \mathcal{M}(y), \tag{1}$$

The performance vector, y, may contain DC power consumption, bandwidth, voltage gain, etc, which varies with circuit types. On the other hand, the circuit parameter vector, x, describes the quantitative values of every component within the circuit, including resistances, capacitances, transistor widths, etc. Compared to conventional circuit design, ML-assisted methods directly learn the mapping from design specifications to circuit parameters, eliminating the need for parameter sweeping on x to find the solutions that meet the design specification in y. Therefore, the whole design process can be significantly simplified.

Various ML models such as multilayer perceptrons (MLPs), transformers, and conventional methods such as decision trees can be used to model the mapping from inputs to outputs. Simple circuits, such as a common-source voltage amplifier, can be modeled with small models. However, large circuit systems with high non-linearity require more complex models. As a key contribution in this work, we investigate the performance of different models on diverse circuits, ranging from a basic common-source amplifier to complex systems such as a transmitter with multiple heterogeneous circuit blocks.

# 3 Dataset

In this section, we present our dataset collection procedure. AICircuit consists of two types of circuits: homogeneous circuits and heterogeneous circuits. A homogeneous circuit only consists of one type of circuit, such as a common-source voltage amplifier. Heterongeneous circuits may consist of two or more types of circuit blocks with different functions, such as a transmitter with a voltage-controlled oscillator (VCO) and a power amplifier (PA).

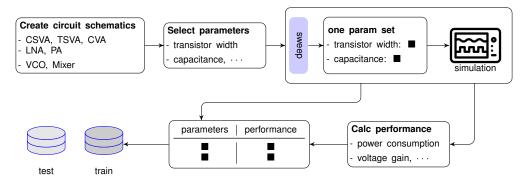

For all circuits, we adopt the procedure as in Figure 3 to generate data. For a circuit, we first design a schematic using Cadence tools [14]. We defer details of circuit schematics in Appendix A. We then identify all key circuit parameters in the schematic that can affect the circuit performance. For each parameter, we set a value range, [beg, end], and sweep the value with a small step size. For each

parameter set, we run a Cadence simulator to obtain the simulation results and calculate performance metrics. Each parameter set and the corresponding performance will be saved as one row in the dataset. After sweeping all parameters, we obtain a dataset with all possible design points. As last, we split the dataset into train and test sets for ML model training and testing.

Figure 3: Procedure for creating datasets for commonly used analog circuits, including homogeneous and heterogeneous circuits.

## 3.1 Datasets for Homogeneous Circuit Blocks

We collect seven commonly used analog and radio-frequency circuits: common-source voltage amplifier (CSVA), cascode voltage amplifier (CVA), two-stage voltage amplifier (TSVA), low-noise amplifier (LNA), mixer, voltage-controlled oscillator (VCO), and power amplifier (PA). Schematics of these circuits are provided in Appendix A. These homogeneous circuits are the building units that are seen in real-world complex heterogeneous systems.

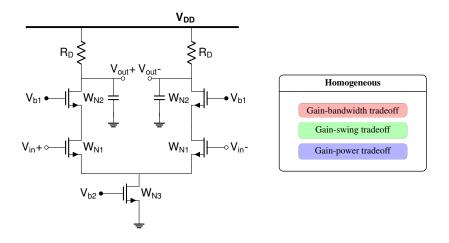

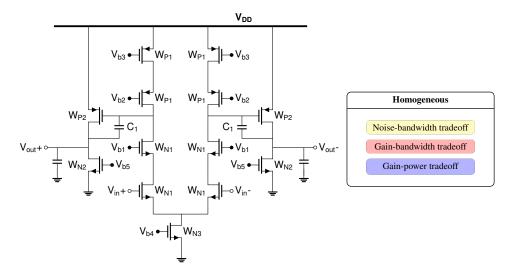

Among these circuits, the analog voltage amplifiers, including the common-source voltage amplifier (CSVA), cascode voltage amplifier (CVA), and two-stage voltage amplifier (TSVA), are essential for voltage amplification, a critical function in most analog circuits and feedback systems [20]. CSVA is a versatile and widely used component in analog and radio-frequency circuit design. It receives input at the *gate* terminal and generates amplified output at the *drain* terminal (See Figure 13). By combining the *common-source* (CS) and *common-gate* (CG) stages, CVA can provide enhanced gain and improved bandwidth over CSVA, which is suitable for high-frequency applications (Figure 14). TSVA further improves the output swings in the cascode configuration and obtains high gains (Figure 15).

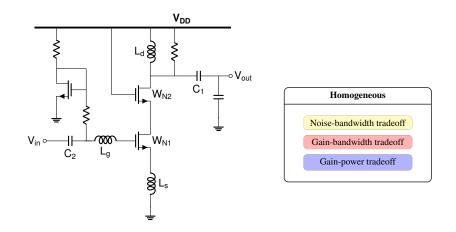

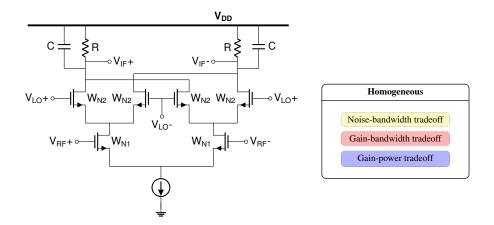

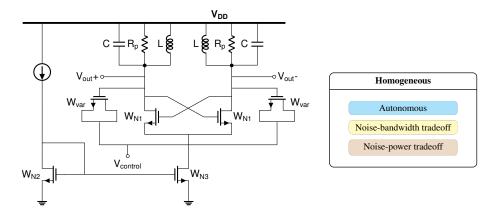

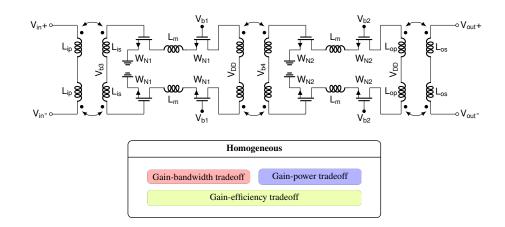

In addition to voltage amplifiers, the dataset also covers other types of circuits in radio-frequency applications, including the low-noise amplifier (LNA), mixer, voltage-controlled oscillator (VCO), and power amplifier (PA). In particular, the cascode LNA in a radio-frequency receiver front-end provides substantial power gain while maintaining low noise across a wide bandwidth range (Figure 16). An active mixer is used for frequency modulation with conversion gain in radio-frequency transmitters and receivers. VCO generates a periodic signal with frequency tuned across a wide range controlled by a voltage signal. Owing to the low phase noise and power consumption, the cross-coupled VCO has become a prevalent configuration to provide sustainable oscillation (Figure 18). The two-stage differential PA, the most power-intensive building block in the radio-frequency transmitter, plays a crucial role in delivering significant power to the transmitting antenna without compromising efficiency (Figure 19).

For each circuit, we select several circuit parameters that can greatly affect the design performance, as listed in Table 2. Based on the complexity of each circuit, a different number of parameters are considered in the simulation. The channel length of each transistor is fixed at 45 nm to simplify the design space and mitigate short-channel effects. These parameters are also the targets that an ML algorithm needs to predict given design specifications.

# 3.2 Datasets for Complex Heterogeneous Systems

In addition to basic homogeneous circuits, the work further investigates complex real-world millimeter-wave (mm-wave) circuit systems that contain multiple circuit blocks with different func-

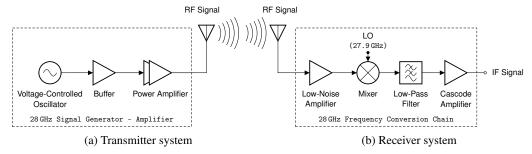

Figure 4: 28 GHz wireless transceiver circuits. (a) Transmitter architecture involving VCO and PA. Buffer used here to sustain system stability; (b) Receiver architecture comprising LNA, Mixer, and CVA. Low-Pass Filter deployed here to filter out the undesired high frequency components.

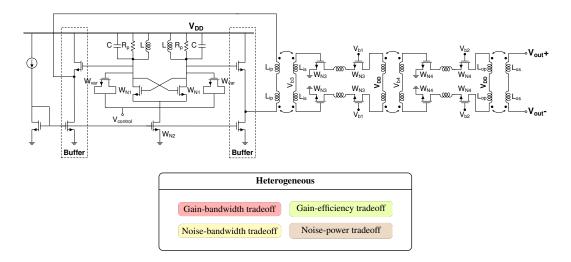

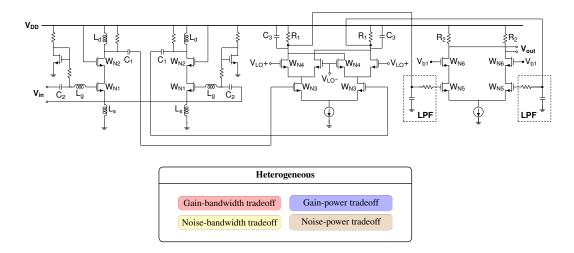

tions, as illustrated in Figure 4 [8]. In particular, we investigate a transmitter and a receiver operating at 28 GHz, which are commonly used in high-speed communication systems for sending and receiving mm-wave signals [13].

For a transmitter, we combine the voltage-controlled oscillator (VCO) and power amplifier (PA) as a typical *signal generator* – *amplifier* system (Figure 4a) [19]. The system first generates a periodic signal via a VCO with tunable frequency, and then amplifies the signal by the PA with substantial power gain. For a receiver, we establish a classical *frequency conversion* chain by integrating the low-noise amplifier (LNA) with a mixer and cascode voltage amplifier (CVA) (Figure 4b) [12]. With a signal received from an antenna, an LNA is first applied to amplify the weak input signal without introducing undesired noise. Then, a mixer is involved in converting the signal from radio frequency to intermediate frequency (IF) [18]. The output IF signal is then amplified by a CVA that serves as an IF amplifier for further processing. There are two additional blocks, buffer and low-pass filter, shown in the transmitter and receiver. As their topology and parameters are usually fixed, we do not optimize them in the pipeline. Table 1 lists design parameters to be optimized and the performance metrics to be examined.

Compared to basic homogeneous circuits, these heterogeneous circuits comprise a large parameter space to be optimized. Moreover, these systems exhibit increased non-linearity and intricate trade-offs between each block, leading to further challenges in learning the mapping from performance metrics to design parameters.

# 4 Evaluations

With the dataset collected from diverse circuits and complex radio-frequency systems, in this section, we train and evaluate multiple ML algorithms on the dataset and investigate their strengths and weaknesses.

Models. We test five different models: multi-layer perceptrons (MLPs), Transformers, support vector regression (SVRs), random forest (RF), and K-nearest neighbors (KNNs). For all models, we feed the model with performance metrics and let the model predict the design parameters. In particular, MLPs/Transformers/SVRs act as a mapping function from input metrics to output design parameters, while KNNs locate the design parameters with performance close to input metrics. In addition, RF regressors [2] combine the predictions from multiple decision trees and output the mean of their predictions to create a more accurate and stable prediction. The transformer model [23] with the implementation based on [3], consists of one embedding layer, several encoder layers, and one fully connected layer for predicting a vector of circuit parameters. The multi-layer perception (MLP) model consists of seven fully connected layers, each intermediate layer having a rectified linear unit (ReLU) activation function. For support vector regressor (SVR), considering that SVR is a single-output regressor, we create multiple SVRs to predict all the circuit parameters. In particular, we fit one SVR per target parameter. To enhance non-linearity, we adopt the rbf kernel [24] for each SVR model. Details of each model are provided in Appendix B.

**Metrics**. In model training, we use  $\ell_1$  loss as the objective function that measures the distance between the predicted parameters and the desired parameters. In model evaluation, we further run a

Cadence simulator given the predicted parameters and obtain the performance,  $\hat{y}$ . We calculate the relative error compared to the desired performance specified in the dataset, y. We report an individual error on each metric as

ith metric:

$$err_i = ||\boldsymbol{y}_i - \hat{\boldsymbol{y}}_i||/\boldsymbol{y}_i$$

(2)

**End-to-End Training and Evaluation**. Our codebase provides an end-to-end model training and evaluation pipeline, as shown in Figure 5. It enables a smooth interaction between the ML workflow and the analog circuit workflow. During the training stage, we simply follow the standard ML workflow to load data and train the model. During the evaluation phase, we first obtain the predicted parameters via the ML workflow and then call Cadence simulator to compute the actual performance and the relative error compared to the desired value. Importantly, by including a Cadence simulator in the evaluation pipeline, we can accurately obtain metrics with inherent randomness based on advanced analyses, such as the noise figure in a low-noise amplifier and the phase noise in a voltage-controlled oscillator, which were not seen in prior works. More details are provided in Table 2 and 1.

```

train

evaluation

simulation

def Eval(model, evalset, simulator):

for _ in range(maxIter):

x, y = loadData(evalset)

xPred = model(y)

class Simulator():

def Train(model, trainset):

for _ in range(maxIter):

x, y = loadData(trainset)

def run(self. xPred):

xPred = model(y)

# circuit workflow

alterCircParam(xPred)

loss = calcLoss(x, xPred)

# update model

# simulator: simulator class with all circuit information

call Cadence simulator

call (cadenceCommand)

model.fit(x, y)

yPred = simulator.run(xPred)

vPred = parseResults()

error = calcError(y, yPred)

```

Figure 5: An end-to-end model training and evaluation pipeline.

As the performance metrics and parameters targeted by the models have different ranges, we first apply the preprocessing and normalize the data to [-1,1]. For training data splitting, we randomly sample 90 percent of the data points as the training dataset, and 10 percent as the test dataset. We train the neural networks (transformer and MLP) for 100 epochs using the Adam optimizer [10] with a learning rate of 0.001. Each training is conducted several times to ensure that our methods are robust to random seeds.

#### 4.1 Homogeneous Circuit Blocks

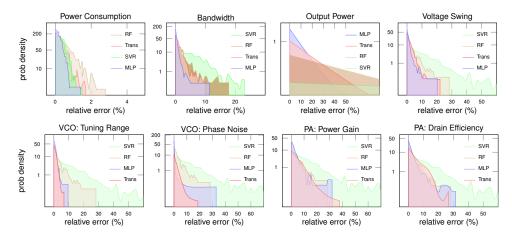

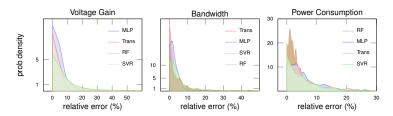

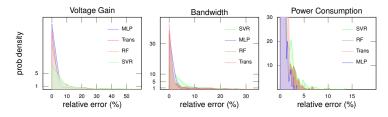

We first evaluate ML algorithms on homogeneous circuits. In particular, we show the results of MLP, Transformer, SVR, and RF on a two-stage voltage amplifier (TSVA), Mixer, voltage-controlled oscillator (VCO), and a power amplifier (PA) in the main paper, and defer other results of other circuits in Appendix D.

To better present the results, we plot the distribution of relative errors (See Eq(2)) of all metrics. We can directly evaluate different ML algorithms by comparing their error distributions in the same plot. We'll begin by presenting the results of each individual circuit, followed by a discussion of some common observations across all circuits.

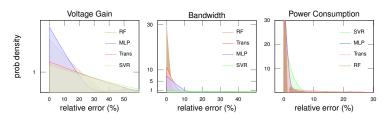

**Two-Stage Voltage Amplifier (TSVA)**. We can observe that all four algorithms can give a design with small errors on the DC power consumption. The reason is that the mapping from circuit parameters to power consumption is easy to predict. However for other metrics, some models fail. For instance, SVR models always generate circuits with large errors on the bandwidth. For the voltage gain, circuits predicted by all four models have large relative errors compared to the desired specifications.

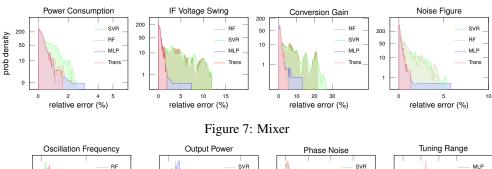

**Mixer**. First we observe similar performance on the DC power consumption. All models generate circuits with very small errors on power consumption. However, advanced models such as MLPs and Transformers perform better on complex metrics. In particular, for the conversion gain, circuits predicted by MLPs and transformers result in  $\leq 10\%$  error, which is significantly lower than SVR and RF.

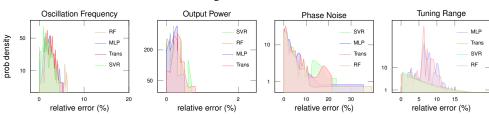

**Voltage-Controlled Oscillator (VCO)**. We observe that all four models generate circuits with small errors on all metrics except phase noise. Even MLPs, that perform well on other circuits, result in a long error tail on the phase noise. The reason is that the mapping from circuit parameters to phase noise is highly non-linear, which makes it difficult for all models to learn the relationship.

Figure 6: Two-Stage Voltage Amplifier

Figure 8: Voltage-Controlled Oscillator

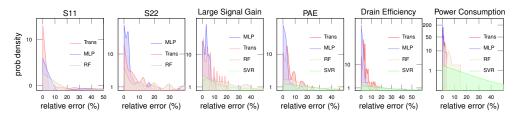

**Power Amplifier (PA)**. A power amplifier is one of the most complex circuits, a complexity that is reflected in the obtained results. Exception for the DC power consumption, all other metrics observe long error tails for all four models. In particular, the circuits predicted by SVR diverge significantly on the metrics of  $S_{11}$  and  $S_{22}$ . Therefore, we did not include them in the figure.

Figure 9: Power Amplifier

**Summary**. Across all circuits examined in this section, we observe that ML models perform well in learning the relationship between circuit parameters and simple performance metrics such as the DC power consumption. Importantly, the observation holds regardless of the complexity of the circuits. The reason is that the simple performance metrics usually exhibit a linear relation with circuit parameters, which makes it easy to predict. However, as the relationship becomes more non-linear, learning the relationships tends to be more challenging, even for MLPs and Transformers. For instance, voltage gain in a two-stage voltage amplifier, conversion gain in a mixer, phase noise in VCO, and performance metrics in PA are highly non-linear in relation to the circuit parameters. As a result, circuits predicted by ML models do not result in performance very close to the desired specifications.

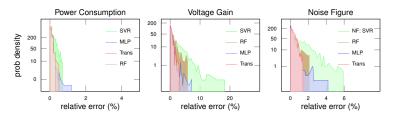

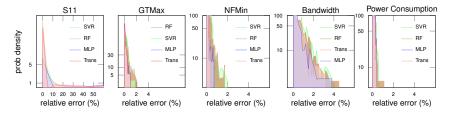

#### 4.2 Heterogeneous Radio-Frequency Systems

Moving from homogenous circuits to heterogenous ones, the number of performance metrics and circuit parameters increases. Furthermore, as heterogeneous circuits comprise multiple circuits,

the relationship between circuit parameters and performance is further complicated. Therefore, evaluations on heterogeneous circuits provide more insights into how ML algorithms learn to predict complex circuits.

**Transmitter**. In a transmitter system comprising VCO and PA, we can observe that as the circuit becomes more complex, circuit parameters are harder to predict to meet the desired specification. Models such as SVR and RF lack sufficient capacity to predict complex systems, resulting in large errors. MLPs and transformers, on the other hand, predict circuits with much smaller errors. However, they still struggle to give a design that meets certain complex specifications, such as output power.

For the metrics of individual components, circuits predicted by MLPs and transformers still result in smaller errors compared to SVRs and RF. One interesting observation is that, as more performance metrics are involved in learning a heterogeneous circuit, the trained models can generate circuits with small errors on individual metrics (e.g., the tuning range of VCO compared to Fig 8).

Figure 10: Transmitter (VCO and PA). Top row: system-level metrics; bottom row: metrics for individual components.

**Receiver.** We further evaluate ML models on a receiver system comprising an LNA, a mixer, and a cascode voltage amplifier. Compared to the transmitter system, circuits in the receiver are less complex. Therefore, models such as MLPs and transmitters can predict circuits with smaller errors compared to the desired specifications. Besides, since the training dataset of the receiver includes more circuit parameters than the transmitter, the trained models exhibit better generalization performance with more training data points.

Figure 11: Receiver (LNA, Mixer, and Cascode)

**Summary**. Throughout the evaluations on a transmitter and a receiver system, we can observe how the performance of ML algorithms is affected by the complexity of circuits. From a receiver to a transmitter, the relationship between circuit parameters and the performance becomes more non-linear. As a result, it is more challenging to predict a circuit that meets design specifications.

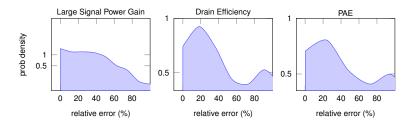

#### 4.3 Learning from Homogeneous to Heterogeneous Circuits

Some prior works argue that models trained on small circuits can be extended to large complex circuits [5]. However, we want to point out that it does not apply to heterogeneous circuits. As we revealed in Figure 12, training an ML model on an individual circuit that is a part of a complex system

results in a much worse learning result. In particular, by training an MLP model with PA-related metrics, we simulate the transmitter system and only calculate the error distribution on PA's metrics. We observe that the predicted circuits behave differently as specified in the datasets, resulting in large errors compared to the desired values. The rationale behind this is that a PA within a transmitter system operates at a different point than when it operates independently, due to the load effects caused by other circuits in the system. Therefore, a model that simply learns a circuit alone cannot generalize well on a large system.

Figure 12: Performance of MLP on PA in a transmitter using only PA-related metrics. The accuracy is significantly affected by the limited number of metrics and the effects of circuits in the transmitter.

#### 5 Conclusion

In this work, we propose a multi-level benchmark dataset for analog and radio-frequency circuit design. The proposed dataset, AICircuit, covers homogeneous and heterogeneous circuits. Homogeneous circuits comprise one or multiple circuits with identical functions, while heterogeneous circuits comprise circuits with different functions. We evaluate various machine learning algorithms on the benchmark datasets, including multi-layer perceptrons (MLPs), transformers, and support vector regression (SVRs). The evaluations provide a comprehensive overview of the strengths and weaknesses of each method. In a word, MLPs and Transformers usually give better designs compared to other methods, especially for complex circuits. We also reveal that for complex circuits, further optimization of model design and training are still needed to improve the design.

Heterogeneous circuits investigated in the paper only cover typical radio-frequency transmitter and receiver systems. However, we will consider extending our research to other complex systems.

#### References

- [1] Phillip E Allen and Douglas R Holberg. CMOS analog circuit design. Elsevier, 2011.

- [2] Leo Breiman. Random forests. *Machine learning*, 45:5–32, 2001.

- [3] Jacob Devlin, Ming-Wei Chang, Kenton Lee, and Kristina Toutanova. Bert: Pre-training of deep bidirectional transformers for language understanding, 2019.

- [4] Sayed Hossein Dokhanchi, Bhavani Shankar Mysore, Kumar Vijay Mishra, and Björn Ottersten. A mmwave automotive joint radar-communications system. *IEEE Transactions on Aerospace and Electronic Systems*, 55(3):1241–1260, 2019.

- [5] Morteza Fayazi, Morteza Tavakoli Taba, Ehsan Afshari, and Ronald Dreslinski. Angel: Fully-automated analog circuit generator using a neural network assisted semi-supervised learning approach. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 2023.

- [6] Kourosh Hakhamaneshi, Nick Werblun, Pieter Abbeel, and Vladimir Stojanović. Analog circuit generator based on deep neural network enhanced combinatorial optimization. In *Proceedings of the 56th Annual Design Automation Conference 2019*, pages 1–2, 2019.

- [7] Kourosh Hakhamaneshi, Nick Werblun, Pieter Abbeel, and Vladimir Stojanović. Bagnet: Berkeley analog generator with layout optimizer boosted with deep neural networks. In 2019 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), pages 1–8. IEEE, 2019.

- [8] Wei Hong, Zhi Hao Jiang, Chao Yu, Debin Hou, Haiming Wang, Chong Guo, Yun Hu, Le Kuai, Yingrui Yu, Zhengbo Jiang, Zhe Chen, Jixin Chen, Zhiqiang Yu, Jianfeng Zhai, Nianzu Zhang,

- Ling Tian, Fan Wu, Guangqi Yang, Zhang-Cheng Hao, and Jian Yi Zhou. The role of millimeter-wave technologies in 5g/6g wireless communications. *IEEE Journal of Microwaves*, 1(1):101–122, 2021.

- [9] Wonbin Hong, Kwang-Hyun Baek, Youngju Lee, Yoongeon Kim, and Seung-Tae Ko. Study and prototyping of practically large-scale mmwave antenna systems for 5g cellular devices. *IEEE Communications Magazine*, 52(9):63–69, 2014.

- [10] Diederik P. Kingma and Jimmy Ba. Adam: A method for stochastic optimization, 2017.

- [11] Dmitrii Krylov, Pooya Khajeh, Junhan Ouyang, Thomas Reeves, Tongkai Liu, Hiba Ajmal, Hamidreza Aghasi, and Roy Fox. Learning to design analog circuits to meet threshold specifications. In *Proceedings of the 40th International Conference on Machine Learning*, ICML'23. JMLR.org, 2023.

- [12] Xiaopeng Li and Mohammed Ismail. *Multi-Standard CMOS Wireless Receivers: Analysis and Design*. Springer US, 2002.

- [13] Xuyang Liu, Md Hedayatullah Maktoomi, Mahdi Alesheikh, Payam Heydari, and Hamidreza Aghasi. A 49-63 ghz phase-locked fmcw radar transceiver for high resolution applications. In ESSCIRC 2023- IEEE 49th European Solid State Circuits Conference (ESSCIRC), pages 509–512, 2023.

- [14] Antonio J Lopez Martin. Cadence design environment. *New Mexico State University, Tutorial paper*, 35, 2002.

- [15] Rayan Mina, Chadi Jabbour, and George E. Sakr. A review of machine learning techniques in analog integrated circuit design automation. *Electronics*, 11(3), 2022.

- [16] Ateeq Ur Rehman Nazih Khaddaj Mallat, Madeeha Ishtiaq and Amjad Iqbal. Millimeter-wave in the face of 5g communication potential applications. *IETE Journal of Research*, 68(4):2522– 2530, 2022.

- [17] Sundeep Rangan, Theodore S. Rappaport, and Elza Erkip. Millimeter-wave cellular wireless networks: Potentials and challenges. *Proceedings of the IEEE*, 102(3):366–385, 2014.

- [18] Behzad Razavi. Architectures and circuits for rf cmos receivers. In *Proceedings of the IEEE 1998 Custom Integrated Circuits Conference (Cat. No.98CH36143)*, pages 393–400, 1998.

- [19] Behzad Razavi. RF Microelectronics. Prentice Hall Press, USA, 2nd edition, 2011.

- [20] Behzad Razavi. *Design of analog CMOS integrated circuits*. McGraw-Hill Education, New York, NY, second edition edition, 2017.

- [21] Robert R Schaller. Moore's law: past, present and future. IEEE spectrum, 34(6):52-59, 1997.

- [22] Keertana Settaluri, Ameer Haj-Ali, Qijing Huang, Kourosh Hakhamaneshi, and Borivoje Nikolic. Autockt: deep reinforcement learning of analog circuit designs. In *Proceedings of the 23rd Conference on Design, Automation and Test in Europe*, DATE '20, page 490–495, San Jose, CA, USA, 2020. EDA Consortium.

- [23] Ashish Vaswani, Noam Shazeer, and et al. Attention is all you need. *Advances in neural information processing systems*, 30, 2017.

- [24] Jean-Philippe Vert, Koji Tsuda, and Bernhard Schölkopf. 2 a primer on kernel methods. *Kernel Methods in Computational Biology*, page 35, 2004.

- [25] Hanrui Wang, Kuan Wang, Jiacheng Yang, Linxiao Shen, Nan Sun, Hae-Seung Lee, and Song Han. Gcn-rl circuit designer: Transferable transistor sizing with graph neural networks and reinforcement learning. In 2020 57th ACM/IEEE Design Automation Conference (DAC), pages 1–6. IEEE, 2020.

- [26] Hanrui Wang, Jiacheng Yang, Hae-Seung Lee, and Song Han. Learning to design circuits, 2018.

- [27] Guo Zhang, Hao He, and Dina Katabi. Circuit-gnn: Graph neural networks for distributed circuit design. In *International conference on machine learning*, pages 7364–7373. PMLR, 2019.

# A Circuits

In this section, we provide details on the examined homogeneous and heterogeneous circuits in Section 3 and 4. As mentioned in the body of the paper, time-consuming parametric sweeps are necessary for designing analog and radio frequency circuits. Often, a small subset of design parameters can satisfy the thresholds for design metrics. From a circuit design perspective, the limited number of parameter combinations that satisfy the metrics happens due to: 1) complexity of transistor models and the sensitivity of their operation to surrounding circuit elements, circuit configuration, bias conditions, size of the transistor, etc. 2) inherent trade-offs among various design metrics in each circuit. In what follows, for each circuit, in addition to the schematics and set of design parameters and metrics, multiple important design trade-offs are listed within colored boxes adjacent to the schematics. The same color is reserved for a trade-off if it is present in more than one circuit.

Figure 13: Common-Source Voltage Amplifier.

Figure 14: Cascode Voltage Amplifier.

Figure 15: Two-Stage Voltage Amplifier.

Figure 16: Low-Noise Amplifier.

Figure 17: Mixer.

Figure 18: Voltage-Controlled Oscillator.

Figure 19: Power Amplifier.

Figure 20: Heterogeneous system on the transmitter side.

Figure 21: Heterogeneous system on the receiver side.

| <b>Heterogeneous Circuits</b>                                                    | Individual Block                            | Parameter                                        | Sweeping Range         |  |

|----------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------|------------------------|--|

|                                                                                  |                                             | C                                                | 50:50:150 (fF)         |  |

|                                                                                  | V 1                                         | L                                                | 60:60:180 (pH)         |  |

|                                                                                  | Voltage-Controlled Oscillator (VCO)         | $R_p$                                            | $300:100:500(\Omega)$  |  |

| Transmitter System specs:<br>dc power   bandwidth   output power   voltage swing | specs:                                      | $W_{N1}^{r}$                                     | 7.5:2.5:12.5 (µm)      |  |

|                                                                                  | phase noise I tuning range                  | $W_{N2}$                                         | 187.5:12.5:212.5 (µm   |  |

|                                                                                  |                                             | W <sub>var</sub>                                 | 70:10:90 (µm)          |  |

|                                                                                  |                                             | L <sub>ip</sub>                                  | 175:175:350 (pH)       |  |

|                                                                                  | Dayyan Amplifian (DA)                       | Lis                                              | 60:60:120 (pH)         |  |

|                                                                                  | Power Amplifier (PA)                        | Lop                                              | 360:353:713 (pH)       |  |

|                                                                                  | specs:                                      | Los                                              | 45:45:90 (pH)          |  |

|                                                                                  | power gain   drain efficiency   PAE         | $W_{N3}$                                         | 22:5:32 (μm)           |  |

|                                                                                  |                                             | $W_{N4}$                                         | 16:5:26 (μm)           |  |

|                                                                                  |                                             | C <sub>1</sub>                                   | 130:50:180 (fF)        |  |

|                                                                                  |                                             | $C_2$                                            | 170:50:220 (fF)        |  |

|                                                                                  | Low-Noise Amplifier (LNA)                   | $L_d$                                            | 180:50:230 (pH)        |  |

|                                                                                  | specs:                                      | $egin{array}{c} L_{ m g} \ L_{ m s} \end{array}$ | 850:100:950 (pH)       |  |

| Receiver System specs:<br>dc power   gain   noise figure                         | power gain   S <sub>11</sub>   noise figure | $L_{\rm s}$                                      | 80:10:90 (pH)          |  |

|                                                                                  |                                             | $W_{N1}$                                         | 20:3:26 (μm)           |  |

|                                                                                  |                                             | $W_{N2}$                                         | 37.5:2.5:42.5 (μm)     |  |

|                                                                                  | Mixer                                       | C <sub>3</sub>                                   | 1:0.1:1.1 (pF)         |  |

|                                                                                  | specs:                                      | $R_1$                                            | $400:100:500 (\Omega)$ |  |

|                                                                                  | voltage swing   conversion gain             | $W_{N3}$                                         | 14:2:18 (μm)           |  |

|                                                                                  | voltage swing rediversion gain              | $W_{N4}$                                         | 6:2:10 (µm)            |  |

|                                                                                  | Cascode Voltage Amplifier (CVA)             | $R_2$                                            | 300:100:400 (Ω)        |  |

|                                                                                  | specs:                                      | $W_{N5}$                                         | 26:2:30 (µm)           |  |

|                                                                                  | gain                                        | $W_{N6}$                                         | 14:2:18 (µm)           |  |

Table 1: Heterogeneous circuits and the chosen parameters for each block. The sweeping range of selected design parameters is written in the form of [beg, increment, end]. Detailed circuit topology is provided in Appendix A. Specs of each circuit are explained in Appendix C.

| Homogeneous Circuit                                         | Parameter                   | Description                   | Sweeping Range        |  |

|-------------------------------------------------------------|-----------------------------|-------------------------------|-----------------------|--|

| Common-Source Voltage Amplifier (CSVA)                      | V <sub>DD</sub>             | supply voltage                | 1.2:0.1:1.8 (V)       |  |

| specs:                                                      | $V_{gate}$                  | gate voltage                  | 0.6:0.05:0.9 (V)      |  |

| dc power   bandwidth   gain                                 | $R_{\mathrm{D}}$            | load resistor                 | $0.5:0.1:3 (k\Omega)$ |  |

| de power i bandwidth i gani                                 | $\mathbf{W}_{\mathbf{N}}$   | width of nmos                 | 3:1:10 (µm)           |  |

| Cascode Voltage Amplifier (CVA)                             | $R_{\rm D}$                 | load resistor                 | 0.5:0.1:2 (kΩ)        |  |

| specs:                                                      | $W_{N1}$                    | width of nmos                 | 6:1:17 (µm)           |  |

| dc power   bandwidth   gain                                 | $W_{N2}$                    | width of nmos                 | 5:1:12 (μm)           |  |

| de power i bandwiddi i gaini                                | $W_{N3}$                    | width of nmos                 | 4.5:0.5:9 (µm)        |  |

|                                                             | $C_1$                       | miller capacitor              | 150:50:250 (fF)       |  |

| Two-Stage Voltage Amplifier (TSVA)                          | $\mathbf{W}_{\mathrm{Pl}}$  | width of pmos                 | 10:1:18 (μm)          |  |

|                                                             | $\mathbf{W}_{P2}$           | width of pmos                 | 7.5:5:22.5 (µm)       |  |

| specs:                                                      | $W_{N1}$                    | width of nmos                 | 10:1:18 (μm)          |  |

| dc power   bandwidth   gain                                 | $\mathbf{W}_{\mathrm{N2}}$  | width of nmos                 | 7.5:5:22.5 (µm)       |  |

|                                                             | $W_{N3}$                    | width of nmos                 | 16:2:24 (µm)          |  |

|                                                             | C <sub>1</sub>              | output capacitor              | 300:100:600 (fF)      |  |

| Low Noise Amplifor (LNA)                                    | $C_2$                       | input capacitor               | 200:100:500 (fF)      |  |

| Low-Noise Amplifier (LNA)                                   | $L_d$                       | drain inductor                | 3:1:5 (nH)            |  |

| specs:                                                      | $L_{g}$                     | gate inductor                 | 8.4:1:11.4 (nH)       |  |

| dc power   bandwidth   power gain   $S_{11}$   noise figure | Ls                          | source inductor               | 0.6:0.1:0.8 (nH)      |  |

|                                                             | $W_{N1}$                    | width of nmos                 | 25:1.25:30 (µm)       |  |

|                                                             | $W_{N2}$                    | width of nmos                 | 25:1.25:30 (µm)       |  |

| Mixer                                                       | C                           | coupling capacitor            | 0.5:0.1:1.5 (pF)      |  |

| specs:                                                      | R                           | load resistor                 | $200:25:500 (\Omega)$ |  |

| dc power   voltage swing                                    | $W_{N1}$                    | width of nmos                 | 15:1:25 (μm)          |  |

| l conversion gain l noise figure                            | $W_{N2}$                    | width of nmos                 | 5:1:15 (μm)           |  |

|                                                             | C                           | capacitor in resonant tank    | 100:25:200 (fF)       |  |

| Voltage-Controlled Oscillator (VCO)                         | L                           | inductor in resonant tank     | 2:1:6 (nH)            |  |

| specs: dc power   frequency   phase noise   tuning range    | $R_p$                       | parallel resistor             | 1:1:4 (k $\Omega$ )   |  |

|                                                             | $W_{N1}$                    | width of nmos                 | 24:8:56 (µm)          |  |

|                                                             | $W_{N2}$                    | width of nmos                 | 11:1:12 (μm)          |  |

|                                                             | $W_{N3}$                    | width of nmos                 | 96:32:160 (μm)        |  |

|                                                             | $\mathbf{W}_{\mathrm{var}}$ | width of nmos capacitor       | 75:12.5:125 (μm)      |  |

|                                                             | Lip                         | input primary inductor        | 175:175:525 (pH)      |  |

| Power Amplifier (PA)                                        | Lis                         | input secondary inductor      | 40:40:120 (pH)        |  |

| specs:                                                      | L <sub>m</sub>              | inter-stage matching inductor | 87.5:87.5:263 (pH     |  |

| dc power   S <sub>11</sub>   S <sub>22</sub>   power gain   | Lop                         | output primary inductor       | 238:238:714 (pH)      |  |

| PAE   drain efficiency   P <sub>sat</sub>                   | Los                         | output secondary inductor     | 30:30:90 (pH)         |  |

| TAE   Graffi Efficiency   F sat                             | $W_{N1}$                    | width of nmos                 | 16:3:28 (µm)          |  |

|                                                             | $W_{N2}$                    | width of nmos                 | 24:4:40 (µm)          |  |

Table 2: Homogeneous circuits and the chosen parameters for each circuit. The sweeping range of selected design parameters is written in the form of [beg, increment, end]. Detailed circuit topology is provided in Appendix A. Specifications of each circuit are explained in Appendix C.

## **B** Model Details

| Model                               | Parameter                                                  | Description                                | Value                          |  |

|-------------------------------------|------------------------------------------------------------|--------------------------------------------|--------------------------------|--|

|                                     | dim_model                                                  | first fully connected layer dim            | 200                            |  |

| Transformer                         | num_heads                                                  | heads in the multi-head attention models   | 2                              |  |

|                                     | dim_hidden                                                 | load resistor                              | 200                            |  |

|                                     | dropout_p the dropout probability                          |                                            | 0.1                            |  |

|                                     | num_encoder_layers number of layers in transformer encoder |                                            | 6                              |  |

|                                     | activation                                                 | activation function of transformer encoder | relu                           |  |

| Multi Layer Perception (MLP)        | num_layers                                                 | number of fully connected layers           | 7                              |  |

|                                     | dim_layers                                                 | dimension of layers                        | [200, 300, 500, 500, 300, 200] |  |

| Support Vector Regressor (SVR)      | kernel                                                     | kernel type of the algorithm               | rbf                            |  |

|                                     | multi_target_regression_type                               | type of combining multiple SVRs            | MultiOutputRegression          |  |

| K Nearest Neighbors Regressor (KNN) | n_neighbors                                                | number of neighbors                        | 5                              |  |

|                                     | weights                                                    | weight function used in prediction         | uniform                        |  |

| D 1 E (D (DE)                       | n_estimators                                               | number of trees in the forest              | 100                            |  |

| Random Forest Regressor (RF)        | criterion                                                  | function to measure the quality of a split | squared_error ( $l_2$ Loss)    |  |

Table 3: Models and the chosen parameters for each model.

| Circuit      | CSVA | CVA   | TSVA  | LNA | Mixer | VCO   | PA   | Transmitter | Receiver |

|--------------|------|-------|-------|-----|-------|-------|------|-------------|----------|

| Dataset Size | 7.8k | 15.1k | 19.3k | 32k | 17.1k | 13.5k | 5.6k | 95.3k       | 155.4k   |

Table 4: Number of data points for each circuit.

# C Specifications of Each Circuit

In this section, we review the definitions of various performance metrics that are simulated for the homogeneous and heterogeneous circuits in this work.

**Voltage gain** of an amplifier, denoted commonly as  $A_v$ , is the ratio of the output amplified voltage  $V_{out}$  to the input voltage  $V_{in}$  in an amplifier circuit.

$$A_v = \frac{V_{out}}{V_{in}} \tag{3}$$

**Bandwidth** is the range of frequencies over which an amplifier can operate effectively, defined by the difference between the upper and lower cutoff frequencies.

$$BW = f_{high} - f_{low} (4)$$

For amplifiers with low-pass profile, the bandwidth is defined as the frequency at which the dB amount of voltage gain drops from the low-frequency gain by 3 dB.

The total power that the circuit draws from the power supply is known as **power consumption**, and it is calculated as the product of supply voltage and supply current.

$$P = V_{supply} \times I_{supply} \tag{5}$$

Conversion gain is the measure of the signal amplification in a mixer, expressed in decibels, comparing the output signal to the input signal.

$$CG = 20 \log \left(\frac{V_{out}}{V_{in}}\right) dB$$

(6)

**Noise figure** is the ratio of the input signal-to-noise ratio to the output signal-to-noise ratio, expressed in decibels, indicating the noise performance of a low-noise amplifier, mixer, or receiver chain.

$$NF = 10\log\left(\frac{SNR_{in}}{SNR_{out}}\right) dB \tag{7}$$

Intermediate frequency (IF) **voltage swing** refers to the peak-to-peak voltage of the mixer's intermediate frequency signal.

The **oscillation frequency** is the frequency at which the oscillator produces its periodic signal, which is normally controlled by the circuit's inductance and capacitance in an LC-based oscillator.

$$f_{\rm osc} = \frac{1}{2\pi\sqrt{LC}}\tag{8}$$

The power that the oscillator provides to a given load is known as **output power**, and it is computed by dividing the root-mean-square (RMS) output voltage squared by the load resistance.

$$P_{\text{out}} = \frac{V_{\text{out,RMS}}^2}{R_{\text{load}}} \tag{9}$$

**Phase noise** is a measure of the oscillator's frequency stability, representing the noise power in a 1 Hz bandwidth at a specific offset frequency from the carrier, relative to the carrier power, where  $S_{\phi}(f)$  is the phase noise power spectral density.

$$L(f) = 10 \log \left( \frac{S_{\phi}(f)}{2P_{\text{carrier}}} \right) \, \text{dBc/Hz}$$

(10)

The oscillator's **tuning range** is the range of frequencies that it can be adjusted over, measured from maximum to minimum.

$$TR = f_{\text{max}} - f_{\text{min}} \tag{11}$$

$S_{11}$  represents the ratio of the reflected voltage wave to the incident voltage wave at the power amplifier's input, which shows how much of the input signal is reflected.

$$S_{11} = \frac{V_{reflected,1}}{V_{incident,1}} \tag{12}$$

$S_{22}$  represents the ratio of the reflected voltage wave to the incident voltage wave at the power amplifier's output, which shows how much of the output signal is reflected.

$$S_{22} = \frac{V_{reflected,2}}{V_{incident,2}} \tag{13}$$

**Large signal gain** is the ratio of the output power to the input power of the amplifier under large signal conditions.

$$G_{\rm LS} = 20 \log \left( \frac{P_{out}}{P_{in}} \right) \, \mathrm{dB} \tag{14}$$

**Power added efficiency** is the amplifier's efficiency in converting DC power into radio frequency output power while taking input power into account.

$$PAE = \frac{P_{out} - P_{in}}{P_{DC}} \times 100\% \tag{15}$$

**Drain efficiency** is defined as the ratio of radio frequency output power to total DC power consumed by the amplifier.

$$DE = \frac{P_{out}}{P_{DC}} \times 100\% \tag{16}$$

**Saturated power** or Psat denotes the highest possible output power level that a power amplifier can produce upon reaching saturation. Up until this point, increasing the input power further does not significantly increase the output power.

$$P_{\text{sat}}(\text{dBm}) = 10\log_{10}\left(\frac{P_{\text{sat}}(\text{mW})}{1\text{mW}}\right) \tag{17}$$

**Power gain** is a measure of how much a circuit increases the power of a signal from its input to its output.

$$G_P = \frac{P_{\text{out}}}{P_{\text{in}}} \tag{18}$$

Voltage-controlled oscillator's (VCO) output power is the amount of electrical power delivered at

its output terminal. The output power  $P_{\rm out}$  is proportional to the square of the RMS voltage  $V_{\rm rms}$  and the load resistance  $R_{\rm load}$ .

$$P_{\text{out}} = \frac{1}{2} \cdot V_{\text{rms}}^2 \cdot R_{\text{load}} \tag{19}$$

**Transmitter output power** is the amount of electrical power delivered by the transmitter to the antenna for transmission as electromagnetic waves.

$$P_{\text{out}} = P_{\text{in}} \cdot G_t \tag{20}$$

where,  $P_{\text{out}}$  is the transmitter output power.  $P_{\text{in}}$  is the input power to the transmitter, and  $G_t$  is the gain of the transmitter.

**Transducer Gain** ( $G_t$ ) of Low Noise Amplifier (LNA) refers to the ratio of the output signal power to the available input signal power which includes the matching effect as well.

$$G_T = \frac{P_{\text{out}}}{P_{\text{in}}} \tag{21}$$

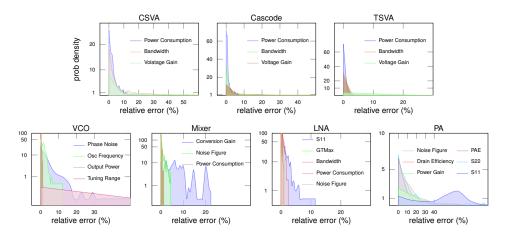

# **D** Results on More Circuits

# Results on Common-Source Voltage Amplifier (CSVA).

Figure 22: Common-Source Voltage Amplifier

#### Results on Cascode Voltage Amplifier (Cascode).

Figure 23: Cascode Voltage Amplifier

#### Results on Low-Noise Amplifier (LNA).

Figure 24: Low-Noise Amplifier

# Results on KNN

Figure 25: KNN performance on homogeneous circuits.