# Missile: Fine-Grained, Hardware-Level GPU Resource **Isolation for Multi-Tenant DNN Inference**

Yongkang Zhang HKUST

Haoxuan Yu HKUST

**Baotong Lu** Microsoft Research China University of Geosciences HKUST (Guangzhou)

Yang Li

Huaicheng Li Virginia Tech

Cheng Wang

Alibaba Group

# Abstract

Colocating high-priority, latency-sensitive (LS) and low-priority, best-effort (BE) DNN inference services reduces the total cost of ownership (TCO) of GPU clusters. Limited by bottlenecks such as VRAM channel conflicts and PCIe bus contentions, existing GPU sharing solutions are unable to avoid resource conflicts among concurrently executing tasks, failing to achieve both low latency for LS tasks and high throughput for BE tasks.

To bridge this gap, this paper presents MISSILE, a general GPU sharing solution for multi-tenant DNN inference on NVIDIA GPUs. MISSILE approximates fine-grained GPU hardware resource isolation between multiple LS and BE DNN tasks at software level. Through comprehensive reverse engineering, MISSILE first reveals a general VRAM channel hash mapping architecture of NVIDIA GPUs and eliminates VRAM channel conflicts using software-level cache coloring. It also isolates the PCIe bus and fairly allocates PCIe bandwidth using completely fair scheduler. We evaluate 12 mainstream DNNs with synthetic and real-world workloads on four GPUs. The results show that compared to the state-ofthe-art GPU sharing solutions, MISSILE reduces tail latency for LS services by up to ~50%, achieves up to 6.1× BE job throughput, and allocates PCIe bus bandwidth to tenants on-demand for optimal performance.

#### Introduction 1

With rapid technological advancements in machine intelligence across various fields such as vision recognition [22, 26], natural language processing [16, 52, 62] and autonomous driving [24], an increasing number of industries are deploying large-scale deep neural network (DNN) inference services in cloud data centers to support their businesses. Many of these services are high-priority, latency-sensitive (LS) services with stringent latency requirements, while others are low-priority, throughput-oriented, best-effort (BE) batch tasks.

To ensure the low tail latency of LS services, it is common practice to place them on dedicated machines [30]. Since the request rates for LS services fluctuate due to their userfacing nature [80], compute resources are often under-utilizd, leading to high total cost of ownership (TCO) within data

centers. Consequently, many cloud service providers colocate multiple LS services and BE tasks on the same machine, overcommitting the idle computing resources of LS services to BE tasks [35, 58, 61, 63, 80]. As the computational capabilities of newer GPUs continue to increase [40], it has also become common to enhance GPU utilization by sharing GPUs among multiple LS tasks [12, 20, 37, 57, 75] or between LS and BE tasks [65, 69, 76, 80].

Chenxia Han

CUHK

Xiaowen Chu

However, colocating DNN tasks with different priorities can lead to challenging contention for GPU resources, adversely impacting the service quality of LS tasks. Although NVIDIA has introduced two GPU isolation schemes, Multi-Process Service (MPS [50]) and Multi-Instance GPU (MIG [49]), both have significant limitations:

1) MPS can partition computing units in all NVIDIA GPUs, but it cannot isolate VRAM channels, resulting in severe contention among colocated tasks.

2) MIG fully isolates compute units and VRAM channels only in a few flagship GPUs (e.g., A100 and H100) through dedicated architecture design. However, many IT giants deploy DNNs on low-end GPUs (e.g., Tesla T4) to reduce TCO [9, 41, 65, 69, 82]. Additionally, MIG can only reconfigure resource allocation when GPU is idle [73], and its granularity is too coarse (e.g., up to 7 instances of 10 GiB for A100).

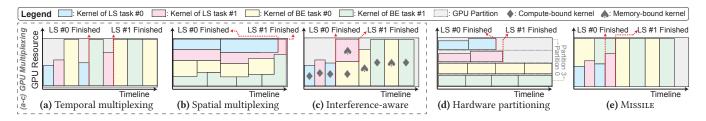

To circumvent these drawbacks, existing work has proposed 4 kinds of software-based GPU sharing solutions (illustrated as (a)~(d) in Fig. 1, where (a)~(c) are referred to as GPU multiplexing):

a) *Temporal multiplexing* (e.g., TGS [67] and Clockwork [20]) allows only one DNN to be executed exclusively on the GPU at a time [8, 20, 20, 67] to ensure low latency for LS tasks.

b) Spatial multiplexing (e.g., Reef [21]) uses MPS [14] or kernel padding [21, 33, 66, 84] to enable concurrent execution of multiple DNNs on a GPU, improving throughput.

c) Interference-aware multiplexing (e.g., Orion [19]) builds on spatial multiplexing by predicting the interference among colocated tasks and only allowing coexecution of mildly interfering kernels. This ensures the tail latency of LS services while achieving higher throughput for BE tasks compared to temporal multiplexing.

**Figure 1.** Illustration of existing GPU sharing schemes and MISSILE. The gray (colored) rectangles represent GPU resources (DNN kernels). The width (height) of a colored rectangle represents the runtime (resource utilization) of a DNN kernel.

d) Software-controlled hardware partitioning (i.e., Fractional GPU, FGPU [33]) eliminates inter-task resource interference by statically partitioning the GPU's compute units and VRAM channels at the software level. This approach requires reverse engineering of the GPU architecture and modifying open-source GPU drivers (§ 3.2).

Through detailed analysis of the aforementioned four approaches (§ 3.1-3.2), we find that GPU multiplexing ((a)–(c)) cannot achieve both low latency for LS services and high throughput for BE tasks. These solutions try to work around the inevitable inter-task resource conflicts rather than isolating them. Although hardware partitioning using FGPU [33] can isolate SM and VRAM channels, it is inapplicable to most GPUs due to its strong assumptions about the GPU's VRAM channel mapping function, which do not hold for most GPUs. Additionally, FGPU's cache coloring granularity is not suitable for newer GPU architectures (§ 5.2). Therefore, GPU performance isolation has remained an obstacle in both industry and academia for over a decade.

To bridge this gap, an intuitive idea emerges: using softwarecontrolled hardware partitioning to eliminate scheduling constraints of interference-aware multiplexing and fine-grainedly isolating GPUs' compute units, VRAM channels, and PCIe bus. However, this is challenging because: 1) NVIDIA's GPU architecture is opaque, and its VRAM channel mapping is still publicly unknown; 2) NVIDIA's proprietary GPU driver implementation disallows partitioning GPUs' PCIe bus.

This paper addresses these challenges and presents MIS-SILE ((e) in Fig. 1), a general GPU sharing solution for multitenant DNN inference on NVIDIA GPUs. MISSILE eliminates resource contention among multiple LS and BE DNN inference tasks colocated on the same GPU. It ensures low latency for LS services while achieving high throughput by making the following contributions:

1) MISSILE conducts the first, to the best of our knowledge, full-spectrum reverse engineering, unearthing the general VRAM channel architecture of black box GPUs.

2) MISSILE reduces inter-task VRAM channel conflicts with low-overhead, fine-grained page coloring at the software level, which is generally applicable to new NVIDIA GPUs.

3) MISSILE isolates the PCIe bus using temporal multiplexing and fairly allocates PCIe bus bandwidth to multiple tenants according to their weights. Our experiments demonstrate that MISSILE significantly reduces the p99 latency of LS services by up to 50% and achieves up to 6.1× throughput for BE tasks compared to state-of-the-art GPU sharing solutions. Additionally, in scenarios of PCIe bus congestion, MISSILE exhibits the capability to allocate PCIe bus bandwidth to different tenants based on their weights, reducing the p99 latency of PCIe-bound LS services by orders of magnitude.

This paper begins by providing research background (§ 2) and elaborating on the motivation of our research (§ 3).

Secondly, we provide a brief overview of MISSILE (§ 4).

Thirdly, we discuss how to reduce inter-SM contention between tasks via reverse engineering on VRAM channel mapping and software-level page coloring (§ 5), and isolate the PCIe bus via the PCIe completely fair scheduler (§ 6).

After that, we implement MISSILE (§ 7) and evaluate it using synthetic and real-world workloads (§ 8).

Finally, we discuss MISSILE's limitations and future work (§ 9) and summarize related literature on our work (§ 10).

# 2 Background

# 2.1 A Primer on NVIDIA GPUs' Architecture

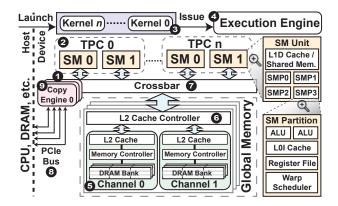

NVIDIA's official documents [46, 51] and previous work on reverse-engineering NVIDIA GPUs [4, 17, 33, 44, 81] provide an overview of NVIDIA GPUs' architecture (Fig. 2):

**Compute units.** A Streaming Multiprocessor (SM, ①) is a basic compute unit of a GPU, which contains multiple SM partitions (SMP). A Texture Processing Cluster (TPC, ②) consists of two SMs. More details about the kernel queue (③) and execution engine ④ can be found in [4].

**Memory hierarchy.** NVIDIA GPU's memory is divided into 3 levels [44]: 1) L1 data cache and shared memory (private to each SM); 2) L2 unified cache (shared by all SMs); and 3) video RAM (VRAM, shared by all SMs). VRAM is composed of multiple groups of GDDR or HBM chips, and each group has an independent memory controller and maps to a set of L2 cache (referred to as a *VRAM channel* [46], **⑤**). A pair of *VRAM channels* share an *L2 cache controller* (**⑥**). When threads running on an SM read data stored in the VRAM, the data is first populated into the L2 cache. Then threads fetch the L2 cacheline through the *Crossbar* (**⑦**). The write process is similar to the read process. Within the *Crossbar*,

Figure 2. NVIDIA GPU's architecture.

there is a direct bus between each SM and each L2 cache controller. This implies that the latency for any SM to access the L2 cache on any channel is the same, making NVIDIA GPU a Uniform Memory Access (UMA) architecture.

Host-device communication. Data is transferred between the host and the GPU through the *PCIe bus* (③), with several *copy engines* [4] (④) on the GPU responsible for transferring data on the PCIe bus. The PCIe bus is full-duplex, meaning that it can simultaneously perform host-to-device and deviceto-host data transfers.

#### 2.2 DNN Inference Workloads

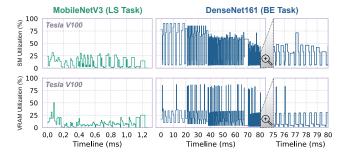

**Dissecting DNN inference tasks.** LS inference tasks utilize small batch sizes to enhance responsiveness, whereas BE inference tasks employ large batch sizes to maximize throughput. Due to the characteristics of large batch size and high throughput, BE inference tasks require more compute resources and VRAM bandwidth compared to LS tasks. DNN inference involves a series of kernels executed sequentially on the GPU, along with PCIe data transfer operations. **Poor, bursty, and unbalanced GPU utilization**. Throughout the execution of a DNN inference task, both compute unit and VRAM bandwidth utilization display bursty patterns. LS tasks notably underutilize the GPU (Fig. 3) [19]. The bursty nature of GPU utilization and the significant underutilization of the GPU emphasize the importance of sharing the GPU among multiple LS and BE DNN inference tasks.

# 2.3 Resource Contention in GPU Sharing

Due to the generally low GPU utilization of LS inference tasks (§ 2.2), many cloud providers choose to deploy multiple DNN workloads on the same GPU, leading to contention for the following resources:

**Intra-SM conflicts (Fig. 4(a)).** Kernel block threads of different tenants running on the same SM could contend for intra-SM resources. For instance, when all Floating-Point Units (FPUs) are actively processing, additional floating-point operations experience delays, hindering the progress of other kernels. Apart from computational units, warps located on

**Figure 3.** GPU resource utilization of MobileNetV3 (LS task) and DenseNet161 (BE task) on Tesla V100.

**Figure 4.** Micro-benchmarking of resource contention in GPU sharing. One victim task is colocated with multiple interference tasks. Then we measure the latency (throughput) of the victim task. *L1 Cache (Comp.)* in **(a)** denotes introducing *L1 cache (compute unit)* interference tasks. **Testbed:** Server A in Tab. 4.

the same SM also compete for SM-local memory resources, such as the L1 cache, shared memory, and instruction cache. **Inter-SM contention (Fig. 4(b)).** As described in § 2.1, different SMs share all VRAM channels. Consequently, physical addresses accessed by threads in different SMs may map to the same VRAM channel. Simultaneous access to these physical addresses leads to frequent contention for the limited L2 cache space. Additionally, since a DRAM bank only serves one request in a clock cycle, memory requests from multiple threads to the same DRAM bank must be processed sequentially [33], increasing the VRAM access latency.

**PCIe bus congestion (Fig. 4(c)).** To minimize the GPU memory footprint, DNN inference systems typically pipeline the loading of weight tensors from host memory to GPU VRAM and swap out intermediate tensors not recently used from GPU VRAM to host memory [6, 20, 25]. Multiple tenants contend for the limited PCIe bus bandwidth when simultaneously swapping tensors between the host and the GPU.

# 3 Motivation

To elucidate the motivation behind our research, we begin by presenting the limitations of GPU multiplexing through micro-benchmarking experiments (§ 3.1), then elaborate on the drawbacks of GPU partitioning through in-depth analysis (§ 3.2). Afterward, we explore the necessity of fine-grained

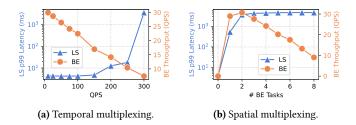

**Figure 5.** Limitations of GPU temporal and spatial multiplexing. **(a)** Temporal multiplexing [8, 20, 20, 67] cannot achieve high throughput for BE tasks; **(b)** Spatial multiplexing [21, 33, 66, 84] can achieve high throughput at the cost of sacrificing service quality of the LS task due to resource contention; **LS Workload:** MobileNet V3; **BE Workload:** ResNet50; **Testbed:** Server A in Tab. 4.

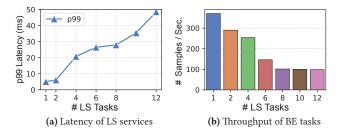

Figure 6. Interference-aware multiplexing is not panecea.

(a) As the number of LS services increases, each LS service maintains low tail latency. Because their p99 latency linearly correlates with the number of concurrent LS tasks.

(b) However, BE tasks' throughput substantially declines.

LS Workload: MobileNet V3; BE Workload: ResNet152; Testbed: Server A in Tab. 4.

PCIe bus isolation (§ 3.3) and summarize the shortcomings of state-of-the-art GPU sharing solutions (§ 3.4).

#### 3.1 Limitations of GPU Multiplexing Solutions

*Temporal multiplexing* eliminates contention in shared GPU resources and meets the low-latency requirements of LS services [8, 86], but it can't fully harness GPUs' compute capabilities, as BE tasks could be starved due to frequent LS task preemption, leading to undesirable throughput [21] (Fig. 5a).

*Spatial multiplexing* leads to intra- and inter-SM conflicts when co-executing LS and BE kernels (Fig. 5b) [70], and PCIe bus congestion [10, 74] when loading weights [10, 68].

Compared to temporal multiplexing and spatial multiplexing, *interference-aware multiplexing* (e.g., Orion [19]) achieves a better trade-off between low latency of LS service and high throughput. However, it is not perfect in all scenarios. We take Orion [19] as an example. When multiple LS services are executed concurrently on a GPU, the abundance of LS kernels in execution makes it challenging for Orion's scheduler to select appropriate BE kernels to co-execute. As a result, despite LS services keeping low tail latency (Fig. 6(a)), the throughput of BE tasks decreases as the concurrency of LS services increases (Fig. 6(b)).

This is because Orion imposes numerous constraints on the co-execution of BE kernels to ensure low latency for LS tasks, as it cannot avoid intra-SM and inter-SM interference. These constraints limit BE tasks' throughput. For BE models listed in Tab. 5, 83.4% of their kernels are subjected to at least one constraint. Therefore, excessive constraints lead to decreased throughput for BE tasks as the concurrency of LS tasks increases.

# 3.2 Limitations of GPU Partitioning Techniques

Although existing GPU multiplexing solutions all tried to work around GPU hardware resource partitioning, they result in either undesirable performance of DNN inference, or low GPU utilization, or both (§ 3.1). Unfortunately, softwarelevel GPU hardware partitioning is also flawed. Although there are numerous mature software [21, 33, 45] or hardwarebased [7, 13, 53] solutions for partitioning computational units, VRAM channel isolation and PCIe bus scheduling are challenging due to their close coupling with proprietary GPU hardware and driver implementations.

Fractional GPU (FGPU) [33] stands out as the sole softwarebased GPU sharing solution capable of partitioning both compute units and VRAM channels on GTX 1080 and Tesla V100. Here, we delve into an in-depth analysis of FGPU. How FGPU works. FGPU isolates VRAM channels based on cache coloring, a mature technique in CPU cache isolation. Cache coloring on CPUs and GPUs both require two steps: 1) intercepting memory allocation and management, ensuring that memory addresses owned by a user program are mapped to given cache sets; 2) reverse engineering the hash mapping from physical addresses to cache sets or VRAM channels. In CPU's LLC cache coloring, the first step can be easily achieved by allocating a contiguous set of large pages in host memory. As for the second step, Intel's CPU LLC hash mapping has been fully decrypted [5, 18, 43]. For FGPU, the first step involves modifying NVIDIA's open-sourced GPU driver module nvidia-uvm (>2K LOC), intercepting cudaMallocManaged() and utilizing the GPU's Memory Management Unit (MMU) to map virtual pages allocated for each task to specific physical pages on the designated VRAM channel. In the second step, due to the unknown structure of NVIDIA GPU's hash functions, FGPU assumes that the GPU's hash mapping functions for VRAM channels, DRAM banks, and L2 cache lines are all XOR functions on the physical address bits. Then FGPU uses Gauss elimination to solve a XOR equation system and gets the exact XOR hash functions.

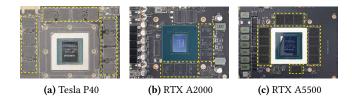

**FGPU is inapplicable to most commodity GPUs and new GPU architecture.** We attempted to reverse engineer other GPUs (Tesla P40, RTX A2000, and RTX A5500) using

**Table 1.** # VRAM channels of representative server GPUs.FGPU [33] is compatible with *italic GPUs*.

| Specifications  | GTX<br>1080 | Tesla<br>V100 | Tesla<br>P40 | RTX<br>A2000 | RTX<br>A5500 |

|-----------------|-------------|---------------|--------------|--------------|--------------|

| Architecture    | Pascal      | Volta         | Pascal       | Ampere       | Ampere       |

| # VRAM Channels | 8           | 32            | 12           | 6            | 12           |

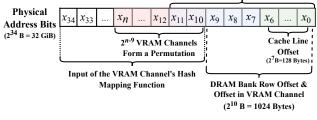

FGPU's approach, but all failed. This is because FGPU assumes that the VRAM channel's hash mapping function is a pure XOR function. This assumption does not hold true for many other NVIDIA GPUs (Tab. 1): XOR function is *linear* (i.e., mapping from a VRAM space with 2<sup>N</sup> bytes to 2<sup>M</sup> VRAM channels), but many GPUs' hash mapping is *nonlinear* (i.e., mapping from a VRAM space with arbitrary size to an arbitrary number of VRAM channels). Furthermore, FGPU only supports page coloring based on 4 KiB granularity, which is the minimum page size supported by NVIDIA GPU's MMU[51]. Our experience indicates that this granularity is inapplicable to newer GPU architectures (§ 5.2).

# 3.3 The Necessity of PCIe Bus Isolation

In § 3.1 and § 3.2, we elucidated why existing GPU multiplexing schemes cannot achieve both low latency for LS tasks and high throughput for BE tasks, as well as the limitations of existing software-based GPU partitioning. However, as discussed in § 2.3, severe PCIe bus conflicts could arise when multiple tenants share a GPU because PCIe data transfers from multiple CUDA streams are parallel and unmanaged. This issue is largely overlooked by most GPU sharing solutions. While there has been some work discussing PCIe bus isolation on other PCIe devices (e.g., NVMe SSDs [27]), finegrained GPU PCIe bus isolation remains immature due to: 1) lack of support for fine-grained PCIe bus isolation in NVIDIA MPS and MIG; 2) proprietary hardware and driver implementations of GPUs, making it challenging for software-based GPU sharing solutions to control the number of copy engines allocated for each PCIe data transfer request.

Baymax [10] and StreamBox [68] have both discussed how to avoid PCIe bus interference between LS and BE tasks on commodity GPUs. Baymax leverages MPS to support parallel task coexecution, predicts PCIe bus contention for different tasks, and limits the PCIe bus data transfer rate for BE tasks to avoid interference between LS and BE tasks' PCIe data transfers. However, it does not support preempting the PCIe bus for LS tasks, resulting in unstable tail latency for LS tasks (§ 8.1.2). StreamBox leverages temporal multiplexing to share the GPU's PCIe bus among multiple serverless tasks, splits CUDA memory copy requests into a series of data packets, allowing LS tasks to preempt PCIe buses. However, it does not provide fine-grained scheduling for PCIe bus among multiple tenants.

# 3.4 Take Away

§ 3.1 and 3.2 emphasize the bottleneck of VRAM channel isolation, and § 3.3 indicates that existing work overlooks dynamic resource needs when sharing PCIe bus under multi-tenancy. Here, we summarize the most competitive GPU sharing solutions for multi-tenant DNN inference in Tab. 2. To address the aforementioned limitations of prior work, we employ the following techniques in MISSILE:

1) Develop a *universal reverse engineering approach* for GPU VRAM channel hash mapping to enable *page coloring applicable to all NVIDIA GPU architectures.*

2) Implement *fine-grained PCIe bus management* to allocate bandwidth for tasks based on their scheduling weights.

It is essential to clarify that MIG [49] complements our work, as MISSILE provides QoS isolation for low-end GPUs. Both Paella [45] and Reef [21] are orthogonal to our work. Reef [21] primarily focuses on achieving fast BE task preemption. The primary contribution of Paella [45] lies in optimizing low-latency GPU kernel scheduling for DNN inference based on spatial multiplexing. On the contrary, our focus is on offering VRAM channel and PCIe bus isolation for multiple tenants.

# 4 **MISSILE Overview**

MISSILE is a GPU sharing solution tailored for multi-tenant DNN inference on NVIDIA GPUs. Based on the analysis of four GPU sharing solutions, MISSILE employs a completely different approach from previous work: approximating finegrained, hardware-level GPU resource isolation at the software level, enabling commodity GPUs to possess microarchitecture QoS management capability.

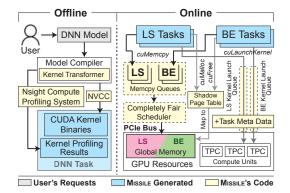

MISSILE serves user-submitted DNN models in two phases (Fig. 7). In the *offline phase*, users submit their models (e.g., in ONNX or PyTorch format) to MISSILE. MISSILE compiles the model, transforms its CUDA kernels to meet its requirements, and uses nvcc to generate cubin binaries. It uses NVIDIA Nsight Compute to profile kernels' VRAM bandwidth consumption and decides to isolate which tensors (§ 5.3). In the *online phase*, MISSILE eliminates three dimensions of GPU resource conflicts (§ 2.3) in the following ways:

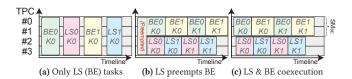

1) **Intra-SM conflicts.** MISSILE prevents LS and BE tasks from intra-SM conflicts by employing *elastic SM multiplexing* (Fig. 8). MISSILE uses libsmctrl [7], a library that manipulates Task Meta Data (TMD [32], an NVIDIA's little-known interface), to control the set of TPCs to which each launched kernel can be assigned. To enhance the utilization of SM units, we allow different LS and BE tasks to share their respective SM units in a time-multiplexed manner, and LS kernels can preempt SMs occupied by BE kernels following FLEP's design [66]. When LS and BE kernels are co-executed, the BE kernel can only use  $SM_{BE}$ % (a tunable parameter) of TPCs.

Table 2. A comparison of mainstream GPU sharing solutions.

| Method         | GPU Sharing<br>Scheme     | Implementation | Computing Unit<br>Isolation | VRAM Channel<br>Isolation | PCIe Bus<br>Isolation | Support All<br>NVIDIA GPUs | Compute Unit<br>Scaling |

|----------------|---------------------------|----------------|-----------------------------|---------------------------|-----------------------|----------------------------|-------------------------|

| MPS [50]       | Native                    | Hardware       | $\checkmark$                | ×                         | ×                     | $\checkmark$               | ×                       |

| MIG [49]       | Native                    | Hardware       | $\checkmark$                | $\checkmark$              | ×                     | ×                          | ×                       |

| FGPU [33]      | Hardware partitioning     | Driver         | $\checkmark$                | $\checkmark$              | ×                     | ×                          | ×                       |

| TGS [67]       | Temporal multiplexing     | User-space     | N/A                         | N/A                       | N/A                   | $\checkmark$               | $\checkmark$            |

| Reef [21]      | Spatial multiplexing      | Driver         | $\checkmark$                | ×                         | ×                     | $\checkmark$               | $\checkmark$            |

| Paella [45]    | Spatial multiplexing      | User-space     | $\checkmark$                | ×                         | ×                     | $\checkmark$               | $\checkmark$            |

| Orion [19]     | Interference-aware        | User-space     | ×                           | ×                         | ×                     | $\checkmark$               | $\checkmark$            |

| MISSILE (Ours) | Fine-grained partitioning | User-space     | $\checkmark$                | $\checkmark$              | $\checkmark$          | $\checkmark$               | $\checkmark$            |

**Figure 7.** MISSILE's architecture. Modules with dashed boarder are on the critical path of DNN inference. *Italic texts* represent intercepted CUDA API calls.

**Figure 8.** MISSILE's elastic SM multiplexing.  $LS_iK_j$  ( $BE_iK_j$ ) represents the *j*-th kernel of the *i*-th LS (BE) task.

2) **Inter-SM conflicts.** Through extensive reverse engineering of black-box GPU VRAM channel architecture, MIS-SILE finds a general way to fit VRAM channel mapping and isolates inter-SM conflicts by employing *fine-grained VRAM coloring* based on shadow page table. (§ 5)

3) **PCIe bus.** MISSILE intercepts cuMemcpy operations and divides PCIe requests into a series of packets, then uses PCIe completely fair scheduler to fine-grainedly allocate the PCIe bus bandwidth to tenants based on their weights. (§ 6)

# 5 Reducing Inter-SM Memory Conflicts

The solution to mitigating inter-SM contention involves preventing memory-bound BE DNN kernels from competing for VRAM channels, as this contention results in L2 cache thrashing and VRAM bank conflicts [33, 70]. This is accomplished through reverse engineering GPUs' VRAM channel mapping and implementing fine-grained page coloring.

#### 5.1 Managing GPU's Physical VRAM Space

Taking over VRAM management from the GPU driver. MISSILE utilizes the cuMemCreate() and cuMemReserve() functions available in the CUDA API to allocate a contiguous physical address space within the VRAM directly to a CUDA program. This space is then mapped to a virtual address space (reserved\_memspace) of the CUDA program using cuMemMap(). This approach allows MISSILE to manage the VRAM space directly within the user-space CUDA program without needing to modify the GPU driver.

Getting VRAM physical address for CUDA programs. MISSILE introduces an API GetPhysAddrFromVirtAddr (consisting of only ~100 LOC) within nvidia-uvm. User-space CUDA programs intercept the GPU device descriptor (/dev/ nvidia-uvm) to invoke this API and provide the querying virtual address virt\_addr. This API then utilizes uvm\_page\_ table\_range\_entry\_address to access and parse the page table entry [51] (stored in the GPU's global memory) to which virt\_addr belongs, thereby retrieving its physical address.

#### 5.2 Reverse Engineering VRAM Channels

Some studies have reverse-engineered the hash mapping functions of Intel's last-level cache (LLC) for cache coloring [59, 71] or side-channel attacks [28]. They utilized the CPU's non-uniform memory access feature to exploit the latency differences in accessing the last-level cache on different CPU cores and match each cache line to the corresponding CPU core. However, GPUs have uniform memory access, rendering these solutions inapplicable. We observe that any pair of physical addresses with a DRAM bank conflict or an L2 cache line conflict must belong to the same VRAM channel because a DRAM bank or L2 cache line is associated with only one VRAM channel (as demonstrated in § 2.1). Thus, identifying all addresses that reside in the same VRAM channel as the virtual address Addr requires 3 steps:

1) Generating a set of addresses belonging to Addr's VRAM channel. Following FGPU's approach [33], we find a series of addresses *DramConflictAddrs*[] that have DRAM bank conflicts with Addr (Algo. 1 in § A.1.1), then retrieve a series of addresses *CacheConflictAddrs*[] that have cache conflicts with *DramConflictAddrs*[] (Algo. 2 in § A.1.1).

2) Identifying a given address's VRAM channel ID. After generating a set of addresses belonging to each VRAM channel, now we can identify the VRAM channel ID that any given address Addr' maps to following three steps: a) Reading Addr' to populate it into a cacheline; b) Reading CacheConflictAddrs[] belonging to the *i*-th VRAM channel to refresh all cachelines in the VRAM channel where Addr resides; and c) Reading Addr' again and timing its latency. If the latency exceeds the threshold (decided by microbenchmarking [44]), it indicates an L2 cache miss, and thus Addr maps to the *i*-th VRAM channel (Algo. 3 in § A.1.1).

3) Cracking the VRAM channel's hash mapping. Marking each address's channel ID in the entire VRAM space is extremely time-consuming. For example, if the VRAM size is 24 GiB, it would require marking 24 GiB/1024 B = 25 million VRAM channels, which takes more than 1 year to complete. Therefore, we need to crack the hash mapping of VRAM channels using a non-brute-force solution. Although the mapping functions of VRAM channels on many NVIDIA GPUs are nonlinear, and the structure of these functions is unknown, fortunately, we can use DNNs to offline approximate them. DNNs have already been theoretically proven to be capable of statistically meaningful approximation of any boolean function [64]. Therefore, for each GPU, we spend one month to collect 15K samples of VRAM channel mapping and trained a 9-layer multi-layer perceptron network to fit this mapping function. The results on the test set indicate that our DNN can accurately label over 99.9% of VRAM channel IDs when provided with an unseen physical address.

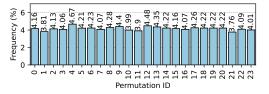

In a contiguous 10 MiB VRAM space, we attempt to mark 2 VRAM channels for RTX A2000 and 4 VRAM channels for both Tesla P40 and RTX A5500, respectively. The findings indicate that every contiguous 1 KiB physical address belongs to the same VRAM channel. We observe 24, 12, and 24 different permutations of VRAM channels uniformly distributed in VRAM space for Tesla P40, RTX A2000, and RTX A5500 respectively (Fig. 9). The physical address structure is illustrated in Fig. 15 of § A.1.2. In each permutation, at most 4 KiB and 8 KiB space share the same set of VRAM channels in any permutation of Tesla P40 and Tesla V100, respectively. At most 2 KiB space shares the same set of VRAM channels in any permutation of both RTX A2000 and RTX A5500. Full reverse engineering results are presented in § A.1.2 of supplementary materials.

#### 5.3 Isolating VRAM Channel Conflicts

Once the VRAM channel mapping is available, MISSILE utilizes cache coloring to isolate VRAM channel conflicts between LS and BE kernels. As the physical address space belonging to the same VRAM channel is not contiguous, we need to remap the address space accessed by each task. This maps the address space accessed by each task to the given set of VRAM channels. An intuitive idea is to use the cuMemMap API to manage the VRAM virtual address mapping in the

|    | (a                                            | a) P | erm | nuta | itio | ns | of C | cha | nne | els . | A~[  | D (T | esl  | a P | 40)  |      |     |      | 1    | (b) I | Pern | nuta | atio | ns o | of C | har | inel | s A | &В | (RT  | ΧA   | 200 | 0)   |

|----|-----------------------------------------------|------|-----|------|------|----|------|-----|-----|-------|------|------|------|-----|------|------|-----|------|------|-------|------|------|------|------|------|-----|------|-----|----|------|------|-----|------|

|    | 0                                             | 1    | 2   | 3    | 4    | 5  | 6    | 7   | 8   | 9     | 10   | 11   | 12   | 13  | 14   | 15   |     |      |      | 0     |      | 1    |      | 2    | 3    |     | 4    |     | 5  |      | 6    | 7   | 7    |

| 00 | ?                                             | ?    | ?   | ?    | А    | В  | С    | D   | В   | Α     | D    | С    | ?    | ?   | ?    | ?    |     | 00   | Т    | ?     |      | ?    |      | ?    | ?    |     | ?    |     | ?  |      | A    | E   | 3    |

| 01 | 2                                             | ?    | ?   | ?    | ?    | ?  | ?    | ?   | ?   | ?     | ?    | ?    | А    | В   | С    | D    |     | 01   |      | ?     |      | ?    | 1    | A    | E    | 5   | ?    |     | ?  |      | ?    | 2   | ?    |

| 02 | ?                                             | ?    | ?   | ?    | D    | С  | В    | А   | С   | D     | А    | В    | ?    | ?   | ?    | ?    |     | 02   |      | ?     |      | ?    |      | ?    | ?    |     | В    |     | А  |      | ?    | ?   | ?    |

|    | (c) Permutations of Channels A~H (Tesla V100) |      |     |      |      |    |      |     |     |       |      |      |      |     |      |      |     |      |      |       |      |      |      |      |      |     |      |     |    |      |      |     |      |

|    | 0                                             | 1    | 2   | 3    | 4    | Ę  | 5 6  | 6   | 7   | 8     | 9    | 10   | 11   | 12  | 13   | 14   | 15  | 16   | 17   | 18    | 19   | 20   | 21   | 22   | 23   | 24  | 25   | 26  | 27 | 28   | 29   | 30  | 31   |

| 00 | A                                             | В    | С   | D    | E    | F  | : (  | ΞI  | н   | ?     | ?    | ?    | ?    | ?   | ?    | ?    | ?   | Α    | В    | С     | D    | Е    | F    | G    | Н    | ?   | ?    | ?   | ?  | ?    | ?    | ?   | ?    |

| 01 | 2                                             | ?    | ?   | ?    | ?    | 1  | 2    | ?   | ?   | А     | В    | С    | D    | E   | F    | G    | н   | ?    | ?    | ?     | ?    | ?    | ?    | ?    | ?    | А   | В    | С   | D  | E    | F    | G   | н    |

| 02 | E                                             | F    | G   | Н    | А    | E  | 3 (  | C I | D   | ?     | ?    | ?    | ?    | ?   | ?    | ?    | ?   | Е    | F    | G     | н    | А    | В    | С    | D    | ?   | ?    | ?   | ?  | ?    | ?    | ?   | ?    |

|    |                                               |      |     |      |      |    |      |     | (0  | d) F  | Perr | nut  | atic | ns  | of 0 | Char | nel | s Aa | kΒ ( | RT    | X AS | 5500 | ))   |      |      |     |      |     |    |      |      |     |      |

|    | 0                                             | 1    | 2   | 3    | 4    | 5  | 6    | 7   | 8   | 9     | 10   | 11   | 12   | 13  | 14   | 15   |     |      | Т    | 0     | 12   | 3    | 4    | 5    | 6    | 7   | 8    | 9   | 10 | 11 1 | 12 1 | 3 1 | 4 15 |

| 00 | ?                                             | ?    | ?   | ?    | ?    | ?  | ?    | ?   | ?   | ?     | ?    | ?    | ?    | ?   | В    | A    |     | 12   | Т    | ? '   | ? ?  | ?    | В    | Α    | ?    | ?   | ?    | ?   | ?  | ?    | ?    | ? ? | ??   |

| 01 | 2                                             | ?    | ?   | ?    | ?    | ?  | ?    | ?   | ?   | ?     | ?    | ?    | ?    | ?   | А    | в    |     | 13   |      | ? '   | ? ?  | ?    | В    | А    | ?    | ?   | ?    | ?   | В  | А    | ?    | ? ? | ??   |

| 02 | 2                                             | ?    | ?   | ?    | ?    | ?  | ?    | ?   | ?   | ?     | ?    | ?    | В    | А   | ?    | ?    |     | 14   |      | ? '   | ? ?  | ?    | A    | В    | ?    | ?   | ?    | ?   | ?  | ?    | ?    | ? ? | ? ?  |

**Figure 9.** A part of permutations of Tesla P40's channels A-D (a), RTX A2000's channels A-B (b), Tesla V100's channels A-H (c), and RTX A5500's channels A-B (d). Full results can be found in § A.1.2 of supplementary materials.

user-space. However, the latest CUDA version only supports minimal mapping granularity of 2 MiB for this API.

Another approach is to modify the GPU driver and control the GPU's memory management unit (MMU), as adopted by FGPU [33]. Nonetheless, it supports mapping 4 KiB physical address pages within the same VRAM channel to the GPU virtual address space, as 4 KiB is the minimal page size supported by NVIDIA GPU's MMU.

However, our reverse engineering results have revealed limitations to these approaches. In the VRAM channel layout of RTX A2000 and RTX A5500, the VRAM space is composed of a series of paired VRAM channels, which means that on new GPU architecture, the coloring granularity can only be 1 KiB or 2 KiB, and larger granularity is inapplicable.

To circumvent this problem and minimize invasive modifications to the GPU driver, MISSILE opts to bind different tasks to their corresponding VRAM channels by transforming their CUDA kernel code. Specifically, we introduce the *shadow page table* (SPT) into DNNs' CUDA kernels, i.e., the mapping between the array index and the offset in reserved \_memspace. The arguments passed into the CUDA kernels are replaced by their shadow page tables. An illustrative example can be found in Fig. 10.

To minimize the extra memory access overhead incurred by shadow page tables, MISSILE adopts a 4 KiB coloring granularity for Tesla V100 and Tesla P40, and a 2 KiB granularity for both RTX A2000 and RTX A5500, respectively. We discuss how to decide coloring granularity in § A.1.3 of supplementary materials. Additionally, MISSILE only isolates tensors accessed by memory-bound kernels (identified by NVIDIA Nsight Compute with DRAM throughput > *ThresDRAM*%, a tunable parameter). This metric is also adopted by Orion [19] and SEER [39]. MISSILE binds  $1 - Ch_{BE}$  and  $Ch_{BE}$  of channels to memory-bound tensors accessed by LS and BE kernels, respectively. *ChannelBE* is a tunable parameter.

MISSILE employs grid search to tune  $SM_{BE}$  (§ 4),  $Ch_{BE}$ , and  $Thres_{DRAM}$ . The objective is to maximize  $SM_{BE}$ ,  $Ch_{BE}$ , and  $Thres_{DRAM}$  (larger values improve BE tasks' throughput) while ensuring that the increase in latency for LS kernels

| mn LS Task                              | BE Task A B C                                   |

|-----------------------------------------|-------------------------------------------------|

|                                         |                                                 |

| Entry #0 Entry #1 Entry #2 ······ Entry | Shadow Page Table<br>y #n (Stored in R/O Cache) |

| · ·                                     | Global Memory                                   |

| Colored Page #0 Colored Page #1 C       | olored Page #2 ····· Page #n                    |

|                                         |                                                 |

| VRAM Channel #0 VRAM Ch                 | annel #1 VRAM Channel #2                        |

| Legend>: Memory-bound VRAM Acces        |                                                 |

(a) Illustration of shadow page table. LS and BE tasks are assigned with 1 and 2 VRAM channel(s), respectively. Tensors m and n are used by the LS task. Tensors A-C are used by the BE task.

```

_global__ void vectorAdd(float *A, float *B, float *C) {

int i = blockIdx.x * blockDim.x + threadIdx.x;

C[i] = A[i] + B[i]; // Directly access the i-th elements in A ~ C

}

```

(b) The original BE kernel in (a), which performs vector addition.

(c) The transformed DNN kernel of BE task in (a). Memory-bound tensors a and b are applied with shadow page tables.

Figure 10. Shadow page table and kernel transformation.

does not exceed 25% compared to running them independently. MISSILE benchmarks over 200 pairs of LS and BE kernels, and the search results yield  $SM_{BE} = 30$ ,  $Ch_{BE} = 1/3$ , and  $Thres_{DRAM} = 40$ .

# 6 Handling PCIe Bus Congestion

# 6.1 Time-Sharing the PCIe Bus

MISSILE decomposes PCIe data transmission requests into a series of packets based on 1 KiB granularity, the minimum GPU coloring granularity (§ 5.2, A.1.1). Inspired by packet transmission in network communication, MISSILE employs temporal multiplexing on the PCIe bus: it allocates time slices for the PCIe transmission of data packets to different tasks, rotating between them.

# 6.2 PCIe Completely Fair Scheduler (CFS)

To ensure the fair allocation of time slices, considering the weights of distinct tasks in the temporal multiplexing on the PCIe bus, MISSILE leverages insights from the Completely Fair Scheduler (CFS) within the Linux kernel [55]. In MISSILE's PCIe CFS, each DNN task is assigned with a nice value (i.e., the scheduling weight, where a larger value indicates a higher priority) and a virtualized runtime (vruntime) (i.e., normalized runtime elapsed in the PCIe bus). When a

task submits a PCIe transfer request (e.g., cuMemcpyHtoD), PCIe CFS updates its vruntime to the globally minimum vruntime value (Algo. 4 in § A.2). During each iteration, PCIe CFS selects cfs\_period memory requests with the minimum vruntime from the queues of all tasks (i.e., the task with the longest waiting time) (Algo. 5 in § A.2). After that, it invokes cuMemcpy to transfer data (Algo. 6 in § A.2).

## 6.3 Auto-Tuning PCIe CFS's Parameter

CFS utilizes cfs\_period as the length of a scheduling cycle. As for PCIe CFS, a smaller cfs\_period refines the scheduling granularity and provides higher responsiveness for small LS requests, while a larger one can improve the PCIe bus throughput. We observe that as cfs\_period increases, the maximum throughput of the PCIe CFS also increases until it converges. To adapt PCIe CFS to PCIe buses with different generations and number of lanes, MISSILE employs microbenchmarking experiments to binary search on the minimum cfs\_period that approaches the peak throughput. As for PCIe 3.0×16, the optimum value of cfs\_period found by the auto-tuner is 2048 (equivalent to transmitting 2 MiB of data in each CFS period).

# 7 Implementation

MISSILE is implemented in C++ with ~8K LOC, consisting of ~1K LOC for reverse engineering the VRAM channels and ~7K LOC for the inference server and client. It utilizes TVM [11], a widely-used DNN compiler in the industry, to generate CUDA kernels for DNNs, and employs auto scheduler [85] for kernel optimization. Following PipeSwitch's practice [6], MISSILE loads DNNs' weights and executes DNNs in parallel to hide a portion of PCIe transmission delay.

# 8 Evaluation

Having discussed how MISSILE addresses intra-SM, inter-SM, and PCIe bus conflicts for different tasks, and how we implement it (§ 7), we now evaluate MISSILE (§ 8.1-8.5) to address the following key questions:

1) What is the performance of MISSILE'S VRAM channel isolation and PCIe CFS? (§ 8.1)

2) Can MISSILE effectively mitigate inter- and intra-SM contention between multiple LS services and BE tasks? (§ 8.3)

3) Can MISSILE effectively isolate PCIe bus and optimize PCIe transmission requests based on given weights? (§ 8.3)

4) How does each design component in MISSILE contribute to its performance improvements? (§ 8.5)

# 8.1 MISSILE Performance Deep Dive

We begin by analyzing the performance of MISSILE's two core components: *VRAM channel isolation* and *PCIe CFS*.

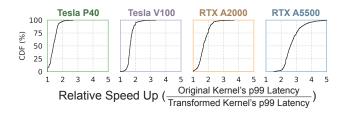

**8.1.1 Micro-benchmarking VRAM channel isolation.** We conduct tests on 4 GPUs in Tab. 4, use NVIDIA Nsight

**Figure 11.** CDF of LS kernels' runtime speed up after applying VRAM channel isolation. A memory-intensive BE kernel is coexecuted with LS kernels. Larger values are better.

Compute to profile and randomly choose some kernels with high DRAM throughput from BE models, to act as the source of VRAM channel conflicts. We incorporate all kernels of LS models in Tab. 5 to evaluate the extent of interference they encountered from memory-bound BE kernels and the overhead resulting from the shadow page tables.

We allocate  $1 - Ch_{BE}$  and  $Ch_{BE}$  of the VRAM channels to the memory-intensive tensors of LS and BE kernels, respectively (in our setting,  $Ch_{BE}$  is tuned to be 1/3). Then we coexecute each LS kernel with the selected VRAM-consuming BE kernels in a closed loop. In the control group, we launch the original LS kernels and also utilize libsmctrl to partition SMs. We compare the p99 latency of LS kernel runtime between MISSILE and the control group (Fig. 11). The results reveal that for all LS kernels on Tesla P40, Tesla V100, RTX A2000, and RTX A5500, MISSILE'S VRAM channel isolation reduces p99 latency compared to the non-isolated control group by ~28.9%, ~40.6%, ~42.2%, and ~63.5% on average, respectively. The p99 latency decreases by up to ~62.7%, ~70.0%, ~72.9%, and ~80.9%, respectively. Noted that these results have taken wrong VRAM channel prediction into consideration, because mispredicted VRAM channel IDs are randomly distributed across the VRAM space.

Although MISSILE'S VRAM channel isolation exhibits outstanding performance, the additional overhead introduced by SPTs remains a focal point of concern, as it incurs extra memory accesses. To address this concern, we conduct the following experiments to assess the overhead of SPT. We allocate all VRAM channels to each DNN kernel with SPT. In the absence of colocated BE kernels, we compare their runtime with that of the original DNN kernels. For all DNNs, on Tesla P40, Tesla V100, RTX A2000, and RTX A5000, the average overheads of SPT are 0.99%, 0.50%, 0.63%, and 0.82% respectively.

**8.1.2** Micro-benchmarking PCIe CFS. We compare the peak performance of PCIe CFS with the interference-aware PCIe scheduler of BayMax [10] and the PCIe preemption policy of StreamBox [68]. We set the LS task's nice=10K and BE task's nice=1 to demonstrate the tail latency of LS requests when LS tasks are assigned the largest weights in PCIe CFS. Tab.3 presents the p99 latency of LS PCIe requests and the throughput of BE requests under different workloads.

**Table 3.** Performance comparison between MISSILE'S PCIe CFS, BayMax's PCIe scheduler [10] and StreamBox's PCIe preemption policy [68]. We measured LS copy requests' p99 latency and BE copy requests' throughput. *HtoD: host-to-device; DtoH: device-to-host* copy; *BM: BayMax* [10]; *SB: StreamBox* [68]; **Testbed:** Server A in Tab. 4.

|         | QPS  | S  | ize | LS p99   | LS p99 Latency (us) |       |      |      | (GiB/s) |

|---------|------|----|-----|----------|---------------------|-------|------|------|---------|

|         | (LS) | LS | BE  | BM       | SB                  | CFS   | BM   | SB   | CFS     |

| Н       | 100  | 4K | 40M | 27718.1  | 177.0               | 177.0 | 11.2 | 11.2 | 11.2    |

|         | 1000 | 4K | 40M | 3385.9   | 177.0               | 177.0 | 11.2 | 11.1 | 11.1    |

| to<br>D | 100  | 2M | 40M | 3562.3   | 348.6               | 348.7 | 11.2 | 11.0 | 11.0    |

| D       | 1000 | 2M | 40M | 3566.3   | 534.7               | 534.7 | 9.5  | 9.3  | 9.3     |

| D       | 100  | 4K | 40M | 27 789.2 | 170.5               | 170.5 | 12.0 | 11.7 | 11.7    |

|         | 1000 | 4K | 40M | 3167.3   | 170.6               | 170.5 | 12.1 | 11.7 | 11.7    |

| to<br>H | 100  | 2M | 40M | 3315.5   | 331.1               | 331.0 | 12.0 | 11.6 | 11.6    |

| п       | 1000 | 2M | 40M | 3338.7   | 385.3               | 385.4 | 10.3 | 10.1 | 10.1    |

Table 4. The specifications of testbeds.

| C      | omponent       |                                     | Sei                                             | ver       |           |  |  |  |

|--------|----------------|-------------------------------------|-------------------------------------------------|-----------|-----------|--|--|--|

| U C    | omponent       | A                                   | В                                               | С         | D         |  |  |  |

|        | CPU            | Intel Xeon®                         | Intel Xeon <sup>®</sup> Intel Xeon <sup>®</sup> |           |           |  |  |  |

|        | CFU            | Gold 6133                           |                                                 | E5 2697V4 |           |  |  |  |

|        | PCIe           |                                     | PCIe                                            | 3.0×16    |           |  |  |  |

|        | Name           | Tesla V100                          | Tesla P40                                       | RTX A2000 | RTX A5500 |  |  |  |

|        | Architecture   | Pascal                              | Volta                                           | Ampere    | Ampere    |  |  |  |

|        | VRAM           | 16 GiB                              | 24 GiB                                          | 12 GiB    | 24 GiB    |  |  |  |

| GPU    | # SMs          | 80                                  | 30                                              | 28        | 80        |  |  |  |

| 010    | L1 Cache       | 128 KB                              | 48 KB                                           | 128 KB    | 128 KB    |  |  |  |

|        | L2 Cache       | 6 MB                                | 3 MB                                            | 3 MB      | 6 MB      |  |  |  |

|        | VRAM           | 897.0 GB/s                          | 346.0                                           | 360.0     | 768.0     |  |  |  |

|        | Bandwidth      | 697.0 GB/S                          | GB/s                                            | GB/s      | GB/s      |  |  |  |

| Softwa | re Environment | NVIDIA driver 535.129.03, CUDA 11.8 |                                                 |           |           |  |  |  |

Compared to BayMax, both StreamBox and PCIe CFS exhibit better latency for LS requests and comparable throughput. Since BayMax cannot preempt BE tasks' PCIe transfers with LS requests, it results in LS request latency several orders of magnitude higher than StreamBox and PCIe CFS. The results indicate that when LS tasks are given sufficiently high priority, the performance of PCIe CFS is nearly identical to that of StreamBox's PCIe preemption strategy, demonstrating that PCIe CFS provides good responsiveness for LS tasks with negligible overheads. The evaluation of PCIe CFS with different scheduling weights in real-world workloads will be presented in § 8.4.

# 8.2 End-to-End Experimental Setup

**Testbeds.** We deploy and evaluate MISSILE in 4 GPU servers A~D (Tab. 4). To mitigate the impact of network latency, we follow Reef's practice [21] and deploy MISSILE's server and clients on the same host machine.

**Workloads.** We reference relevant literature [19, 21, 40, 45, 60, 67, 88] and select 12 representative computer vision, natural language, and generative models as testing workloads (Tab. 5 and 6). These models are categorized into LS and BE tasks based on their sizes. Models' input sizes (i.e., batch size, image size, and sequence length) follow settings of DISB [31], the DNN benchmark used by Reef [21]. Considering the varying computational capabilities and VRAM

**Table 5.** Testing DNN models (input image size: 224×224, LS input sequence length: 32, BE input sequence length: 64).

| Class | Model Name                                                                                                                             |

|-------|----------------------------------------------------------------------------------------------------------------------------------------|

| LS    | MobileNetV3 (A), SqueezeNet (B), ShuffleNet (C), EfficientNet (D),<br>ResNet34 (E), MobileBert (F), MobileViT (G), EfficientFormer (H) |

| BE    | ResNet152 (I), DenseNet161 (J), Bert (K), StableDiffusion(img2img) (L)                                                                 |

**Table 6.** Runtime (ms), size (MiB), and average utilization of SM & VRAM bandwidth (%, on Tesla V100) of testing DNNs.

| Tune | Task | Size  |       | Runti | Runtime (ms) |       |      |      |  |  |  |  |

|------|------|-------|-------|-------|--------------|-------|------|------|--|--|--|--|

| Туре | Task | Size  | P40   | V100  | A2000        | A5500 | SM   | VRAM |  |  |  |  |

|      | А    | 20.9  | 3.8   | 4.1   | 3.8          | 3.0   | 11.1 | 9.4  |  |  |  |  |

|      | В    | 4.7   | 2.1   | 2.4   | 2.2          | 1.6   | 22.0 | 7.5  |  |  |  |  |

|      | С    | 13.3  | 3.1   | 3.1   | 3.4          | 2.5   | 17.2 | 7.3  |  |  |  |  |

| LS   | D    | 17.7  | 3.3   | 3.9   | 3.7          | 2.6   | 18.1 | 12.1 |  |  |  |  |

| LS   | E    | 83.1  | 4.5   | 3.8   | 4.4          | 2.5   | 40.3 | 7.2  |  |  |  |  |

|      | F    | 93.8  | 23.0  | 22.6  | 23.8         | 19.5  | 4.9  | 3.0  |  |  |  |  |

|      | G    | 21.3  | 9.3   | 18.7  | 9.6          | 7.3   | 19.0 | 2.5  |  |  |  |  |

|      | Η    | 109.9 | 13.5  | 10.9  | 11.8         | 9.5   | 24.1 | 9.9  |  |  |  |  |

|      | Ι    | 229.3 | 55.5  | 67.4  | 32.5         | 53.7  | 75.2 | 13.9 |  |  |  |  |

| BE   | J    | 109.2 | 69.9  | 83.0  | 35.9         | 57.7  | 47.0 | 21.7 |  |  |  |  |

| DE   | Κ    | 422.1 | 37.7  | 43.6  | 21.8         | 32.4  | 63.5 | 13.3 |  |  |  |  |

|      | L    | 238.2 | 289.2 | 193.2 | 155.8        | 140.4 | 86.6 | 10.4 |  |  |  |  |

bandwidth of the 4 GPUs, we set the batch size for BE tasks to be 32 for both Tesla V100 and RTX A5500, 16 and 8 for Tesla P40 and RTX A2000, respectively. LS services' clients send requests following two patterns: 1) Poisson distribution; 2) Apollo trace, which is a real-time DNN inference trace collected from Baidu's Apollo autonomous driving system. Both were adopted by Reef [21] and Orion [19] to evaluate their systems. BE tasks run in a closed-loop manner.

Testing scenarios. We evaluated MISSILE in 3 scenarios:

1) *In-VRAM model serving*. In this case, we evaluate whether MISSILE can eliminate intra- and inter-SM contention without considering the PCIe bus congestion. On servers A-D, we deploy LS models A-I and BE models J-M in GPU's VRAM before serving requests. As MISSILE and baselines don't support request batching, each LS model has 4 instances to serve multiple requests concurrently. Each LS client sends requests following two patterns: 1) Poisson distribution (QPS is fit to Apollo trace's value), and 2) Apollo trace.

2) Model swapping on PCIe bus. In this scenario, we simulate the case where many DNNs are stored in host memory, and a DNN needs to be preloaded into VRAM before serving a request, causing PCIe bus congestion. This scenario is common for multi-DNN serving [20, 57, 74]. Due to space limitations, we only evaluate this scenario on server A, as the performance of PCIe-bound tasks mainly depends on PCIe bus bandwidth and PCIe scheduling algorithms. We deploy 8 LS models (A-H in Tab. 5, with each model running 2 instances) and 4 BE models (I-L) in host memory. The clients for LS models send requests by replaying the Apollo trace. We scale the Apollo trace's request interval to 2× because its average request interval is much smaller than the DNN's PCIe transmission delay.

3) *Ablation study*. In this scenario, we use the settings from scenarios #1 and #2, along with the Apollo trace, to explore the effects of different components on MISSILE's performance.

**Baselines.** We select MPS [50], TGS [67], and Orion [19] as baselines. Since TGS inherently supports the colocation of one LS and one BE container, we forward CUDA requests from each LS service and BE task to these two containers in a round-robin fashion. As the maximum number of instances supported by MPS is constrained, and too many MPS instances concurrently executing on one GPU can lead to severe contention, we evenly divide the GPU into two MPS instances and serve LS and BE tasks on them separately in a round-robin manner (we name it MPS+). Considering that Orion's open-source code only supports DNN inference on PyTorch's backend with outdated CUDA and cuDNN libraries, we implement Orion's scheduling policy within MISSILE to ensure comparison fairness.

Scenario #2 needs to evaluate DNNs' performance with different nice and scheduling policies. Specifically, when evaluating MISSILE, BE models' nice is set to be 100, and LS models' nice are configured with 1/20/10K (the corresponding settings are referred to as MISSILE-1, -20, and -10K, respectively). The implementation of StreamBox's PCIe preemption policy is also incorporated into MISSILE as a baseline (named as MISSILE-SB). Its performance is regarded as the optimum value when colocating LS and BE tasks.

**Evaluation metrics.** For LS services, we gather their p99 latency (including queueing delays), while for BE tasks, we collect their throughput (# samples processed per second).

#### 8.3 Evaluation of In-VRAM Model Serving

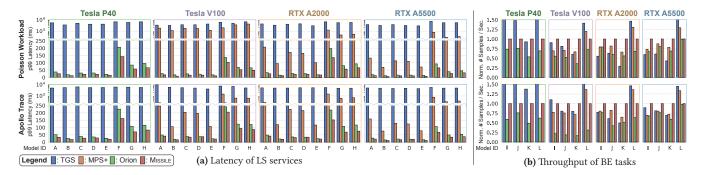

We present the results in Fig.12. In the Poisson and Apollo workloads, MISSILE demonstrates the lowest p99 latency for LS models compared to TGS, MPS+, and Orion, decreasing by up to ~30%, ~50%, ~36%, and ~48% compared to Orion's results. Its BE throughput is higher than Orion, although lower than TGS and MPS+ in some cases. That's because both TGS and MPS+ sacrifice LS services' tail latency to achieve higher overall throughput. TGS exhibits the highest p99 latency for LS services. This can be attributed to: 1) the substantial overhead resulting from frequent CUDA context switches between GPU containers; 2) the feedback-based dynamic sending rate control algorithm fluctuates containers' resource allocation. The high LS p99 latency of MPS+ can be attributed to the fact that MPS+ isolates only SM resources without addressing VRAM channel conflicts. Across P40, V100, RTX A2000, and RTX A5500, the BE throughput of MISSILE is up to ~2.0×, ~6.1×, ~2.3×, and ~1.7× compared to Orion, respectively. This significant improvement can be attributed to the challenges faced by Orion in identifying suitable co-execution of BE kernels (as elaborated in §3.1).

Figure 12. Evaluation results in In-VRAM Model Serving. Note: MPS is no longer supported on Tesla P40.

Legend

10

atency

Figure 13. Results of Model Swapping on PCIe Bus.

10

ế 10<sup>8</sup>

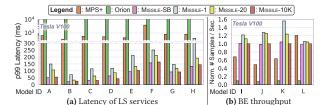

#### 8.4 Evaluation of Model Swapping on PCIe Bus

We have demonstrated that MISSILE exhibits superior performance compared to the baseline in both intra- and inter-SM isolation. Now, we evaluate MISSILE in terms of PCIe bus isolation. Owing to TGS's inadequate performance in LS tail latency, we omit it from the baselines in this experiment. The results are shown in Fig.13. Orion demonstrates the poorest LS p99 latency and BE throughput on all models. This is attributed to Orion's multi-streaming execution without implementing PCIe bus control. For all LS models, both MISSILE-10K and MISSILE-SB exhibit optimal p99 latency. While the throughput of BE tasks running on both MISSILE-SB and MISSILE-10K improved by up to ~2× compared to MPS+, because NVIDIA's MPS cannot isolate PCIe bus between different instances. Compared to MISSILE-SB, MISSILE-1, 20, and 10K exhibit a trend of decreasing latency for LS services and reduced throughput for BE tasks. This proves that MISSILE's PCIe CFS is capable of fine-grained allocating PCIe bandwidth among tenants based on their weights (nice), which is unsupported by StreamBox's[68] PCIe bus preemption. When LS tasks are assigned a larger nice value, more PCIe bus bandwidth is reserved for them. The runtime of all LS models and the throughput of BE models I-K are significantly correlated with LS tasks' nice values. But model L is least affected. This is because the runtime of LS models and BE models I-K is significantly shorter than their model transfer time (Tab. 6), thereby making the PCIe bus bottleneck more apparent. In contrast, L's runtime is much longer than its model transfer time, allowing the model loading time to be hidden by the kernel's runtime on the GPU.

Figure 14. Ablation study in scenarios #1 and #2.

1.0

0.4

# 8.5 Ablation Study

We utilize settings from scenarios #1 and #2 along with Apollo trace to analyze the impact of various components on MISSILE's performance. By removing certain components from MISSILE, we establish four baselines: i) Multi-streaming (no resource isolation); ii) Multi-streaming + PCIe CFS (not necessary for reevaluating scenario #1); iii) Multi-streaming + PCIe CFS + elastic SM multiplexing; and iv) Multi-streaming + PCIe CFS + elastic SM multiplexing + VRAM channel isolation (full MISSILE). The results are depicted in Fig. 14.

In scenario #1, the introduction of elastic SM multiplexing drastically reduces LS tasks' latency, while enabling VRAM channel isolation decreases LS tasks' latency by approximately 20×. However, BE tasks' throughput declines with the introduction of SM and VRAM isolation due to these techniques constraining excessive resource consumption by BE tasks.

In scenario #2, introducing PCIe CFS reduces LS tasks' latency significantly. Nevertheless, compared to the ablation evaluation results in scenario #1, SM multiplexing and VRAM channel isolation exhibit lesser improvement on LS tasks' latency. This is because BE models spend more time loading their weights, reducing the chances of intra- and inter-SM conflicts with LS models. Furthermore, after enabling VRAM channel isolation, BE tasks' throughput diminishes. This is because MISSILE cannot adjust memory-bound BE kernels' VRAM channel allocation when LS models are inactive or awaiting PCIe data transmission completion. We will elaborate on the solution to this issue in § 9.

# 9 Discussions and Future Work

**Integration with NVIDIA MIG.** The objective of MISSILE is to offer hardware resource isolation for DNN inference services on mid-to-low-end GPUs lacking MIG support. In the future, MISSILE may integrate with MIG on NVIDIA's flagship enterprise GPUs (e.g., A100, H100), enabling partitioning of VRAM channels within each MIG instance. However, it's crucial to acknowledge that the L2 caches in A100 [47] and H100 [48] consist of multiple separate caches, making their L2 caches a hybrid of UMA and NUMA. Consequently, MISSILE's reverse engineering approach requires slight adaptation for A100 and H100.

**Extending to AMD GPUs.** MISSILE has thus far been implemented and evaluated only on NVIDIA GPUs. Nevertheless, we posit that extending MISSILE to AMD's GPUs is viable because: 1) AMD's GPU architecture [15] closely resembles NVIDIA's; 2) AMD's ROCm [3], HIP [1] (comparable to CUDA), and kernel drivers [2] are fully open-sourced; and 3) AMD offers an official SM masking interface [54] (akin to NVIDIA's TMD [32]).

**GPU L2 cache side-channel attacks.** Reverse engineering the hash mapping of the CPU's last-level cache (LLC) [5, 34, 71] enables side-channel attacks on CPUs [34, 38]. MISSILE poses side-channel threats for the GPU L2 cache. Fully decrypting the GPU's VRAM channel and L2 cacheline hash mappings could facilitate side-channel attacks on the GPU's L2 cache, similar to those on the GPU's TLB [81].

**Fault isolation.** Like Reef [21], Paella [45], and Orion [19], MISSILE aggregates multiple workloads into one CUDA context to reduce task switching overhead, MISSILE and these solutions can't isolate colocated DNNs' GPU runtime errors. However, we believe this is acceptable, as MISSILE relies on TVM [11] to generate and check CUDA kernels, and runtime errors due to incorrect kernel implementations are unlikely to occur. In the future, MISSILE could isolate faults through static analysis-based [42] or runtime-based [56] methods.

# 10 Related Work

**CPU cache partitioning and memory bandwidth isolation.** In multi-tenant cloud data centers, contention in CPU's last-level cache (LLC) and main memory bandwidth can significantly impact the service quality [80]. Many work reverse engineered the hash mapping function of CPU Lastlevel cache (LLC) [5, 18, 43] and partitioned LLC for different tenants using cache coloring [18, 59, 72], which is inapplicable to GPUs (we've elaborated the reason in § 5.2). In response to the growing demand, Intel has introduced Cache Allocation Technology [23], Memory Bandwidth Allocation [29], and Dynamic Resource Control [79] on its server CPUs to partition the LLC and memory bandwidth. **GPU compute unit partitioning.** GPU compute unit partitioning has been supported at both hardware and software level. Both NVIDIA [7, 32] and AMD [53] have exposed their hardware interfaces to control a kernel's SM placement. A widely-used software-based solution is kernel padding [21, 45], which merges multiple kernels into one monolithic kernel for co-execution. This approach severely limits the concurrency because it requires the colocated BE kernel's runtime to be smaller than LS kernel's. This technique can help MISSILE extend to other vendors' GPUs.

**GPU VRAM channel isolation.** Although some work has proposed new GPU architectures in simulators to support VRAM channel isolation [83], GPU's VRAM channel isolation is much more challenging than compute unit partitioning on commodity GPUs, because only NVIDIA has so far implemented static partitioning (a.k.a., Multi-instance GPU, MIG [36]) for L2 cache and VRAM on a few flagship server GPUs (e.g., A100, H100). FGPU [33] only implemented VRAM channel isolation on GTX 1080 and V100, and we've elaborated on its limitations in § 3.2.

# 11 Conclusion

This paper presents MISSILE, a general, hardware-level, and fine-grained GPU isolation solution for multi-tenant DNN inference on NVIDIA GPUs. MISSILE isolates conflicts of SM units, VRAM channels, and the PCIe bus by elastic SM multiplexing, fine-grained software-level cache coloring, and PCIe completely fair scheduler. MISSILE mitigates the degradation of BE throughput observed in other GPU sharing techniques based on interference-aware multiplexing when multiple LS services are concurrently executing. Compared to state-ofthe-art gpu sharing solutions, MISSILE reduces LS service p99 latency by up to 50% and achieves up to 6.1× throughput of BE tasks. When considering PCIe bus contention, MISSILE supports fine-grained bandwidth allocation among tenants and shows the lowest LS latency and highest BE throughput.

# Acknowledgments

We thank Dr. Liping Zhang (Alibaba Group), Dr. Zhifeng Jiang (HKUST), Mr. Yuanchi Zhang (Tsinghua University), and Mr. Guoqing Luo (University of Alberta) for providing insightful suggestions. Yongkang Zhang is the corresponding author (E-mail: yzhangne@cse.ust.hk).

# References

- AMD. 2024. AMD HIP Library repository. https://github.com/ROCm/ HIP.

- [2] AMD. 2024. AMD ROCK Kernel Driver repository. https://github.com/ ROCm/ROCK-Kernel-Driver.

- [3] AMD. 2024. AMD ROCm Library repository. https://github.com/ ROCm/ROCm.

- [4] Tanya Amert, Nathan Otterness, Ming Yang, James H. Anderson, and F. Donelson Smith. 2017. GPU Scheduling on the NVIDIA TX2: Hidden Details Revealed. In 2017 IEEE Real-Time Systems Symposium, RTSS

2017, Paris, France, December 5-8, 2017. IEEE Computer Society, 104– 115. https://doi.org/10.1109/RTSS.2017.00017

- [5] Gorka Irazoqui Apecechea, Thomas Eisenbarth, and Berk Sunar. 2015. Systematic Reverse Engineering of Cache Slice Selection in Intel Processors. *IACR Cryptol. ePrint Arch.* (2015), 690. http://eprint.iacr.org/ 2015/690

- [6] Zhihao Bai, Zhen Zhang, Yibo Zhu, and Xin Jin. 2020. PipeSwitch: Fast Pipelined Context Switching for Deep Learning Applications. In 14th USENIX Symposium on Operating Systems Design and Implementation, OSDI 2020, Virtual Event, November 4-6, 2020 (2020). USENIX Association, 499–514. https://www.usenix.org/conference/osdi20/ presentation/bai

- [7] Joshua Bakita and James H. Anderson. 2023. Hardware Compute Partitioning on NVIDIA GPUs. In 29th IEEE Real-Time and Embedded Technology and Applications Symposium, RTAS 2023, San Antonio, TX, USA, May 9-12, 2023. IEEE, 54–66. https://doi.org/10.1109/RTAS58335. 2023.00012

- [8] Nicola Capodieci, Roberto Cavicchioli, Marko Bertogna, and Aingara Paramakuru. 2018. Deadline-Based Scheduling for GPU with Preemption Support. In 2018 IEEE Real-Time Systems Symposium, RTSS 2018, Nashville, TN, USA, December 11-14, 2018. IEEE Computer Society, 119–130. https://doi.org/10.1109/RTSS.2018.00021

- [9] Shubham Chaudhary, Ramachandran Ramjee, Muthian Sivathanu, Nipun Kwatra, and Srinidhi Viswanatha. 2020. Balancing efficiency and fairness in heterogeneous GPU clusters for deep learning. In EuroSys '20: Fifteenth EuroSys Conference 2020, Heraklion, Greece, April 27-30, 2020, Angelos Bilas, Kostas Magoutis, Evangelos P. Markatos, Dejan Kostic, and Margo I. Seltzer (Eds.). ACM, 1:1–1:16. https://doi. org/10.1145/3342195.3387555

- [10] Quan Chen, Hailong Yang, Jason Mars, and Lingjia Tang. 2016. Baymax: QoS Awareness and Increased Utilization for Non-Preemptive Accelerators in Warehouse Scale Computers. In Proceedings of the Twenty-First International Conference on Architectural Support for Programming Languages and Operating Systems, ASPLOS 2016, Atlanta, GA, USA, April 2-6, 2016, Tom Conte and Yuanyuan Zhou (Eds.). ACM, 681–696. https://doi.org/10.1145/2872362.2872368

- [11] Tianqi Chen, Thierry Moreau, Ziheng Jiang, Lianmin Zheng, Eddie Q. Yan, Haichen Shen, Meghan Cowan, Leyuan Wang, Yuwei Hu, Luis Ceze, Carlos Guestrin, and Arvind Krishnamurthy. 2018. TVM: An Automated End-to-End Optimizing Compiler for Deep Learning. In 13th USENIX Symposium on Operating Systems Design and Implementation, OSDI 2018, Carlsbad, CA, USA, October 8-10, 2018, Andrea C. Arpaci-Dusseau and Geoff Voelker (Eds.). USENIX Association, 578– 594. https://www.usenix.org/conference/osdi18/presentation/chen

- [12] Seungbeom Choi, Sunho Lee, Yeonjae Kim, Jongse Park, Youngjin Kwon, and Jaehyuk Huh. 2022. Serving Heterogeneous Machine Learning Models on Multi-GPU Servers with Spatio-Temporal Sharing. In 2022 USENIX Annual Technical Conference, USENIX ATC 2022, Carlsbad, CA, USA, July 11-13, 2022, Jiri Schindler and Noa Zilberman (Eds.). USENIX Association, 199–216. https://www.usenix.org/conference/ atc22/presentation/choi-seungbeom

- [13] Marcus Chow, Ali Jahanshahi, and Daniel Wong. 2023. KRISP: Enabling Kernel-wise RIght-sizing for Spatial Partitioned GPU Inference Servers. In IEEE International Symposium on High-Performance Computer Architecture, HPCA 2023, Montreal, QC, Canada, February 25 - March 1, 2023. IEEE, 624–637. https://doi.org/10.1109/HPCA56546.2023.10071121

- [14] Weihao Cui, Han Zhao, Quan Chen, Ningxin Zheng, Jingwen Leng, Jieru Zhao, Zhuo Song, Tao Ma, Yong Yang, Chao Li, and Minyi Guo. 2021. Enable simultaneous DNN services based on deterministic operator overlap and precise latency prediction. In *International Conference for High Performance Computing, Networking, Storage and Analysis, SC 2021, St. Louis, Missouri, USA, November 14-19, 2021*, Bronis R. de Supinski, Mary W. Hall, and Todd Gamblin (Eds.). ACM, 15. https://doi.org/10.1145/3458817.3476143

- [15] Sal Dasgupta, Teja Singh, Ashish Jain, Samuel Naffziger, Deepesh John, Chetan Bisht, and Pradeep Jayaraman. 2020. Radeon RX 5700 Series: The AMD 7nm Energy-Efficient High-Performance GPUs. In 2020 IEEE International Solid- State Circuits Conference, ISSCC 2020, San Francisco, CA, USA, February 16-20, 2020. IEEE, 150–152. https: //doi.org/10.1109/ISSCC19947.2020.9062947

- [16] Jacob Devlin, Ming-Wei Chang, Kenton Lee, and Kristina Toutanova. 2019. BERT: Pre-training of Deep Bidirectional Transformers for Language Understanding. In Proceedings of the 2019 Conference of the North American Chapter of the Association for Computational Linguistics: Human Language Technologies, NAACL-HLT 2019, Minneapolis, MN, USA, June 2-7, 2019, Volume 1 (Long and Short Papers), Jill Burstein, Christy Doran, and Thamar Solorio (Eds.). Association for Computational Linguistics, 4171–4186. https://doi.org/10.18653/V1/N19-1423

- [17] envytools. 2024. Envytools. https://github.com/envytools/envytools.

- [18] Alireza Farshin, Amir Roozbeh, Gerald Q. Maguire Jr., and Dejan Kostic. 2019. Make the Most out of Last Level Cache in Intel Processors. In Proceedings of the Fourteenth EuroSys Conference 2019, Dresden, Germany, March 25-28, 2019, George Candea, Robbert van Renesse, and Christof Fetzer (Eds.). ACM, 8:1–8:17. https://doi.org/10.1145/3302424.3303977

- [19] Strati Foteini, Ma Xianzhe, and Klimovic Ana. 2024. Orion: Interference-aware, Fine-grained GPU Sharing for ML Applications. In EuroSys '24: Nineteenth EuroSys Conference 2024, Athens, Greece, April 22-25, 2024. Association for Computing Machinery.

- [20] Arpan Gujarati, Reza Karimi, Safya Alzayat, Wei Hao, Antoine Kaufmann, Ymir Vigfusson, and Jonathan Mace. 2020. Serving DNNs like Clockwork: Performance Predictability from the Bottom Up. In 14th USENIX Symposium on Operating Systems Design and Implementation, OSDI 2020, Virtual Event, November 4-6, 2020. USENIX Association, 443– 462. https://www.usenix.org/conference/osdi20/presentation/gujarati

- [21] Mingcong Han, Hanze Zhang, Rong Chen, and Haibo Chen. 2022. Microsecond-scale Preemption for Concurrent GPU-accelerated DNN Inferences. In 16th USENIX Symposium on Operating Systems Design and Implementation, OSDI 2022, Carlsbad, CA, USA, July 11-13, 2022, Marcos K. Aguilera and Hakim Weatherspoon (Eds.). USENIX Association, 539–558. https://www.usenix.org/conference/osdi22/ presentation/han

- [22] Kaiming He, Xiangyu Zhang, Shaoqing Ren, and Jian Sun. 2016. Deep Residual Learning for Image Recognition. In 2016 IEEE Conference on Computer Vision and Pattern Recognition, CVPR 2016, Las Vegas, NV, USA, June 27-30, 2016. IEEE Computer Society, 770–778. https: //doi.org/10.1109/CVPR.2016.90

- [23] Andrew Herdrich, Edwin Verplanke, Priya Autee, Ramesh Illikkal, Chris Gianos, Ronak Singhal, and Ravi R. Iyer. 2016. Cache QoS: From concept to reality in the Intel® Xeon® processor E5-2600 v3 product family. In 2016 IEEE International Symposium on High Performance Computer Architecture, HPCA 2016, Barcelona, Spain, March 12-16, 2016. IEEE Computer Society, 657–668. https://doi.org/10.1109/HPCA.2016. 7446102

- [24] Yihan Hu, Jiazhi Yang, Li Chen, Keyu Li, Chonghao Sima, Xizhou Zhu, Siqi Chai, Senyao Du, Tianwei Lin, Wenhai Wang, Lewei Lu, Xiaosong Jia, Qiang Liu, Jifeng Dai, Yu Qiao, and Hongyang Li. 2023. Planning-oriented Autonomous Driving. In *IEEE/CVF Conference on Computer Vision and Pattern Recognition, CVPR 2023, Vancouver, BC, Canada, June 17-24, 2023.* IEEE, 17853–17862. https://doi.org/10.1109/ CVPR52729.2023.01712

- [25] Chien-Chin Huang, Gu Jin, and Jinyang Li. 2020. SwapAdvisor: Pushing Deep Learning Beyond the GPU Memory Limit via Smart Swapping. In ASPLOS '20: Architectural Support for Programming Languages and Operating Systems, Lausanne, Switzerland, March 16-20, 2020, James R. Larus, Luis Ceze, and Karin Strauss (Eds.). ACM, 1341– 1355. https://doi.org/10.1145/3373376.3378530

- [26] Gao Huang, Zhuang Liu, Laurens van der Maaten, and Kilian Q. Weinberger. 2017. Densely Connected Convolutional Networks. In 2017

IEEE Conference on Computer Vision and Pattern Recognition, CVPR 2017, Honolulu, HI, USA, July 21-26, 2017. IEEE Computer Society, 2261–2269. https://doi.org/10.1109/CVPR.2017.243

- [27] Jian Huang, Anirudh Badam, Laura Caulfield, Suman Nath, Sudipta Sengupta, Bikash Sharma, and Moinuddin K. Qureshi. 2017. Flash-Blox: Achieving Both Performance Isolation and Uniform Lifetime for Virtualized SSDs. In 15th USENIX Conference on File and Storage Technologies, FAST 2017, Santa Clara, CA, USA, February 27 - March 2, 2017, Geoff Kuenning and Carl A. Waldspurger (Eds.). USENIX Association, 375–390. https://www.usenix.org/conference/fast17/technicalsessions/presentation/huang

- [28] Mehmet Sinan Inci, Berk Gülmezoglu, Gorka Irazoqui Apecechea, Thomas Eisenbarth, and Berk Sunar. 2015. Seriously, get off my cloud! Cross-VM RSA Key Recovery in a Public Cloud. *IACR Cryptol. ePrint Arch.* (2015), 898. http://eprint.iacr.org/2015/898

- [29] Intel. 2024. Introduction to Memory Bandwidth Allocation. https://www.intel.com/content/www/us/en/developer/articles/ technical/introduction-to-memory-bandwidth-allocation.html.

- [30] Calin Iorgulescu, Reza Azimi, Youngjin Kwon, Sameh Elnikety, Manoj Syamala, Vivek R. Narasayya, Herodotos Herodotou, Paulo Tomita, Alex Chen, Jack Zhang, and Junhua Wang. 2018. PerfIso: Performance Isolation for Commercial Latency-Sensitive Services. In 2018 USENIX Annual Technical Conference, USENIX ATC 2018, Boston, MA, USA, July 11-13, 2018, Haryadi S. Gunawi and Benjamin C. Reed (Eds.). USENIX Association, 519–532. https://www.usenix.org/conference/ atc18/presentation/iorgulescu

- [31] SJTU IPADS. 2024. DISB: DNN Inference Serving Benchmark. https: //github.com/SJTU-IPADS/disb/tree/main.

- [32] J. D. Hall J. F. Duluk Jr, T. J. Purcell and P. A. Cuadra. 2018. Error checking in out-of-order task scheduling. https://patents.google.com/patent/ US20130152094. https://patents.google.com/patent/US20130152094 US Patent 9,965,321.

- [33] Saksham Jain, Iljoo Baek, Shige Wang, and Ragunathan Rajkumar. 2019. Fractional GPUs: Software-Based Compute and Memory Bandwidth Reservation for GPUs. In 25th IEEE Real-Time and Embedded Technology and Applications Symposium, RTAS 2019, Montreal, QC, Canada, April 16-18, 2019 (2019), Björn B. Brandenburg (Ed.). IEEE, 29–41. https: //doi.org/10.1109/RTAS.2019.00011