# Mover Logic: A Concurrent Program Logic for Reduction and Rely-Guarantee Reasoning (Extended Version)\*

Cormac Flanagan 💿

University of California, Santa Cruz, Santa Cruz, CA, USA

Stephen N. Freund ≥ •

Williams College, Williamstown, MA, USA

#### **Abstract**

Rely-guarantee (RG) logic uses thread interference specifications (relies and guarantees) to reason about the correctness of multithreaded software. Unfortunately, RG logic requires each function postcondition to be "stabilized" or specialized to the behavior of other threads, making it difficult to write function specifications that are reusable at multiple call sites.

This paper presents mover logic, which extends RG logic to address this problem via the notion of atomic functions. Atomic functions behave as if they execute serially without interference from concurrent threads, and so they can be assigned more general and reusable specifications that avoid the stabilization requirement of RG logic. Several practical verifiers (Calvin-R, QED, CIVL, Armada, Anchor, etc.) have demonstrated the modularity benefits of atomic function specifications. However, the complexity of these systems and their correctness proofs makes it challenging to understand and extend these systems. Mover logic formalizes the central ideas of reduction in a declarative program logic that provides a foundation for future work in this area.

**2012 ACM Subject Classification** Theory of computation  $\rightarrow$  Program verification; Theory of computation  $\rightarrow$  Program specifications; Software and its engineering  $\rightarrow$  Concurrent programming languages; Software and its engineering  $\rightarrow$  Formal software verification

Keywords and phrases concurrent program verification, reduction, rely-guarantee reasoning, synchronization

Funding This work was supported by NSF grants 2243636 and 2243637.

# 1 Introduction

Verifying that a multithreaded software system behaves correctly for all possible inputs and thread interleavings is a critically important problem in computer science. To verify large systems, verification techniques must employ modular reasoning in which each function's implementation is verified with respect to its specification. In a multithreaded system, writing precise and reusable function specifications is a rather difficult challenge, since concurrent threads can observe and change the state of a function call not just in its initial and final states, but also at any intermediate states during the function's execution. Thus, function specifications must describe not just the function's precondition and postcondition, but also how the function may influence and be influenced by other concurrent threads. To address this problem, Rely-Guarantee (RG) logic [32] uses function specifications that include:

- a guarantee G describing how each step of the function may update shared state, and

- $\blacksquare$  a rely assumption R describing the behavior of interleaved steps of other threads. The rely assumption might, for example, specify that interleaved steps preserve a data invariant.

<sup>\*</sup> To appear at ECOOP 2024.

#### 2 Mover Logic

Under RG logic, however, a function's postcondition must summarize not only the behavior the function itself but also the behavior of interleaved steps of other threads [55]. Consequently, RG function specifications are often specialized to the rely assumption and data invariants of a particular client, limiting reuse of those function specifications in other clients, as we illustrate in Section 2.

Lipton's theory of reduction [40] provides a promising approach to address this problem. It uses a commuting argument to show that certain functions are *atomic* and behave as if they execute serially (without interleaved steps of other threads). Consequently, atomic functions do not require interleaved rely assumptions, and they can be precisely specified using preconditions and postconditions that are independent of any specific client.

Reduction has been widely adopted in a variety of software validation tools, including dynamic analyses [17, 53, 54, 9], type systems [49, 23, 22, 21], and other tools [6, 60, 61, 59]. Over the past two decades, software verifiers based on reduction (e.g., Calvin-R [24], QED [15], CIVL [29, 37], Armada [41], and Anchor [19]) have demonstrated the utility of atomic function specifications in verifying sophisticated concurrent code. To date, however, reduction-based verifiers have not been based on an underlying program logic, such as RG logic. Instead, their soundness arguments are typically based on monolithic proofs whose complexity inhibits further research. To address this complexity barrier, we present mover logic, which extends RG logic to support atomic function specifications via reduction-based reasoning.

In mover logic, thread interference points are documented with yield annotations that have no run-time effect. Mover logic verifies that every sequence of operations between two yield points is reducible and hence amenable to sequential reasoning. In order to verify reducibility, mover logic uses synchronization specifications describing both when each thread can access each shared location and how those accesses commute with concurrent accesses of other threads. In contrast to RG logics that must stabilize all state predicates under the rely assumption, mover logic only needs to stabilize predicates at yield points. Atomic functions have no yield points and can thus be specified with traditional pre- and postconditions. Moreover, atomic function specifications need not include a client-specific rely assumption that would limit reuse in other clients that have different rely assumptions or data invariants.

Mover logic is a declarative program logic (similar in style to Hoare Logic and RG Logic) that helps explain and justify many subtle aspects of reduction-based verification, including:

- what code blocks are reducible;

- where yield annotations are required;

- which functions are atomic;

- what atomic and non-atomic function specifications mean;

- what reasoning is performed by the verifier;

- why this reasoning is sound; and

- which programs are verifiable or not verifiable, and why.

Mover logic simplifies the soundness proof for any specific verifier, because the proof now must only show that the verifier follows the rules of mover logic.

The presentation of our results proceeds as follows.

- Section 2 illustrates the specification entanglement problem of RG logic and shows how mover logic avoids this problem.

- Section 3 reviews Lipton's theory of reduction.

- Sections 4 and 5 present an overview of mover logic and additional examples.

- Section 6 formalizes a core multithreaded language.

- Section 7 and 8 present mover logic for this language.

- Sections 9 and 10 discuss related work and summarize our contributions.

For clarity of exposition, our presentation of mover logic targets an idealized multithreaded language that captures the essential complexities of multithreaded function specifications. Extending the logic to more complex languages remains an important topic for future work.

# 2 Limitations of Rely-Guarantee Logic

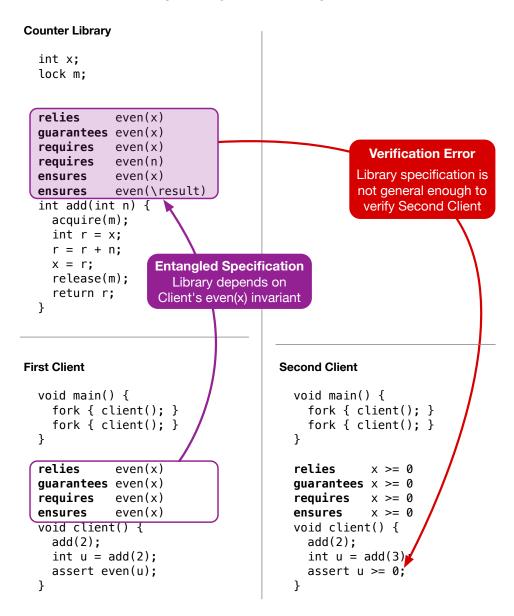

We motivate the need for mover logic via the example code in Figure 1 (left). That code consists of:

- A counter library that contains the function add(n) that adds n to the variable x and returns the new value of x. The initial value of variable x is 0, and it is protected by lock m, whose value is either the thread identifier tid of the thread holding the lock or 0 if unheld. The lock is initially unheld.

- 2. A first client that creates two threads, and each thread calls add(2) multiple times before asserting that x is even.

This program verifies under RG logic based on the invariant that x is always even. This even(x) invariant is a precondition and postcondition for both add() and client()<sup>1</sup>:

```

requires even(x)

ensures even(x)

```

In addition, each step by each thread in the program is guaranteed to preserve this invariant. As a result, each thread can rely on other threads to preserve the invariant:

```

relies even(x)

guarantees even(x)

```

These RG specifications are sufficient to verify that the program does not go wrong by failing the even(u) assertion in client(), but unfortunately the specification for add() is tightly-coupled, or entangled, with the even(x) data invariant from this particular client. A different client would necessitate revising and re-verifying the counter library, which makes modular verification more challenging and less scalable. For example, the second client in Figure 1 (right) enforces the data invariant  $x \ge 0$ , but it cannot be verified with the add() specification entangled with the first client. Others have noted this limitation as well (see, for example, [14, 55]).

# 2.1 Disentangling RG Specifications: First Attempt

The goal of this paper is to support specifications for library functions like add() that are not specialized to one particular client. As a first attempt to achieve that goal, the code in Figure 2 (left) uses the following natural postconditions for add(), where  $\old(x)$  and x refer to the value of x upon function entry and exit, respectively:

```

ensures x == \old(x) + n

ensures \result == x

```

<sup>&</sup>lt;sup>1</sup> Frame conditions, which specify the locations a function may read or modify, also play a key role in modular function specifications, but we do not consider them in this paper due to lack of space. Extending mover logic with frame conditions, perhaps using ideas from separation logic [46, 48], remains an important topic for future work.

# **Entangled Rely-Guarantee Specification**

Figure 1 Our idealized running example is an add(n) library function that atomically increases shared variable x by n. (Left) A rely-guarantee specification. The client's data invariant even(x) becomes entangled in the library specification. (Right) A second client that cannot be verified because the specification is insufficiently general.

# Disentangled RG Specification (First Attempt)

#### **Verification Error Counter Library** Postconditions are int x; not stable under lock m; rely assumption $m == tid ==> x == \old(x)$ relies ensures $x == \old(x) + n$ ensures \result == x int add(int n) { acquire(m); int r = x; r = r + n;x = r; release(m); return r;

#### Client

```

void main() {

fork { client(); }

fork { client(); }

}

relies    even(x)

guarantees even(x)

requires    even(x)

ensures    even(x)

void client() {

add(2);

int u = add(2);

assert even(u);

}

```

# Disentangled RG Specification (Second Attempt)

#### **Counter Library**

```

int x;

lock m;

```

```

relies

m == tid ==> x == \setminus old(x)

ensures true;

int add(int n) {

acquire(m);

int r = x;

r = r + n;

x = r;

release(m);

Verification Error

return r;

Assertion fails

under add's

weaker

postcondition

Client

void main() {

fork { client(); }

fork { client(); }

relies

even(x)

guarantees even(x)

requires

even(x)

even(x)

ensures

void client() {

add(2);

int u = add(2)

assert even(u);

}

```

Figure 2 (Left) An attempt to disentangle the library specification from the client that does not meet RG stability requirements. (Right) Another attempt that meets stability requirements but fails to verify the client.

#### 6 Mover Logic

In addition, if add() has no knowledge of its client, it must assume that other client threads could call add() with arbitrary arguments at any time, and so the natural rely assumption is that other threads may update x whenever the lock m is not held by the current thread. That assumption is most easily expressed as its contra-positive (where tid is the identifier of the current thread and lock m is held by that thread when m == tid):

Here,  $\old(x)$  and x refer to the value of x before and after an interleaved action of another thread, respectively.

To account for interleaved steps of other threads, a central requirement of RG logic is that all store predicates (e.g. preconditions, postconditions, and invariants) used to reason about program behavior must be stable under this rely assumption R. This means that interleaved R-steps from other threads must not invalidate those predicates. In the case of add in Figure 2 (left), the postcondition  $x == \old(x) + n & \old(x) +$

# 2.2 Disentangling RG Specifications: Second Attempt

To ensure stability we must weaken the add() function's postcondition to be stable under the rely assumption, as shown in Figure 2 (right). Unfortunately, the resulting stable post condition is simply true, which no longer guarantees anything about the value of x and is too weak to verify the client.

# 2.3 Broken Invariants and Bidirectional Entanglement

As a more challenging example, consider the add() library variant in Figure 3 (left) that temporarily breaks the even(x) invariant while holding the lock. In this case, the invariant holds only when lock m is free:

$$m == 0 ==> even(x)$$

Stores at the program points in which the invariant is broken are not intended to be observable by clients. However, the revised RG specifications for add() and the client must now be based on this conditional invariant, resulting in two problems. First, the library specification is again specialized to the client's even(x) invariant. Second, the library's internal locking discipline leaks into the client's specification, limiting our ability to modify the library code without breaking clients. This example demonstrates that RG reasoning may force us to lose modularity between client and library.

# 3 Review of Lipton's Theory of Reduction

Our solution to this specification problem employs Lipton's theory of reduction [40], which classifies how steps of one thread commute with concurrent steps of another thread.

■ A step is a *right-mover* (R) if it commutes "to the right" of any subsequent step by a different thread, in that performing the steps in the opposite order does not change the final store. A lock acquire is a right-mover because any subsequent step from another thread cannot modify that lock.

# Verifiable but Entangled **Rely-Guarantee Specification**

#### **Counter Library**

```

int x;

lock m;

relies

m == 0 ==> even(x)

guarantees m == 0 ==> even(x)

m == 0 ==> even(x)

requires

requires

even(n)

m == 0 ==> even(x)

ensures

ensures

even(\result)

int add(int n) {

acquire(m);

int r = x;

r = r + n;

x = 1;

// Break invariant

x = r;

// and restore it

release(m);

return r;

Entangled Specifications

Library depends on Client's

even(x) invariant

· Client depends on Library's

Client

synchronization

void main() {

fork { client(); }

fork { client(); }

relies

m == 0 ==> even(x)

guarantees m == 0 ==> even(x)

requires m == 0 ==> even(x)

ensures

m == 0 ==> even(x)

void client() {

add(2);

int u = add(2);

assert even(u);

```

# Verifiable and Disentangled **Mover Logic Specification**

#### **Counter Library**

```

int x

both-mover if m == tid;

lock m

write right-mover

if \odd(m) == 0 \&\& m == tid

write left-mover

if \odd(m) == tid && m == 0;

atomic

x == \operatorname{old}(x) + n

ensures

ensures

\text{result} == x

int add(int n) {

acquire(m);

int r = x;

r = r + n;

x = 1;

// Break invariant

x = r;

// and restore it

release(m);

return r;

Disentangled

Specifications!

```

#### Client

```

void main() {

fork { client(); }

fork { client(); }

relies

even(x)

guarantees even(x)

requires

even(x)

ensures

even(x)

void client() {

add(2);

yield;

int u = add(2);

assert even(u);

yield;

```

Figure 3 A second version of the counter library with a temporarily broken even(x) invariant. (Left) Under RG logic, the library specification is entangled with the client's even(x) invariant and the client specification is entangled with the library's synchronization discipline. (Right) Under mover logic, the specifications are cleanly disentangled.

Figure 4 Reduction applied to an execution trace of add() from Figure 1.

- Conversely, a step is a *left-mover* (L) if it commutes "to the left" of a preceding step of a different thread. A lock release is a left-mover because any preceding step cannot modify that lock.

- A step is a both-mover (B) if it is both a left- and a right-mover, and it is a non-mover (N) if neither. A race-free memory access is a both-mover because there are no concurrent, conflicting accesses. An access to a race-prone variable is a non-mover since there may be concurrent writes.

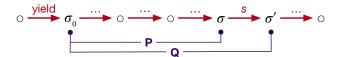

A sequence of steps performed by a particular thread is reducible if consists of (1) zero or more right-movers; (2) at most one non-mover; and (3) zero or more left-movers. That is, a sequence is reducible if the commutativity of the steps match the pattern  $R^*[N]L^*$ . Any interleaved steps of other threads can be "commuted out" to produce a serial execution.

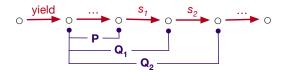

Figure 4 illustrates this technique for a call to add() interleaved with steps of a second thread. In that figure and below, the solid and hollow arrow heads indicate steps from different threads, and arrows labeled "..." represent any number of steps by that thread. The steps of add() have the mover behavior RBBBLB, matching the reducible pattern  $R^*[N]L^*$ . Thus we can reason about add() as if it executes sequentially and assign it the intuitive postcondition  $x == \old(x) + n &\& \result == x$ .

# 4 Overview of Mover Logic

Mover logic extends RG logic to verify that certain functions are *atomic* and can therefore be assigned more precise (unstabilized) postconditions than under RG logic. Figure 3 (right) shows a mover logic specification for our library/client example. The declaration

```

int x both-mover if m == tid;

```

means that accesses to x are both-movers provided that the current thread holds lock m. All other accesses are errors. The declaration for lock m specifies that acquires (which change m from 0 to the current thread's identifier tid) are right-movers and releases (which change m from tid back to 0) are left-movers:

```

lock m write right-mover

if \old(m) == 0 && m == tid

write left-mover

if \old(m) == tid && m == 0;

```

These mover specifications are sufficient to verify that add is atomic. Consequently, there is no need to apply the rely assumption at each intermediate store inside this atomic function. Instead, sequential reasoning suffices to establish the desired postcondition  $x == \old(x) + n \&\& \result == x$ .

The client() function in Figure 3 (right) is not atomic because steps of other threads could be interleaved between the two calls to add(2). Mover logic uses a yield annotation to identify that thread interference may occur at that point, and the store invariants at yields must be stable under the rely assumption:

```

relies even(x);

guarantees even(x);

```

Note that this thread guarantee does not need to summarize individual steps inside the callee add(), which would expose the broken invariant. Instead, it summarizes the entire atomic effect of add(), which preserves the even(x) invariant. With mover logic, the client() specification is independent of the internal synchronization discipline inside add().

This library/client example illustrates several benefits of mover logic:

- Verifying that add() is atomic enables sequential reasoning inside add().

- We thus avoid applying the rely assumption at each program point inside add().

- As a result, add() satisfies the desired postcondition  $x == \operatorname{old}(x) + n && \operatorname{result} == x$ , which is independent of the client-specific data invariant even(x).

- On the client side, the thread guarantee even(x) summarizes the entire behavior of add(), rather than the behavior of each individual step.

- Consequently, the client can be verified based on the illusion that even(x) always holds, with no loss of soundness.

Thus, mover logic disentangles the library specification from the data invariant of the client while also disentangling the client specification from the library synchronization discipline.

# 5 Additional Examples

# 5.1 Spin Lock

To further illustrate the benefits of disentangled specifications, Figure 5 (left) shows our counter library rewritten to employ a user-defined spin lock. The <code>spin\_lock()</code> code employs a compare-and-set operation (<code>cas</code>) to attempt to change the lock 1 from 0 to the current thread's <code>tid</code>. The <code>cas</code> operation returns true if the update succeeds, and false otherwise. Thus, the function retries until the update is success, at which point the current thread holds the lock. The <code>spin\_unlock()</code> function releases the lock by setting 1 back to 0.

Mover logic verifies that calls to spin\_lock() and spin\_unlock() are atomic right- and left-movers, respectively. That enables us to avoid entangled specifications for the spin lock and counter libraries, and the counter library's add specification is *identical* to the earlier implementation. It is still atomic and it guarantees the same post condition.

#### 5.2 Lock-Free Queue

Figure 5 (top right) shows a lock-free single-element queue, where buf holds either the single enqueued int or None if the queue is empty, as indicated by the declared type Optional[int].

The enqueue(v) function uses cas to switch buf from None to v and is atomic since failing cas operations are both-movers. The dequeue() function use the action  $r \sim buf$  to denote an *unstable read* of buf that can load any value into the local variable r [21]. Unstable reads can be treated as right-movers since they commute past steps by other

#### Verifiable Spin Lock, Counter, Client

```

Spin Lock Library

```

```

int l write right-mover

if \od(l) == 0 \&\& l == tid

write left-mover

if \old(l) == tid && l == 0;

atomic right-mover

ensures l == tid

void spin_lock() {

while (!cas(l, 0, tid)) {

skip;

}

}

atomic left-mover

requires l == tid

void spin_unlock() {

l = 0;

}

Disentangled

Specifications!

Counter Library

both-mover if l == tid;

int x

atomic

ensures x == \operatorname{old}(x) + n

ensures \result == x

int add(int n) {

spin_lock();

int r = x;

r = r + n;

// Break invariant

x = 1;

x = r;

//

and restore it

spin_unlock();

return r;

}

Disentangled

Specifications!

Client

void main() {

fork { client(); }

fork { client(); }

relies

even(x)

guarantees even(x)

requires

even(x)

ensures

even(x)

void client() {

add(2);

(yield;

int u = add(2);

assert even(u);

(yield;

```

## **Verifiable Lock-Free Queue Library**

```

Optional[int] buf non-mover;

```

```

atomic

requires n != None

ensures buf == n

void enqueue(int n) {

while (!cas(buf, None, n)) {

skip;

}

}

atomic

ensures \result == \old(buf)

ensures buf == None

int dequeue() {

Optional[int] r ~= buf;

while (r == None) \{ r \sim= buf; \}

while (!cas(buf, r, None)) {

r \sim= buf;

while (r == None) \{ r \sim= buf; \}

}

return r;

}

```

#### **Verifiable Lock-Free Stack Library**

List top non-mover;

```

atomic

ensures head(top) == v

ensures tail(top) == \old(top)

void push(int v) {

List t ~= top;

List nu = v::t;

while (!cas(top, t, nu)) {

t ~= top;

nu = v::t;

}

}

ensures head(\old(top)) == \result

ensures tail(\old(top)) == top

int pop() {

List t ~= top;

while (t == Nil) { t \sim= top; }

List tl = tail(t);

while (!cas(top, t, tl) {

t ~= top;

while (t == Nil) { t \sim= top; }

tl = tail(t);

return head(t);

```

Figure 5 (Left) A new implementation of the counter library using a user-defined spin lock. (Top Right) A single-element lock-free queue. (Bottom Right) A lock-free stack.

threads.<sup>2</sup> Consequently, the dequeue() function is atomic. All executions of that function consist of unstable reads (right-movers) and failed cas operations (both-movers) followed by a successful cas (non-mover). These sequences match the reducible pattern  $R^*[N]L^*$ . Moreover, the final cas ensures that r is equal to the pre-cas value of buf, which enables mover logic to establish the desired post-conditions \result == \old(buf) and buf == None.

#### 5.3 Lock-Free Stack

Figure 5 (bottom right) shows a lock-free stack. This examples uses immutable lists, where Nil is the empty list, v::s adds v to the front of the list s, and head(s) and tail(s) extract the first element and the rest of s, respectively.<sup>3</sup>

The push(v) function is atomic since it has only one non-mover operation, namely the successful cas. The unstable reads, list allocations v::t, and failed cas operations are both-movers or right-movers. Therefore, we can assign push(v) the following intuitive post-condition without needing to stabilize under the rely assumption of a particular caller.

```

ensures head(top) == v

ensures tail(top) == \old(top)

```

The pop() function is also atomic due to similar reasoning and satisfies the following post-condition without the need to stabilize it.

```

ensures head(\old(top)) == \result

ensures tail(\old(top)) == top

```

# 6 Mover Logic Language

We formalize mover logic for the idealized language MML (mover logic language), which we summarize in Figure 6. Section 7.3 below translates our running example into MLL. In MLL, threads manipulate a shared store  $\sigma$  that maps variables to values. Variables include x,y,z, and m. We often use the variable m as a lock, where m is the thread identifier (tid) of the thread holding the lock, or 0 if it is not held.

Thread-local variables r are supported by having each thread access a separate variable  $r_{tid}$  for each thread tid. The language includes reads and writes to global and local variables, acquires and releases of locks, local computations, etc. For generality and simplicity, we abstract all of these store-manipulation operations as  $actions\ A\subseteq Tid\times Store\times Store$ . Note that an action may depend on the current thread's identifier. We write actions as formulae in which  $\old(x)$  and x to refer to the values of x in the pre-store and post-store, respectively. We write  $\langle A \rangle_x$  to denote an action that only changes x:

$$\langle A \rangle_x \stackrel{\mathrm{def}}{=} \{ (tid, \sigma, \sigma') \mid (tid, \sigma, \sigma') \in A \land \forall y \in Var. \ y \neq x \Rightarrow \sigma(y) = \sigma'(y) \}$$

We can then express assignments and locking operations as follows. Note that acquire(m) blocks if the lock is already held, *i.e.* if  $\old(m) \neq 0$ . We use the notation  $expr[x := \old(x)]$

<sup>&</sup>lt;sup>2</sup> Unstable reads are a proof technique that trades off our ability to reason about the value stored in **r** for the ability to treat the unstable read as a right-mover. An implementation of unstable read may exhibit any a subset of the allowed behaviors, including simply performing a conventional read.

<sup>&</sup>lt;sup>3</sup> The duplicated code in this example could be removed in a language with richer control structures such as break statements.

#### **Syntax**

```

(Statements)

skip | wrong | A | s; s | if C s else s

s ::=

| while C s \mid f() | yield

(Action)

A

\subseteq

Tid \times Store \times Store

(Thread Identifier)

\in Tid = \{1, 2, \ldots\}

t, u

::= A \diamond A

(Conditional Action)

C

(Variable Declaration)

:= x \ var\_spec

var

x, y, r, m

\in

Var

(Function Declaration)

fn ::= fn\_spec f() \{ s \}

\in FunctionName

f

(Declaration Table)

D ::= var \mid fn

(D is left implicit in the semantics for brevity)

```

#### **Semantics**

$$(State) \qquad \qquad \sigma \in Var \rightarrow Value \\ (State) \qquad \qquad \Sigma ::= s_1...s_n \cdot \sigma \\ (Evaluation \ Context) \qquad E ::= \bullet \mid E; s$$

$$\boxed{s \cdot \sigma \rightarrow_t s' \cdot \sigma'}$$

$$[E\text{-SEQ}] \qquad \qquad E[\text{skip}; s] \cdot \sigma \rightarrow_t \qquad E[s] \cdot \sigma \\ [E\text{-YIELD}] \qquad \qquad E[\text{yield}] \cdot \sigma \rightarrow_t \qquad E[\text{skip}] \cdot \sigma \\ [E\text{-ACTION}] \qquad \qquad E[A] \cdot \sigma \rightarrow_t \qquad E[\text{skip}] \cdot \sigma' \quad \text{if } (t, \sigma, \sigma') \in A \\ [E\text{-IF}] \qquad E[\text{if } (A_1 \diamond A_2) \ s_1 \ \text{else} \ s_2] \cdot \sigma \rightarrow_t \qquad E[s_i] \cdot \sigma' \quad \text{if } (t, \sigma, \sigma') \in A_i, \text{ for } i \in 1, 2 \\ [E\text{-WHILE}] \qquad \qquad E[\text{while} \ C \ s] \cdot \sigma \rightarrow_t \qquad E[\text{if} \ C \ (s; \text{while} \ C \ s) \ \text{else} \ \text{skip}] \cdot \sigma \\ [E\text{-CALL}] \qquad \qquad E[f()] \cdot \sigma \rightarrow_t \qquad E[s] \cdot \sigma \qquad \text{if } fn\_spec \ f() \ \{\ s\ \} \in D$$

$$\boxed{\Sigma \rightarrow \Sigma'}$$

$$\boxed{E\text{-STATE}}$$

$$\boxed{E\text{-STATE}}$$

$$\boxed{s_t \cdot \sigma \rightarrow_t s'_t \cdot \sigma'} \\ \hline s_1...s_t...s_n \cdot \sigma \rightarrow s_1...s'_t...s_n \cdot \sigma'$$

Figure 6 Mover Logic Language.

to denote expr with all occurrences of x replaced by  $\old(x)$ .

$$\begin{array}{lll} \operatorname{acquire}(m) & \overset{\operatorname{def}}{=} & \langle \operatorname{\verb"lold}(m) = 0 \wedge m = tid \rangle_m \\ \\ \operatorname{release}(m) & \overset{\operatorname{def}}{=} & \langle m = 0 \rangle_m \\ \\ x = expr & \overset{\operatorname{def}}{=} & \langle x = expr[x := \operatorname{\verb"lold}(x)] \rangle_x \end{array}$$

The unstable read  $r_{tid} \sim x$  from Section 5.3 may store any value in the local variable  $r_{tid}$ :

$$r_{tid} \sim x = x \stackrel{\text{def}}{=} \{ (tid, \sigma, \sigma[r_{tid} := v]) \mid v \in Value \}$$

Mover Logic Language includes if and while statements that condition execution either on whether a Boolean test is true or on whether a store-manipulating operation, such as cas, succeeds. To handle these two cases uniformly, we introduce a conditional action  $C = A_1 \diamond A_2$  where  $A_1$  is an action capturing a true test or successful operation and  $A_2$  is an action capturing a false test or failed operation. For generality, both cases may modify the store and both may be feasible on some pre-states.

We encode any state predicate  $B \subseteq Store$  as the conditional action  $\{(tid, \sigma, \sigma) \mid \sigma \in B\} \diamond \{(tid, \sigma, \sigma) \mid \sigma \notin B\}$  that distinguishes the true/false cases but never modifies the store. The following illustrates this encoding for the test  $x \ge 0$ .

$$x >= 0 \stackrel{\text{def}}{=} \{(tid, \sigma, \sigma) \mid \sigma(x) \ge 0\} \diamond \{(tid, \sigma, \sigma) \mid \sigma(x) < 0\}$$

As a more interesting example, we encode **cas** as the following conditional action:

$$cas(x,v,v') \stackrel{\text{def}}{=} \langle \text{lold}(x) = v \land x = v' \rangle_x \diamond I$$

where the identity action  $I = \{ (t, \sigma, \sigma) \mid t \in Tid \text{ and } \sigma \in Store \}$ . This definition permits cas to non-deterministically fail from any pre-state, which enables us to treat failed cas operations as both movers [19].

Given  $C = A_1 \diamond A_2$ , the if statement if C  $s_1$  else  $s_2$  may either: 1) evaluate the action  $A_1$  and then  $s_1$ , or 2) evaluate  $A_2$  and then  $s_2$ . The former is the "true" case and the latter is the "false" case, with the desired behavior regardless of whether C encodes a predicate test or a potentially-failing store update. To prevent the if statement from blocking, we require  $(A_1 \cup A_2)$  to be total on the state, i.e.  $\{\sigma \mid (t, \sigma, \underline{\ }) \in (A_1 \cup A_2)\} = State$ .

The while statement while C s behaves similarly. It iterates as long as C succeeds. We may need to test the negation of a conditional action. The negation of  $C = A_1 \diamond A_2$ , written !C, is simply  $A_2 \diamond A_1$ . The language includes the statement wrong to indicate than an error occurred. The statement assert B abbreviates if B skip else wrong. The goal of mover logic is to verify that programs do not go wrong.

Global variable declarations have the form  $x\ var\_spec$  and are kept in a global declaration table D. Function declarations have the form  $fn\_spec\ f()\ \{\ s\ \}$  and are also kept in D. Specifications for globals  $(var\_spec)$  and functions  $(fn\_spec)$  are described in Sections 7 and 8, respectively. For notational simplicity, D is left as an implicit argument to the evaluation judgments. To keep the core language as simple as possible, we elide formal parameters and return values. Instead, parameters and return values are passed in thread-local variables, as described below in Section 7.3.<sup>5</sup>

In our examples, we include types, curly braces, semicolons, and other standard syntactic forms to aid readability.

An execution state

$$\Sigma = s_1..s_n \cdot \sigma$$

$<sup>^4</sup>$  In a language with types, this definition can be easily adapted to only store type-correct values into  $r_{tid}$ .

<sup>&</sup>lt;sup>5</sup> Extending the language to include function arguments and results is straightforward, but it adds notational complexities that are orthogonal to our core contributions.

#### 14 Mover Logic

consists of sequence of threads  $s_1..s_n$  with a shared store  $\sigma$ . The evaluation relation  $\Sigma \to \Sigma'$  is based on evaluation contexts  $E[\ldots]$ , which identify the next statement to be evaluated. A state  $\Sigma = s_1..s_n \cdot \sigma$  is wrong if any thread is about to execute wrong, i.e., if  $s_i = E[\text{wrong}]$ . The semantics demonstrates that yield annotations have no effect at run time, but they are used in the mover logic described below.

# 7 Mover Logic Effects and Specifications

Mover logic divides the execution of each thread into reducible code sequences that are separated by yield statements identifying where thread interference may be observed.

#### 7.1 Effects

We use a language of effects to reason about reducible code sequences separated by yields:

$$e \in \mathit{Effect} \quad ::= \quad \mathbf{Y} \mid \mathbf{R} \mid \mathbf{L} \mid \mathbf{B} \mid \mathbf{N} \mid \mathbf{E}$$

where

- **Y** is the effect of a yield annotation;

- R describes right-mover actions;

- **L** describes left-mover actions;

- **B** describes both-mover actions that are both left- and right-movers;

- N describes non-mover actions that are neither left- nor right- movers; and

- E describes erroneous situations, such as the sequential composition of two non-mover actions without an intervening yield, which is not a reducible sequence.

Our strategy for verifying that yields correctly separate reducible sequences is based on the DFA [61] shown below (left). The DFA captures reducible sequences  $R^*[N]L^*$  separated by yields Y, which resets the DFA to the initial "pre-commit" state on the left to start a new reducible sequence. The first left-mover or non-mover in a reducible sequence is often called the *commit* action and moves us from the pre-commit to the post-commit phase.

From this DFA, we derive the ordering  $Y \sqsubseteq B \sqsubseteq R, L \sqsubseteq N \sqsubseteq E$ , which is also shown above (right). For example,  $R \sqsubseteq N$ , since for any effect sequences  $\alpha$  and  $\beta$ , if  $\alpha N \beta$  is accepted by this DFA, the  $\alpha R \beta$  is also accepted. We define a standard join operation  $\sqcup$  via this ordering.

We also define sequential composition  $e_1$ ;  $e_2$  and iterative closure  $e^*$ , as in [61]. For example,  $\mathbb{R}$ ;  $\mathbb{L} = \mathbb{N}$  since to show  $\alpha \mathbb{R} \mathbb{L} \beta$  is accepted by the DFA it is sufficient to show that

| $e_1; e_2$            | Y | В | R | L | N | Ε | e           | $e^*$ |

|-----------------------|---|---|---|---|---|---|-------------|-------|

| Y<br>B<br>R<br>L<br>N | Y | Y | Y | L | L | Е | Y           | Y     |

| В                     | Y | В | R | L | N | E | В           | В     |

| R                     | R | R | R | N | N | Ε | R           | R     |

| L                     | Y | L | E | L | Е | E | B<br>R<br>L | L     |

| N                     | R | N | E | N | E | Ε | N           | E     |

| E                     | Ε | Ε | Ε | Ε | Ε | Ε | Ε           | Ε     |

# 7.2 Mover Specifications

In mover logic, the verification of a thread tid is performed in the context of a mover specification describing how each program action A starting in the store  $\sigma$  commutes with steps of other threads. Thus, mover specifications M have the type

$$M:Action \times Tid \times Store \rightarrow Effect \setminus \{Y\}$$

For example, if action A is a local computation that only accesses thread-local variables, we would naturally have

$$M(A, tid, \sigma) = \mathbf{B}$$

Alternatively, if a global variable x is protected by a lock m, the write action x = expr might have the mover specification

$$M(\mathbf{x} = expr, tid, \sigma) = \left\{ \begin{array}{ll} \mathbf{B} & \text{if } \sigma(\mathbf{m}) = tid \\ \mathbf{E} & \text{otherwise} \end{array} \right.$$

indicating that the write is a both-mover only if thread tid holds lock m. Otherwise, it is an error. We assume that expr only accesses local variables, and that  $M(A, tid, \sigma)$  is never Y since actions do not yield.

We write mover specifications in the source code using the following notation, which is inspired by earlier reduction-based verifiers [29, 19, 20]:

```

var\_spec ::= var\_clause^*

var\_clause ::= read e if P | write e if P

```

where  $P \subseteq Tid \times Store \times Store$  is a two-store predicate describing the pre-store and post-store of the access to x in question. Further, P can depend on the current thread identifier tid. Similar to actions, we write these predicates as formulae in which  $\old(y)$  and y to refer to the values of y in the pre-store and post-store, respectively. To determine the mover effect of a variable access, we evaluate the specification clauses in order and take the effect of the first case where the condition P is satisfied. If no clauses apply, the access has the error effect E. More formally, given the specification for a variable x in the source code, we collect the sequence of clauses for reads and writes separately and then create the mover specification

M for x as follows:

$$\left[ \begin{array}{c} \texttt{read} \ e_1 \ \texttt{if} \ P_1 \\ \vdots \\ \texttt{read} \ e_n \ \texttt{if} \ P_n \end{array} \right] \quad \Longrightarrow \quad M(\texttt{r}_{tid} = \texttt{x}, tid, \sigma) = \left\{ \begin{array}{c} e_1 \quad \texttt{if} \ P_1(tid, \sigma, \sigma) \\ \vdots \quad \vdots \\ e_n \quad \texttt{if} \ P_n(tid, \sigma, \sigma) \\ \texttt{E} \quad \texttt{otherwise} \end{array} \right.$$

$$\left[ \begin{array}{c} \text{write } e_1 \text{ if } P_1 \\ \vdots \\ \text{write } e_n \text{ if } P_n \end{array} \right] \quad \Longrightarrow \quad M(\mathbf{x} = expr, tid, \sigma) = \left\{ \begin{array}{c} e_1 & \text{if } P_1(tid, \sigma, \sigma[\mathbf{x} := \sigma(expr)]) \\ \vdots & \vdots \\ e_n & \text{if } P_n(tid, \sigma, \sigma[\mathbf{x} := \sigma(expr)]) \\ \mathbf{E} & \text{otherwise} \end{array} \right.$$

where  $\mathbf{r}_{tid}$  is a local variable, expr only accesses thread-local variables,  $\sigma(expr)$  is the result of evaluating expr in the store  $\sigma$ , and the cases for M are evaluated in the order listed.

The declaration for a global variable x protected by a lock m is thus written as

```

int x read both-mover if m == tid

write both-mover if m == tid

```

where **both-mover** is syntactic sugar for the effect **B**. (Similarly, we use **left-mover** for **L**, and so on.) In our examples, we abbreviate these identical read and write cases as follows.

```

int x both-mover if m == tid

```

# 7.3 Motivating Example, Revisited

Figure 7 expresses our motivating example from Figure 3 (right) in our Mover Logic Language. As mentioned earlier, an access to a thread-local variable r actually accesses a (global) variable  $r_{tid}$  that is reserved for use by thread tid. We use thread-local variables to encode function arguments and results. The fork statements are converted into parallel threads in the initial state  $\Sigma$ . We insert a yield at the start of each thread in  $\Sigma$  so that the initial state is well-formed under the non-preemptive semantics we introduce in our formal development.

Given this mover specification, mover logic successfully verifies this code. Figure 7 also demonstrates the reasoning carried out by mover logic. The left margin shows the effect of each action and groups those effects into reducible sequences. The add() function is a single reducible sequence, ensuring that we may treat it as atomic. The client() function consists of multiple reducible sequences separated by yields. We also show invariants demonstrating that client() is correct in comments at each program point.<sup>6</sup>

# 7.4 Additional Mover Specification Examples

Figure 3 (right) showed how mover specifications can capture the synchronization/commuting behavior of lock acquires, lock releases, and lock-protected variable accesses. Our mover

<sup>&</sup>lt;sup>6</sup> In this example, the rely assumption even(x) is sufficient for reasoning about yield points. In code where live ranges for local variables span yield points, we would add to the rely assumptions the requirement that one thread does not change another thread's local variables.

Initial State **\Sigma**

```

Counter Library

Client

int x

both-mover if m == tid

relies

even(x)

lock m

write right-mover

guarantees even(x)

if \odd(m) == 0 \&\& m == tid

requires

even(x)

write left-mover

ensures

even(x)

if \odd(m) == tid \&\& m == 0

client() {

// even(x)

atomic

В

non-mover

arg1_{tid} = 2;

requires

true

// even(x) && arg1<sub>tid</sub> == 2

ensures

x == \old(x) + arg1_{tid}

N

add<sub>tid</sub>();

ensures

result_{tid} == x

// even(x)

add() {

Υ

yield;

\langle d(m) == 0 \land m == tid \rangle_m

// even(x)

В

r_{tid} = x;

arg1_{tid} = 2;

r_{tid} = r_{tid} + arg1_{tid};

// even(x) && arg1<sub>tid</sub> == 2

N

add();

x = 1;

В

x = r_{tid};

// even(x) && even(result_{tid})

\langle m == 0 \rangle_m;

В

u_{tid} = result_{tid};

result_{tid} = r_{tid};

// even(x) && even(u_{tid})

В

if even(u<sub>tid</sub>) skip else wrong;

// even(x)

Υ

yield;

// even(x)

```

(yield; client()).(yield; client())  $\cdot$  [x := 0, m := 0]

**Figure 7** The example from Figure 3 (right) expressed in Mover Logic Language.

specifications are inspired by the Anchor verifier, which used mover specifications to capture many synchronization idioms [19, 1].<sup>7</sup>

To illustrate how mover specifications capture more complex synchronization disciplines, suppose the variable y is *write-protected* by a lock m. That is, lock m must be held for all writes to y but not necessarily held for reads. Consequently, y should be declared volatile if the code is run under a weak memory model. Writes to y are non-movers (due to concurrent reads); lock-protected reads are both-movers (because there can be no concurrent writes); and reads without holding the lock are non-movers (due to concurrent writes). Mover specifications capture this synchronization discipline concisely as follows, where the last clause applies only when m is not tid.

```

int y write non-mover if m == tid

read both-mover if m == tid

read non-mover

```

The FASTTRACK dynamic race detector [18, 56] uses a combination of lock-protected and write-protected disciplines to synchronize accesses to some array pointers. We illustrate that discipline for an array pointer vc: initially, a flag is false and the pointer vc is guarded by lock; when flag becomes true, vc becomes write-guarded by lock. The mover specification for this discipline is captured by the first four lines in the specification for vc:

Our syntax for mover specifications is a syntactic variant of the Anchor syntax. In essence, our specifications are sequential var\_clauses, whereas Anchor combines these clauses into a single binary decision tree using the syntax bool\_expr? mover\_spec: mover\_spec.

```

int vc[] both-mover if !flag && lock == tid

write non-mover if flag && lock == tid

read both-mover if flag && lock == tid

read non-mover if flag

[i] both-mover if !flag && lock == tid

[i] read both-mover if flag && (lock == tid || tid == i)

[i] write both-mover if flag && (lock == tid && tid == i)

```

This idiom enables the algorithm to avoid using a lock to protected all accesses to vc but still replace vc with a larger array when necessary. The last three lines capture the synchronization discipline for accessing the array entry vc[i], where we use the extended notation "[i]  $var\_clause$ " to describe the synchronization cases for actions that access vc[i]. That entry is also initially guarded by lock when flag is false; when flag becomes true, the entry vc[i] can only be written by thread i while holding lock, read by any thread while holding the lock, or read by thread i without holding the lock. These reads and writes are all both-movers. These rules prevent all conflicting reads and writes, and thus all accesses to vc[i] are both-movers under this synchronization discipline.

As a final example, consider a concurrent hashtable consisting of a table array and a locks array, which has length N. The entry table[i] is protected by locks[i % N]. The table reference itself may change when, for example, table is replaced with a larger array. To ensure such changes are done without interference, a write to table is permitted only when a thread holds *all* locks. In contrast, table can be read by a thread holding *any* lock. All such reads and writes are both-movers, as captured by the following mover specification:

```

Entry table[] write both-mover if \forall i \in [0, N). locks[i] == tid read both-mover if \exists i \in [0, N). locks[i] == tid both-mover if locks[i % N] == tid

```

As illustrated in the previous two examples from the Anchor verifier [19], mover specifications can naturally capture synchronization disciplines that vary with the current program state.

A final example comes from the common iterative parallel algorithm pattern in which a synchronization barrier is used to divide the computation into a series of phases. In the even phases, the main thread (with  $\mathtt{tid} = 0$ ) updates shared data structures, and in odd phases, worker threads concurrently read data from those structures, as specified below.

```

int z read both-mover if phase % 2 == 1

both-mover if phase % 2 == 0 && tid == 0

```

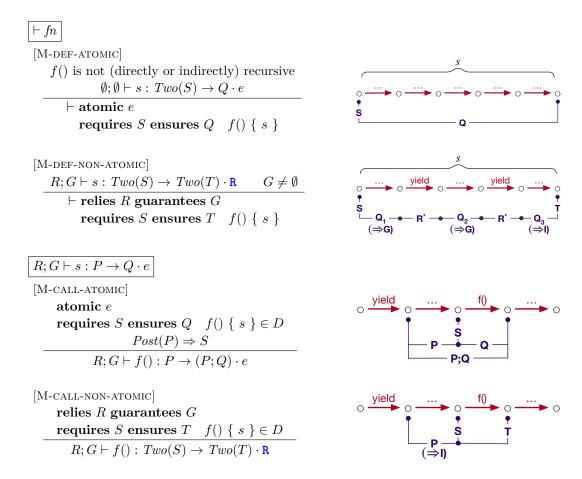

# 8 Mover Logic

In this section, we show the proof rules for how mover logic handles statements (Section 8.1); function definitions, calls, and specifications (Section 8.2–8.3); and run-time states (Section 8.4).

#### 8.1 Mover Logic

Mover logic is defined via the judgments in Figures 8 and 9. The main judgment

$$R: G \vdash s: P \rightarrow Q \cdot e$$

#### One-Store and Two-Store Predicates and Supporting Definitions

$$S,T\subseteq Tid\times Store\\R,G,P,Q,A\subseteq Tid\times Store\times Store\\Two(S)\stackrel{\mathrm{def}}{=} \{\ (t,\sigma,\sigma)\mid (t,\sigma)\in S\ \}\\Post(P)\stackrel{\mathrm{def}}{=} \{\ (t,\sigma)\mid (t,\_,\sigma)\in P\ \}\\I\stackrel{\mathrm{def}}{=} \{\ (t,\sigma,\sigma)\mid t\in Tid,\sigma\in Store\ \}\\Yield(P,R)\stackrel{\mathrm{def}}{=} \left\{(t,\sigma',\sigma')\mid (t,\_,\sigma)\in P\ \mathrm{and}\\ (t,\sigma',\sigma')\in R^*\right\}$$

### Mover Logic Proof Rules

**Figure 8** Mover logic proof rules and supporting definitions.

verifies that, when starting from a store satisfying the precondition P, the statement s terminates only in stores satisfying the postcondition Q (i.e. partial correctness). In addition, the judgment uses the mover specification M to verify that s consists of reducible sequences separated by yields. At each yield point, the rely assumption  $R \subseteq Tid \times Store \times Store$  is used to model potential interference from other threads. Conversely, the thread guarantee  $G \subseteq Tid \times Store \times Store$  summarizes the behavior of each reducible code sequence between two yield points in s. The effect e summarizes how s commutes with steps of other threads.

In the rules, the precondition P can refer to the value of variable  $\mathbf{x}$  in the initial store  $\sigma_0$  of the current reducible code sequence via the notation  $\cdot old(\mathbf{x})$ . Thus P is a two-store relation

20

#### **Function Specification Syntax**

$$fn\_spec ::=$$

atomic  $e$  requires  $S$  ensures  $Q$  relies  $R$  guarantees  $G$  requires  $S$  ensures  $T$

#### **Proof Rules for Function Definitions and Calls**

#### Verification of States

**Figure 9** Mover logic proof rules for function definition, calls, and run-time states.

$P \subseteq Tid \times Store \times Store$  relating that initial store  $\sigma_0$  to the pre-store  $\sigma$  for the execution of s. We show that requirement visually in the following trace, where  $(tid, \sigma_0, \sigma) \in P$ .

The two-store postcondition  $Q \subseteq Tid \times Store \times Store$  relates  $\sigma_0$  to the post-store  $\sigma'$  of s.

Many of the mover logic rules are extensions of Hoare logic incorporating reduction effects. For example, the rule [M-SEQ] states that a sequential composition  $(s_1; s_2)$  commutes as  $e_1; e_2$ , the sequential composition of the effects of its sub-statements, and that the precondition and postcondition are related as follows:

The rule [M-skip] indicates that skip has no effect, so its precondition and postcondition are identical. The rule [M-wrong] verifies that wrong is never executed via the unsatisfiable precondition  $\emptyset$ . That is, this rule rejects any program that may execute wrong from any state. The rule [M-action] computes the effect of action A from states  $\sigma$  satisfying the current precondition P. That rule uses the function to compute this effect:

$$M(A, P) \stackrel{\text{def}}{=} \bigsqcup_{(t, ,\sigma) \in P} M(A, t, \sigma)$$

(Note that we are overloading M here.) The postcondition of A is then the precondition P sequentially composed with the action A, i.e. P; A. A key technical requirement of the reduction theorem is that once an atomic block  $R^*[N]L^*$  enters its post-commit (or left-mover part), then it must terminate. It cannot block or diverge [23]. Hence, we require that A is total if it is a left-mover. We place similar restrictions on loops.

The rule [M-IF] requires both the true case  $(A_1; s_1)$  and the false case  $(A_2; s_2)$  to have the same post-condition Q. The effect e is the maximal effect of executing either  $A_1$  followed by  $s_1$  or  $A_2$  followed by  $s_2$ . The rule [M-while] for while  $A_1 \diamond A_2$  s checks that a successful test followed by the body preserves precondition P, which functions as a loop invariant. The postcondition of the loop is the postcondition of  $A_2$  given the precondition P. The effect of a loop is the iterative closure of the effect of one iteration sequentially composed with the effect of the loop-terminating test  $A_2$ .

Consider the loop in  $spin_lock()$  in Figure 5. The test !cas(1,0,tid) is the conditional action  $I \diamond \langle \texttt{vold}(1) = 0 \land 1 = \texttt{tid} \rangle_1$  and the loop body is skip. Since P; I = P, rule [M-SKIP] concludes that  $R; G \vdash \texttt{skip} : P \to P \cdot \texttt{B}$ . Further, M(I,P) = B, because that action accesses no global variables, and the specification for 1 indicates that  $M(\langle \texttt{vold}(1) = 0 \land 1 = \texttt{tid} \rangle_1, P) = \texttt{R}$ . Thus,  $e = (\texttt{B}; \texttt{B})^*; \texttt{R} = \texttt{R}$ . Also, the postcondition  $P; A_2$  for the loop simplifies to the expected

To motivate this requirement consider the program (x = 1; while (true) skip; yield) || (assert x != 1). This program can go wrong because the first thread writes 1 to x. However, the reducible block containing that write never terminates after performing that write, and that write is not included in the thread guarantee G. Thus, we require that once a reducible block commits, it must terminate.

P[1 := tid]. To ensure the left-mover termination requirement, rule [M-WHILE] requires that  $e \not\sqsubseteq \mathbf{L}$ . That is, the post-commit part of a reducible sequence cannot contain loops.

The rule [M-YIELD] for yield first checks that the thread guarantee G includes all possible behaviors P of the reducible sequence preceding the yield via the antecedent  $P \Rightarrow G$ . The reducible sequence following the yield starts with postcondition Q = Yield(P, R) which incorporates repeated thread interference from other threads via the iterated rely assumption  $R^*$  and then resets each old(x) value to be the current value of x at the start of the new reducible sequence.

The rule [M-conseq] extends the consequence rule of RG logic to reduction effects.

#### 8.2 **Atomic Functions**

Mover logic supports both atomic and non-atomic functions. An atomic function is one whose code body is reducible (i.e., no yield statements) and has the following form:

```

atomic e

requires S ensures Q - f() \{ s \}

```

(We elide e in the surface syntax when it is N, as in Figure 3 (right)). The precondition  $S \subseteq Tid \times Store$  describes valid initial stores for the function call and must be established by the caller. The post condition  $Q \subseteq Tid \times Store \times Store$  describes possible final stores, and it may refer to values of variables on function entry using the  $\old(x)$  notation. Since s is atomic and yield-free, we elide the rely and guarantee components from atomic function specifications. We require atomic functions to be non-recursive to facilitate the "left-mover terminates" requirement mentioned above.

To ensure that the function body s conforms to the function's specification, rule [M-DEF-ATOMIC] in Figure 9 first converts S into the two-store precondition Two(S) (in which  $\operatorname{old}(x) = x$  for all variables x) and then verifies the function body s with respect to that precondition. We use the guarantee  $\emptyset$  to enforce that s is indeed yield-free. (Rule [M-YIELD] will always fail if G is  $\emptyset$ , provided that the yield is actually reachable, i.e. if  $P \neq \emptyset$ ).

The rule [M-CALL-ATOMIC] for a corresponding call to f() retrieves the above specification from the declaration table D and then ensures that the precondition P at the call site implies the callee's precondition S. That rule uses Post(P) to first convert P into a one-state predicate. The postcondition (P;Q) combines the call precondition P with the two-store postcondition Q of the callee, as illustrated in the trace to the right of the rule.

#### 8.3 **Non-Atomic Functions**

Non-atomic function definitions have the following form:

```

requires R guarantees G

requires S ensures T - f() \{ s \}

```

We include thread rely R and guarantee G components in these function specifications since non-atomic function may include yield points where thread interference may occur. For simplicity, we require that non-atomic function calls and returns happen at the start of a reducible sequence. Consequently, the precondition  $S \subseteq Tid \times Store$  and postcondition  $T \subseteq Tid \times Store$  are both one-store predicates since there is no need to summarize the preceding reducible sequence.

The rule [M-DEF-NON-ATOMIC] checks that the function body s runs from the precondition Two(S), possibly via multiple reducible sequences separated by yields, to terminate after a final yield s in a store satisfying T. Those requirements are enforced by using Two(T) as the postcondition for s. Further, the body s should end in a yield, which from the definition of  $e_1$ ;  $e_2$  entails that the effect of s is at most R. At a call site, the rule [M-CALL-NON-ATOMIC] requires that the current reducible sequence is trivial/empty and meets the function's one-store precondition S by requiring the precondition Two(S) prior to the call. The rule also converts the function's one-store postcondition T to the two-store predicate Two(T).

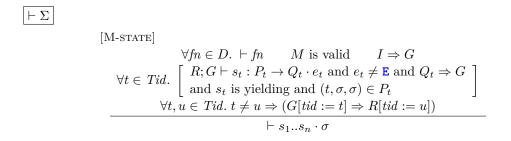

# 8.4 Verifying States

We now define the verification judgment  $\vdash \Sigma$  to verify program states  $\Sigma = s_1..s_n \cdot \sigma$ . The rule [M-STATE] for this judgment in Figure 9 ensures that:

- $\blacksquare$  each thread  $s_t$  verifies from a precondition  $P_t$  that includes the initial store  $\sigma$ ;

- $\blacksquare$  any pending behavior  $Q_t$  at thread termination is published to G;

- $\blacksquare$  the thread guarantee G is reflexive;

- the guarantee of each thread is contained in the rely assumption of every other thread;

- $\blacksquare$  each function definition in the global table D is verifiable; and

- that all threads start with a yield statement (to simplify the correctness proof).

A mover specification M makes claims about how steps of one thread commute with respect to steps of other threads, and mover logic needs to ensure that those claims are correct. Specifically, we define a mover specification to be valid if:

- 1. Right-moving actions can be moved later in a trace without changing the final store.

- 2. Left-moving actions can be moved earlier in a trace without changing the final store.

- 3. An action by one thread cannot change the effect of an action in another thread.

- **4.** An action by one thread cannot cause a left-moving action in another thread to block. We formalize these validity requirements as follows:

- ▶ **Definition 1** (Validity). M is valid if the following four conditions hold for all threads  $t \neq u$  and  $A_1, A_2, \sigma, \sigma'$ :

(1) if

$$M(A_1, t, \sigma) \sqsubseteq \mathbf{R}$$

and  $(t, \sigma, \sigma') \in A_1$  and  $M(A_2, u, \sigma') \sqsubseteq \mathbf{N}$  and  $(u, \sigma', \sigma'') \in A_2$ , then there exists  $\sigma'''$  such that  $(u, \sigma, \sigma''') \in A_2$  and  $(t, \sigma''', \sigma'') \in A_1$ .

$$\sigma \xrightarrow{\mathbf{R}} \sigma' \xrightarrow{\sim_2} \sigma''$$

$$\Rightarrow \sigma \xrightarrow{\wedge_2} \sigma'' \xrightarrow{\wedge_1} \sigma'$$

(2) if

$$M(A_1, t, \sigma) \sqsubseteq \mathbb{N}$$

and  $(t, \sigma, \sigma') \in A_1$  and  $M(A_2, u, \sigma') \sqsubseteq \mathbb{L}$  and  $(u, \sigma', \sigma'') \in A_2$ , then there exists  $\sigma'''$  such that  $(u, \sigma, \sigma''') \in A_2$  and  $(t, \sigma''', \sigma'') \in A_1$ .

$$\sigma \xrightarrow{A_1} \sigma' \xrightarrow{A_2} \sigma''$$

$$\Rightarrow \sigma \xrightarrow{A_1} \sigma' \xrightarrow{A_2} \sigma'$$

$$\sigma \xrightarrow{A_2} \sigma'' \xrightarrow{A_1} \sigma'$$

(3) if

$$M(A_1, t, \sigma) \subseteq \mathbb{N}$$

and  $(t, \sigma, \sigma') \in A_1$  and  $M(A_2, u, \sigma) = e$  for some  $e$ , then  $M(A_2, u, \sigma') = e$ .

(4) if

$$M(A_1, t, \sigma) \sqsubseteq \mathbb{N}$$

and  $(t, \sigma, \sigma') \in A_1$  and  $M(A_2, u, \sigma) \sqsubseteq \mathbb{L}$  and  $(u, \sigma, \sigma'') \in A_2$ , then there exists  $\sigma'''$  such that  $(u, \sigma', \sigma''') \in A_2$  and  $(t, \sigma'', \sigma''') \in A_1$ .

$$\begin{array}{ccc}

\sigma \xrightarrow{A_2} & \sigma'' \\

\bullet & \bullet \\

\sigma \xrightarrow{A_1} & \sigma'

\end{array}

\Rightarrow

\begin{array}{cccc}

\sigma \xrightarrow{A_2} & \sigma'' \xrightarrow{A_1} & \sigma''' \\

\bullet & \bullet & \bullet \\

\sigma \xrightarrow{A_1} & \sigma' \xrightarrow{A_2} & \sigma'''

\end{array}$$

# 8.5 Correctness

The central correctness theorem for mover logic is that verified programs do not go wrong by, for example, failing an assertion.

#### ▶ **Theorem 2** (Soundness). *If* $\vdash \Sigma$ *then* $\Sigma$ *does not go wrong.*

The proof appears in full in the Appendix. The basic structure is as follows.

- 1. We first develop an instrumented semantics that enforces the mover specification M and also that each thread consists of reducible sequences separated by yields.

- 2. In addition to the usual preemptive scheduler, we also develop a non-preemptive scheduler for the instrumented semantics that context switches only at yields.

- 3. We show that the instrumented semantics under the preemptive scheduler behaves the same as the standard semantics except that it may go wrong more often.

- **4.** We use a reduction theorem to show that programs exhibit the same behavior under the preemptive and non-preemptive instrumented semantics.

- **5.** Finally, we use a preservation argument [57] to show that verified programs do not go wrong under the non-preemptive instrumented semantics.

- **6.** The steps above then imply that verified programs do not go wrong under the preemptive standard semantics.

#### 9 Related Work

# Modular Reasoning

Concurrent software verification introduces a number of scalability challenges that require a synthesis of various notions of modularity or abstraction to address. For example, procedure-modular reasoning tackles large code bases by verifying each procedure with respect to a specification of other procedures in the system. Rely-guarantee logic [32] augments procedure-modular reasoning with a notion of thread-modular reasoning that accommodates multiple threads by verifying each thread with respect to a specification of other threads in the system. As demonstrated in Section 2, systems like RG logic that support procedure-modular and thread-modular reasoning have great potential, but they are limited by entanglement between library and client specifications.

To address that limitation, mover logic augments procedure-modular and thread-modular reasoning with Lipton's theory of reduction [40]. This complementary form of "interleaving" modularity limits the number of interleavings that must be considered and enables more precise procedure specifications for atomic functions.

In other work, separation logic combines procedure-modular reasoning with a notion of heap-modular reasoning [46, 48], which enables verification of sub-goals while ignoring irrelevant heap objects. Separation logic has been the foundation for a variety of verification tools [3, 31, 43]. Concurrent separation logics including, for example [52, 45, 5, 51], extend those ideas to a concurrent setting. While initially focused on noninterference via disjoint access and read-only sharing, later work [14, 13] supports more tightly-coupled threads.

Much of the work on concurrent separation logic focuses on resources (e.g., heap locations) and on ensuring threads access disjoint resources (hence ensuring noninterference). In contrast, mover logic focuses on commuting actions.

Concurrent separation logic and mover logic also differ in where thread interference specifications are placed. Concurrent separation logic conveniently merges interference (or resource footprint) specifications into each method's precondition, thus enabling the logic to

capture sophisticated resource usage idioms in a concise and elegant manner. Deny-guarantee reasoning [14] extends concurrent separation logic to focus more on actions rather than resources. In particular, a method's precondition can include an "action map" specifying what actions the method (and its concurrent threads) may perform. This action map is analogous to our mover specifications. Several projects employ permissions or ownership, similar to separation logic, to reason about which memory locations are available to different threads. These include Viper [42] and VerCors [4]. These systems do not support reduction.

An important topic of for future study is how to extend mover logic with a notion of heap modularity, perhaps similar to the core ideas of concurrent separation logic or dynamic frames [2, 50, 34]. This body of work may also provide insight into how to develop a compositional semantics based on mover logic.

# **Reduction-based Techniques**

QED [15] is a program calculus and verification procedure for concurrent programs. It utilizes iterative reduction and abstraction refinement to increase the size of the blocks that can be considered serializable regions (at the abstract level). That approach has been shown to be quite successful for verifying complex concurrent code and has inspired a number of subsequent verification tools described below. Mover logic is a complementary approach in that the combination of RG reasoning and reduction enables direct verification of code with yield points, without the need to create layers of abstractions. As part of that, mover logic supports specifying and reasoning about functions that are not atomic, which is not supported in QED. We also note that QED checks the commutativity properties of an action via a pairwise check with all other actions in the code, whereas mover logic uses the mover specification validity check for that purpose.

Several more recent verification tools utilize the same approach of writing a series of programs related by refinement, abstraction, and reduction. These include the CIVL verifier [29, 37, 39, 35, 36, 38] and the Armada verifier [41]. They are capable of handling sophisticated concurrent code, but do require the programmer to write and maintain multiple versions of the source code. The correctness arguments for these tools have typically been based on monolithic proofs.

Calvin-R [24] developed a number of early ideas related to reduction and thread-modular reasoning. The Anchor verifier [19] builds on ideas behind Calvin-R and CIVL to create a verification technique supporting an executable, object-oriented target language, a variety of synchronization primitives, and a new notation for specifying the interference between threads that is the foundation for our mover specifications. While effective at some verification tasks, Anchor's correctness arguments are also challenging to understand and build upon. Further, Anchor is inherently limited to small programs because it inlines nested calls during verification, with no mechanism for procedure-modular reasoning. Mover logic may provide a useful foundation for a procedure-modular extension of Anchor.

The difficulty in assessing the strengths and weaknesses of the tools mentioned above without a robust underlying logic capturing what they do inspired this work. Mover logic may provide such a foundation, detached from any particular full-scale implementation, that it is accessible, general, and extensible. We hope implementations based on mover logic will follow, as the logic clarifies exactly what conditions must be met in reduction-based verifiers that attempt to integrate modular reasoning in the presence of interference.

# **Coq-based Techniques**

Complementary approaches develop proof frameworks for verifying concurrent programs in Coq [12]. For example, CCAL [27] provides a compositional semantic model for composing and verifying the correctness of multithreaded components. CCAL focuses on only rely-guarantee reasoning [32] and not reduction. CSpec [7] is a Coq library for verifying concurrent systems modeled in Coq [12] using movers and reduction. While highly expressive, particularly because additional proof techniques can be added as additional Coq code, users must write significant Coq code for both specifications and proofs to use such a system. We have focused on a logic more amenable to fully automatic reasoning. Iris [33] uses higher-order separation logic to verify correctness of higher-order imperative programs.

# Model Checking

An orthogonal approach to software verification utilizes explicit state, exhaustive model checking. Such approaches have lower programmer overhead than other techniques, but they are non-modular [16, 10, 11]. Specialized techniques, including reduction [28] and partial-order methods [26, 25, 47], have been used to limit state-space explosion while checking concurrent programs. A variety of concurrent software model checkers [8, 58, 44] have demonstrated the potential of these approaches in constrained settings.

# 10 Summary

Over the last two decades, several promising multithreaded program verifiers have leveraged reduction to verify sophisticated concurrent code including non-blocking algorithms, dynamic data race detectors, and garbage collectors by leveraging precise, reusable specifications for atomic functions. The reasoning used by these verifiers, including the notion of which programs are verifiable, and why the verification process is sound, is unfortunately rather complex. In contrast, Hoare logic [30] provides an accessible foundation for sequential verifiers, and RG logic [32] provides a similar foundation for some multithreaded verifiers.

In developing mover logic, we aim to facilitate future research on reduction-based verification. Mover logic provides a declarative and formal explanation of reduction-based verification, making it easier to understand which programs are verifiable, or not, and why; which functions can be specified as atomic; what atomic and non-atomic function specifications mean; which code blocks are reducible; where yield annotations are required, etc. The correctness proof for a reduction-based verifier need only show that the verifier follows the rules of mover logic, a significant simplification over existing proof techniques.

We hope that mover logic inspires the development of more expressive reduction-based logics and verification tools, potentially supporting features such as objects, data abstraction, dynamic allocation, dynamic thread creation, and precise frame conditions [2, 50, 34].

#### References -

- 1 The Anchor verifier. Accessed: March 30, 2024. URL: http://www.anchor-verifier.com/.

- 2 Anindya Banerjee, David A. Naumann, and Stan Rosenberg. Regional logic for local reasoning about global invariants. In *ECOOP*, volume 5142 of *Lecture Notes in Computer Science*, pages 387–411. Springer, 2008.

- 3 Josh Berdine, Cristiano Calcagno, and Peter W. O'Hearn. Smallfoot: Modular automatic assertion checking with separation logic. In *FMCO*, volume 4111 of *Lecture Notes in Computer Science*, pages 115–137. Springer, 2005.

- 4 Stefan Blom, Saeed Darabi, Marieke Huisman, and Wytse Oortwijn. The vercors tool set: Verification of parallel and concurrent software. In *IFM*, volume 10510 of *Lecture Notes in Computer Science*, pages 102–110. Springer, 2017.

- 5 Stephen Brookes. A semantics for concurrent separation logic. *Theor. Comput. Sci.*, 375(1-3):227–270, 2007.

- 6 Pavol Cerný, Edmund M. Clarke, Thomas A. Henzinger, Arjun Radhakrishna, Leonid Ryzhyk, Roopsha Samanta, and Thorsten Tarrach. From non-preemptive to preemptive scheduling using synchronization synthesis. *Formal Methods Syst. Des.*, 50(2-3):97–139, 2017.

- 7 Tej Chajed, M. Frans Kaashoek, Butler W. Lampson, and Nickolai Zeldovich. Verifying concurrent software using movers in CSPEC. In OSDI, pages 306–322. USENIX Association, 2018.

- 8 A. T. Chamillard and Lori A. Clarke. Improving the accuracy of petri net-based analysis of concurrent programs. In *ISSTA*, pages 24–38. ACM, 1996.

- 9 Qichang Chen, Liqiang Wang, Zijiang Yang, and Scott D. Stoller. HAVE: detecting atomicity violations via integrated dynamic and static analysis. In FASE, volume 5503 of Lecture Notes in Computer Science, pages 425–439. Springer, 2009.

- 10 Edmund M. Clarke and E. Allen Emerson. Design and synthesis of synchronization skeletons using branching-time temporal logic. In *Logic of Programs*, volume 131 of *Lecture Notes in Computer Science*, pages 52–71. Springer, 1981.

- Edmund M. Clarke, E. Allen Emerson, and A. Prasad Sistla. Automatic verification of finite-state concurrent systems using temporal logic specifications. ACM Trans. Program. Lang. Syst., 8(2):244–263, 1986.

- 12 The Coq proof assistant, 2023. URL: https://coq.inria.fr/.

- 13 Thomas Dinsdale-Young, Lars Birkedal, Philippa Gardner, Matthew J. Parkinson, and Hongseok Yang. Views: compositional reasoning for concurrent programs. In *POPL*, pages 287–300. ACM, 2013.

- Mike Dodds, Xinyu Feng, Matthew J. Parkinson, and Viktor Vafeiadis. Deny-guarantee reasoning. In ESOP, volume 5502 of Lecture Notes in Computer Science, pages 363–377. Springer, 2009.

- Tayfun Elmas. QED: a proof system based on reduction and abstraction for the static verification of concurrent software. In *ICSE* (2), pages 507–508. ACM, 2010.

- E. Allen Emerson and Edmund M. Clarke. Characterizing correctness properties of parallel programs using fixpoints. In *ICALP*, volume 85 of *Lecture Notes in Computer Science*, pages 169–181. Springer, 1980.

- 17 Cormac Flanagan and Stephen N. Freund. Atomizer: a dynamic atomicity checker for multithreaded programs. In POPL, pages 256–267. ACM, 2004.

- 18 Cormac Flanagan and Stephen N. Freund. Fasttrack: efficient and precise dynamic race detection. Commun. ACM, 53(11):93-101, 2010.

- 19 Cormac Flanagan and Stephen N. Freund. The Anchor verifier for blocking and non-blocking concurrent software. *Proc. ACM Program. Lang.*, 4(OOPSLA):156:1–156:29, 2020.

- 20 Cormac Flanagan, Stephen N. Freund, Marina Lifshin, and Shaz Qadeer. Types for atomicity: Static checking and inference for java. ACM Trans. Program. Lang. Syst., 30(4):20:1–20:53, 2008.

- 21 Cormac Flanagan, Stephen N. Freund, and Shaz Qadeer. Exploiting purity for atomicity. In ISSTA, pages 221–231. ACM, 2004.

- 22 Cormac Flanagan and Shaz Qadeer. A type and effect system for atomicity. In *PLDI*, pages 338–349. ACM, 2003.

- 23 Cormac Flanagan and Shaz Qadeer. Types for atomicity. In TLDI, pages 1–12. ACM, 2003.

- 24 Stephen N. Freund and Shaz Qadeer. Checking concise specifications for multithreaded software. *J. Object Technol.*, 3(6):81–101, 2004.

- 25 Patrice Godefroid. Model checking for programming languages using verisoft. In POPL, pages 174–186. ACM Press, 1997.

- 26 Patrice Godefroid and Pierre Wolper. A partial approach to model checking. In *LICS*, pages 406–415. IEEE Computer Society, 1991.

- 27 Ronghui Gu, Zhong Shao, Jieung Kim, Xiongnan (Newman) Wu, Jérémie Koenig, Vilhelm Sjöberg, Hao Chen, David Costanzo, and Tahina Ramananandro. Certified concurrent abstraction layers. In *PLDI*, pages 646–661. ACM, 2018.

- 28 John Hatcliff, Robby, and Matthew B. Dwyer. Verifying atomicity specifications for concurrent object-oriented software using model-checking. In VMCAI, volume 2937 of Lecture Notes in Computer Science, pages 175–190. Springer, 2004.

- 29 Chris Hawblitzel, Erez Petrank, Shaz Qadeer, and Serdar Tasiran. Automated and modular refinement reasoning for concurrent programs. In CAV (2), volume 9207 of Lecture Notes in Computer Science, pages 449–465. Springer, 2015.

- 30 C. A. R. Hoare. An axiomatic basis for computer programming. Commun. ACM, 12(10):576–580, 1969.

- 31 Bart Jacobs, Jan Smans, Pieter Philippaerts, Frédéric Vogels, Willem Penninckx, and Frank Piessens. Verifast: A powerful, sound, predictable, fast verifier for C and java. In NASA Formal Methods, volume 6617 of Lecture Notes in Computer Science, pages 41–55. Springer, 2011.

- 32 Cliff B. Jones. Tentative steps toward a development method for interfering programs. *ACM Trans. Program. Lang. Syst.*, 5(4):596–619, 1983.

- Ralf Jung, Robbert Krebbers, Jacques-Henri Jourdan, Ales Bizjak, Lars Birkedal, and Derek Dreyer. Iris from the ground up: A modular foundation for higher-order concurrent separation logic. J. Funct. Program., 28:e20, 2018.

- 34 Ioannis T. Kassios. Dynamic frames: Support for framing, dependencies and sharing without restrictions. In FM, volume 4085 of Lecture Notes in Computer Science, pages 268–283. Springer, 2006.

- 35 Bernhard Kragl, Constantin Enea, Thomas A. Henzinger, Suha Orhun Mutluergil, and Shaz Qadeer. Inductive sequentialization of asynchronous programs. In *PLDI*, pages 227–242. ACM, 2020.

- 36 Bernhard Kragl and Shaz Qadeer. Layered concurrent programs. In CAV (1), volume 10981 of Lecture Notes in Computer Science, pages 79–102. Springer, 2018.

- 37 Bernhard Kragl and Shaz Qadeer. The civl verifier. In FMCAD, pages 143–152. IEEE, 2021.