# A Transverse-Read-assisted Valid-Bit Collection to Accelerate Stochastic Computing MAC for Energy-Efficient in-RTM DNNs

Jihe Wang, Zhiying Zhang, Xingwu Dong, and Danghui Wang

Abstract—It looks very attractive to coordinate racetrack-memory(RM) and stochastic-computing (SC) jointly to build an ultra-low power neuron-architecture. However, the above combination has always been questioned in a fatal weakness that the narrow bit-view of the RM-MTJ structure, a.k.a. shift-and-access pattern, cannot physically match the great throughput of direct-stored stochastic sequences. Fortunately, a recently developed Transverse-Read(TR) provides a wider segment-view to RM via detecting the resistance of domain-walls between a couple of MTJs on single nanowire, therefore RM can be enhanced with a faster access to the sequences without any substantial domain-shift. To utilize TR for a power-efficient SC-DNNs, in this work, we propose a segment-based compression to leverage one-cycle TR to only read those kernel segments of stochastic sequences, meanwhile, remove a large number of redundant segments for ultra-high storage density. In decompression stage, the low-discrepancy stochastic sequences can be quickly reassembled by a select-and-output loop using kernel segments rather than slowly regenerated by costly SNGs. Since TR can provide an ideal in-memory acceleration in one-counting, counter-free SC-MACs are designed and deployed near RMs to form a power-efficient neuron-architecture, in which, the binary results of TR are activated straightforward without sluggish APCs. The results show that under the TR aided RM model, the power efficiency, speed, and stochastic accuracy of Seed-based Fast Stochastic Computing significantly enhance the performance of DNNs. The speed of computation is 2.88× faster in Lenet-5 and 4.40× faster in VGG-19 compared to the CORUSCANT model. The integration of TR with RTM is deployed near the memory to create a power-efficient neuron architecture, eliminating the need for slow Accumulative Parallel Counters (APCs) and improving access speed to stochastic sequences.

Index Terms—Racetrack Memory, Stochastic computing, Transverse Read, DNN, High Parallelism

#### 1 Introduction

S TOCHASTIC computing (SC), as a lightweight computing method, reduces the area and energy consumption by gate-level operations [1], [2], [3]. However, current SC solutions are still far from practical by the expensive bitwise stochastic-to-binary conversion [4], [5], [6]. A recently developed racetrack memory (RTM) is able to provide both ultra-high storage density [7], [8] and a transverse-read (TR) mechanism [9], empowering a global view of sequences within memory so that the fast counting of valid-bits can be built to overcome the bit-wise conversion. Therefore, this work first proposes a TR-aided in-RTM processing architecture to accelerate SC-operations of DNNs [10], [11], [12], in which, the slow stochastic-to-binary conversions can be totally removed.

DNNs deployed in traditional in-memory processing architectures face energy efficiency issues at both the storage and computing sides: 1) The refresh operation of DRAM causes high static power in memory; 2) The MAC units processing DNNs needs large area and energy consumption in limited resources environment. Recently, combining SC and RTM to rebuild above in-RTM processing architecture becomes a new solution to low energy efficiency [13]. This

Jihe Wang, Zhiying Zhang, Xingwu Dong and Danghui Wang are with the School of Computer Science, Northwestern Polytechnical University and Engineering Research Center of Embedded System Integration, Ministry of Education, Xi'an, Shaanxi 710072, China. E-mail: wangjihe@nwpu.edu.cn new architecture uses non-volatile memory with near-zero static power consumption on the memory side, and SCs with gate-level operations that can drastically reduce the overhead of on-chip logic. However, in this high energy efficient architecture, accumulative parallel counter (APC) becomes the bottleneck of energy and latency. Because in digital system, APCs converse stochastic sequences to binary numbers (BNs) need by counting the "1" in sequences bit-by-bit between two DNN layers , seriously slowing the computing speed. And it is also hard to balance the energy and latency consumption causing by bit-wise APCs one counting.

Recently, a new developed analog system data access mechanism named TR was proposed to counting the number of "1" in multiple domains by measuring the the resistance of these domains. This new data access mechanism provides SC with a global view that can be used to quickly count the number of "1"s in the stochastic sequences. For example, a 256-bit long stochastic sequences needs a 9layer tree adder to finish the conversion with 255 additions with energy consumption and much more latency. But if the theoretical transverse-read distance (TRD) is 32, there will be 8 counting results which need a 4-layer tree adder to finish the conversion with 7 additions, reducing adder resource by 93%. However, to use the TR mechanism, data must be stored on the RTM, which leads to two questions impairing architectural performance: 1) surge in the storage of SN, e.g., a 8-bit binary number is conversed to a 256bit long stochastic sequence; 2) insufficient concurrency by RTM linear data accesses, because the shift to access pattern of RTM with port is the bottleneck of throughput. Therefore, to build the SC+RTM architecture breaking the bottleneck of APCs needs to enhance the representation efficiency of stochastic sequences, at the same time rearrange Data with multi-Ports to release the bottleneck of throughput.

In this work, we propose a TR-assisted in-RTM processing architecture to implement stochastic computing in RTM with TR mechanism replacing the APCs. To reduce the storage of SN, we utilize the pseudo-fractal structure of SC stochastic number (SN) coding to compress the long SN by extracting the repetitive part to store as one seed to reduce the area consumption of storage and multiplication operations. Based on above PFC, we leverage the cost-effectively and directly store SN to re-built simpler multiplication logic in a simpler way and remove the redundant operations of traditional SC using shorter pseudo-fractal compressed SN which can be computed directly. After multiplication computing, we stack the result sequences to store them with multiple ports in multiple nanowires of RTM to realize high concurrency of RTM data access. Finally We leverage TR to fast count the number "1"s to get the multiplication binary result.

The results show that under the TR-assisted LD-SC architecture, which utilizes SLC for one operand and controls the output into RTM with another, there is a marked improvement in energy efficiency and computing speed suitable for DNNs computation. Specifically, our architecture demonstrates a 1.26× to 1.42× reduction in energy consumption and achieves a 2.88× to 4.40× increase in computational speed compared to other PIM architectures, while also maintaining high stochastic accuracy.

In summary, our main contributions and insights are:

- We design a new compression method named pseudofractal compression (PFC) to compress the long SN to approximate binary number length.

- We build a in-RTM fast compute architecture computing with shorter PFC SN and utilize TR to access wider view of data without sluggish APCs.

- We utilize the proposed architecture to realize simpler and faster vectors dot-product operation in DNN by counting the "1" of dot-product rather than "1" of each multiplication.

#### 2 Background and Motivation

# 2.1 Low Representation Efficiency of LD-SC

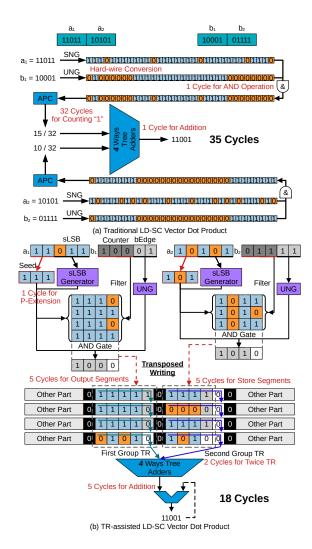

Different with tradition SC, Low discrepancy stochastic computing (LD-SC) has more powerful fault tolerance capability which is benefited by its coding method. In LD-SC multiplication computing, the binary numbers need to be conversed by stochastic number generator (SNG) and unary number generator (UNG) to two kinds of stochastic sequences which are stochastic number (SN) and unary number (UN). After conversion, the long SN and UN execute AND operation to get the result sequence which be sent into APC to converse into binary result showing in Fig. 1. However, SC requires more time than binary multiplication to obtain the final binary result, the main reason being that the representation of stochastic sequences

Fig. 1. LD-SC Multiplication Process

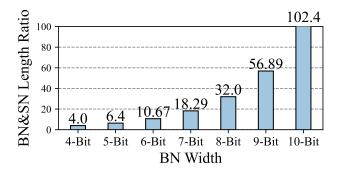

Fig. 2. BN & SN Length Ratio

is extremely inefficient which leads that a significant amount of time is used to realize the conversion from the stochastic domain to the binary domain (S2B). Figure 2 illustrates the ratio of the binary number representation efficiency and the corresponding SN representation efficiency, and it can be seen that as the length of the binary number increases the efficiency of the corresponding SN representation is decreasing. The low representation efficiency of SC coding leads to two problems: 1) the storage of longer stochastic sequences puts a lot of storage pressure, and 2) the S2B conversion of counting "1" bit-wise via APC takes a long time to complete.

#### 2.1.1 Surge in the Storage of SN

During the SC process, the binary number undergoes a number field conversion (B2S) from the binary domain to the random domain, and then the long SN and UN are fed into AND operation. After B2S, the SNs and UNs waiting for the AND operation are stored temporarily in memory, so the longer SNs and UNs can greatly increase the storage pressure of the PIM. Upon comparison, it was found that the space overhead of storing a 256-bit SN can store its corresponding 32 8-bit binary numbers,, which is the data required for 16 multiplications. The reason for this is the low representation efficiency of SC coding, which makes stochastic sequences require an exponential amount of storage space for binary numbers. Meanwhile, in RTM's shift to access pattern, a 256-bit long SN requires 959 ns to complete the read and 1787 ns to complete the write, but the corresponding 8-bit binary number only requires 28 nsto complete the read and 54 ns to complete the write.

#### 2.1.2 Expensive S2B by APC

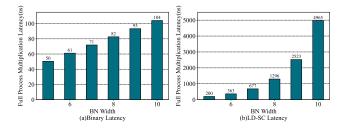

The multiplication of SC is divided into three steps, which are B2S, with gate logic, and S2B, which B2S is now available in a variety of fast conversions such as hardwired. The operation that occupies most of the delay in SC multiplication is S2B, because APC needs to perform single bit access accumulation of the result sequence length times to get the binary result. Fig. 3 compares the computational latency of a single multiplication with different bit-width

Fig. 3. Multiplication Latency Comparison

for binary multiplication and SC in PIM architecture based RTM. It can be clearly seen that the binary multiplication has lower latency, while the computational latency of SC shows a multiplicative increase with the bit width. What's more, More than 90% of this latency originates from the S2B conversion, i.e., the latency of APC bit-wise counting "1"s. Therefore to realize the architecture, it is necessary to accelerate the S2B conversion with a new access method.

#### 2.2 Motivation

To solve the problem of low representation efficiency of SC coding, this work cuts across the two phenomena mentioned above. Compressing the complete and long stochastic sequences into short sequences, which can be directly used to execute SC without complete stochastic sequences. In this case, the short sequences can effectively release the pressure of storage and reduce the operations of accessing operand sequences. Also, this work no longer use the access pattern of bit-view in digital system, i.e., APCs, but choose a global view access pattern. Since each bit in existing digital systems can only represent binary information, using an analog system allows for multiple representations of information. Therefore, this work utilize the analog access method TR to globally count "1"s in the result sequences.

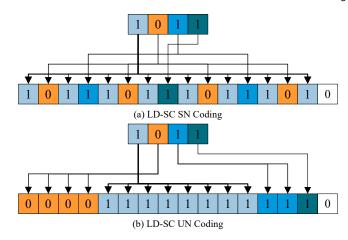

#### 2.2.1 Pseudo-Fractal Coding of LD-SC

LD-SC has better fault tolerance than traditional SC, also, LD-SC has fixed coding rules for faster B2S conversion. The SN is conversed by SNG to distribute "1"s with the same number of values evenly throughout the sequence, and the UN is conversed by UNG to put all "1"s at one end of the sequence. With this coding rule, the B2S conversion can be realized quickly by using hard-wire showing in Fig. 4. Peculiarly, after dividing the SN into two equal segments, each segment is identical except for the last digit. Continuing with the equalization of the 1/2 segments, each 1/4 segment is also identical except for the last bit. This coding structure is very similar to the fractal structure, and at the same time suggests that the SN can hopefully use this recurring subsegment to achieve compression. In this work, we named this coding structure a pseudo-fractal structure and describe the recurring key part as a seed for the equally divided segments. Pseudo-fractal compression (PFC) of a complete SN can be achieved as long as the last bit of each segment and the seed can be output in an orderly manner to form a complete segment.

# 2.2.2 Transverse Read on Racetrack Memory

The state-of-art RTM, AkA domain walls memory (DWM) has been found a new access pattern named transverse read

Fig. 4. B2S Hard-wire Conversion

(TR) which can access several bits data between a couple of bit lines at one time, because TR recieves the analog signals so TR process provides a global view of 3 to 7 bits.

The resistances originate from the change of anisotropic magnetoresistance (AMR) of the nanowire due to the domain walls, and the magnetic orientation of walls. The novelty of TR lies in capturing these two phenomena via tunneling magnetoresistance (TMR) to distinguish the states having different numbers of '1's.The TMR of such a nanowire across the read-head is similar to that of a multilevel cell based magnetic over a MLC-MTJ.In the research of domain walls resistance, the force on electrons and trajectory of electrons has been demaonstrated to support TR access pattern.

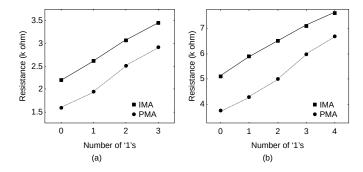

When implementing current between two bit lines, there is a transfer of momentum between the passing electrons and the local magnetic moment of the wall. This transfer process is adiabatic. Due to the conservation of energy, the electrons exert a force on the wall to move. However, due to the presence of local strains, inhomogeneities, and shape anisotropy there exists a pining force on the wall to impede the movement of electrons. The TR process starts by applying a read current between the access ports, and the resistance values for different bit patterns are calculated by measuring the voltage difference between the leftmost domain and the fixed layer of the read port. Fig.4 shows the average resistance values and standard deviations for all possible numbers of '1's in a domain walls nanowire having three and four domains. Fig.5 shows the TR results of three and four domains based on in-plane and perpendicular magnetic anisotropy (IMA/PMA) nanowires. The results of both kinds of nanowires are approximately linear so, it is feasible to use TR access the number of "1" stored in RTM.

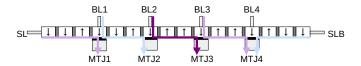

TR process accesses a global view of multiple bits by receiving analog signals at one time, the efficiency of TR is much higher than current combinational logic of digital signals. In the efficiency aspect, TR has more superiority over accumulative methods, but TR process can only be implemented in nanowires. And the parellel access has a problem which is that the adjacent segments can not execute TR operation at the same time because the adjacent segments has a public domain at the connected position showing in Fig.6. We can access the number of "1"s using TR

Fig. 5. Resistance of TR Access

from SL to MTJ1 and BL1 to MTJ2, but these tow segments cannot access at the same time because of the domain over MTJ1 which is public for two segments. The resistance from BL3 to MTJ4 can be access by TR with SL to MTJ1 because they have no public domains and no interact.

Fig. 6. Parallel TR Method

# 2.3 Designing Issues to Be Addressed

To solve the storage pressure problem, the SN must be compressed and the recurring seeds in it are extracted to be stored only once. In addition, an effective strategy to reduce the computation latency of LD-SC in RTM is to eliminate APC, a bit-wise access strategy, in favor of TR, an access method that can provide a global view. Also in order to build an in-RTM PIM architecture with LD-SC based on the solutions above, it is necessary to design computation units adapted to the computation intensive characteristics of DNNs. In this case, we need to address these designing issues:

- Design a compression method that uses approximate binary storage space and preserves the distribution information of "1"s in the original SN.

- Design a computation unit that can directly perform fast multiplication using compressed SN while eliminating a large number of unnecessary gate-level operations.

- Design an in-RTM PIM architecture and use the above computation unit to perform dot product computation directly, accelerating the computation of vectors or matrices and improving the throughput rate.

#### 3 PSEUDO-FRACTAL CODING

#### 3.1 Pseudo-Fractal Compression Potential Analysis

Fig 4(a) has illustrated the B2S conversion process of SN and shows that a n bits long BN is converted into a  $2^n$  bits long SN which increase the storage pressure. In computing, the longer SN needs more AND-gate logic units to finish LD-SC multiplication in once AND operation delay, but it is hard to implement large number of AND-gates in near-memory

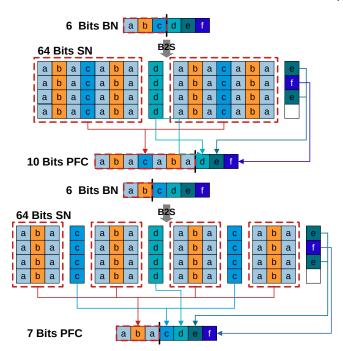

Fig. 7. Pseudo-Fractal Compression

situation. Therefore, the long SN needs to be compressed to cut down its length reducing the storage pressure and computing consumption. Fig. 7 shows the conversion of a 6-bit BN to a 64-bit SN and the area consumption has increased over 10 times. However, a closer look at the SN sequence reveals that if the 64-bit long SN is divided into 8 segments in upper Fig. 7, so, each segment is 8 bits long, it can be noticed that the first 7 bits in each segment is exactly the same. Therefore, when storing SNs involved in the computing, the first 7 bits in each segment that are all the same can be extracted for storage only once. As for the LSB in each segment, after extracting the LSBs and arranging them in order, it is just the conversion result from the last 3 bits in the 6-bit BN. The Pseudo-Fractal Compression combines the repetitive 7 bits in each segment and the binary 3-bit segment LSBs (sLSB) into a new hybrid 10 bits coding and the repetitive in each segment is named as a seed. The seed length can be adjusted showing in the lower part of Fig. 7, when the segments are 4 bits long means that the seed is 3 bits long and the seed is coming from the first 2 bits in 6-bit BN. At this time the sLSB becomes 4 bits, therefore, the pseudo-fractal coding is 7 bits long including a 3 bits long seed and 4 bits long sLSB and if the seed is shorter, the compression efficiency is higher.

#### 3.2 Compressible Proof

During SN conversion from binary domain to stochastic domain, the number of "1"s equals to the value of BN and these "1"s are uniformly distributed in whole SN. In conversion, the "1"s in different positions of BN represent different values, which makes the occurrence times and positions of these "1"s in the SN different. According to the rules of LD-SC conversion, we have summarized the mapping equation from n bits BN to  $2^n$  SN:

$$S_{2^{k+1}i+2^k-1} = B_k \tag{1}$$

the k  $(k \leq n)$  means the kth valid bit in BN and the i  $(i \leq 2^n/2^{k+1})$  represents the repeated times of the kth valid bit in stochastic number and i should be smaller than or equivalent to  $2^n/2^{k+1}$ . The current problem is that it is not clear if this formula achieves the correct conversion from BN to SN for all lengths of SN. Therefore, We propose a theorem: expression  $2^{k+1}i+2^k-1$  can represent all the non-negative integers less than  $2^n-1$ . Integrity Proof:

We use I to represent all non-negative integers and I can be divided into two parts which are even and odd, so I can be represented by 2i and 2i+1. The i can be still divided into two parts and then continue dividing until  $i_m$ . At this point the non-negative integer I is divided into two parts,those that can be represented by the formula  $2^{k+1}i+2^k-1$  and hose that cannot be represented by  $2^{m+1}i_m+2^{m+1}-1$ . Because the representation  $2^{m+1}i_m+2^{m+1}-1$  can only represents the number larger than  $2^{m+1}-1$ , when the n in Eqn(1) is less than m, all the numbers less than  $2^{m+1}-1$  can only represent by  $2^{k+1}i+2^k-1$ .

# **Uniqueness Demonstration:**

So far, we have demonstrated that the Eqn(1) can implement in all SN&BN conversion, but there is another question which is whether the valid bit of SN can match a single valid bit of BN. Assuming that a non-negative integer is N, and can be represented by two forms as  $2^{(m+1)}i+2^m-1$  and  $2^{(n+1)}i+2^n-1$ , that is to say:

$$2^{(m+1)}i_m + 2^m - 1 = 2^{(n+1)}i_n + 2^n - 1 \tag{2}$$

when m is not equal to n, the Eqn(2) never can be equal and The same goes for  $i_m$  and  $i_n$ . The equation only holds if m and n are equal and  $i_m$  and  $i_n$  are equal, even if equal to 0.

Overall, Eqn(1) is applicable to all the valid bits in SN and each valid bit of SN has only one representation form using Eqn(1).

# 3.3 Pseudo-Fractal Coding LD-SC

After the above proof, the source of the repetitive seeds in SN are exactly the same so it is possible to store them compressed. PFC compression as a hybrid coding method extracts the fractal-like seeds in SN and stores them only once and then stores the remaining parts in binary form. As shown in Fig. 7, the length of the seed is variable, the shorter the seed then represents the more times it repeats itself, which is more efficient when compressed, when the seed is 7 bits the compressed PF coding is 10 bits, whereas under 3 bit seed compression it is only 7 bits. Fig. 8 has shown the

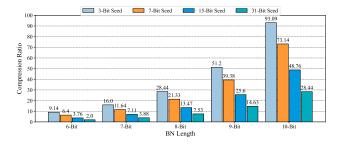

Fig. 8. Compression Ratio of Multiple Seeds

compression efficiency of PFC method with multiple seeds,

Fig. 9. PF Coding SN Multiplication

compared to the full SN, the compression efficiency of the PFC is at least twice as high, and it rises as the length of the BN increases.

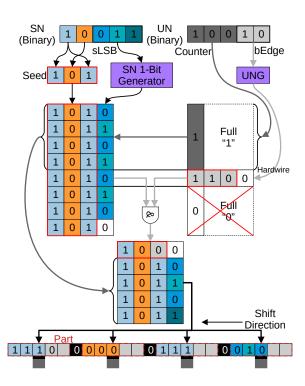

But these SNs compressed by PFC need to ensure that they can be used directly in LD-SC, otherwise re-expanding them into complete SNs will still increase the computing pressure. We use two 5-bit operands to analyze the process of LD-SC showing in Fig. 9. In Fig. 9, SN and UN are partitioned into 8 segments of 4 bits each and it can be clearly seen that UN has three different kinds of segment, which are full "1" segment, mixed segment and full "0" segment. In LD-SC, the SN segments AND with the full "1" segments output the SN segments themselves, and AND with the full "0" segments output full "0" segments. Only the mixed segment need to be sent into AND-gate logic unit with its corresponding SN segment.

In this case, traditional LD-SC can be simplified by remove AND operation of full "1" segments and full "0" segments. The new LD-SC assisted by TR, directly outputs the SN segments into RTM with the corresponding full "1" segments in UN and we named this computing process as output computation in this work. The mixed segment is sent into AND-gate logic units with its corresponding segment named mixed computation and this is the only AND operation stage in each LD-SC multiplication, after computing the result is streamed out with the results from output computation into RTM. But if the binary edge (bEdge) which is the origin of mixed segment is all "0", which means that this segment is full "0" segment and the computing can be finished prematurely because there is no mixed segment to be sent into AND-gate logic units. Therefore, in TR-assisted LD-SC, the multiplication only needs several segments of SN and the mixed segment in UN. Because sLSB is obeys SN conversion rules, so, the segments of SN is generated

by seed and the LSB from SN 1-bit generator. As for the generated number of SN segments, it depends on the value of counter in UN which controls the number of full "1" segments. In this example, the length of each segment is 4 bits, so, the value of counter is the former 3 bits of binary UN. The mixed segment can be converted by UNG from binary edge (bEdge) part which includes the last 2 bits in binary UN using hard-wire conversion method showing in Fig. 4. The streamed out segments are stored into 4 parts on nanowire, while the number of parts is the same as the length of the segment to ensure that in once store operation delay, a whole segment is finished storage and each part owns 5 domains between two black constant 0 domains. After all the segments are stored in the RTM, the TR operations access the parts to get the number of "1"s and send these interim results into the tree adder to get the final multiplication result.

# 4 TR Assisted Computation Frame

# 4.1 Vector MAC Operation using LD-SC

In tradition LD-SC dot product computing showing in Fig. 10(a), the operands from two vectors need to be converted into SNs and UNs by SNGs and UNGs, after that, the correlated SN and UN sequences execute AND operation to get the result sequence in place of multiplication. The APCs will count the number of "1"s in each result sequence to convert result sequences into binary number and this is the most time-consuming operation. Because APCs need to bit-wise access the results sequences and accumulate every bit in results sequences to realize the coversion. In the end, these binary results will be sent into tree adders to add the results from all the multiplications together to get the dot-product result using totally 35 cycles to finish the dot-product. This kind of tradition computing way divides once dot-product computing into multiplication and addition two steps, and multiplications provide interim results for additions, but TR-assisted LD-SC can computing a dot-product excuting multiplication and additions in the same time.

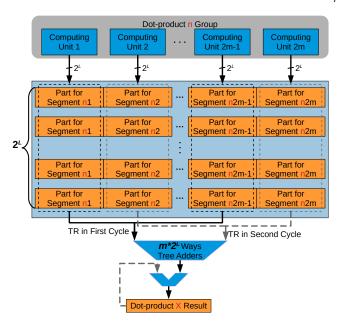

TR-assisted LD-SC utilize TR operations to fast "counting" the number of "1"s in result sequences, at the beginning, the operands from each multiplication are divided into 4 components which seed, sLSB, counter and bEdge. In this division, the seed can be seen as a part extension of BN at the first 2 bits and is converted into SN form. And then the quadruple performs output computation and mixed computation according to the computing way in Fig. 9 and streams out the segments into parts on nanowires. In our work, from the segment generation to output, the computing works in a pipelined way to accelerate comuting, when the last segment is outputting into parts, the last segment is generating. In dot-product computing, These segments will be transposed to be written to multiple parts of multiple nanowires instead of multiple parts of one nanowire to finish store operation in once operation time. Each nanowire only store 1 bit of a segment, so, the number of nanowires is determined by the length of segments. Multiplication  $a_1b_1$ outputs 5 segments but multiplication  $a_2b_2$  only outputs 4 segments, and these is no more segments need to be stored in this dot-product. Therefore, the rest domains in the parts need to store "0" to keep the number of valid

Fig. 10. Different Dot Product Operation

bits unchanged. But if the the segments outputted by a multiplication is more than 5, the parts are filled up, TR needs to access the parts now to get all the interim results and send into tree adders to temporarily store at the next adder. Until all the segments are all accessed by TR and binary interim results have been sent into tree adders, at this time the adder sums up all interim results to get the final dot-product result. TR-assisted LD-SC takes only 18 cycles which is faster than traditional LD-SC twice to finish this dot-product, because TR operations accelerate "counting" and advance the tree adder runtime.

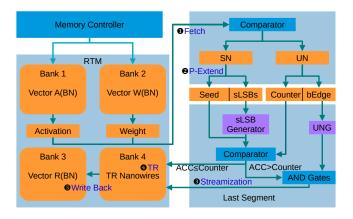

# 4.2 Architecture of Computation

Figure 11 has shown the complete computing architecture of this TR-assisted LD-SC near memory computing. The vectors in Bank 1 and 2 is transferred by memory controller into buffers waiting for computing units as step 1 Fetch. The second step is P-Extension, the generation of seed need the former part of larger operand extension and the seed combine with other three parts which are sLSB, counter and bEdge to form the quadruple. The quadruple supports generating stream segments to output into Bank 4 as step 3 Steamization until the last segment output and the next

Fig. 11. Comprehension Architecture

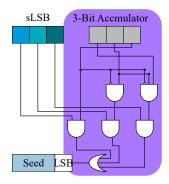

couple of operands from same one dot-product enter the computing unit to output new segments. Actually, there is a accumulator in SN 1 bit generator whose structure showing in Fig. 12 to control the sLSB output order and the accumulator can be compared to the counter to determine if the output computation can be terminated. Owing to the

Fig. 12. SN 1 Bit Generator

length of TRD, each part of nanowire can only store 5 bits because the domains in each end are public for adjacent parts. In this case, after 5 output cycles, TR will access the valid bits of each part on the nanowire and place the binary numbers into the tree adders corresponding to each part's associated dot-product as fourth step. If in the storage stage, some units has finished the computing and the new segments are not ready to output, TR controller will force the parts belong to these unready units to store "0" until new segments arrive. When the tree adder finishes the last time operation, all the valid bits in one dot-product has been accessed and the results in the buffer is the dot-product final result which will be transferred into Bank 3 as binary number as the last step.

#### 4.3 Data Placement Scheme for TR Schedule

The domain block cluster (DBC), as a storage matrix is composed of multiple (usually 8,16,32,...) nanowires and the segments outputted from one dot-product are stored in this kind of matrix. Because of the access pattern of TR which is the adjacent parts can not be access in once operation, we design a ping-pong TR access mode showing in Fig. 13. In this placement scheme, when the parts are all filled up or all

Fig. 13. Data Placement Scheme for Computing

the segments has been outputted into RTM, there are two TR operations to access all the parts in twice operation time to get the interim results and send the interim results into tree adders. The length of segments is  $2^L$ , so, the number of nanowires in each DBC is also  $2^L$ , and each part belongs to a specific computing units but belongs to the same dot-product. This placement scheme can ensure the tree adders are fully loaded and increase the resource utilization.

# 5 EXPLORATION OF DESIGNING SPACE

#### 5.1 Decompression and Efficiency of SLC

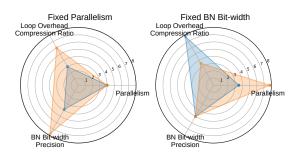

As Fig. 8 shows the seed and BN length control the compression ratio and output computation scale. If a segment is 8 bits long, the 5 bits computation example in Fig. 9 just need two cycles to finish the output computation and one cycle for mixed computation, however, the nanowire need 8 MTJs to parallelly access and larger tree adders to execute addition. So, this is a situation about how to trade of between the overhead of circuits and time. In Fig.14, we qualitatively analyze the relation among

Fig. 14. The Correlation of Parallelism, Loop Cycles, Compression Ratio, and BN Bit-width Precision

Parallelism(P), Output Cycles&Compression Ratio(R) and BN Bit-width&Precision(L). Parallelism(P) represents how

many bits can be parallelly outputted into RTM, that is the length of a segment; Output Cycles means how many cycles need to finish the computation and the more cycles are needed the higher the compression ratio is, because shorter PFC SN has more sLSB and shorter seed; the longer BN bitwidth has more bits to get higher precision of computation in decimal computation. When P is fixed, the longer BN needs more cycles to finish computation and more output computation overhead. When L is fixed, the longer seed can accelerate output computation with less cycles output.

# 5.2 Reconfiguration of Parallelism and BN Length

To vary the output computation overhead when P and L are fixed, we optimize for these two cases separately, trying to get the best configuration. We divide the overhead of whole architecture into three parts: energy overhead in Computation  $(E_C)$ , energy overhead in Racetrack  $(E_R)$  and energy overhead in adders  $(E_A)$ .  $E_C$  is composed of operand converting energy, segment LSB generating energy , energy of selectors controlling the output ways and output energy.  $E_R$  is caused by the operations on RTM which are segments writing energy, domain walls shifting energy and TR energy. The tree adders and the accumulative adders energy overhead is the source of  $E_A$ .

When P is fixed, equivalently, the seed length is fixed,

When L is fixed, equivalently, the BN length is fixed, we utilize energy and time product (EDP) to evaluate the energy efficiency and speed of this architecture. The constraint equation of this situation is that:

$$OPJ = \frac{N_O}{E_C + E_R + E_A} \tag{3}$$

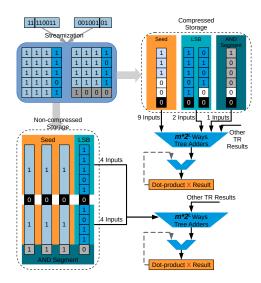

#### 5.3 Seed of Segment Compression

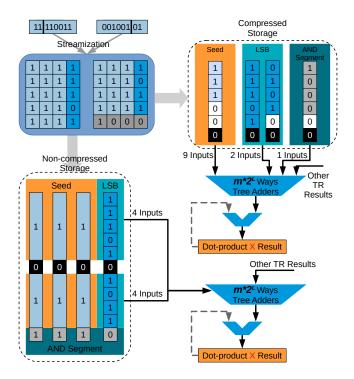

In the former computing examples, it can be noticed that the seed in output computation is receptively wrote into parts, so, when counter is larger there are multiple domains storing same data wasting the storage area. Therefore, if the seed in one multiplication is stored only once and sent multiple TR results in tree adder, the area consumption can be release effectively. Instead of generating segments via seed and SN 1 bit generator when computing a multiplication with LD-SC, the seed is written directly to a part. And the sLSB are converted into SN through SN conversion rules and truncated the SN length by the value of counter, at this time the rest bits of this SN are the segment LSBs written into RTM. As for the mixed computation, whether the stochastic sequences converted by SNGs or UNGs, the last bit is always constant "0", therefore, in mixed computation the LSB of SN segment is negligible. In this case, the mixed computation can be simplified as the mixed segments without LSB of UN AND with seed. In Fig .21 when excuting TR operations, the TR result of seed group needs 9 inputs into tree adder, the LSB group needs 2 inputs for there are two parts LSBs and the mixed computation result needs 1 input. The final result remains the same compared to non-compressed storage, but the utilization of tree adder is reduced because the parts of compressed storage has domain waste and this optimization is not suitable for situations with small counter value.

Fig. 15. Seed Compression Example

#### 6 EXPERIMENT RESULTS

In this section, we first evaluate the energy consumption and latency of our proposed TR-assited LD-SC and compare these metrics with other computing units based on RTM to quantify the advantages our proposed units. To ensure the fairness of the comparison, we will calculate the energy consumption and latency of multiplication and addition operations for computational units which are from COR-USCANT, SPIMand DW-NNin the same energy consumption and latency of read, write, shift and TR operations. Finally we will compare the total energy consumption and total latency of a single classifier computation in VGG19, Alexnet, Lenet, and Resnet18 neural networks, where we are outperforming the other computational units in a single computation, and thus the total energy consumption and latency will theoretically be outperforming the other PIM architectures as well. In the next subsection we will describe the setup of the experiment for TR-assited LD-SC.

#### 6.1 TR-assited LD-SC Experimental Setup

Based on the TR operation of RTM information provided in CORUSCANT, the transverse read distance is 7 domains, and the timing and energy of TR are calculated with the foundation data in CORUSCANT. In order to get a fairer comparison result, we compare each computing unit in the same situation, the read, shift and write timing and energy are referred from DW-NN. RTSim, an open-source domain wall memory simulator, is used to evaluate all the timing and energy consumption of racetrack, but we have modified the foundation information of RTM to ensure that each computing unit uses the same situation of RTM. All the RTM information has been listed in Table 1, the domains in each track is set as 256, but TRD is 7 domains of which 5 domains are valid data and the public domains at both ends are constant 0. Because the adjacent parts can not exceute TR at same time, in this case, we set 32 parts in one track and actually use 193 domains and TR operations can only access 16 parts in one track in one time TR.

The segment output unit and tree adders in this work are synthesized in 45 nm technology using FreePDK45Design

TABLE 1 Experimental setup & RTM parameter.

|                                                                                                               | D ( 1 ()                      |                                   |     |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------|-----|--|--|--|--|--|

| Racetrack properties  Racetrack width/length/thickness $32nm / 64nm / 2.2nm$ Number of bits per racetrack 256 |                               |                                   |     |  |  |  |  |  |

| Racetrack width/length/thickness                                                                              | Number of bits per racetrack  |                                   |     |  |  |  |  |  |

| Critical current density for TR                                                                               | $3.5 \times 10^7 A/cm^2$      | Number of used bits per racetrack |     |  |  |  |  |  |

| shift / write / TR latence                                                                                    | 2 / 2 / 5                     |                                   |     |  |  |  |  |  |

| shift / write / TR energy for                                                                                 | 0.3 / 0.1 / 0.175             |                                   |     |  |  |  |  |  |

| Bank pool properties                                                                                          |                               |                                   |     |  |  |  |  |  |

| Number of tracks per DBC (wordsize)                                                                           | 32                            | Number of DBCs per bank           | 256 |  |  |  |  |  |

| Number of banks per bankpool                                                                                  | 2048                          | Number of bankpools per channel   | 1   |  |  |  |  |  |

| Number of channels per system                                                                                 | 1                             | Number of access ports per track  | 33  |  |  |  |  |  |

| Addressing Sche                                                                                               | Channel:Bankpool:Bank:DBC:Dom | nain                              |     |  |  |  |  |  |

Compile (DC). Due to the different segment length, the output logic has 6 different version, Table 2 shows the output times of each logic version. When seed is composed of first two bits in SN, the output logic is the slowest version and The fastest version of the seed consisting of the first 6 bits outputs only 4 fragments at worst. In the experimental comparisons, we choose the fastest version as output logic. In addition implementation stage, considering that there are positive and negative in neural network multiplication, the track will be divided equally into two halves storing positive and negative LD-SC segment respectively. But in the output logic is unsigned computation, all the TR results of the additions in the final same signed tree adder will be fixed a sign bit for the distinction between positive and negative, and finally into the last signed adder of the whole addition module.

TABLE 2 8 bits Multiplication Output logic & tree adder power.

| 8 bits Multiplication Output logic ( $mW$ ) |                      |       |        |  |  |  |  |  |

|---------------------------------------------|----------------------|-------|--------|--|--|--|--|--|

| Segment Parallelism                         | Largest output times | Power |        |  |  |  |  |  |

| 4-Parallelism                               | 3                    | 64    | 0.1249 |  |  |  |  |  |

| 8-Parallelism                               | 7                    | 32    | 0.1108 |  |  |  |  |  |

| 16 - Parallelism                            | 15                   | 16    | 0.0972 |  |  |  |  |  |

| 32 - Parallelism                            | 31                   | 8     | 0.0848 |  |  |  |  |  |

| 64 - Parallelism                            | 63                   | 4     | 0.0702 |  |  |  |  |  |

Cifar and ImageNet datasets for inmage classification tasks are used to evaluate the timing and energy performance of our proposed architecture with other PIM architectures. To fit the scale of the datasets, Alexnet, VGG19, Inception- V3, Resnet-18, Squeezenet-1.1and LeNet-5are choosen to quantify the performance of each architectures.

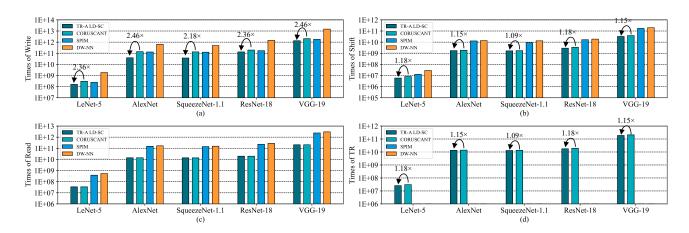

# 6.2 Evaluation of Latency

In this sub-section, we will evaluation the latency of each kind of operations in different PIM architectures based on RTM. We apply 5 Network models on 4 PIM architectures under the same frequency of 1000MHz to record and compare the consumed cycles showing in Table 3. In Table3, the latency changes with the scale of the network, in Lenet-5 our proposed is  $2.88\times$  faster than CORUSCANT and in VGG-19 is  $4.40\times$  faster than CORUSCANT. When the scale of network is larger, TR-assisted LD-SC has higher efficiency in computation, because the write, shift and TR op rations in multiplications executes parallelly and the addition operations are finished by tree adders whose input data comes from TR results. In this case, the number of

ones has no need to be stored into RTM waiting APCs, but input into tree adders to get the addition result of several multiplications. The other three architectures finish the multiplication operation by addition, then they need to calculate the sum and carry bit by bit from LSB to MSB, this is one of the reasons why their overall latency is higher than our proposed work.

Actually, during the computation, our proposed work has fewer operations than other PIM architecture in each stage. In Figure16, our write, shift, read and TR operations are all less than other three architectures, because our multiplication is more data-oriented. There are a large number of data values that are very small in the classifier computation of neural networks, so when performing stochastic computation, there are many zeros in a complete stochastic sequence. TR-assisted LD-SC splits the complete sequence into several sub-sections of shorter lengths, reducing the number of write, shift, and TR operations, and thus speeding up the computation. In subsection *D*, we will provide a detailed description of the data distribution of a single classifier computation in networks and explain why various basic operations are reduced.

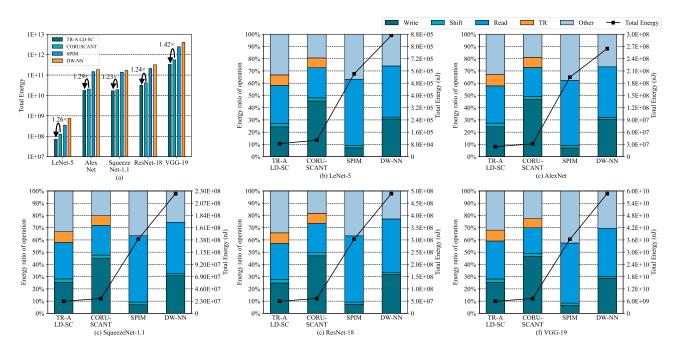

#### 6.3 Evaluation of Energy

The energy consumption in computation of each PIM architectures comes from logic and RTM, and the logic in our proposed work consists mostly of the segments output logic and tree adders logic. The RTM energy consumption is mainly composed of write, shift, read and TR which is the proprietary operation of TR-assisted LD-SC and COR-USCANT. The total energy consumption in computation part is shown as Figure17(a), where five different scale networks are deployed on each PIM architecture. In samll networks, e.g., our proposed work is  $1.26\times$ ,  $6.37\times$  and  $10.3\times$  less energy than the other three architectures and in large networks, e.g., VGG-19, our proposed work is  $1.42\times$ ,  $7.4\times$  and  $11.5\times$  less energy than the other three architectures.

Because, our proposed work has less write, read and shift operations, but the mainly energy consumption is from the logic of outputting segments and adding TR results. The energy consumption increase of logic comes from that our proposed work uses tree adders to execute the multiplication results addition ,but actually saving steps of complete addition operations in one convolution, thereby reducing total energy consumption. In computation write stage, the segment written into RTM are not complete stochastic sequences, that is, the output logic truncates valid

TABLE 3

Latency Evaluation in Different Architectures and Comparison of Speedup.

| Networks Architectures(cycles) |                   |            |            |            | Speedup           |               |               |               |  |

|--------------------------------|-------------------|------------|------------|------------|-------------------|---------------|---------------|---------------|--|

| Networks                       | TR-Assisted LD-SC | CORUSCANT  | SPIM       | DW-NN      | TR-Assisted LD-SC | CORUSCANT     | SPIM          | DW-NN         |  |

| LeNet-5                        | 2.62E + 02        | 7.54E + 02 | 3.17E + 03 | 3.42E + 03 | Ø                 | 2.88×         | 12.0×         | 12.9×         |  |

| AlexNet                        | 3.17E + 03        | 1.36E + 03 | 6.60E + 04 | 7.16E + 04 | Ø                 | $4.29 \times$ | $20.8 \times$ | $22.6 \times$ |  |

| SqueezeNet-1.1                 | 3.48E + 03        | 1.26E + 04 | 5.22E + 04 | 5.66E + 04 | Ø                 | $3.61 \times$ | $15.0 \times$ | $16.3 \times$ |  |

| ResNet-18                      | 5.64E + 03        | 2.22E + 04 | 1.15E + 05 | 1.24E + 05 | Ø                 | $3.94 \times$ | $20.3 \times$ | $22.0 \times$ |  |

| VGG-19                         | 1.06E + 06        | 4.66E + 05 | 2.27E + 06 | 2.46E + 06 | Ø                 | $4.40 \times$ | $21.5 \times$ | $23.3 \times$ |  |

Fig. 16. Latency Evaluation of Different PIM Architecture in Several Networks

Fig. 17. Energy Evaluation of Different PIM Architecture in Several Networks

segments in the complete sequences. In our evaluation, the truncates segments is 64 bits long and written into 64 domains in one DBC in once write operation, which causes that the write operations are less than other three PIM architectures. The Design of tree adders adding multiple multiplications results and less write operations is benefit from that the multiplications of our proposed work are more data-oriented and support the truncation of sequences. The

detail introduction will be presented in subsection 6.4.

# 6.4 Comparision with Prior RTM PIM Architectures

To obtain fair comparison results, the experiments were conducted in the same base lines, and set output logic, RTM and tree adders in a 1ns cycle speed, that is, 1000MHz. Memory architecture refer the DWM architecture in , and also compare DBCs with the architecture proposed in prior

TABLE 4

Operation Comprasion.

| Computing Unit | TI   | R-assited L         | D-SC                | CORUSCANT |                     |                     | SPIM |                     |                     | DW-NN |                     |                     |

|----------------|------|---------------------|---------------------|-----------|---------------------|---------------------|------|---------------------|---------------------|-------|---------------------|---------------------|

| Operation      | Mult | 2 Mults<br>&<br>Add | 5 Mults<br>&<br>Add | Mult      | 2 Mults<br>&<br>Add | 5 Mults<br>&<br>Add | Mult | 2 Mults<br>&<br>Add | 5 Mults<br>&<br>Add | Mult  | 2 Mults<br>&<br>Add | 5 Mults<br>&<br>Add |

| Speed(cycles)  | 32   | 32                  | 34                  | 64        | 90                  | 90                  | 149  | 198                 | 328                 | 163   | 217                 | 357                 |

| Energy(pJ)     | 44.3 | 90.2                | 167.1               | 46.7      | 107.4               | 261.5               | 196  | 420                 | 1101.6              | 308   | 656                 | 1709.6              |

Fig. 18. Distribution of Once Operation in Our work & CORUSCANT

work. The timing of one cycle is already set, so the latency is calculating the number of operations which includes segments output, writing, TR and results addition needed for addition and multiplication. Our proposed architecture combine multiplication and addition, that is, in an 8-bit 2operand multiplication, the worst case under 64-segmentparallelism needs 4 cycles to output all segments. RTM needs 2 cycles for shifting and 2 cycles to writing, that is, in 16 cycles RTM can finish the segment writing, because of one part owning 5 domains, the worst case multiplication outputs 4 64-bit long segments which leave the fifth domain in the 64 parts needs to be "0" to keep the number of "1" in this worst case multiplication unchanged. When the parts are filled by valid data, 64 TR operations need 5 cycles to get the results of this multiplication and send them in to the tree adders waiting for 3 cycles to get the LD-SC multiplication result, which yields to a total 32 cycles and the energy consumption of one worst case multiplication is 167.1pJ. And the multiplications can be parallel, the data in each parts can be TR at the same time and just need another 2 cycles for combinational logic tree adder to add two or more multiplication results together.

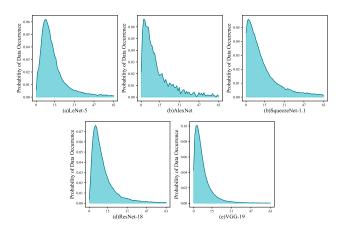

However, in networks computation, there are quite few situation is the worst case multiplication, that is, the multiplication operands are larger than 191 which causes the output logic outputs 4 64-bit segments. The mainly situation is that the output time is only once and the writing, shifting times will reduce significantly. In order to obtain the value distribution of multiplications smaller one operand, we sampled 5 million multiplications with non-zero results in each of Alexnet, VGG19, Resnet-18, Squeezenet-1.1 and Lenet-5 and counted the number of each value appearing in multiplications. Figure 18 shows the distribution from

"0" to "255" of multiplication smaller operands value, and all the networks distributuion shows that the value of 99% operands is between "0" to "63" which means that 64 parts with 5 domains in each part could hold the results of 5 multiplications. The latency and energy consumption used in the worst case multiplication now can finish 5 real multiplications. TR in our proposed work could read 5 multiplications results using less parallelism, cycles and energy as same as in the worst case. In CNN computation, there are quite a few additions in average pooling layers, our proposed architecture could save the addition timing by parallel computers and tree adders.

Table 4 reports the actual speed and energy of TRassited LD-SC, CORUSCANT, SPIM and DW-NN for 2operand multiplication, 2-multiplication results addition and 5-multiplication results addition in network computations. From the data reported in Table4, our proposed TRassisted LD-SC is faster and less energy than CORUSCANT, SPIM and DW-NN at every aspect in actual computation, because the LD-SC multiplication executes in a parallel way. And our architecture is  $2\times$ ,  $2.6\times$  and  $2.6\times$  faster than CORUSCANT in 2-operand multiplication, 2-multiplication results addition and 5-multiplication results addition. In just one multiplication, TR-assisted LD-SC could put one segment on one nanowire which means that the part could fill four domains in one part like the distribution way in Figure ??. The energy consumption is 2.4pJ less than CORUSCANT and in 2-multiplication results addition is 17.2pJ less than CORUSCANT. In 5-multiplication results addition, we change the distribution way as Figure ??, Five 64-bit long segments are written vertically into 64 nanowires and fully fill one part in every nanowires. In this case, TR-Assisted LD-SC owns hihg parallelism in 5-multiplication results addition leading to the lower energy consumption which is  $1.56 \times$  less than CORUSCANT and faster speed.

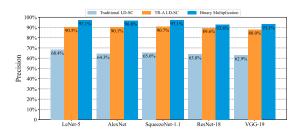

#### 6.5 Neural Networks Precision Comparison

In the classifier computation process, we have chosen to use three different scale neural network models and implement traditional SC, TR-Assisted LD-SC and three other PIM architectures in the networks. The other three PIM architectures are grouped together because they are all exact multiplications. Figure 19 reports the precision results and shows that Our proposed work is slightly lower than exact multiplication but much higher than conventional SC in terms of accuracy. The reason lower than exact multiplication is that the Monte Carlo error in LD-SC itself cannot be eliminated, and some error exists in the most calculations.

Fig. 19. Evaluation of Precision

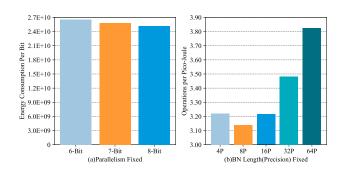

# 6.6 Evaluation of Parallelism and Precision Reconfiguration

In Section *V*, we have discussed the reconfiguration of TR-Assisted LD-SC in parallelism and precision two aspects. The following content will give the energy consumption per bit, OPJ and latency for two different reconfigurable cases.

# 6.6.1 Evaluation of Parallelism Reconfiguration

In Figure 20(a), we take VGG-19 as an example of a setup with a parallelism of 4 at different binary data lengths, i.e., computational accuracy. Then the computational energy consumption per unit bit is calculated based on the constraint formula in Section V with fixed parallelism. Figure 20(a) reports the energy consumption per bit in 3 different binary data length, that is, the computation precision at the 4-paralellism and the lowest energy consumption per unit of precision at a parallelism of 4 is the case where the binary data length is 8-bit. But total energy consumption is indeed highest in the 8bits case, although compared to the 6-bit and 7-bit cases energy consumption is only 26% and 11% higher, respectively. At the same time, the latency of three different precision are 7314, 251855, 930295 cycles. Figure 20(a) and latency also characterize our previous analysis that when the parallelism is constant and the length of the binary number, i.e., the precision, is increased, then the output cycles increase and thus the energy consumption and latency of the whole architecture increases.

Fig. 20. Evaluation of Reconfiguration in Parallelism and BN length

# 6.6.2 Evaluation of Precision Reconfiguration

Figure 20(b) reports the Operation per Pico-Joule(OPJ) of 8-bit case at five different parallelism. When the parallelism is 64, the energy consumption per unit of pico-joule can support 3.82 operations, which is much higher than the OPJ at other parallelism. And high parallelism comes will

TABLE 5 8-Bit Case VGG-19 Computation Latency.

| Parallelism     | 64-P   | 32-P   | 16-P   | 8-P           | 4-P    |

|-----------------|--------|--------|--------|---------------|--------|

| Latency(Cycles) | 105835 | 160799 | 270727 | 490583        | 930295 |

| Speedup         | Ø      | 1.52×  | 2.56×  | $4.64 \times$ | 8.79×  |

more parallel operation which save much latecy. Table 5 reports the latency of different parallelism, as we have analyzed that parallelism and latency are inversely related. Because the low parallelism is more energy efficient that high parallelism, however, in computation, the low parallel output logic need more cycles to output the segments, and a single segment can carry less valid data in low parallelism, and multiple segments are needed to complete the output of all valid data.

# 6.7 Discussion of Segment Compression

In section 5, we analyze that the seed in a segment can be compressed because the seed is the same and repeatedly written and TR in all segments. Taking the case of parallelism of 4 as an example, in the 8-bit case, we only need to know the number of original segment outputs, i.e., the value of the counter in the binary UN. And then input the TR result of the seed into the input of the tree adder that corresponds to the value, to get the same result of multiplication computation. In this example, seed expands to "111"

Fig. 21. Seed Compression Example

and the value of counter is "9", so the output logic needs to output 10 segments including the last segment that requires AND operations. These 10 segments need to be written to 8 parts without compression, while the TR result is 8 binary values, which are input to the tree adder showing in Figure 21(a) and the consumption of area is 40 domains. But if the storage scheme is seed compressed sotrage showing in

Figure 21(b), seed needs one parts, LSB area consumption is same as non-compressed storage, and last segment needs one part, finally total area consumption is 20 domains obviously less than non-compressed storage. Compressed storage is more like changing the write direction of the segment to horizontal, with the complete SEED written in one part and the final AND segment in one part. However, when the value of counter is less than 4, that is, the ouput logic outputs less than 5 segments, the compressed storage will use more cycles than non-compressed mode. Because in compressed storage, even if SEED does not write the full domains of the PARTS it is in, the write will not have any other VALID bits written to it anymore, or else it may cause the TR result to be incorrect. The seed must need 5 times write to keep the TR results of seed is correct. Therefore, when the value of counter is greater than or equal to 4, the compressed storage scheme could optimize both in space and latency. In Table 6, we list the optimization in space, one of the peculiarities is that at 64 parallelism, the number of output segments is at most 4, so compressing the storage inevitably brings an increase in latency, but the optimization is obvious in terms of space overhead. When the number of outputs is 3 and 4, the number of domains is nearly twothirds and one-half of that of non-compressed storage.

TABLE 6 8-Bit Data Compressed Storage Optimization in Space.

| The value of output segment: S(S≥4) (Unit: Part) |      |                     |                |                          |                       |  |  |  |  |

|--------------------------------------------------|------|---------------------|----------------|--------------------------|-----------------------|--|--|--|--|

| Parallelism                                      |      | Comp                | Non-Compressed |                          |                       |  |  |  |  |

| 1 aranensin                                      | Seed | LSB                 | AND<br>Segment | Total                    | Storage               |  |  |  |  |

| 4-P                                              | 1    | $\lceil S/5 \rceil$ | 1              | 2 + [S/5]                | $\lceil 4S/5 \rceil$  |  |  |  |  |

| 8-P                                              | 2    | $\lceil S/5 \rceil$ | 2              | $4 + \lceil S/5 \rceil$  | $\lceil 8S/5 \rceil$  |  |  |  |  |

| 16-P                                             | 3    | $\lceil S/5 \rceil$ | 3              | $6 + \lceil S/5 \rceil$  | $\lceil 16S/5 \rceil$ |  |  |  |  |

| 32-P                                             | 6    | $\lceil S/5 \rceil$ | 6              | $12 + \lceil S/5 \rceil$ | $\lceil 32S/5 \rceil$ |  |  |  |  |

# 7 CONCLUSION

In this work, we develop an in-RTM fast compute architecture utilizing shorter stochastic numbers (SNs) compressed by a novel method called pseudo-fractal compression (PFC). Additionally, we employ TR to access a broader data view without the latency typically associated with APCs. By integrating these techniques, we design counter-free SC-MACs and deploy them near memory, creating a power-efficient neuron architecture. Our evaluation demonstrates that this architecture achieves a 1.26× to 1.42× reduction in energy consumption and a 2.88× to 4.40× increase in computational speed compared to other PIM architectures, all while maintaining high stochastic accuracy.

# **REFERENCES**

- [1] M. H. Najafi and D. J. Lilja, "High quality down-sampling for deterministic approaches to stochastic computing," *IEEE Transactions on Emerging Topics in Computing*, vol. 9, no. 1, pp. 7–14, 2021.

- [2] D. Wang, Z. Wang, L. Yu, Y. Wu, J. Yang, K. Mei, and J. Wang, "A survey of stochastic computing in energy-efficient dnns onedge," in 2021 IEEE Intl Conf on Parallel & Distributed Processing with Applications, Big Data & Cloud Computing, Sustainable Computing & Communications, Social Computing & Networking (ISPA/BDCloud/SocialCom/SustainCom), 2021, pp. 1554–1561.

- [3] Y. Zhang, R. Wang, Y. Hu, W. Qian, Y. Wang, Y. Wang, and R. Huang, "Accurate and energy-efficient implementation of non-linear adder in parallel stochastic computing using sorting network," in 2020 IEEE International Symposium on Circuits and Systems (ISCAS), 2020, pp. 1–5.

- [4] Y. Zhang, S. Lin, R. Wang, Y. Wang, Y. Wang, W. Qian, and R. Huang, "When sorting network meets parallel bitstreams: A fault-tolerant parallel ternary neural network accelerator based on stochastic computing," in 2020 Design, Automation & Test in Europe Conference & Exhibition (DATE), 2020, pp. 1287–1290.

- [5] W. Li, A. Hu, G. Wang, N. Xu, and G. He, "Low-complexity precision-scalable multiply-accumulate unit architectures for deep neural network accelerators," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 70, no. 4, pp. 1610–1614, 2023.

- [6] Y. Hu, T. Zhang, R. Wei, M. Li, R. Wang, Y. Wang, and R. Huang, "Accurate yet efficient stochastic computing neural acceleration with high precision residual fusion," in 2023 Design, Automation & Test in Europe Conference & Exhibition (DATE), 2023, pp. 1–6.

- [7] S. Parkin, "Racetrack memory: a high capacity, high performance, non-volatile spintronic memory," in 2022 IEEE International Memory Workshop (IMW), 2022, pp. 1–4.

- [8] T.-Y. Yang, X. Peng, W. Kang, and M.-C. Yang, "Towards write optimization for skyrmion racetrack memory by skyrmion repermutation," *IEEE Transactions on Computer-Aided Design of In*tegrated Circuits and Systems, pp. 1–1, 2024.

- [9] K. Roxy, S. Ollivier, A. Hoque, S. Longofono, A. K. Jones, and S. Bhanja, "A novel transverse read technique for domainwall "racetrack" memories," *IEEE Transactions on Nanotechnology*, vol. 19, pp. 648–652, 2020.

- [10] T. Nishimura, Y. Ichikawa, A. Goda, N. Misawa, C. Matsui, and K. Takeuchi, "Stochastic computing-based computation-inmemory (sc cim) architecture for dnns and hierarchical evaluations of non-volatile memory error and defect tolerance," in 2023 IEEE International Memory Workshop (IMW), 2023, pp. 1–4.

- [11] J. Wang, H. Chen, D. Wang, K. Mei, S. Zhang, and X. Fan, "A noise-driven heterogeneous stochastic computing multiplier for heuristic precision improvement in energy-efficient dnns," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 42, no. 2, pp. 630–643, 2023.

- Systems, vol. 42, no. 2, pp. 630–643, 2023.

[12] J. Wang, Z. Wang, and D. Wang, "Pseudosc: A binary approximation to stochastic computing within latent operation-space for ultra-lightweight on-edge dnns," in 2023 60th ACM/IEEE Design Automation Conference (DAC), 2023, pp. 1–6.

- [13] Y. Liu, L. Liu, F. Lombardi, and J. Han, "An energy-efficient and noise-tolerant recurrent neural network using stochastic computing," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 27, no. 9, pp. 2213–2221, 2019.