# Just-in-Time Packet State Prefetching

Hamid Ghasemirahni KTH Royal Institute of Technology Stockholm, Sweden

Dejan Kostić KTH Royal Institute of Technology Stockholm, Sweden

## Abstract

Could information about *future* incoming packets be used to build more efficient CPU-based packet processors? Can such information be obtained accurately? This paper studies novel packet processing architectures that receive external "hints" about which packets are soon to arrive, thus enabling prefetching into fast cache memories of the state needed to process them, *just-in-time* for the packets' arrival. We explore possible approaches to (*i*) obtain such hints either from network devices or the end hosts in the communication and (*ii*) use these hints to better utilize cache memories. We show that such information (if accurate) can improve packet processing throughput by at least 50%.

### 1 Introduction

The introduction of multi-100-Gbps links has made packet processing highly challenging on commodity hardware. To process packets at these high rates, without causing a large amount of queuing and performance degradation, recent works advocate: (*i*) offloading computationally expensive operations to programmable network devices & accelerators [3, 4, 6, 20, 40] and/or (*ii*) performing optimizations to maximize the benefits provided by the CPU's cache memories [7, 9–13, 25, 28, 29, 39].

While these efforts improve performance, stateful applications, relying on per-flow data structures, still struggle to achieve high throughput and low latency due to their large memory footprint (i.e., large amount of per-flow state). Fast memories with low-latency access time, such as CPU caches or SRAMs on programmable switches, are essential for supporting high-throughput packet processing. Yet, their limited size makes it difficult to accommodate the large states required by stateful applications. On a CPU-based server, when the state needed to process a packet is not available in any of the cache memories, the CPU must fetch the state from the slow (yet large) DRAM memory and it puts the processing of a packet on "stand-by", an operation that is detrimental for throughput and latency (as shown in this paper). We observe increasing friction between computer architectures and network protocols: computer architectures increasingly require packets processed using the same state to be received in *bursts* to sustain higher cache-hit ratio [12], whereas networking protocols progressively *pace* traffic for

Alireza Farshin NVIDIA Stockholm, Sweden

Marco Chiesa KTH Royal Institute of Technology Stockholm, Sweden

better network-level statistical multiplexing [5]. Existing highthroughput packet processors delay packet processing for tens or hundreds of microseconds to rebuild bursts of packets before processing them [12, 16], which are then transmitted as bursts, defying the purpose of pacing packets at the network level.

Our goal is to combine the best of two worlds by satisfying both networking and hardware requirements, thus achieving higher performance. Our work complements previous optimizations by facilitating stateful networking applications to benefit from cache memories, thereby achieving better performance at higher packet rates. We minimize memory accesses (or equivalently cache misses) by ensuring that the essential data structures required for packet processing are already available in the cache when packets arrive. In particular, we focus on a stateful network function, specifically an L4 load balancer, and try to (i) investigate the impact of looking into the future and prefetching the perflow states before a packet arrives and (ii) explore different possibilities & challenges of building a system, called NOSTRADAMUS, which provides information regarding upcoming packets and enables just-in-time prefetching. We exploit the prefetching capabilities supported by x86 processors to potentially increase performance without imposing any additional cost. We focus on CPU-based packet processing, yet similar principles could apply to any system relying on a hierarchy of memories with different access-time latencies, e.g., a programmable switch with an internal fast & small SRAM and an external DRAM memory.

This work is still underway, but the aim is to spur discussion of effectively performing packet state prefetching to better exploit cache memories. Preliminary results show that carefully-timed packet state prefetching results in up to 50% throughput improvement on a (stateful) L4 load balancer when dealing with a large number of flows. Our work primarily focuses on load balancers because they are a fundamental building block in the current data center architecture, the performance of which directly affects the Internet services latency; however, our results and takeaways could be applicable to other stateful networking applications.

**Contributions.** We (*i*) show the negative impact of statefulness on performance, as cache misses cause a  $3 \times$  throughput drop (§2.2), (*ii*) highlight the benefits of carefully-timed state

prefetching (\$3), and (*iii*) discuss the challenges of building a just-in-time prefetcher (\$4) while exploring future directions to extend such a system (\$5). We plan to release our source code to facilitate the reproducibility of our experiments.

#### 2 Background and Motivation

Section 2.1 provides essential background on load balancers' implementation while Section 2.2 shows the impact of the state size on their performance.

## 2.1 Load Balancers

Load balancers are one of the most critical network functions deployed in today's data centers. They ensure incoming requests are distributed efficiently among backend servers based on a pre-defined policy (*e.g.*, round-robin) and the content of the packet header/payload. For instance, an L4 load balancer typically uses the network- and transport-layer headers (*e.g.*, the TCP/IP 5-tuple) to dispatch the incoming packets, whereas an L7 load balancer may use the application content (*e.g.*, HTTP URL) [6].

When distributing packets to backend servers, it is essential to send the subsequent packets of the same flow to the same server to prevent connection dropping and daisy chaining [34]. To do so, many providers rely on stateful load balancers (rather than stateless ones) to guarantee per-connection consistency [3].

Stateful load balancers typically employ hashing data structures to ensure fast lookups (*e.g.*, Cuckoo hashing) or fast insertions (*e.g.*, chained hashing) [15]. Cuckoo hashing [35] is increasingly used in many networking applications (*e.g.*, the DPDK hash library uses the Cuckoo hash algorithm to resolve collisions).

Cuckoo hashing is an open-addressing algorithm that employs multiple hash functions to assign each key to multiple locations (aka buckets) in order to resolve collisions. It guarantees worst-case O(1) lookup & deletion times. In cases where the number of entries is lower than 50% of the hash table's capacity, Cuckoo hashing also offers O(1)insertion times. While a very large hash table would guarantee fast insertion times, it may prevent the hash table entries from staying in (or requests to be served from) the cache, as the hardware prefetching mechanisms might prefetch sparse buckets and evict useful information from the cache. Most Cuckoo-hashing implementations use only two hash functions, where the locations are referred to as primary and secondary buckets. Some extensions of Cuckoo hashing store multiple entries per bucket to achieve better performance by reducing the number of memory loads [8]. The DPDK implementation of Cuckoo hashing maintains two tables. The first table is an array of buckets that contains a signature of the key and an index to the second table, whereas the second table is an array of stored keys along with their associated data. To minimize memory accesses for a lookup, DPDK stores 8

entries per bucket (this value is configurable); hence, each bucket can fit on a single cache line (*i.e.*, 64 B) and the system is able to examine up to 8 entries with a single memory-fetch operation.

#### 2.2 Impact of Statefulness on Performance

The goal of this section is to show the impact of statefulness on performance. More specifically, we hypothesize that increasing the application state size could eventually cause the states to not fit in the cache, causing performance degradation. To verify our hypothesis and understand the impact of memory footprint on the performance of load balancers, we use a simple L4 load balancer implemented on top of DPDK-based FastClick [2]. We intentionally rely on DPDK, a kernel-bypass framework, to be able to purely consider the load balancer states and exclude other stateful operations done within the Linux network stack<sup>1</sup>. Our load balancer implementation distributes flows among K servers in a roundrobin fashion. To do so, it chooses a destination IP address (i.e., a server) when the first packet of each flow arrives and then keeps the chosen address in the  $i^{th}$  index of an array. The value of *i* is stored in a Cuckoo hash table, enabling the load balancer to retrieve the chosen address upon the arrival of other packets belonging to the same flow.

Testbed. Experiments were run on a testbed containing two commodity servers connected together via a  $32 \times 100$ -Gbps Edgecore Networks DCS800 Wedge 100BF-32X switch equipped with an Intel<sup>®</sup> Tofino<sup>TM</sup>ASIC [17]. One server acts as a traffic generator, and the other is our Device Under Test (DUT) which runs a stateful load balancer. The DUT is equipped with NVIDIA Mellanox ConnectX<sup>®</sup>-5 NICs [33] and Intel® Xeon® Gold 6246R CPUs @ 3.40 GHz with 2×32-KiB per-core L1 (instruction & data) & 1-MiB per-core L2 caches and a 36-MiB shared Last Level Cache (LLC) with 11 cache ways. The Tofino switch enables us to (i) make clones of incoming packets in a known order to increase the offered load on the DUT and (ii) write the 5-tuple hash of current & predicted packets into the packets. We plot median values with min/max error bars (though in many experiments the range is small and almost invisible).

**Workload generation.** We use Fastclick [2] on the traffic generator to create synthetic traffic traces (with UDP flows) and inject them into the network. We minimize the locality of packets in the generated trace files by keeping the packets of each flow far from each other<sup>2</sup>. Additionally, we make multiple clones of each packet coming from the generator to put a higher load on the DUT. We change the source UDP port number for each cloned packet to avoid creating a batch of packets belonging to the same flow. For the sake of simplicity

<sup>&</sup>lt;sup>1</sup>Evaluating the impact of statefulness within the Linux kernel remains as our future work.

<sup>&</sup>lt;sup>2</sup>Real-world traffic may have a different inter-packet distance distribution; further evaluation remains as our future work.

and enforcing predictability, we only change the UDP ports between different flows in our experiments. Moreover, we warm up the hash table with the relevant entries to ignore insertion overhead and ensure that all the state lookups are served at a constant time.

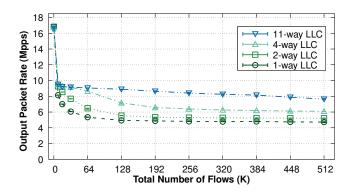

The performance of stateful NFs drops with increasing numbers of flows. The first experiment measures the per-core throughput of a load balancer when the total number of flows increases. Intel's Cache Allocation Technology (CAT) [32] is utilized to change the size of the LLC allocated to the working core. Figure 1 shows that the NF's throughput decays exponentially with an increasing number of flows. Reducing the size of the LLC causes the throughput to drop earlier, *i.e.*, with a smaller number of flows. For instance, when the working core is limited to use only 1 way (*i.e.*, 3.5 MiB), throughput drops almost 70% after exceeding 64 k flows. We expect a larger LLC quota to experience the same throughput drop but with a larger number of flows.

**Figure 1.** Increasing the number of flows causes an exponential decay in throughput of an L4 load balancer.

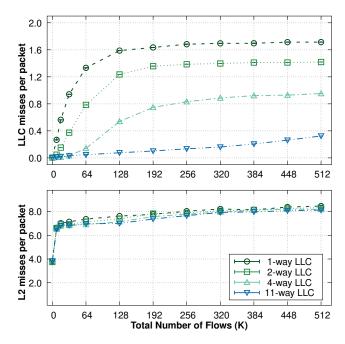

To understand the reason behind the throughput drop, we measure the number of per-packet cache misses in each experiment. Figure 2 illustrates that the drop in throughput is correlated with the increase in the number of per-packet LLC misses, which verifies our hypothesis that increasing the size of the state would prevent stateful network functions from benefitting efficiently from the cache memories. Additionally, the exponential increase in the number of per-packet L2 misses<sup>3</sup> justifies the sharp throughput drop after exceeding 8 k flows. Table insertions are *not* the bottleneck since we have warmed up the table.

The rest of this paper will focus on the smallest LLC size to: (i) emulate advanced applications with a larger memory footprint (to compensate for our simple low-overhead load balancer implementation), (ii) consider real-world scenarios where multiple applications running on the same hardware have their own cache allotment to ensure security, privacy, and

**Figure 2.** The average number of per-packet LLC misses increases with larger numbers of flows, which is inversely proportional to the throughput. The exponential increase in the number of per-packet L2 misses corresponds to the initial throughput drop.

performance [27, 39], and (*iii*) show the full potential of our solution when states do not fit into the cache. Investigating the impact of other cache allotments remains our future work.

## **3** Prefetch the State in Advance

The last section showed that increasing the state size prevents stateful network functions benefitting from the cache. To alleviate this, we exploit prefetching instructions (e.g., PREFETCHn) offered by modern processors to issue memory load requests in advance and thus fetch data into the cache earlier than the actual packet processing time. This section investigates the impact of state prefetching, i.e., before packets arrive. Some highly optimized frameworks prefetch some data structures and/or some parts of the received packets at packet reception time, e.g., FastClick [2] prefetches the content of the packet and its metadata when receiving a batch of packets via DPDK, while FAJITA [14] and VPP [26] utilize software prefetching to provide required state data for processing a batch of packets in stateful network functions. In contrast to previous works, we use *software prefetching mechanisms* to minimize the memory loads for *future* batches of packets, which is complementary to the earlier efforts.

#### 3.1 Challenges and Solutions

While sounding appealing, performing prefetching requires addressing the following challenges:

<sup>&</sup>lt;sup>3</sup>We use 12\_rqsts.miss event to measure L2 misses, *i.e.*, similar trend as LLC loads in a non-inclusive cache hierarchy [30].

What to prefetch? It is important to find the trade-off between the benefits and overheads of prefetching, as sometimes prefetching the data may be very expensive due to many dependencies & extra processing. For instance, DPDKbased hash tables store 8 hashes per bucket; therefore, loading the actual data stored in a bucket requires performing up to 8 comparison operations, which may cancel out the benefits of prefetching. Additionally, premature prefetching is known to be detrimental to performance [23]; prefetching a large amount of data may cause more harm than good, *i.e.*, this may evict the other useful data/code from the cache. We use large hash tables in our experiments, which increases the chance of finding data at the primary location of the key. Therefore, we only prefetch the primary bucket of the upcoming packet to avoid unnecessary prefetching. However, prefetching data from the secondary location could also be beneficial when the probability of finding data at the secondary location is higher (e.g., when the hash tables are smaller).

How long to keep the data? Intel's prefetching instructions make it possible to specify a temporal and spatial locality factor for data. Table 1 shows the specification of different x86 prefetching instructions [18]. Our experiments mainly use prefetcht0 to maximize the state locality. The next section shows the impact of different locality factors.

Table 1. Prefetching instructions in Intel processors.

| Instructions | Cache Levels |    |     | Early Replacement |

|--------------|--------------|----|-----|-------------------|

| prefetcht0   | L1           | L2 | LLC | -                 |

| prefetcht1   | -            | L2 | LLC | _                 |

| prefetcht2   | -            | L2 | LLC | ×                 |

| prefetchnta  | -            | L2 | _   | ×                 |

When to prefetch? Prefetching too early or too late could reduce the benefits of prefetching due to potential evictions and overheads. Thus, it is essential to prefetch the required data structure *just-in-time* to maximize the benefits. Therefore, we measure the improvements for different "spatial prefetching distances" to find the optimal distance for our use case. We define spatial prefetching distance as the packet gap between the currently-being-processed packet and the upcoming packet that is expected to be processed in the near future.

Next, we will show the potential benefits of just-in-time state prefetching. We only report the throughput of a singlecore load balancer due to our workload-generation method that clones packets & embeds Cuckoo hash values; however, our takeaways could be applicable to multi-core applications and could have a positive impact on latency.

#### 3.2 Potential Benefits

We run a simple experiment with a deterministic packet order and we embed the flow identifier of an upcoming packet into the current packet. We modify the FlowIPManagerIMP element of the load balancer to prefetch the first bucket of its hash table based on the embedded packet identifier before proceeding to the actual lookup operation. Using a trace with deterministic packet order also enables us to investigate the impact of spatial prefetching distance. This helps us to maximize the prefetching benefits, *i.e.*, how far in the future (or how many packets ahead) we should see to maximize the throughput improvements.

As upcoming packets are always predictable in our experiments (given their deterministic order), we initially calculate the 5-tuple value of the upcoming (*i.e.*, expected-tobe-received) packet based on the currently-being-processed packet's header. This allows us to calculate the Cuckoo hash value of the upcoming packet based on its 5-tuple value. As expected, this method ("NoOffload") imposes additional computation overhead on the load balancer; therefore, we also consider an alternative approach ("Offload") where we calculate the Cuckoo hash of the upcoming packet on a programmable switch and embed the Cuckoo hash of the current and upcoming packets into the current packet. By doing so, we can eliminate the prefetching overhead to a great extent and can see the full potential of network-accelerated just-in-time prefetching.

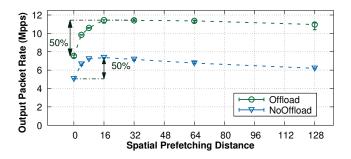

Figure 3 shows the impact of prefetching states for different spatial prefetching distances. When the spatial prefetching distance is small, the prefetched data will become available in caches too late; therefore, the load balancer does not experience the full potential of the state prefetching. On the other hand, large spatial prefetching distances load the data too early into the cache, which increases the probability of the data/state being evicted from the cache before the (expected) packet arrives. This experiment demonstrates that performing just-in-time prefetching is crucial to maximizing the benefits of state prefetching. Moreover, these results show that the maximum benefit occurs when prefetching distance is 16 with and without hash offloading. Note that DPDK typically receives 32 or fewer packets in each batch; therefore, the prefetching distance of 16 can benefit both current & future batches.

**Figure 3.** Fine-tuning the spatial prefetching distance is essential to maximize the throughput improvements.

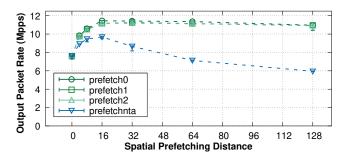

Figure 4 shows the impact of using different prefetching instructions. These results show that prefetching data to different levels of cache hierarchy has a negligible impact on performance benefits. Additionally, using prefetchnta with the lowest temporal & spatial factor reduces the throughput improvements for large prefetching distances.

**Figure 4.** Using prefetchnta reduces the throughput improvements for large spatial prefetching distances, due to its lower temporal & spatial locality.

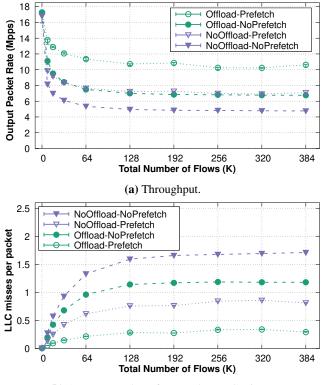

**Impact on throughput drop.** We conclude our preliminary analysis by demonstrating the impact of carefully-timed prefetching on throughput and the number of per-packet LLC misses when an L4 load balancer is receiving different numbers of flows. Figure 5 shows that performing prefetching improves the throughput by up to 50% (*i.e.*, it recovers the throughput drop due to statefulness); similarly, it reduces the number of per-packet LLC misses. As expected, when we offload the hash calculation to the programmable switch, the load balancer achieves higher throughput and experiences a smaller number of LLC misses. Furthermore, performing prefetching (without offloading) results in similar throughput to the no-prefetching case (with offloading) despite spending some cycles on hash calculation.

### 4 Building a Just-in-time Prefetcher

The last section showed the potential benefits of just-in-time state prefetching for stateful networking applications. However, deploying a real-world solution requires knowing the estimated arrival time of upcoming packets and performing the prefetching as efficiently as possible.

This section explores different alternatives for building a just-in-time prefetcher, called NOSTRADAMUS, which is responsible for (i) providing prefetching hints to backend servers and (ii) prefetching the required data structures.

(i) How to provide hints? The first step is to estimate the arrival time of upcoming packets. This hinting can potentially be implemented in different entities in the network that inform the backend servers regarding the time and contents to be prefetched. We envision two alternatives for providing the prefetching hints.

(b) Average number of per-packet LLC misses.

**Figure 5.** Performing just-in-time prefetching improves the throughput by up to 50% (*i.e.*, it recovers the throughput drop due to statefulness).

- Clients can incorporate signals to specify an estimate to the backend servers regarding the arrival time of the next packet in a flow. This approach can potentially be accompanied by a mechanism to further fine-tune the estimated time. For instance, a backend server can track the number of per-packet cache misses and use a control loop to more timely prefetch the required data structures. Moreover, some applications send traffic periodically with a known interval (*e.g.*, video streaming), this interval can be used by stateful applications as a prefetching signal. When embedding such information, security measures should be considered to prevent potential attacks.

- A programmable network device (*e.g.*, a programmable switch or a smart NIC) can send a signal to the backend servers regarding the arrival time of the upcoming packets. The device can either rely on (1) buffering packets in the network or (2) employing statistical pattern recognition techniques (*e.g.*, AI-based algorithms) to estimate the arrival time and provide hints to the backend servers. The former method can be already implemented in existing programmable switches, as they currently support packet recirculation, making it possible to delay/buffer packets in the network to enforce a deterministic packet order.

(ii) How to prefetch? After crafting the prefetching hints, the next step is to efficiently use the received information. As shown in §2.2, an obvious method to use the prefetching hints is to modify the stateful applications to perform the prefetching at an appropriate time. This method would potentially provide the most locality for the prefetched data, as the required data structures would be loaded into the highest level (L1) cache of the core responsible for processing the upcoming packet. However, it may not be preferable in some scenarios, since it requires modifying the application's code and executing additional instructions to prefetch the data. An alternative implementation can exploit other available resources to perform the prefetching. For example, a smart NIC can be configured to (i) extract the prefetching information and (ii) redirect them to cores specifically deployed to handle prefetching requests, or (ii-b)to perform the prefetching itself. Step (ii) prefetches the data into other cores' caches, which requires inter-core communication to move the states to the processing core; therefore, this method may be less efficient than performing prefetching by the application. However, it is still beneficial, as it mitigates loading states from the memory and eliminates the need to modify the application's code. It is worth mentioning that step (i) can be potentially omitted if the clients and/or network devices send prefetching hints as standalone packets rather than incorporating the information into the existing packets; however, this alternative would consume more network bandwidth.

## **5** Future Use Cases and Directions

This section elaborates on (i) future use cases of state prefetching and (ii) further optimizations.

#### 5.1 Applications

**Network functions.** This paper primarily focused on an L4 load balancer; however, just-in-time prefetching can be beneficial for *other* stateful network functions, such as advanced packet schedulers or a TCP optimizer.

**Congestion control protocols.** Many networking applications rely on either Linux-based or userspace congestion control protocols (*e.g.*, TCP and QUIC) to ensure reliable & fair transmission. These protocols operate at the granularity of a flow, which requires them to keep per-flow states; therefore, a highly optimized implementation of congestion control protocol could potentially benefit from just-in-time state prefetching to optimize the protocol stack processing.

**Key-value stores.** Key-value stores are one of the main building blocks of Internet services. They often act as an intermediate cache layer between slow database servers and frontend servers (*e.g.*, web servers) to hide the additional latency of storage systems. Similar to stateful load balancers, key-value stores mostly employ hash tables to store the

key-value pairs; therefore, prefetching the key-value pairs in advance could improve their performance. However, providing hints to the servers requires a different traffic pattern recognition since key-value GET/SET requests are not necessarily flow dependant, *i.e.*, each flow can hypothetically access all key-value pairs. Key-value store workloads are often skewed, *i.e.*, some keys are requested more than others; hence, popular key-value pairs may have a higher probability of being available in the cache; however, less popular large key-value pairs could evict the popular ones from the cache, making just-in-time prefetching beneficial.

#### 5.2 Programmable Hardware & Accelerators

We focused on commodity CPU-based hardware with cache memories; however, other networking equipment with a hierarchical memory can benefit from our solution. For instance, a recent wave of publications [21, 22, 37, 38] extends the limited memory on programmable switches with disaggregated memory accessible from RDMA-capable servers to address the challenges of implementing advanced networking applications. In those proposals, a programmable switch may need to fetch some data structures from the remote memory, where performing in-advance prefetching could hide the imposed fetching/loading latency and improve performance. Moreover, our solution could be applicable to (*i*) disaggregated servers to minimize remote memory access latency [1, 24, 36] and (*ii*) smart NICs to hide PCIe overhead when using the host memory [19, 31].

#### 5.3 Optimizing Data Structures and Code

This paper mainly considered the benefits of just-in-time prefetching for a two-layer implementation of Cuckoo hashing in DPDK; however, any other hash table or data structure could potentially benefit from our approach. For instance, one can potentially embed the data in the hash table (rather than the index of an array), thus prefetching the actual data without imposing computational overhead. An implementation of NOSTRADAMUS could potentially parse a DPDK program (along with a workload profile similar to PGO) and automatically include prefetching instructions and/or *optimize data structures* for the performance-critical data structures keeping per-flow states. For instance, if a programmable device guarantees a deterministic order for the packets, NOSTRADAMUS can replace a hash table with a queue to mitigate unnecessary overheads of keeping states.

### 5.4 Further Cache Optimizations

This paper only considered using *prefetching* instructions to efficiently handle packet states for networking applications. Future processors are expected to be shipped with more cache management instructions & techniques. For instance, Intel Xeon "Sapphire Rapids" processors are going to feature a "CLDEMOTE" instruction that can be used to demote cache lines by moving them to lower/further levels in the cache

hierarchy. One can exploit this instruction to better manage the cache for stateful applications based on prefetching hints.

# 6 Conclusion

Statefulness can make cache memories less effective for high-speed networking applications. This paper proposes an unexplored path to notify the applications in advance about upcoming packets, enabling them to prefetch the data structures required for packet processing into the cache *before* the arrival of the actual packets. Our goal is to emphasize the importance of exploring new opportunities and developing modern techniques to better take advantage of cache memories at multi-100-Gbps rates.

### References

- [1] E. Amaro, C. Branner-Augmon, Z. Luo, A. Ousterhout, M. K. Aguilera, A. Panda, S. Ratnasamy, and S. Shenker. Can Far Memory Improve Job Throughput? In *Proceedings of the Fifteenth European Conference* on Computer Systems, EuroSys '20, New York, NY, USA, 2020. Association for Computing Machinery.

- [2] T. Barbette, C. Soldani, and L. Mathy. Fast Userspace Packet Processing. In *Proceedings of the Eleventh ACM/IEEE Symposium on Architectures for Networking and Communications Systems*, ANCS '15, pages 5–16, Washington, DC, USA, 2015. IEEE Computer Society.

- [3] T. Barbette, C. Tang, H. Yao, D. Kostić, G. Q. Maguire Jr., P. Papadimitratos, and M. Chiesa. A High-Speed Load-Balancer Design with Guaranteed Per-Connection-Consistency. In *17th USENIX* Symposium on Networked Systems Design and Implementation (NSDI 20), pages 667–683, Santa Clara, CA, Feb. 2020. USENIX Association.

- [4] M. S. Brunella, G. Belocchi, M. Bonola, S. Pontarelli, G. Siracusano, G. Bianchi, A. Cammarano, A. Palumbo, L. Petrucci, and R. Bifulco. hXDP: Efficient software packet processing on FPGA NICs. In 14th USENIX Symposium on Operating Systems Design and Implementation (OSDI 20), pages 973–990. USENIX Association, Nov. 2020.

- [5] N. Cardwell, Y. Cheng, S. H. Yeganeh, I. Swett, and V. Jacobson. BBR Congestion Control. Internet-Draft draft-cardwell-iccrg-bbrcongestion-control-02, Internet Engineering Task Force, Mar. 2022. Work in Progress.

- [6] T. Cui, W. Zhang, K. Zhang, and A. Krishnamurthy. *Offloading Load Balancers onto SmartNICs*, page 56–62. Association for Computing Machinery, New York, NY, USA, 2021.

- [7] B. Deng, W. Wu, and L. Song. Redundant Logic Elimination in Network Functions. In *Proceedings of the Symposium on SDN Research*, SOSR '20, page 34–40, New York, NY, USA, 2020. Association for Computing Machinery.

- [8] M. Dietzfelbinger and C. Weidling. Balanced allocation and dictionaries with tightly packed constant size bins. *Theoretical Computer Science*, 380(1-2):47–68, 2007.

- [9] A. Farshin, T. Barbette, A. Roozbeh, G. Q. Maguire Jr., and D. Kostić. PacketMill: Toward per-Core 100-Gbps Networking. ASPLOS 2021, page 1–17, New York, NY, USA, 2021. Association for Computing Machinery.

- [10] A. Farshin, A. Roozbeh, G. Q. Maguire Jr., and D. Kostić. Make the Most out of Last Level Cache in Intel Processors. In *Proceedings of the Fourteenth EuroSys Conference 2019*, EuroSys '19, pages 8:1–8:17, New York, NY, USA, 2019. ACM.

- [11] A. Farshin, A. Roozbeh, G. Q. Maguire Jr., and D. Kostić. Reexamining Direct Cache Access to Optimize I/O Intensive Applications for Multi-hundred-gigabit Networks. In 2020 USENIX Annual Technical Conference (USENIX ATC 20), pages 673–689. USENIX Association, July 2020.

- [12] H. Ghasemirahni, T. Barbette, G. P. Katsikas, A. Farshin, A. Roozbeh, M. Girondi, M. Chiesa, G. Q. Maguire Jr., and D. Kostić. Packet Order Matters! Improving Application Performance by Deliberately Delaying Packets. In 19th USENIX Symposium on Networked Systems Design and Implementation (NSDI 22), pages 807–827, Renton, WA, Apr. 2022. USENIX Association.

- [13] H. Ghasemirahni, A. Farshin, M. Scazzariello, M. Chiesa, and D. Kostić. Deploying stateful network functions efficiently using large language models. In *Proceedings of the 4th Workshop on Machine Learning and Systems*, EuroMLSys '24, page 28–38, New York, NY, USA, 2024. Association for Computing Machinery.

- [14] H. Ghasemirahni, A. Farshin, M. Scazzariello, G. Q. Maguire Jr., D. Kostić, and M. Chiesa. Fajita: Stateful packet processing at 100 million pps. *Proc. ACM Netw.*, 2(CoNEXT3), September 2024.

- [15] M. Girondi, M. Chiesa, and T. Barbette. High-speed Connection Tracking in Modern Servers. In 2021 IEEE 22nd International Conference on High Performance Switching and Routing (HPSR), pages 1–8, 2021.

- [16] J. Hu. Accelerating Packet Processing with GRO and GSO in DPDK, 2018. https://www.dpdk.org/wpcontent/uploads/sites/35/2018/06/GRO-GSO-Libraries-Bring-Significant-Performance-Gains-to-DPDK-based-Applications.pdf.

- [17] Intel. Intel Tofino Series, 2022. https://www.intel.com/content/ www/us/en/products/network-io/programmable-ethernetswitch/tofino-series.html.

- [18] Intel. MM\_PREFETCH Development Reference Guides, 2022. https://www.intel.com/content/www/us/en/develop/ documentation/fortran-compiler-oneapi-dev-guide-andreference/top/language-reference/a-to-z-reference/m-ton/mm-prefetch.html.

- [19] G. P. Katsikas, T. Barbette, M. Chiesa, D. Kostić, and G. Q. Maguire Jr. What You Need to Know About (Smart) Network Interface Cards. In O. Hohlfeld, A. Lutu, and D. Levin, editors, *Passive and Active Measurement*, pages 319–336, Cham, 2021. Springer International Publishing.

- [20] G. P. Katsikas, T. Barbette, D. Kostić, R. Steinert, and G. Q. Maguire Jr. Metron: NFV Service Chains at the True Speed of the Underlying Hardware. In 15th USENIX Symposium on Networked Systems Design and Implementation (NSDI 18), pages 171–186, Renton, WA, 2018. USENIX Association.

- [21] D. Kim, Z. Liu, Y. Zhu, C. Kim, J. Lee, V. Sekar, and S. Seshan. TEA: Enabling State-Intensive Network Functions on Programmable Switches. In Proceedings of the Annual Conference of the ACM Special Interest Group on Data Communication on the Applications, Technologies, Architectures, and Protocols for Computer Communication, SIGCOMM '20, page 90–106, New York, NY, USA, 2020. Association for Computing Machinery.

- [22] J. Langlet, R. Ben-Basat, S. Ramanathan, G. Oliaro, M. Mitzenmacher, M. Yu, and G. Antichi. Zero-CPU Collection with Direct Telemetry Access. In *Proceedings of the Twentieth ACM Workshop on Hot Topics in Networks*, HotNets '21, page 108–115, New York, NY, USA, 2021. Association for Computing Machinery.

- [23] J. Lee, H. Kim, and R. Vuduc. When Prefetching Works, When It Doesn't, and Why. ACM Trans. Archit. Code Optim., 9(1), mar 2012.

- [24] S.-s. Lee, Y. Yu, Y. Tang, A. Khandelwal, L. Zhong, and A. Bhattacharjee. MIND: In-Network Memory Management for Disaggregated Data Centers. In *Proceedings of the ACM SIGOPS* 28th Symposium on Operating Systems Principles, SOSP '21, page 488–504, New York, NY, USA, 2021. Association for Computing Machinery.

- [25] T. Lévai, F. Németh, B. Raghavan, and G. Retvari. Batchy: Batch-scheduling Data Flow Graphs with Service-level Objectives . In 17th USENIX Symposium on Networked Systems Design and Implementation (NSDI 20), pages 633–649, Santa Clara, CA, Feb.

2020. USENIX Association.

- [26] L. Linguaglossa, D. Rossi, S. Pontarelli, D. Barach, D. Marjon, and P. Pfister. High-speed data plane and network functions virtualization by vectorizing packet processing. *Computer Networks*, 149:187– 199, 2019. https://www.sciencedirect.com/science/article/pii/ S1389128618312957.

- [27] A. Manousis, R. A. Sharma, V. Sekar, and J. Sherry. Contention-Aware Performance Prediction For Virtualized Network Functions. In Proceedings of the Annual Conference of the ACM Special Interest Group on Data Communication on the Applications, Technologies, Architectures, and Protocols for Computer Communication, SIGCOMM '20, page 270–282, New York, NY, USA, 2020. Association for Computing Machinery.

- [28] S. Miano, A. Sanaee, F. Risso, G. Rétvári, and G. Antichi. Domain Specific Run Time Optimization for Software Data Planes. In Proceedings of the 27th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, ASPLOS 2022, page 1148–1164, New York, NY, USA, 2022. Association for Computing Machinery.

- [29] L. Molnár, G. Pongrácz, G. Enyedi, Z. L. Kis, L. Csikor, F. Juhász, A. Kőrösi, and G. Rétvári. Dataplane Specialization for High-Performance OpenFlow Software Switching. In *Proceedings of the* 2016 ACM SIGCOMM Conference, SIGCOMM '16, page 539–552, New York, NY, USA, 2016. Association for Computing Machinery.

- [30] D. Mulnix. Intel Xeon Processor Scalable Family Technical Overview. https://www.intel.com/content/www/us/en/developer/articles/ technical/xeon-processor-scalable-family-technical-overview, Sep 2017. Online; accessed 2022-06-1.

- [31] R. Neugebauer, G. Antichi, J. F. Zazo, Y. Audzevich, S. López-Buedo, and A. W. Moore. Understanding PCIe Performance for End Host Networking. In *Proceedings of the 2018 Conference of the ACM Special Interest Group on Data Communication*, SIGCOMM '18, pages 327–341, New York, NY, USA, 2018. ACM.

- [32] K. Nguyen. Introduction to Cache Allocation Technology in the Intel Xeon Processor E5 v4 Family, Feb 2016. https://www.intel.com/content/www/us/en/developer/articles/ technical/introduction-to-cache-allocation-technology.html, accessed 2022-06-13.

- [33] NVIDIA Networking. NVIDIA Mellanox ConnectX-5 adapters, 2021. https://www.nvidia.com/en-us/networking/ethernet/connectx-5/.

- [34] V. Olteanu, A. Agache, A. Voinescu, and C. Raiciu. Stateless Datacenter Load-balancing with Beamer. In 15th USENIX Symposium on Networked Systems Design and Implementation (NSDI 18), pages 125–139, Renton, WA, Apr. 2018. USENIX Association.

- [35] R. Pagh and F. F. Rodler. Cuckoo Hashing. J. Algorithms, 51(2):122–144, may 2004.

- [36] A. Roozbeh, J. Soares, G. Q. Maguire Jr., F. Wuhib, C. Padala, M. Mahloo, D. Turull, V. Yadhav, and D. Kostić. Software-Defined "Hardware" Infrastructures: A Survey on Enabling Technologies and Open Research Directions. *IEEE Communications Surveys Tutorials*, 20(3):2454–2485, thirdquarter 2018.

- [37] A. Sapio, M. Canini, C.-Y. Ho, J. Nelson, P. Kalnis, C. Kim, A. Krishnamurthy, M. Moshref, D. Ports, and P. Richtarik. Scaling Distributed Machine Learning with In-Network Aggregation. In 18th USENIX Symposium on Networked Systems Design and Implementation (NSDI 21), pages 785–808. USENIX Association, Apr. 2021.

- [38] M. Scazzariello, T. Caiazzi, H. Ghasemirahni, T. Barbette, D. Kostić, and M. Chiesa. A High-Speed stateful packet processing approach for tbps programmable switches. In 20th USENIX Symposium on Networked Systems Design and Implementation (NSDI 23), pages 1237– 1255, Boston, MA, Apr. 2023. USENIX Association. https://www. usenix.org/conference/nsdi23/presentation/scazzariello.

- [39] A. Tootoonchian, A. Panda, C. Lan, M. Walls, K. Argyraki, S. Ratnasamy, and S. Shenker. ResQ: Enabling SLOs in Network Function Virtualization. In 15th USENIX Symposium on Networked Systems Design and Implementation (NSDI 18), pages 283–297, Renton, WA, Apr. 2018. USENIX Association.

- [40] Z. Zhao, H. Sadok, N. Atre, J. C. Hoe, V. Sekar, and J. Sherry. Achieving 100Gbps Intrusion Prevention on a Single Server. In 14th USENIX Symposium on Operating Systems Design and Implementation (OSDI 20), pages 1083–1100. USENIX Association, Nov. 2020.