# Runtime Instrumentation for Reactive Components (Extended Version)

Luca Aceto **□** •

Reykjavik University, Reykjavik, Iceland Gran Sasso Science Institute, L'Aquila, Italy

Duncan Paul Attard

□

University of Glasgow, Glasgow, UK

Adrian Francalanza ⊠ ©

University of Malta, Msida, Malta

Reykjavik University, Reykjavik, Iceland

#### Abstract

Reactive software calls for instrumentation methods that uphold the reactive attributes of systems. Runtime verification imposes another demand on the instrumentation, namely that the trace event sequences it reports to monitors are sound—that is, they reflect actual executions of the system under scrutiny. This paper presents RIARC, a novel decentralised instrumentation algorithm for outline monitors meeting these two demands. The asynchronous setting of reactive software complicates the instrumentation due to potential trace event loss or reordering. RIARC overcomes these challenges using a next-hop IP routing approach to rearrange and report events soundly to monitors.

RIARC is validated in two ways. We subject its corresponding implementation to rigorous systematic testing to confirm its correctness. In addition, we assess this implementation via extensive empirical experiments, subjecting it to large realistic workloads to ascertain its reactiveness. Our results show that RIARC optimises its memory and scheduler usage to maintain latency feasible for soft real-time applications. We also compare RIARC to inline and centralised monitoring, revealing that it induces comparable latency to inline monitoring in moderate concurrency settings, where software performs long-running, computationally-intensive tasks, such as in Big Data stream processing.

2012 ACM Subject Classification Software and its engineering → Software verification and validation

Keywords and phrases Runtime instrumentation, decentralised monitoring, reactive systems

Funding This work is supported by the Reykjavik University Research Fund, the Doctoral Student Grant (No: 207055) and the MoVeMnt project (No: 217987) under the IRF, and the STARDUST project (No: EP/T014628/1) under the EPSRC.

**Acknowledgements** We thank our anonymous reviewers and the Artifact Evaluation Committee for their feedback. Thanks also to Simon Fowler, Simon J. Gay, and Phil Trinder for their input.

#### 1 Introduction

Modern software is generally built in terms of concurrent components that execute without relying on a global clock or shared state [90]. Instead, components interact via non-blocking messaging, creating a loosely-coupled architecture known as a *reactive system* [8, 97], which:

- responds in a timely manner (is *responsive*),

- remains available in the face of failure (is *resilient*),

- reacts to inputs from users or their environment (is message-driven), and

- **grows** and shrinks to accommodate varying computational loads (is *elastic*).

The real-world behaviour of reactive systems is hard to understand statically, and *monitoring* is used to inspect their operation at *runtime*, *e.g.* for debugging [114], security checking [63], profiling [79], resource usage analysis [37], *etc.* This paper considers runtime verification (RV),

#### 2 Runtime Instrumentation for Reactive Components (Extended Version)

an application of monitoring used to detect whether the *current* execution of a system under scrutiny (SuS) deviates from its correct behaviour [15, 74, 21]. A RV monitor is a *sequence* recogniser [130, 104]: a state machine that incrementally analyses a *finite* fragment of the runtime information exhibited by a SuS to reach an *irrevocable* verdict (see [6, 5] for details).

Instrumentation lies at the core of runtime monitoring [73, 21, 65]. It is the mechanism by which runtime information from a SuS is extracted and reported to monitors as a stream of system events called a trace. Software is typically instrumented in one of two ways. Inline instrumentation, or inlining, modifies the SuS by injecting tracing instructions at specific joinpoints, e.g. using AspectJ [93] or BCEL [54]. Outline instrumentation, or outlining, uses an external tracing infrastructure to gather events, e.g. LTTng [56] or OpenJ9 [59], thereby treating the SuS as a black box. A key requirement setting RV apart from monitoring, e.g., telemetry [88] or profiling [128, 26], is that the instrumentation must report sound traces.

- ightharpoonup Definition 1 (Sound traces). A finite trace T is sound w.r.t. a system component P iff it is

- 1. Complete. T contains all the events exhibited by P so far, and

- 2. Consistent. The event sequence in T reflects the order these occur locally at P.

Traces that violate this soundness invariant are unfit for RV, as omitted, spurious, or out-of-sequence events incorrectly characterise the system behaviour, *nullifying* the verdicts that monitors flag [21, 52]. Reactive software imposes another requirement: that the instrumentation *safeguards* the responsive, resilient, message-driven, and elastic attributes of the SuS. This necessitates an instrumentation method that is itself *reactive*, such that it:

- 1. does not hamper the SuS by inducing unfeasible runtime overhead (is responsive),

- 2. permits monitors to fail independently of SuS components (is resilient),

- 3. reacts to trace events without blocking the SuS (is message-driven), and

- 4. grows and shrinks in proportion to the size of the SuS (is elastic).

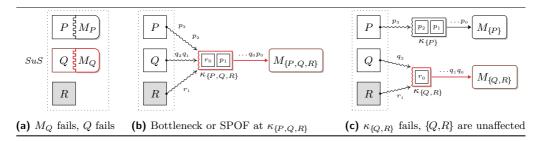

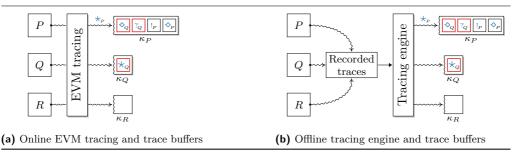

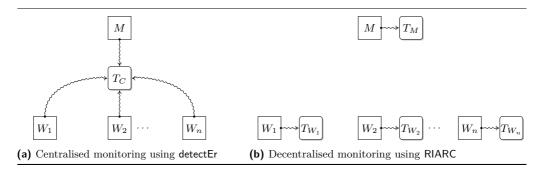

Limitations of current RV instrumentation methods State-of-the-art RV tools use instrumentation methods that do not satisfy all of the conditions 1-4 above. This renders them inapplicable to reactive software; see [65, Tables 3 and 4] for details. Many approaches, including [24, 31, 49, 78, 113, 129, 134, 17], assume systems with a fixed architecture where the number of components remains constant at runtime, failing to meet condition 4. Works foregoing the assumption of a fixed system size, such as [45, 94, 61, 60, 25, 31, 71, 3], inline the SuS with monitors statically. Inlining monitors pre-deployment inherently accommodates systems that grow and shrink (condition 4) as a by-product of the embedded monitor code that executes on the same thread of system components; see fig. 1a. This scheme, however, has shortcomings that make it less suited to reactive software. Recent studies [21, 52] observe that the lock-step execution of the SuS and monitors can impair the operation of the instrumented system, e.g. slow runtime analyses manifest as high latencies [38], and faulty monitors may break the system [72], which do not meet conditions 1 and 2 (e.g.  $M_Q$  in fig. 1a). Other works [46, 14] argue that errors, such as deadlocks or component crashes, are hard to detect since the monitoring logic shares the runtime thread of the affected component. Entwining the execution of the SuS and monitors may also diminish the scalability, performance, and resource usage efficiency of the monitored system because inlined monitor code cannot be run on separate threads [11]. Lastly, inlining is incompatible with unmodifiable software, such as closed-source components (e.g. R in figs. 1a-1c), making outlining the only alternative.

Outline instrumentation can address the limitations of inlining by isolating the SuS and its monitors (works [45, 38, 39] that view externalised monitors as 'outline' embed tracing code to extract events from the SuS, subjecting them to the cons of inlining). The

latest survey on decentralised RV [74, Tables 1 and 2] establishes that outlining-based tools, e.g. [50, 16, 17, 75, 38, 39, 132, 66], are variations on centralised instrumentation. In this set-up, events exhibited by SuS components are funnelled through a global trace buffer (e.g.  $\kappa_{\{P,Q,R\}}$  in fig. 1b) that a singleton monitor can analyse asynchronously, meeting condition 3. Yet, the central buffer introduces contention and sacrifices the scalability of the SuS [10], violating condition 4. Centralised architectures are prone to single point of failures (SPOFs) [97, 96] (violating condition 2), which is not ideal for monitoring medium-scale reactive systems.

**Contribution** We propose RIARC, a decentralised instrumentation algorithm for outline monitors that overcomes the above shortcomings, fulfilling conditions 1-4. Outline monitors minimise latency effects due to slow trace event analyses associated with inlining (meeting condition 1). While RIARC does not handle monitor failure explicitly, it intrinsically enjoys a modicum of partial failure by isolating the SuS and its decentralised monitor components (meeting condition 2); e.g. monitors  $M_{\{P\}}$  and  $M_{\{Q,R\}}$  in fig. 1c. RIARC uses a tracing infrastructure to obtain system events passively without modifying the SuS (meeting condition 3). The algorithm equips each isolated monitor with a local trace buffer, using it to report events based on the SuS components a monitor is tasked to analyse (e.g. buffers  $\kappa_{\{P\}}$  and  $\kappa_{\{Q,R\}}$  in fig. 1c). RIARC reorganises its instrumentation set-up to reflect dynamic changes in the SuS. It reacts to specific events in traces to instrument monitors for new SuS components and to remove redundant monitors when it detects graceful or abnormal component terminations. This enables RIARC to grow and shrink the verification set-up on demand (meeting condition 4). Given the challenges in fulfilling the conditions 1-4, we scope our work to settings where communication is reliable (i.e., no message corruption, duplication, and loss) [58] and Byzantine failures do not arise [99].

To the best of our knowledge, the approach RIARC advocates is novel. One reason why outlining has never been adopted for decentralising monitors are the onerous conditions 1–4 imposed by reactive software. Utilising non-invasive tracing makes our set-up necessarily asynchronous. At the same time, this complicates the instrumentation, which must ensure trace soundness (def. 1), notwithstanding the inherent phenomena arising from the concurrent execution of the SuS and monitors, e.g. trace event reordering and process crashes. Consequently, the second reason is that the overhead incurred to uphold this invariant—in addition to scaling the verification set-up as the SuS executes—is perceived as prohibitive when compared to inlining. This opinion is often reinforced when the viability of outline instrumentation is predicated on empirical criteria tied to monolithic, batch-style programs, that may not apply to reactive software (e.g. percentage slowdown); e.g. see [100, 117, 116, 47, 46, 124, 30, 101].

This paper shows how instrumenting outline monitors under conditions 1-4 can be achieved using a decentralised approach that guarantees def. 1, and with overheads considered feasible for typical soft real-time reactive systems. Concretely, we:

- (i) recall the benefits of the actor model of computation [85, 9] for building reactive systems and argue how our model of processes and tracers readily maps to that setting, sec. 2;

- (ii) give a decentralised instrumentation algorithm for outline monitors, detailing how the reactive characteristics of the SuS can be preserved whilst ensuring def. 1, sec. 3;

- (iii) show the implementability of our algorithm in an actor language and systematically validate the correctness of its corresponding implementation w.r.t. def. 1 by exhaustively inducing interleaved executions for a selection of instrumented systems, sec. 4;

- (iv) back up the feasibility of the implemented algorithm via a comprehensive empirical study that uses various workload configurations surpassing the state of the art, showing that the induced overhead minimally impacts the reactive attributes of the SuS, sec. 5.

#### 4 Runtime Instrumentation for Reactive Components (Extended Version)

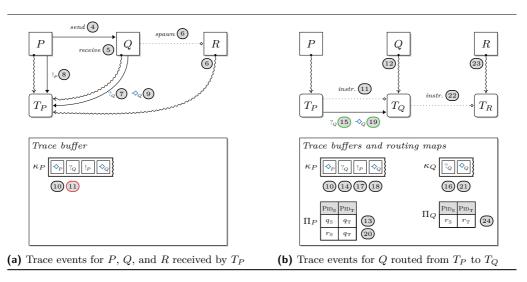

Figure 1 P,Q,R instrumented in inline (left), centralised (middle) and decentralised (right) modes

# 2 A computational model for reactive systems

The actor model [85, 9] emerged as the paradigm to design and build reactive systems [33]. Actors—the units of decomposition in this model—are abstractions of concurrent entities that share no mutable memory with other actors. Instead, actors interact through asynchronous message passing and alter their internal state based on the messages they consume. Asynchronous communication decouples actors spatially and temporally, which fully isolates system components and establishes the foundation for resiliency and elasticity [32, 97]. Each actor is equipped with an incoming message buffer called the mailbox, from which messages deposited by other actors can be selectively read. Besides sending and receiving messages, actors can spawn other actors. Actors in a system are addressable by their unique process identifier (PID), which they use to engage in directed, point-to-point communication. This idea of addressability is central to the actor model: it enables reasoning about decentralised computation, as the identity of components or messages can be propagated through a system and used in handling complex tasks, such as process registration and failure recovery [33]. As is often the case in decentralised computations, we assume that messages exchanged between pairs of processes are always received in the order in which they have been sent [43].

Frameworks, notably Erlang [11], Elixir [91], Akka [1] for Scala [120], along with others [123, 139], instantiate the actor model. We adopt Erlang since its ecosystem is specifically engineered for highly-concurrent, soft real-time reactive systems [140, 12, 44]. The Erlang virtual machine (EVM) implements actors as lightweight processes. It employs per process garbage collection that, unlike the JVM, does not subject the virtual machine to global unpredictable pauses [89, 119]. This factor minimises the impact on the soft real-time properties of a system and is also crucial to the empirical evaluation of sec. 5 since it stabilises the variance in our experiments. The EVM exposes a flexible process tracing API aimed at reactive software [42]. Erlang provides other components, e.g. supervision trees, message queues, etc., for building fault-tolerant distributed applications. While we scope our work to fault-free settings (see sec. 1), adopting Erlang gives us the foundation upon which our work can be naturally extended to address these aspects. Henceforth, we follow the established convention in Erlang literature and use the terms actor, process, and component synonymously.

#### 2.1 Process tracing and trace partitioning

Processes in a concurrent system form a *tree*, starting at the *root* process that spawns *child* processes, and so forth<sup>1</sup>. Concurrency induces inherent *partitions* to the execution of the

For example, using spawn() in Erlang [42] and Elixir [91], ActorContext.spawn() in Akka [1], Actor.createActor() in Thespian [123], CreateProcess() in Windows [111], etc.

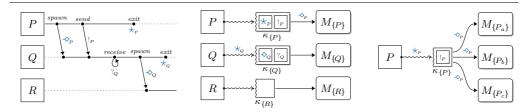

(a) Interaction flow of P, Q and R (b) Trace partitions of P, Q, and R (c) Event replicas to monitors

**Figure 2** SuS with processes P, Q, and R instrumented with independent monitors

SuS in the form of isolated traces that reflect the *local* behaviour at each process [17]. RIARC exploits this aspect to attain several benefits. First, one can *selectively* specify the SuS processes to be instrumented. The upshot is that fewer trace events need to be gathered, improving *efficiency*. Another benefit of partitioned traces is that each process can be dynamically instrumented, free from assumptions about the number of processes the SuS is expected to have. This makes the RV set-up *elastic*. Lastly, the instrumentation set-up can *partially fail*, as faulty SuS or monitor processes do not imperil the execution of one another.

▶ Example 2 (Trace partitions). Trace partitions enable RIARC to instrument a system in various arrangements. Fig. 2a depicts an interaction sequence for the execution of the SuS from sec. 1. In this interaction, the root process, P, spawns Q and communicates with it, at which point Q spawns process R; P and Q eventually terminate. We denote the process spawning and termination trace events by  $\Rightarrow$  and  $\star$ , and use! and? for send and receive events respectively. The sound trace partitions for the processes in fig. 2a are ' $\Rightarrow_P.!_P.\star_P$ ' for P, '? $_Q. \Rightarrow_Q. \star_Q$ ' for Q, and the empty trace for R.

A centralised set-up such as that of fig. 1b can be obtained by instrumenting  $\{P,Q,R\}$  with one monitor,  $M_{\{P,Q,R\}}$ , whereas instrumenting the components  $\{P\}$  and  $\{Q,R\}$  with monitors  $M_{\{P\}}$  and  $M_{\{Q,R\}}$  gives the decentralised arrangement of fig. 1c. Each of these instrumentation arrangements generates different executions.

- ▶ Example 3 (Sound traces). For the case of fig. 1b, RIARC can report to  $M_{\{P,Q,R\}}$  one of four possible traces ' $\rightsquigarrow_P.!_P. \star_P.?_Q. \star_Q. \star_Q$ ', ' $\rightsquigarrow_P.!_P.?_Q. \star_P. \star_P. \star_Q. \star_Q$ ', ' $\rightsquigarrow_P.!_P.?_Q. \star_Q. \star_Q$ ', ' $\rightsquigarrow_P.!_P.?_Q. \star_Q. \star_Q$ ', or ' $\rightsquigarrow_P.!_P.?_Q. \star_Q. \star_Q. \star_Q. \star_P$ .' These sound traces result from the interleaved execution of processes P, Q. Any other trace, e.g. ' $\rightsquigarrow_P. \star_P.?_Q. \rightsquigarrow_Q. \star_Q$ ' or ' $\rightsquigarrow_P.!_P. \star_P.?_Q. \star_Q. \star_Q$ ', is unsound since it contradicts the local behaviour at processes P and Q of fig. 2a. The former trace omits the request  $!_P$  that P makes to Q (it is incomplete w.r.t. P), and the latter trace inverts  $\rightsquigarrow_Q$  and  $\star_Q$ , suggesting that Q spawns R after Q terminates (it is inconsistent w.r.t. Q).

- ▶ Example 4 (Separate instrumentation). Fig. 2b shows another decentralised set-up, where P, Q, and R are instrumented separately. In this case, the instrumentation should report to  $M_{\{P\}}$ ,  $M_{\{Q\}}$  and  $M_{\{R\}}$  the events observed *locally* at each process, as stated in ex. 2.  $\blacktriangleleft$

RIARC makes two assumptions about process tracing in order to support the instrumentation arrangements shown in figs. 1b, 1c, and 2b:

- **A**<sub>1</sub> Tracing processes sets. Tracing can gather events for sets of SuS processes, e.g.  $\kappa_{\{P,Q,R\}}$  in fig. 1b gathers the events of  $\{P,Q,R\}$ , and  $\kappa_{\{Q,R\}}$  in fig. 1c gathers the events of  $\{Q,R\}$ .

- A<sub>2</sub> Tracing inheritance. Tracing gathers the events of a SuS process and the children it spawns by default to eliminate the risk that trace events from child processes are missed.

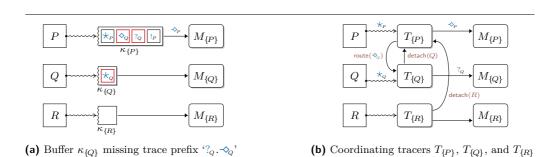

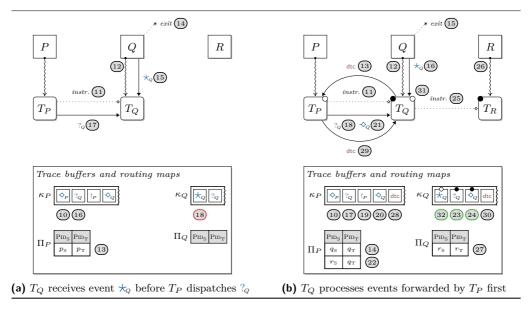

Figure 3 Choreographed tracers coordinating to ensure sound traces

We opt for tracing inheritance since it follows established centralised RV monitoring tools, including [16, 41, 50, 113]. In fact, tracing assumptions  $A_1$  and  $A_2$  mean that centralised set-ups like that of fig. 1b can be obtained just by tracing the root process P. Tracing inheritance requires the instrumentation to *intervene* if it needs to channel the events of a child process into a *new* trace partition that is *independent* from that of its parent, *e.g.* as in fig. 1c. In such cases, the instrumentation must first stop tracing the child process, allocate a fresh trace buffer, and resume tracing the child process. The out-of-sync execution of the SuS and instrumentation complicates the creation of these new trace partitions because it can lead to reordered or missed events. This, in turn, would violate trace soundness, def. 1.

We supplement  $A_1$  and  $A_2$  with the following to keep our exposition in sec. 3 manageable:

A<sub>3</sub> Single-process tracing. Any SuS process can be traced at most once at any point in time. A<sub>4</sub> Causally-ordered spawn events. Tracing gathers the spawn trace event of a parent process before all the events of the child process spawned by that parent, e.g. if P spawns Q, and Q receives, as in fig. 2a, the reported sequence is ' $\diamondsuit_P$ ? ? a rather than '? Q.  $\leadsto_P$ ?.

The constraint of tracing assumption  $A_3$  is easily overcome by replicating trace events for a process and reporting them to different monitors (e.g. the events in the trace partition of process P are replicated to monitors  $M_{\{P_a\}}$ ,  $M_{\{P_b\}}$ ,  $M_{\{P_c\}}$  in fig. 2c). Tracing assumption  $A_4$  requires trace buffers to reorder  $\Rightarrow$  events using the spawner and spawned process information carried by each event before reporting them to monitors. Sec. 3.3 gives more details.

▶ Example 5 (Unsound traces). Fig. 3a shows one possible configuration that can be reached by our three-process system introduced in fig. 2a, where the trace buffer  $\kappa_{\{P\}}$  contains the events for both P and Q. The trace in buffer  $\kappa_{\{Q\}}$  is unsound, as it inaccurately characterises the local behaviour of process Q (the sound trace for Q should be '? $_Q$ .  $\rightsquigarrow_Q$ .  $\rightsquigarrow_Q$ , not ' $\rightsquigarrow_Q$ ').  $\blacktriangleleft$

RIARC programs trace buffers to coordinate with one another to ensure that sound traces are invariably reported to monitors. We refer to a trace buffer and the coordination logic it encapsulates as a *tracer*. RIARC employs an approach based on *next-hop routing* in IP networks [83, 107] to counteract the effects of trace event reordering and loss by rearranging and forwarding events to different tracers. Fig. 3b conveys our organisation of tracers (refer to fig. 10 in app. A for legend). Sec. 3 details how RIARC dynamically reorganises the tracer choreography and performs next-hop routing.

### 2.2 Modelling decentralised instrumentation

Since RV monitors are passive verdict-flagging machines (refer to sec. 1), they are orthogonal to our instrumentation. We, thus, focus our narrative on tracers and omit monitors, except when relevant in the surrounding context. The model assumes a set of SuS process,  $P,Q,R \in PRC$ ,

and tracer names,  $T \in \text{Trc}$ , together with a countable set of PID values to reference processes. We distinguish between SuS and tracer PIDs, which we denote respectively by the sets,  $p_{\text{S}}, q_{\text{S}} \in \text{PID}_{\text{S}}$  and  $p_{\text{T}}, q_{\text{T}} \in \text{PID}_{\text{T}}$ . The variables  $i_{\text{S}}$  and  $i_{\text{T}}$  and  $i_{\text{T}}$  and  $i_{\text{T}}$  range over PIDs from the corresponding sets PIDs and PIDT. We also assume the function signature sets,  $f_{\text{S}} \in \text{SIG}_{\text{S}}$ ,  $f_{\text{T}} \in \text{SIG}_{\text{T}}$ , and,  $f_{\text{M}} \in \text{SIG}_{\text{M}}$ , to denote SuS, tracer, and RV monitor functions, together with the variables  $i_{\text{S}}$ ,  $i_{\text{T}}$ , and  $i_{\text{C}}$  that range over each signature set. New SuS processes are created via the function  $i_{\text{S}}$  that accepts the function signature  $i_{\text{S}}$  to be spawned, and returns a fresh PID,  $i_{\text{S}}$ . We overload spwn to spawn tracer signatures  $i_{\text{T}}$  equivalently, returning corresponding PIDs,  $i_{\text{T}}$ . The function self obtains the PID of the process invoking it. We write  $i_{\text{T}}$  as shorthand for a singleton process set  $i_{\text{T}}$  to simplify notation.

RIARC uses three message types,  $\tau \in \{\text{evt,dtc,rtd}\}\$ . These determine when to *create* or *terminate* tracer processes, and what trace events to *route* between tracers:

- evt are trace events gathered via process tracing,

- **dtc** are *detach* requests that tracers exchange to reorganise the tracer choreography, and

- **rtd** are *routing* packets that transport evt or dtc messages forwarded between tracers.

We encode messages m as tuples. Trace event messages,  $\langle \text{evt}, \ell, \imath_s, \jmath_s, \varsigma_s \rangle$ , comprise the event label  $\ell$  that ranges over the SuS events  $\Rightarrow$  (spawn),  $\star$  (exit), ! (send), and ? (receive). The PID value  $\imath_s$  identifies the SuS process exhibiting the trace event, and is defined for all events. The SuS PID  $\jmath_s$  and function signature  $\varsigma_s$  depend on the type of the event. Tbl. 1a catalogues the values defined for each event. We write trace events in their shorthand form, omitting undefined values (denoted by  $\bot$ ), e.g.  $\langle \text{evt}, \star, \imath_s \rangle$  instead of  $\langle \text{evt}, \star, \imath_s, \bot, \bot \rangle$ .

Detach request messages have the form  $\langle \mathsf{dtc}, \iota_\mathsf{T}, \iota_\mathsf{s} \rangle$ . A tracer with the PID  $\iota_\mathsf{T}$  uses  $\mathsf{dtc}$  to request that another tracer  $\mathsf{stop}$  tracing the SuS PID  $\iota_\mathsf{S}$ . Routing packet messages,  $\langle \mathsf{rtd}, \iota_\mathsf{T}, m \rangle$ , move  $\mathsf{evt}$  and  $\mathsf{dtc}$  messages between tracers. The PID  $\iota_\mathsf{T}$  identifies the tracer that embeds the message m into the routing packet and dispatches it to other tracers. Tbl. 1b summarises detach request and routing packet messages.

We reserve the variables e, d, and r for the messages types evt, dtc, and rtd respectively. Our model uses the suggestive dot notation (.) to index message fields, e.g.  $m.\tau$  reads the message type,  $e.\ell$  reads the trace event label, etc. (see tbl. 1). For simplicity, we occasionally write the label  $\ell$  in lieu of the full trace event form, e.g. we write  $\star$  instead of  $\langle \text{evt}, \star, \iota_s \rangle$ .

| Label $\ell$ | Index                                               | Description ( $i_S$ and $j_S$ are SuS PIDs)                          |

|--------------|-----------------------------------------------------|----------------------------------------------------------------------|

|              | $e.\imath_{	ext{	iny S}}$                           | Parent PID spawning new child PID $\jmath_{\rm s}$                   |

| <b>→</b>     | $e.\jmath_{	ext{	iny S}}$                           | Child PID spawned by parent PID $i_{\rm S}$                          |

|              | $e.arsigma_{	ext{	iny S}}$                          | Signature $\varsigma_{\rm S}$ spawned by parent PID $\imath_{\rm S}$ |

| *            | $e.\imath_{	ext{	iny S}}$                           | Terminated PID                                                       |

| ^            | $e.j_{	ext{	iny S}}, e.\zeta_{	ext{	iny S}}$        | Undefined for exit events                                            |

|              | $e.\imath_{	ext{	iny S}}$                           | Sending PID                                                          |

| !            | $e.\jmath_{	ext{	iny S}}$                           | Recipient PID                                                        |

|              | $e.\zeta_{	ext{S}}$                                 | Undefined for send events                                            |

| 2            | $e.\imath_{	ext{	iny S}}$                           | Recipient PID                                                        |

| ?            | $e.\jmath_{	ext{	iny S}}, e.arsigma_{	ext{	iny S}}$ | Undefined for receive events                                         |

| Index                     | Description                                                 |  |  |  |

|---------------------------|-------------------------------------------------------------|--|--|--|

| m.	au                     | Message type: event (evt) detach (dtc), routing (rtd)       |  |  |  |

| $d.\imath_{	ext{T}}$      | PID of tracer requesting detach of SuS PID $\imath_{\rm S}$ |  |  |  |

| $d.\imath_{	ext{	iny S}}$ | PID of SuS process to<br>stop tracing                       |  |  |  |

| $r.\imath_{	ext{	iny T}}$ | PID of tracer that starts routing message $m$               |  |  |  |

| r.m                       | Embedded evt or dtc<br>message being routed                 |  |  |  |

<sup>(</sup>a) Messages encoding spawn, exit, send, and receive events

(b) Detach and routing messages

**Table 1** Trace event (evt), detach request (dtc), and routing packet (rtd) message index names

#### 8 Runtime Instrumentation for Reactive Components (Extended Version)

| Requirement                                | Approach                                                    |  |  |  |

|--------------------------------------------|-------------------------------------------------------------|--|--|--|

| R <sub>1</sub> Growing the set-up          | Instrument tracers on-demand to create new trace partitions |  |  |  |

| $\mathbf{R_2}$ Ensuring complete traces    | Route trace events to deliver them to the correct tracer    |  |  |  |

| ${ m R}_{ m 3}$ Ensuring consistent traces | Prioritise routed trace events before others                |  |  |  |

| R <sub>4</sub> Isolating tracers           | Detach tracers from others once all trace events are routed |  |  |  |

| ${ m R}_{ m 5}$ Minimising overhead        | Target specific processes to instrument                     |  |  |  |

| $R_6$ Shrinking the set-up                 | Garbage collect redundant tracers and monitors              |  |  |  |

**Table 2** RIARC approach to ensure trace soundness (def. 1) and reactive instrumentation (sec. 1)

#### 3 Decentralised instrumentation

Our reason for encapsulating trace buffers and their coordination logic as tracers stems from the actor model. Trace buffers align with actor mailboxes, which localise the tracer state and enable tracers to run *independently*. The main logic replicated at each tracer is given in algs. 1-3. Tracers operate in two modes, *direct* ( $\circ$ ) and *priority* ( $\bullet$ ), to counteract the effects of trace event reordering. We organise our tracer logic in algs. 1 and 3 to reflect these modes, respectively. Algs. 1 and 3 use the function AnalyseEvt, tasked with analysing events; see app. C.5.2 for details. Auxiliary tracer logic referenced in this section is relegated to app. A.

Every tracer maintains an internal state  $\sigma$  consisting of the following three maps:

- $\blacksquare$  the routing map,  $\Pi$ , governing how events are routed to other tracers,

- $\blacksquare$  the instrumentation map,  $\Lambda$ , that determines which SuS processes to instrument, and

- $\blacksquare$  the traced-processes map, Γ, tracking the SuS process set that the tracer currently traces. Tbl. 2 summarises the challenges that RIARC needs to overcome to attain the reactive characteristics stated in sec. 1. Requirements R<sub>1</sub> and R<sub>6</sub> in tbl. 2 oblige the instrumentation to reorganise dynamically while the SuS executes to preserve its elasticity. Requirement R<sub>4</sub> offers a modicum of resiliency between the SuS and tracer processes, whereas R<sub>5</sub> minimises the instrumentation overhead by gathering only the events monitors require. This keeps the overall set-up responsive. Since RIARC builds on the actor model, it fulfils the message-driven requirement intrinsically. Trace soundness is safeguarded by requirements R<sub>2</sub> and R<sub>3</sub>.

The operations Trace, Clear and Preempt give access to the tracing infrastructure. Trace  $(i_s, i_T)$  enables a tracer with PID  $i_T$  to register its interest in receiving trace events of a SuS process with PID  $i_S$ . This operation can be undone using Clear  $(i_S, i_T)$ , which blocks the calling tracer  $i_T$  and returns once all the trace event messages for the SuS process  $i_S$  that are in transit to the tracer  $i_T$  have been delivered to  $i_T$ . It is worth remarking that this behaviour conforms to our proviso in sec. 1, i.e., no communication faults. Preempt $(i_S, i_T)$  combines Clear and Trace. It enables the tracer pre-empting  $i_T$  to take control of tracing the SuS process  $i_S$  from another tracer  $i_T'$  that is currently tracing  $i_S$ . Tracers use Clear or Preempt to modify the default process-tracing inheritance behaviour that tracing assumption  $A_2$  describes. We refer to alg. 5 for the specifics of these operations.

We focus our presentation in secs. 3.1-3.6 of how RIARC addresses the challenges listed in tbl. 2 on the set-up of fig. 2b, where the processes P, Q and R, are instrumented separately. This specific case highlights two aspects. First, it *emphasises* the complications that RIARC overcomes to establish the desired set-up while ensuring trace soundness, def. 1. Second, fig. 2b *covers all* other possible instrumentation set-ups. Disjoint sets of SuS processes, including the one shown in fig. 1c, can be obtained when tracers do not act on certain  $\rightarrow$

(spawn) events, as sec. 3.1 explains. Notably, any centralised set-up, e.g. the one in fig. 1b, emerges naturally when the root tracer disregards all  $\Rightarrow$  events exhibited by the SuS.

▶ Note 6 (Naming conventions). For clarity, we adopt the convention that a SuS process P is spawned from the signature  $f_{S_P}$  and is assigned the PID  $p_s$ . A tracer for P is named  $T_P$  (short for  $T_{\{P\}}$ ) and has the PID  $p_r$ . Other processes are treated likewise, e.g. the SuS process Q has signature  $f_{S_Q}$ , PID  $q_s$ , while the tracer  $T_Q$  for Q has PID  $q_r$ , etc.

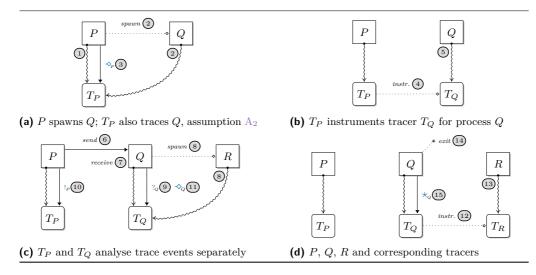

#### 3.1 Growing the set-up

Fig. 4 illustrates how the hierarchical creation sequence of SuS processes described in sec. 2.1 is exploited to instrument separate tracers. RIARC programs tracers to react to ⋄ (spawn) events in the trace. In fig. 4a, the root tracer  $T_P$  traces process P, step 1. When P spawns process Q, Q automatically inherits  $T_P$  (tracing assumption  $A_2$  from sec. 2.1). Steps ② in fig. 4a emphasise that tracing inheritance is instantaneous. The event  $e = \langle \text{evt}, \diamond, p_s, q_s, f_{so} \rangle$ is generated by P when it spawns its child Q, step 3 in fig. 4a. The PID values of the parent and child processes carried by e, namely  $p_{\rm S}$  and  $q_{\rm S}$ , are accessed via the indexes e.1s and e.3s respectively (see tbl. 1a). Tracer  $T_P$  uses this PID information to instrument a new tracer  $T_Q$  for process Q in step 4 of fig. 4b. By invoking PREEMPT $(q_s, q_T)$ ,  $T_Q$  takes over tracing process Q from the former tracer  $T_P$  going forward.  $T_Q$  creates a new trace partition for process Q that is independent of the partition of P, step 5. Meanwhile,  $T_P$  receives the send event  $\langle \text{evt}, !, p_s, q_s \rangle$  in step 10 after P messages Q in step 6 of fig. 4c. Subsequent  $\Rightarrow$  events that  $T_P$  or  $T_Q$  may gather are handled as described in steps 3-5. Figs. 4c and 4d show how the final tracer  $T_R$  is instrumented in step 2 after Q spawns R in step 8. As before,  $T_Q$  traces R automatically in step  $\otimes$ .  $T_Q$  receives the event  $\langle \text{evt}, \diamond, q_s, r_s, f_{s_R} \rangle$  generated by Q in step  $\blacksquare$ .  $T_R$  invokes PREEMPT $(r_s, r_T)$  to create the trace partition for R in step  $\blacksquare$ .

#### 3.2 Ensuring complete traces

The asynchrony between the SuS and tracer processes can induce the interleaved execution shown in fig. 5, as an alternative execution to that shown in figs. 4b-4d. In fig. 5a,  $T_P$  is slow

**Figure 4** Growing the tracer instrumentation set-up for processes *P*, *Q* and *R* (monitors omitted)

Figure 5 Next-hop trace event routing using tracer routing maps Π (monitors omitted)

to handle  $\rightsquigarrow_P$  it receives in 3 of fig. 4a and fails to instrument  $T_Q$  promptly. Consequently, the events  $?_Q$  and  $\rightsquigarrow_Q$  that Q exhibits are sent to  $T_P$  in steps 7 and 9 of fig. 5a. Step 1 shows the case where  $\langle \text{evt},?,q_T \rangle$  is processed by  $T_P$ , rather than by the *intended* tracer  $T_Q$  that would have been instrumented by  $T_P$ . This error breaches the *completeness* property of trace soundness w.r.t. Q, as the events  $?_Q$  and  $\rightsquigarrow_Q$  meant for Q reach the wrong tracer  $T_P$ .

To address this issue, RIARC uses a next-hop routing approach, where tracers retain the events they should handle and forward the rest to neighbouring tracers. We use the term dispatch tracer (dispatcher for short) to describe a tracer that receives trace events meant to be handled by another tracer. For instance,  $T_P$  in fig. 5a becomes the dispatch tracer for Q when it receives the events  $?_Q$  and  $\multimap_Q$  exhibited by Q, steps g and g. We expect these events to be handled by  $T_Q$  once it is instrumented. Dispatchers are tasked with embedding trace event (evt) or detach requests (dtc) into routing packet messages (rtd) and transmitting them to the next known hop. In fig. 5b,  $T_P$  dispatches the events  $?_Q$  and  $\rightsquigarrow_Q$  as follows. It first instruments  $T_Q$  with Q in step g. Next,  $T_P$  prepares  $\langle \text{evt}, ?, r_s \rangle$  and  $\langle \text{evt}, \rightsquigarrow_Q , r_s, f_{s_R} \rangle$  for transmission by embedding each in rtd messages (steps g and g).  $T_P$  forwards the resulting routing packets,  $\langle \text{rtd}, \langle \text{evt}, ?, r_s \rangle \rangle$  and  $\langle \text{rtd}, \langle \text{evt}, \rightsquigarrow_Q , r_s, f_{s_R} \rangle \rangle$ , to its next-hop neighbour  $T_Q$  in steps g and g. The trace event  $\langle \text{evt}, !, p_s, q_s \rangle$ , however, is not forwarded but handled by  $T_P$ , as step g shows. Concurrently,  $T_Q$  acts on the forwarded events  $?_Q$  and  $\rightsquigarrow_Q$  in steps g and g and instruments  $T_R$  as a result, step g.

Tracers determine the events to retain or forward using the routing map,  $\Pi: \operatorname{PID}_S \rightharpoonup \operatorname{PID}_T$ . Every tracer queries its private routing map for each message it receives on SuS PID  $m.i_s$ . A tracer forwards a message to its neighbouring tracer with PID  $i_T$  if a next-hop for that message exists, *i.e.*,  $\Pi(m.i_s) = i_T$ . When the next-hop is undefined, *i.e.*,  $\Pi(m.i_s) = \bot$ , m is handled by the tracer. Handlepwn, Handlexit and HandleComm in alg. 1 implement this forwarding logic on lines 14, 23 and 31.

Dynamically populating the routing map is key to transmitting messages between tracers. A tracer adds the new mapping  $e.\jmath_{\mathbb{S}} \mapsto \jmath_{\mathbb{T}}$  to its routing map  $\Pi$  in case 1 or 2 below whenever it processes spawn trace events  $e = \langle \text{evt}, \rightsquigarrow, \imath_{\mathbb{S}}, \jmath_{\mathbb{S}}, \varsigma_{\mathbb{S}} \rangle$ . One of two cases is considered for  $e.\imath_{\mathbb{S}}$ :

1.  $\Pi(\imath_{\mathbb{S}}) = \bot$ . The next-hop for e is undefined, which cues the tracer to instrument the SuS process with PID  $\jmath_{\mathbb{S}}$ . When applicable, the tracer processes the event and instruments a

Algorithm 1 Logic handling ∘ trace events, detach request dispatching, and forwarding

```

\overline{\operatorname{def} \operatorname{Loop}_{\circ}(\sigma, \zeta_{\mathrm{M}})}

35 def DISPATCHDTC(\sigma.d)

forever do

match \sigma.\Pi(d.i_s) do

m \leftarrow next message from trace buffer \kappa

case \perp: fail dtc next-hop must be defined

match m.\tau do

case \eta_T:

case evt: \sigma \leftarrow \text{HANDLEVENT}_{\circ}(\sigma, \varsigma_{\text{M}}, m)

DISPATCH(d, j_{\text{T}})

case dtc: \sigma \leftarrow \text{DISPATCHDTC}(\sigma, \varsigma_{\text{M}}, m)

# Next-hop for d.i_s no longer needed

\sigma. \Pi \leftarrow \sigma. \Pi \setminus \{\langle d.\imath_{\scriptscriptstyle S}, \jmath_{\scriptscriptstyle T} \rangle\}

case rtd: \sigma \leftarrow \text{FORWDRTD}_{\circ}(\sigma, \varsigma_{\text{M}}, m)

TryGC(\sigma)

41

8 def Handlevto(\sigma, \zeta_{\text{M}}, e)

return \sigma

42

match e.\ell do

43 def FORWDRTD_{\circ}(\sigma,r)

case ❖: return HandlSpwn<sub>o</sub>(\sigma, \varsigma_{\text{M}}, e)

m \leftarrow r.m \# Read \ embedded \ message \ in \ r

case \star: return Handlexito(\sigma, \varsigma_{\rm M}, e)

11

match m.\tau do

case !,?: return HANDLCOMM_{\circ}(\sigma, \varsigma_{\text{M}}, e)

12

case dtc: return FORWDDTC(\sigma,r)

13 def HANDLSPWN<sub>\circ</sub>(\sigma,\varsigma_{\rm M},e)

case evt: return FORWDEVT(\sigma,r)

47

match \sigma.\Pi(e.i_s) do

14

48 def FORWDDTC(\sigma,r)

case \perp: # No next-hop for e.i<sub>s</sub>; handle e

15

d \leftarrow r.m

49

AnalyseEvt(\varsigma_{\rm M}, e) # App. C.5.2

16

match \sigma.\Pi(d.i_s) do

50

\sigma \leftarrow \text{Instrument}_{\circ}(\sigma, e, \text{self}())

17

\mathbf{case} \perp : \mathbf{fail} \ \mathit{dtc} \ \mathit{next-hop} \ \mathit{must} \ \mathit{be} \ \mathit{defined}

51

case j_T: # Next-hop for e.i_S exists via j_T

18

case j_T:

Dispatch(e, j_T)

FORWD(r, j_T)

\# Set next-hop of e.j_s to tracer of e.i_s

# Next-hop for d.i_s no longer needed

\sigma.\Pi \leftarrow \sigma.\Pi \cup \{\langle e.j_s, j_T \rangle\}

20

\sigma. \prod \leftarrow \sigma. \prod \setminus \{\langle d.\imath_{\mathrm{S}}, \jmath_{\mathrm{T}} \rangle\}

54

return \sigma

21

TryGC(\sigma)

55

def Handlexito(\sigma, \varsigma_{\text{M}}, e)

return \sigma

match \sigma.\Pi(e.i_s) do

57 def FORWDEVT(\sigma,r)

case \perp: # No next-hop for e.i<sub>s</sub>; handle e

24

e \leftarrow r.m

58

AnalyseEvt(\varsigma_{\rm M}, e) # App. C.5.2

25

match \sigma.\Pi(e.i_s) do

59

\sigma.\Gamma \leftarrow \sigma.\Gamma \setminus \{\langle e.i_s, \circ \rangle\}

26

case \perp: fail evt next-hop must be defined

60

TryGC(\sigma)

27

case \eta_T:

61

case j_{\text{T}}: DISPATCH(e, j_{\text{T}})

FORWD(r, j_T)

return \sigma

29

# For spawn events, tracer also sets a

def HandlComm<sub>o</sub>(\sigma, \varsigma_{\text{M}}, e)

# new next-hop for e.js

# Next-hop of e.j<sub>s</sub> to same tracer of e.i<sub>s</sub>

match \sigma.\Pi(e.i_s) do

if (e.\ell = \Rightarrow)

case \perp: AnalyseEvt(\varsigma_{\text{M}},e) # App. C.5.2

63

\sigma.\Pi \leftarrow \sigma.\Pi \cup \{\langle e.j_s, j_T \rangle\}

64

case j_{\text{T}}: DISPATCH(e, j_{\text{T}})

33

return \sigma

return \sigma

34

```

separate tracer with PID  $j_T$ . It then adds the mapping  $e.j_S \mapsto j_T$  to  $\Pi$ . The tracer leaves  $\Pi$  unmodified and handles the event itself if a separate tracer is not required. Opting for a separate tracer is determined by the instrumentation map  $\Lambda$ , as discussed in sec. 3.5.

2.  $\Pi(\imath_s) = \jmath_T$ . The next-hop for e is defined, and the tracer forwards the event to the neighbouring tracer  $\jmath_T$ . The tracer also records a new next-hop by adding  $e.\jmath_s \mapsto \jmath_T$  to  $\Pi$ . The addition of  $e.\jmath_s \mapsto \jmath_T$  in cases 1 and 2 ensures that future events originating from  $\jmath_s$  can always be forwarded via a next-hop to a neighbouring tracer  $\jmath_T$  (see invariants on lines 37, 51, and 60). Fig. 5b shows the routing maps of the tracers  $T_P$  and  $T_Q$ .  $T_P$  adds  $q_s \mapsto q_T$  in step 1 after processing  $\langle \text{evt}, \diamondsuit, p_s, q_s, f_{s_Q} \rangle$  from its trace buffer in 10.  $T_P$  then instruments Q with the tracer  $T_Q$  in step 11; an instance of case 1. The function Instrument in alg. 2 details this on line 4, where the mapping  $e.\jmath_s \mapsto \jmath_T$  is added to  $\Pi$  following the creation of

■ Algorithm 2 Tracer instrumentation operations for direct (o) and priority (•) modes

```

Expect: e = \langle \text{evt}, \rightsquigarrow, i_S, j_S, \varsigma_S \rangle

Expect: e = \langle \text{evt}, \leadsto, i_S, j_S, \varsigma_S \rangle

1 def Instrument<sub>o</sub>(\sigma, e, i_{\rm T})

8 def Instrument \bullet(\sigma, e, i_{\text{T}})

if ((\varsigma_{\text{M}} \leftarrow \sigma.\Lambda(e.\varsigma_{\text{S}})) \neq \bot)

if ((\varsigma_{\text{M}} \leftarrow \sigma.\Lambda(e.\varsigma_{\text{S}})) \neq \bot)

# New tracer j_T for new SuS process e.j_S

# New tracer \gamma_T for new SuS process e.\gamma_S

j_{\text{T}} \leftarrow \text{spwn}(\text{Tracer}(\sigma, \zeta_{\text{M}}, e.j_{\text{S}}, i_{\text{T}}))

j_{\text{T}} \leftarrow \text{spwn}(\text{Tracer}(\sigma, \zeta_{\text{M}}, e.j_{\text{S}}, i_{\text{T}}))

\sigma.\Pi \leftarrow \sigma.\Pi \cup \{\langle e.\jmath_{\scriptscriptstyle S}, \jmath_{\scriptscriptstyle T} \rangle\}

\sigma.\Pi \leftarrow \sigma.\Pi \cup \{\langle e.\jmath_{\scriptscriptstyle S}, \jmath_{\scriptscriptstyle T} \rangle\}

11

else

#In \circ mode, this tracer has detached

# In • mode, this tracer must detach

# all processes from its dispatcher i_T

\# SuS \ process \ e.j_s \ from \ its \ dispatcher \ \imath_{\scriptscriptstyle T}

# This tracer traces new SuS process e.js

Detach(e. j_S, i_T)

# This tracer traces new SuS process e.j_s

# by tracing inheritance assumption A_2

\sigma.\Gamma \leftarrow \sigma.\Gamma \cup \{\langle e.\jmath_s, \bullet \rangle\}

\sigma.\Gamma \leftarrow \sigma.\Gamma \cup \{\langle e.j_s, \circ \rangle\}

return \sigma

return \sigma

```

tracer  $j_T$ , line 3. Step 20 of fig. 5b is an instance of case 2. Here,  $T_P$  adds  $r_S \mapsto q_T$  to  $\Pi_P$ after processing  $\langle \text{evt}, \multimap, q_s, r_s, f_{S_R} \rangle$  for R in step 18 since  $\Pi_P(q_s) = q_T$ . Crucially,  $T_P$  does not instrument a new tracer, but delegates the task to  $T_Q$  by forwarding  $\triangleleft_Q$ . Lines 20 and 64 in alg. 1 (and later line 24 in alg. 3) are manifestations of this, where the mapping  $e.j_s \mapsto j_T$  is added after the  $\Rightarrow$  event e is forwarded to the next-hop  $f_T$ .  $T_Q$  instruments the SuS process R in step 22 with  $T_R$ , which has the PID  $r_{\scriptscriptstyle T}$ . It then adds the mapping  $r_{\scriptscriptstyle S}\mapsto r_{\scriptscriptstyle T}$  to  $\Pi_Q$  in step  $\mathfrak{P}_{\mathfrak{S}}$ , as no next-hop is defined for  $q_{\mathfrak{S}}$ , i.e.,  $\Pi_{Q}(q_{\mathfrak{S}}) = \bot$ . Henceforth, any events exhibited by R and received at  $T_P$  can be dispatched by the latter tracer through  $T_Q$  to  $T_R$ .

We note that every tracer is only aware of its neighbouring tracers. This means messages may pass through multiple tracers before reaching their intended destination. Next-hop routing keeps the logic inside RIARC straightforward since tracers forward messages based solely on local information in their routing map. Such an approach makes the instrumentation set-up readily adaptable to dynamic changes in the SuS, is easier to scale, and has been shown to induce lower latency when compared to general routing strategies [83, 107]. The DAG of interconnected tracers induced by next-hop routing ensures that every message is eventually delivered to the correct tracer if a path exists or is handled by the tracer otherwise. Fig. 5b illustrates this concept, where the next-hop mappings inside  $\Pi_P$  point to  $T_O$ , and the mappings in  $\Pi_O$  point to  $T_R$  in turn. Consequently, any events that R exhibits and that  $T_P$ receives are forwarded twice to reach the target tracer  $T_R$ : from tracer  $T_P$  to  $T_Q$ , and from  $T_O$  to  $T_R$ . RIARC relies on the operations DISPATCH and FORWD to accomplish next-hop routing (see alg. 4 in app. A). DISPATCH creates a routing packet  $\langle i_s, m \rangle$  and embeds the trace event or detach message m to be routed. Alg. 1 shows how routing packets are handled by tracers. For instance, FORWDEVT extracts the embedded message from the routing packet on line 58 and queries the routing map to determine the next-hop, line 59. If it does, the packet is forwarded, as FORWD $(r, \gamma_T)$  on line 62 indicates. Crucially, the **fail** invariant on line 60 asserts that the next-hop for a routing packet is always defined. The cases for DISPATCHDTC and FORWDDTC in alg. 1 are analogous.

#### 3.3 **Ensuring consistent traces**

Next-hop routing alone does not guarantee trace consistency, i.e., that the order of events in the trace reflects the one in which these occur locally at SuS processes, def. 1. Trace event reordering arises when a tracer gathers events of a SuS process (we call these direct events) and simultaneously receives routed events concerning said process from other tracers. Fig. 6a gives another interleaving to the one of fig. 5b to underscore the deleterious effect such a race condition provokes when events are reordered at  $T_Q$ . In step 12  $T_Q$  takes over  $T_P$  to continue tracing process Q.  $T_Q$  collects the event  $\bigstar_Q$  in step 15, which happens before  $T_Q$  receives the routed event  $?_Q$  concerning Q in step 17 of fig. 6a. If  $T_Q$  processes events from its trace buffer  $\kappa_Q$  in sequence, as in step 18, it violates trace consistency w.r.t. Q (the correct trace ordering should be  $?_Q.\bigstar_Q.\bigstar_Q$ ). Naïvely handling  $\bigstar$  before ? erroneously reflects that Q receives messages after it terminates.

RIARC tracers resolve this issue by prioritising the processing of routed trace events using selective message reception [42]. In doing so, tracers encode the invariant that 'routed events temporally precede all others that are gathered directly by the tracer'. RIARC tracers operate in one of two modes, priority  $(\bullet)$  and direct  $(\circ)$ , which adequately distinguishes past (i.e., routed) and current (i.e., direct) events from the perspective of the tracer receiving them.

Fig. 6b illustrates this concept. It shows that when in priority mode,  $T_Q$  dequeues the routed events  $?_Q$  and  $\multimap_Q$  labelled by  $\bullet$  first. The event  $?_Q$  is handled in step 23, whereas  $\multimap_Q$  results in the instrumentation of tracer  $T_R$  in step 25 of fig. 6b. Meanwhile,  $T_Q$  can still receive events directly from Q while priority events are being handled. Yet, direct trace events from Q are considered only after  $T_Q$  transitions to direct mode. Newly-instrumented tracers default to  $\bullet$  mode to implement the described logic; see line 14 in alg. 4 of app. A.

LOOP. in alg. 3 shows the logic prioritising routed events, which are dequeued on line 3 and handled on line 6. HANDLSPWN, HANDLEXIT, and HANDLCOMM in LOOP. and LOOP. handle events differently. A tracer in direct mode performs one of three actions (see alg. 1):

- 1. it analyses events for RV purposes via the function ANALYSEEVT( $\varsigma_{\rm M}, e$ ), e.g. line 32,

- 2. it dispatches events that it directly gathers using DISPATCH $(e, j_T)$ , when events ought to be handled by other tracers, e.g. line 33, or

- 3. it forwards routed events to the next-hop through FORWD $(r, j_T)$ , e.g. line 62. Tracers in priority mode exclusively handle routed messages as points 1 and 3 describe, e.g. lines 38 and 39 in alg. 3. However, no event dispatching is performed.

Figure 6 Trace event reordering using priority (●) and direct (○) tracer modes (monitors omitted)

■ Algorithm 3 Logic handling • trace events, detach request acknowledgements, and forwarding

```

\overline{\mathbf{def}} \operatorname{Loop}_{\bullet}(\sigma, \varsigma_{\mathrm{M}})

def Handlexit(\sigma, \zeta_{\rm M}, r)

forever do

e \leftarrow r.m

2

r \leftarrow \text{next rtd} message from trace buffer \kappa

match \sigma.\Pi(e.i_s) do

28

m \leftarrow r.m \# Read \ embedded \ message \ in \ r

case \perp: # No next-hop for e.i<sub>s</sub>; handle e

29

match m.\tau do

AnalyseEvt(\varsigma_{\rm M}, e) # App. C.5.2

30

case evt: \sigma \leftarrow \text{HANDLEVT}_{\bullet}(\sigma, \varsigma_{\text{M}}, r)

\sigma.\Gamma \leftarrow \sigma.\Gamma \setminus \{\langle e.i_s, \bullet \rangle\}

31

TryGC(\sigma)

case dtc:

32

# dtc ack relayed from dispatch tracer

case j_{\text{T}}: Forwd(r, j_{\text{T}})

\sigma \leftarrow \text{HANDLDTC}(\sigma, \varsigma_{\text{M}}, r)

return \sigma

34

9 def HANDLEVT<sub>•</sub>(\sigma, \zeta_{\rm M}, r)

35 def HANDLCOMM_{\bullet}(\sigma, \zeta_{\text{M}}, r)

e \leftarrow r.m

e \leftarrow r.m

match e.\ell do

match \sigma.\Pi(e.i_s) do

case \rightarrow: return HANDLSPWN_{\bullet}(\sigma, \zeta_{\text{M}}, r)

case \perp: AnalyseEvt(\varsigma_{\text{M}},e) # App. C.5.2

case \star: return Handlexit_{\bullet}(\sigma, \varsigma_{\text{M}}, r)

case j_{\text{T}}: FORWD(r, j_{\text{T}})

13

39

case !,?: return HandlComm_{\bullet}(\sigma, \varsigma_{\text{M}}, r)

return \sigma

14

40

41 def HANDLDTC(\sigma, \zeta_{\text{M}}, r)

15 def HANDLSPWN_{\bullet}(\sigma, \varsigma_{\rm M}, r)

d \leftarrow r.m

e \leftarrow r.m

42

16

match \sigma.\Pi(d.\jmath_s) do

match \sigma.\Pi(e.i_s) do

43

17

\mathbf{case} \perp :

case \perp: # No next-hop for e.is; handle e

44

18

assert d.\imath_{\text{T}} = \text{self}() unexpected dtc ack

45

19

AnalyseEvt(\varsigma_{\rm M}, e) # App. C.5.2

\sigma.\Gamma \leftarrow (\sigma.\Gamma \setminus \{\langle d.\jmath_{S}, \bullet \rangle\}) \cup \{\langle d.\jmath_{S}, \circ \rangle\}

i_T \leftarrow r.i_T \# Read PID of dispatch tracer

46

20

if (\{\langle i_s, \gamma \rangle \mid \langle i_s, \gamma \rangle \in \sigma. \Gamma, \gamma = \bullet\} = \emptyset)

47

\sigma \leftarrow \text{Instrument}_{\bullet}(\sigma, e, i_{\text{T}})

Loop_{\circ}(\sigma, \varsigma_{M}) \# Put \ tracer \ in \circ \ mode

case j_T: # Next-hop for e.i_S exists via j_T

22

49

FORWD(r, \eta_T)

23

assert d.i_T \neq self() dtc meant for i_T

# Set next-hop of e.j_s to tracer of e.i_s

50

FORWD(r, j_{\mathrm{T}})

\sigma.\Pi \leftarrow \sigma.\Pi \cup \{\langle e.j_s, j_T \rangle\}

51

24

return \sigma

52

return \sigma

```

#### 3.4 Isolating tracers

A tracer in priority mode coordinates with the dispatch tracer of a particular SuS process it traces. This enables the tracer to determine when all of the events of that process have been routed to it by the dispatch tracer. The negotiation is effected using dtc, which the tracer sends to the relevant dispatch tracer. Each tracer records the set of processes it traces in the traced-processes map,  $\Gamma: \operatorname{PID}_S \to \{\circ, \bullet\}$ . A SuS process mapping is added to  $\Gamma$  when a tracer starts gathering trace events for that process and removed once the process terminates. Lines 6 and 14 in alg. 2 add fresh mappings to  $\Gamma$ ; lines 26 in alg. 1 and 31 in alg. 3 purge mappings from  $\Gamma$ . A tracer in priority mode must issue a dtc request for each process it tracks in  $\Gamma$  before it can transition to direct mode and start operating on the trace events it gathers directly. The detach request,  $d = \langle dtc, i_T, i_S \rangle$ , contains the PIDs of the issuing tracer and the SuS process to be detached from the dispatch tracer. Once the tracer receives an acknowledgement to the dtc request for the SuS PID  $d.i_s$  from the dispatch tracer, it updates the corresponding entry  $d.\imath_s \mapsto \bullet$  in  $\Gamma$ , marking it as detached,  $d.\imath_s \mapsto \circ$ . Alg. 3 shows this logic on line 46. A tracer transitions from priority to direct mode once all the processes in its  $\Gamma$  map are marked detached; line 47 in alg. 3 performs this check. Once in direct mode, tracers are isolated from others in the choreography.

Fig. 6b depicts the tracer  $T_Q$  in priority mode sending the detach request  $\langle \mathsf{dtc}, q_{\scriptscriptstyle \mathrm{T}}, q_{\scriptscriptstyle \mathrm{S}} \rangle$  for SuS PID  $q_{\scriptscriptstyle \mathrm{S}}$  to the dispatch tracer. This happens in step  $\mathfrak{T}_Q$  after  $T_Q$  starts tracing Q

directly in step ②. Alg. 2 effects this transaction with the dispatch tracer by the operation DETACH on line 13; see app. A for definition of DETACH. The dtc request issued by  $T_Q$  is deposited in the trace buffer of the dispatch tracer  $T_P$  after the events  $?_Q$  and  $\rightsquigarrow_Q$ .  $T_P$  processes the messages in its buffer sequentially in ①, ①, ①, ② and ②, and forwards  $?_Q$  and  $\rightsquigarrow_Q$  to  $T_Q$ , steps ③ and ②]. Crucially,  $T_P$  acknowledges the dtc request issued by  $T_Q$ :  $T_P$  dispatches dtc back to tracer  $T_Q$ , as step ② indicates.  $T_Q$  first handles the events  $?_Q$  and  $\rightsquigarrow_Q$  (tagged with • in fig. 6b) in steps ② and ②4. Lastly,  $T_Q$  handles dtc in ③ and marks process Q as detached from its dispatch tracer  $T_P$ . The update on the traced-process map  $\Gamma$  is performed by Handlet on line 46 in alg. 3. Tracer  $T_Q$  in fig. 6b transitions to direct mode in step ③, when the only process Q that it traces is detached.  $T_Q$  resumes handling  $\star_Q$  in step ③2, which is consistent w.r.t. the events exhibited locally at Q, i.e.,  $`?_Q . \star_Q . \star_Q . \star_Q .$

An acknowledgement to a detach request sent from a dispatch tracer,  $\langle \mathsf{dtc}, \iota_{\mathsf{T}}, \iota_{\mathsf{s}} \rangle$ , is generally propagated through multiple next-hops before it reaches the tracer with PID  $\iota_{\mathsf{T}}$  issuing the request. Since a dtc request informs the dispatch tracer that  $\iota_{\mathsf{T}}$  is gathering trace events for the SuS PID  $\iota_{\mathsf{S}}$  directly, the next-hop entries in the routing maps of tracers on the DAG path from the dispatch tracer to  $\iota_{\mathsf{T}}$  are stale. Each tracer on this DAG path purges the next-hop entry for the SuS PID  $\iota_{\mathsf{S}}$  in  $\Gamma$  once it forwards dtc to the neighbouring tracer. DISPATCHDTC and FORWDDTC in alg. 1 perform this clean-up. Fig. 6b does not illustrate the latter clean-up flow, which we summarise next. After receiving dtc, the dispatch tracer  $T_P$  removes from  $\Pi_P$  the next-hop mapping  $q_{\mathsf{S}} \mapsto q_{\mathsf{T}}$  and calls DISPATCHDTC to acknowledge the detach request  $\langle \mathsf{dtc}, q_{\mathsf{T}}, q_{\mathsf{S}} \rangle$  it receives from  $T_Q$ . Similarly,  $T_P$  removes  $r_{\mathsf{S}} \mapsto q_{\mathsf{T}}$  once it acknowledges the detach request  $\langle \mathsf{dtc}, r_{\mathsf{T}}, r_{\mathsf{S}} \rangle$  sent from  $T_R$ . Once  $T_Q$  receives the routing packet  $\langle \mathsf{rtd}, p_{\mathsf{T}}, \langle \mathsf{dtc}, r_{\mathsf{T}}, r_{\mathsf{S}} \rangle \rangle$  that embeds the detach acknowledgement  $T_P$  sends, it removes the next-hop mapping  $r_{\mathsf{S}} \mapsto r_{\mathsf{T}}$  from  $\Pi_Q$ .  $T_Q$  then forwards this dtc acknowledgement to  $T_R$ .

RIARC ensures that all routing packets carrying dtc acknowledgements terminate at the tracers that issued these dtc requests. This requires *one* of two tracer conditions to hold:

- 1. either the tracer cannot forward the  ${\sf dtc}$  acknowledgement to a next-hop, meaning that the tracer sent the  ${\sf dtc}$  request, or

- 2. the tracer can forward the dtc acknowledgement via a next-hop, in which case the tracer did not issue the dtc request.

Alg. 3 enforces this invariant on lines 44 and 45 for case 1, and on lines 49 and 50 for case 2.

#### 3.5 Minimising overhead

Instrumenting specific processes—in contrast to fully instrumenting the SuS—reduces the volume of gathered trace events and helps lower the runtime overhead induced. RIARC uses the instrumentation map,  $\Lambda: SIG_S \rightarrow SIG_M$ , to this end.  $\Lambda$  specifies the SuS function signatures to instrument and the corresponding RV monitor signatures tasked with the analysis via ANALYSEEVT. RIARC utilises the signature  $e.\varsigma_s$  carried by spawn events  $e=\langle \text{evt}, \diamondsuit, \imath_s, \jmath_s, \varsigma_s \rangle$  to determine whether the SuS process spawning  $e.\varsigma_s$  requires a separate tracer. The INSTRUMENT operations in alg. 2 perform this check against  $\Lambda$  (lines 2 and 9). If a separate tracer is not required,  $e.\jmath_s$  is instrumented using the tracer of its parent process,  $e.\imath_s$ ; see tracing assumptions  $A_1$  and  $A_2$ . This logic caters for all the set-ups shown in figs. 1b, 1c, and 2b.

#### 3.6 Shrinking the set-up

RIARC remains elastic by discarding unneeded tracers. Tracers in direct and priority mode purge SuS PID references from the traced-process map when handling  $\star$  trace events. HANDLEXIT<sub>o</sub> and HANDLEXIT<sub>o</sub> implement this logic in algs. 1 and 3 on lines 26 and 31.

#### 16 Runtime Instrumentation for Reactive Components (Extended Version)

Tracer termination does *not* occur when the tracer has no processes left to trace, *i.e.*, when  $\Gamma = \emptyset$ , since the tracer may be required to forward trace events to neighbouring tracers. Instead, tracers perform a garbage collection check each time a mapping from  $\Gamma$  or  $\Pi$  is removed. A tracer terminates when  $\Gamma = \Pi = \emptyset$ , indicating that it has no SuS processes left to trace or any next-hop forwarding to perform. TRYGC used on lines 27, 41, and 55 in alg. 1, as well as on line 32 in alg. 3 encapsulates this check. Note that garbage collection never prematurely disrupts the RV analysis that tracers conduct, as invocations to ANALYSEEVT always precede TRYGC checks in our logic of algs. 1 and 3.

#### 4 Correctness validation

We assess the validity of RIARC in two stages. First, we confirm its implementability by instantiating the core logic of algs. 1-3 to Erlang. Our implementation targets two RV scenarios: online and offline monitoring [65, 21]. Second, we subject the implementation to a series of systematic tests using a selection of instrumentation set-ups. These tests exhaustively emulate the interleaved execution of the SuS and tracer processes by generating all the *valid* permutations of events in a set of traces. This exercises the tracer choreography invariants mentioned in sec. 3, confirming the integrity of the tracer DAG topology under each interleaving. We also use specialised RV monitor signatures in ANALYSEEVT to assert the soundness (def. 1) of trace event sequences analysed by tracers; see algs. 1 and 3 in sec. 3.

#### 4.1 Implementability

Our implementation of RIARC maps the tracer processes from sec. 3 to Erlang actors<sup>2</sup>. The routing ( $\Pi$ ), instrumentation ( $\Lambda$ ), and traced-processes ( $\Gamma$ ) maps constituting the tracer state  $\sigma$  are realised as Erlang maps for efficient access. Trace event buffers  $\kappa$  coincide with actor mailboxes, while the remaining logic in algs. 1–3 translates directly to Erlang code. This one-to-one mapping gives us confidence that our implementation reflects the algorithm logic.

In online RV, monitors analyse trace events while the SuS executes, whereas the offline setting defers this analysis until the system terminates. Fig. 11 in app. B.1 captures the distinction in process tracing between online and offline instrumentation in our setting (showing trace buffers only). The online instrumentation set-up (fig. 11a) employs the tracing infrastructure offered by the EVM, which deposits SuS trace event messages in tracer mailboxes. Erlang tracing complies with tracing assumption  $A_1$ , enabling RIARC to instrument disjoint SuS processes sets. We configure the EVM with the set\_on\_spawn flag so that spawned processes automatically inherit the same tracer as their parent [42]. This tracer assignment is atomic, meeting tracing assumption  $A_2$ . We also use the proces, send, and receive tracing flags, which constrain the events emitted by the EVM to  $\diamondsuit$ ,  $\bigstar$ , !, and  $\bigstar$ . The EVM enforces single-process tracing, i.e., tracing assumption  $A_3$ , and guarantees that  $\diamondsuit$  events of descendant processes are causally-ordered [137], i.e., tracing assumption  $A_4$ .

The offline counterpart differs only in its tracing layer, where events are read as recorded runs of the SuS. Recorded runs can be obtained externally, e.g. using DTrace [37] or LTTng [56], making it possible to monitor systems that execute outside of the EVM. Our bespoke offline tracing engine of fig. 11b fulfils tracing assumptions  $A_1 - A_4$ . This is crucial since it permits the same implementation of RIARC to be used in online and offline settings. Sec. 4.2 leverages this aspect to validate RIARC exhaustively using trace permutations.

<sup>&</sup>lt;sup>2</sup> The artefact may be found at https://doi.org/10.5281/zenodo.10634182.

We develop two versions of the Trace, Clear, and Preempt functions of alg. 5 to standardise the tracing API for online and offline use. The overloads for online use give access to the EVM tracing via the Erlang built-in primitive trace [42]. The second set of overloads wraps around our offline tracing engine to replay files containing specifically-formatted trace events. Offline tracing relaxes tracing assumption  $A_4$ , as recorded runs do not generally and recover the causal ordering per tracing assumption  $A_4$ . TRACE( $i_s, i_T$ ) registers a tracer  $i_{\rm T}$  with the offline tracing engine, which maintains an event buffer for  $i_{\rm T}$ , together with a set of SuS PIDs that  $i_T$  traces. A tracer can use TRACE with multiple SuS PIDs to register to obtain events for a set of processes, i.e., tracing assumption  $A_1$ . The tracing engine accumulates the events it reads from file in each tracer buffer and delivers events to the corresponding tracer mailbox once the casual ordering between → events of descendant SuS processes is established. Our offline tracing engine implements tracing inheritance (tracing assumption A<sub>2</sub>) and enforces single-process tracing (tracing assumption A<sub>3</sub>). Ex. 7 in app. B.1 sketches how the tracing engine uses its internal tracer buffers to deliver events to tracers.

#### 4.2 Correctness

Conventional testing does not guarantee the absence of concurrency errors due to the different interleaved executions that may be possible [108]. While subjecting the system under test to high loads raises the likelyhood of obtaining more coverage, this still depends on external factors, such as scheduling, which dictate the executions induced in practice. Controlling the conditions for concurrency testing requires a systematic exploration of all the interleaved executions [77]. In fact, it is not the size of the testing load that matters, but the choice of interleaved executions that exhaust the space of possible system states [13]. Concuerror [48] is a tool for systematic Erlang code testing. Unfortunately, we could not use Concuerror to test our RIARC implementation, as we were unable to integrate it with Erlang tracing.

We, nevertheless, adopt the systematic scheme advocated by Concuerror. Our approach uses the offline tracing tool described in sec. 4.1 to induce specific interleaved sequences for instrumentation set-ups, such as those of figs. 1b, 1c, and 2a. We obtain these sequences by taking all the sound (def. 1) event permutations of traces produced by the SuS. These sequences are then replayed by the offline tracing engine to systematically induce interleaving sequences in the SuS. Our final RIARC implementation embeds additional invariants besides the ones mentioned in sec. 3, e.g. the assert and fail statements in algs. 1 and 3. Readers are referred to app. B.2 for the full list. We ascertain trace soundness for each SuS interleaving that is emulated. This is accomplished via the function ANALYSEEVT, which we preload with monitors that assert the event sequence expected at each tracer. We also use identical tests in our empirical evaluation of sec. 5 under high loads. It is worth mentioning that while we systematically drive the execution of the SuS, we do not control the execution of tracers. Yet, we indirectly induce various dynamic tracer arrangements in the monitor DAG topology under the different groupings of SuS process sets that tracers instrument. For example, we fully instrument system depicted in fig. 2a in all its configurations, e.g.  $C_1 = [T_{\{P\}} \leadsto$  $\{P\}, T_{\{Q\}} \leadsto \{Q\}, T_{\{R\}} \leadsto \{R\}\}, C_2 = [T_{\{P,Q\}} \leadsto \{P,Q\}, T_{\{R\}} \leadsto \{R\}], \ldots, C_5 = [T_{\{P,Q,R\}} \leadsto \{P,Q,R\}],$ as well as instrument it partially, e.g.  $C_6 = [T_{\{P\}} \leadsto \{P\}], C_7 = [T_{\{P,Q\}} \leadsto \{P,Q\}], etc.$  Each of these configurations, when individually paired with every fabricated interleaved execution of the SuS, indicate that our RIARC implementation and corresponding logic of sec. 3 is correct.

#### 5 Empirical evaluation

We assess the feasibility of our RIARC implementation, confirming it safeguards the responsive, resilient, message-driven, and elastic attributes of the SuS. Sec. 4 targets a small selection of instrumentation set-ups to induce interleaved execution sequences and validate correctness exhaustively. We now employ stress testing [112] to investigate how RIARC performs in terms of the runtime overhead it exhibits. Our study focusses on online monitoring, as its overhead requirement is far more stringent than offline monitoring [64, 65, 21, 74]. We evaluate RIARC against inline instrumentation since the latter is regarded as the most efficient instrumentation technique [63, 62, 21]. This comparison establishes a solid basis for our results to be generalised reliably. We also compare RIARC to centralised instrumentation to confirm that the latter approach does not scale under typical loads.

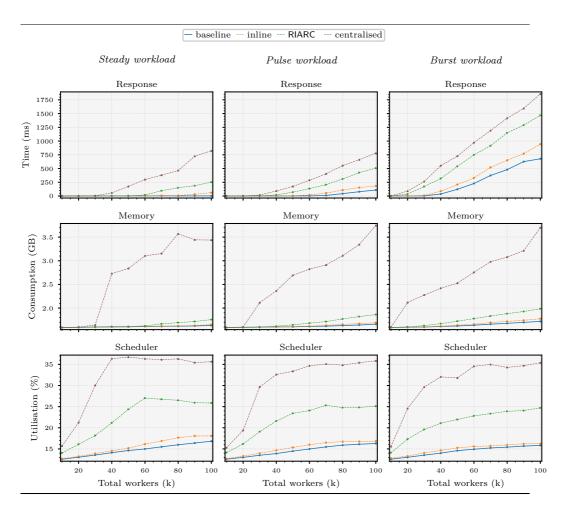

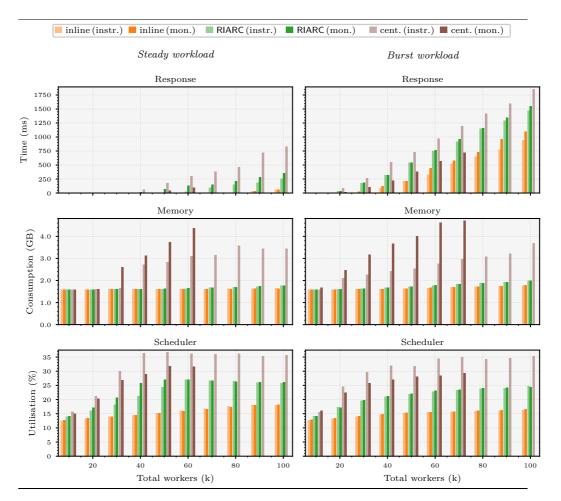

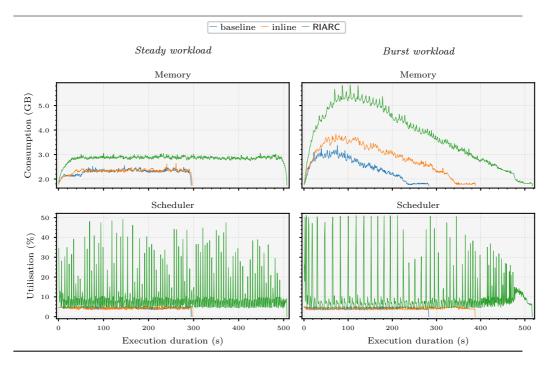

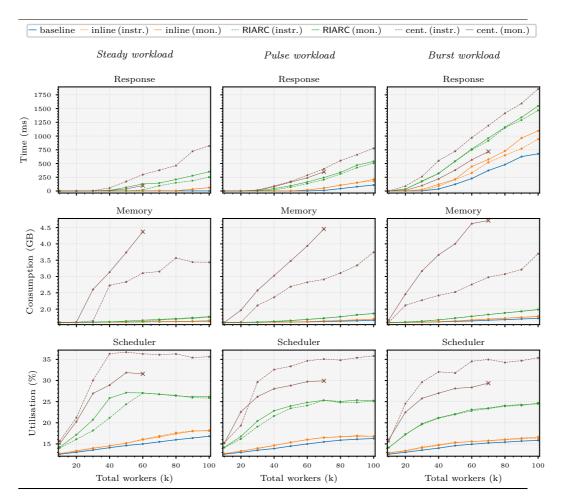

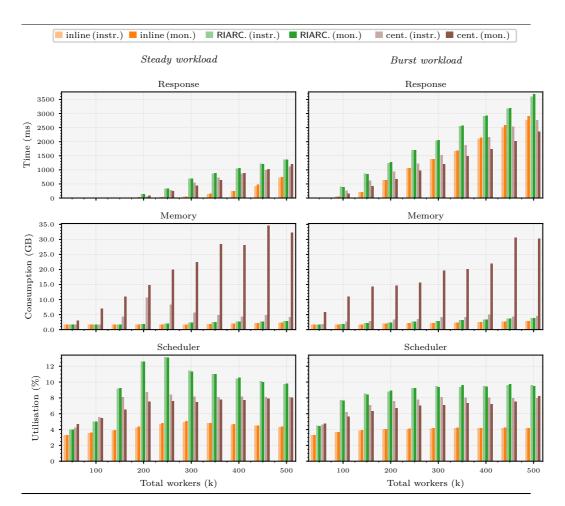

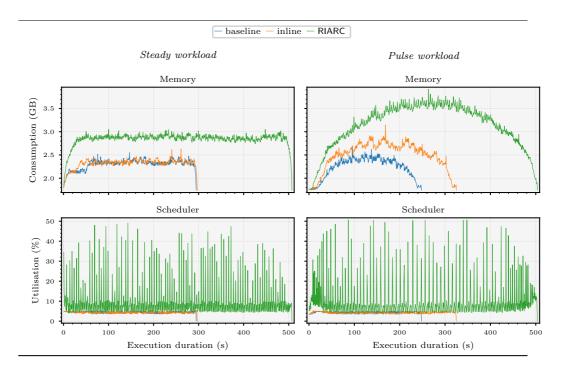

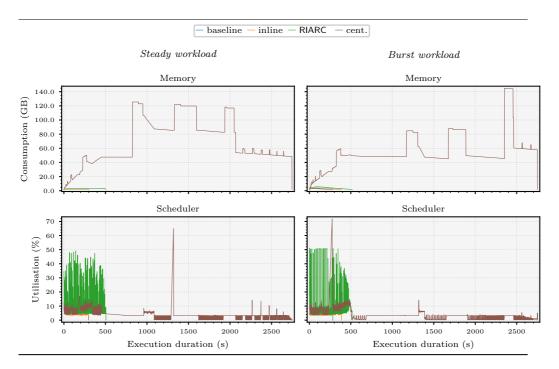

Our experiments are extensive. We use two hardware platforms to model edge-case scenarios based on limited hardware and general-case scenarios using commodity hardware. The evaluation subjects inline, centralised, and RIARC instrumentation to high loads that go beyond the state of the art and use realistic workload profiles. We gauge overhead under three performance metrics, the response time, memory consumption, and scheduler utilisation, which are crucial for reactive systems [7, 112]. Our results confirm that the overhead RIARC induces is adequate for applications such as soft real-time systems [42, 97], where the latency requirement is typically in the order of seconds [95]. We also show that RIARC yields overhead comparable to inlining in settings exhibiting moderate concurrency.

#### 5.1 Benchmarking tool

Benchmarking is standard practice for gauging runtime overhead in software [103, 80, 36]. Frameworks, including DaCapo [28] and Savina [87], offer limited concurrency, making them inapplicable to our case; see App. C.1 for detailed reasons. Industry-proven synthetic load testing benchmarking tools cater to reactive systems, e.g. Apache JMeter [70], Tsung [118], and Basho Bench [23]. Their general-purpose design, however, necessarily treats systems as a black box by gathering metrics externally, which may impact measurement precision [7]. Moreover, these load testers generate standard workloads, e.g. Poisson processes [82, 105, 92], but lack others, e.g. load bursts, that replicate typical operation or induce edge-case stress.

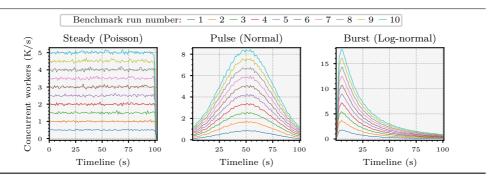

We adopt BenchCRV [7], another synthetic load tester specific to RV benchmarking for reactive systems. It sets itself apart from the tools above because it does not require external software (e.g., a web server) to drive tests. Instead, BenchCRV produces different models that closely emulate real-world software behaviour. These models are based on the master-worker paradigm [127]: a pervasive architecture in distributed (e.g. Big Data frameworks, render farms) and concurrent systems [138, 76, 55, 141]. Like Tsung and Basho Bench, BenchCRV exploits the lightweight EVM process model to generate highly-concurrent workloads.

BenchCRV creates master-worker models and induces workloads derived from configurable parameters. In these models, the master process spawns a series of workers and allocates tasks. The volume of workers per benchmark run is set via the parameter n. Each worker task consists of a batch of requests that the worker receives, processes, and echoes back to the master process. The amount of requests batched in one task is given by the parameter w. Workers terminate when all of their allotted tasks are processed and acknowledged by the master. BenchCRV creates workers based on  $workload\ profiles$ . A profile dictates how the master spreads its creation of workers along the loading timeline, t, given in seconds. BenchCRV supports three workload profiles based on ones typical in practice (e.g. see fig. 13): Steady models the SuS under stable workload (Poisson process).

Pulse models the SuS under gradually rising and falling workload (Normal distribution).

Burst models the SuS under stress due to workload spikes (Log-normal distribution).

The tool records three performance metrics to give a multi-faceted view of system overhead:

Mean response time in milliseconds (ms), gauging monitoring latency effects on the SuS.

Mean memory consumption in GB, gauging monitoring memory pressure on the SuS.

Mean scheduler utilisation as a percentage of the total processing capacity, showing how monitors maximise the scheduler use.

The prevalent use of the master-worker paradigm, the veracity with which BenchCRV models systems, the range of realistic workload profiles, and the choice of runtime metrics it gathers make this tool ideal for our experiments. Readers are referred to app. C.2 and [7] for details.

#### 5.2 Benchmark configuration

The BenchCRV master-worker models we generate take the role of the SuS in our experiments. We consider *edge-case* and *general-case* hardware platform set-ups for the following reasons:

- P<sub>E</sub> Edge-case captures platforms with *limited* hardware. It uses an Intel Core i7 M620 64-bit CPU with 8GB of memory, running Ubuntu 18.04 LTS and Erlang/OTP 22.2.1.

- $P_G$  General-case captures platforms with *commodity* hardware. It uses an Intel Core i9 9880H 64-bit CPU with 16GB of memory, running macOS 12.3.1 and Erlang/OTP 25.0.3. The EVMs on platforms  $P_E$  and  $P_G$  are set with 4 and 16 scheduling threads, respectively. These scheduler settings coincide with the processors available on each SMP [11] platform. We also use the  $P_E$  and  $P_G$  platforms with two concurrency scenarios for reactive systems:

- **C<sub>H</sub> High concurrency scenarios** perform short-lived tasks, *e.g.* web apps that fulfil thousands of HTTP client requests by fetching static content or executing back-end commands.

- **C**<sub>M</sub> **Moderate concurrency scenarios** engage in long-running, computationally-intensive tasks, *e.g.* Big Data stream processing frameworks.

Our benchmark workloads match the hardware capacity afforded by  $P_E$  and  $P_G$ :

- High concurrency benchmarks on  $P_E$  set n=100k workers and w=100 work requests per worker. These generate  $\approx (n\times w \text{ requests}\times w \text{ responses}) = 20M \text{ message exchanges}$  between the master and worker processes, totalling  $\approx (20M\times!\text{ events}\times?\text{ events}) = 40M$  analysable trace events. Platform  $P_G$  sets n=500k workers batched with w=100 requests to produce  $\approx 100M$  messages and  $\approx 200M$  trace events. The high concurrency model  $C_H$  is studied in sec. 5.4.

- Moderate concurrency benchmarks on  $P_G$  set n=5k workers and w=10k work requests per worker. These settings yield roughly the same number of trace events as on  $P_G$  with concurrency scenario  $C_H$ . The moderate concurrency model  $C_M$  is studied in sec. 5.5.

All experiments in secs. 5.4 and 5.5 use a total loading time of t=100s. Each experiment consists of ten benchmarks that apply Steady, Pulse, and Burst workloads. We repeat every experiment three times to obtain negligible variability and ensure the accuracy of our results; see app. C.4 for a summary of these workloads and app. C.5 for the precautions we take.

The hardware, OS, and Erlang versions of platforms  $P_E$  and  $P_G$ , combined with the workloads of concurrency scenarios  $C_H$  and  $C_M$  provide generality to our conclusions.

#### 5.3 Instrumentation configuration

One challenge in conducting our experiments is the lack of RV monitoring tools targeting the EVM. To the best of our knowledge [65, Tables 3 and 4], detectEr [75, 16, 17, 15, 73, 40]

is the only RV tool for Erlang that implements centralised outline instrumentation<sup>3</sup>. We are unaware of inline RV tools besides [39] and [3, 4]. Since the former tool is unavailable, we use the latter, more recent work<sup>4</sup>. In our experiments, we instrument the master and each worker process in the SuS models generated from sec. 5.2 to exert the highest possible load and capture worst-case scenarios. BenchCRV annotates work requests and responses with a unique sequence number to account for each message in benchmark runs. We leverage this numbering to write specialised monitor replicas that ascertain the soundness of trace event sequences reported to every RV monitor linked with the master and workers; see app. C.5 for details. Equally crucial, this runtime checking introduces a degree of realistic RV analysis slowdown that is uniform across all monitors in the inline, centralised, and RIARC monitoring set-ups. We empirically estimate this slowdown at  $\approx 5 \, \mu s$  per analysed event.

#### 5.4 High concurrency benchmarks

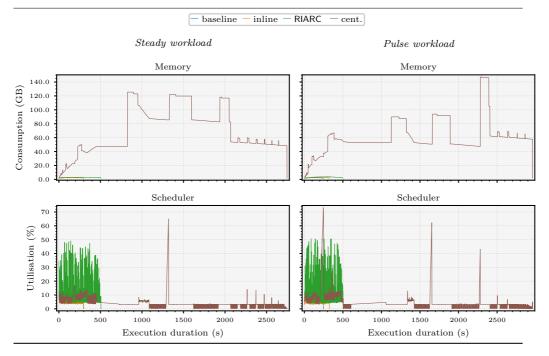

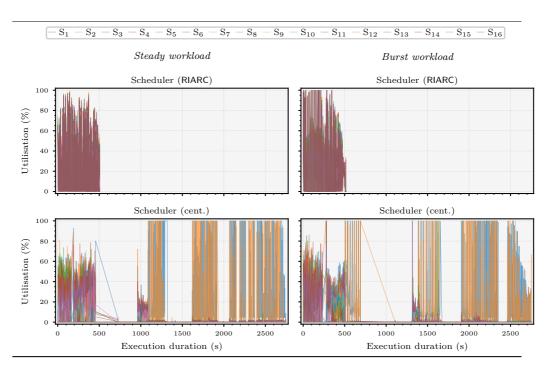

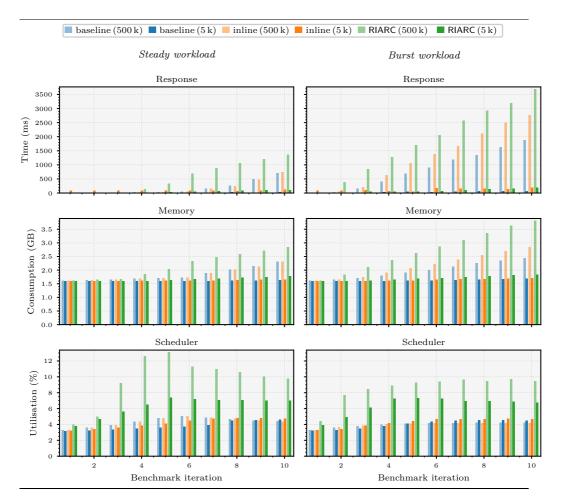

We study runtime overhead in the high concurrency scenario  $C_H$  with two aims. First, we show the effect overhead has on the SuS as it executes. Specifically, we consider how the memory consumption and scheduler utilisation impact the *latency* a client of the SuS experiences, *e.g.* end-user or application. We use the edge-case platform  $P_E$  for these experiments; analogous results obtained on  $P_G$  are detailed in app. C. Our second goal targets the general-case platform  $P_G$  to assess the *scalability* of the instrumentation methods through their optimal use of the *additional* memory and scheduler capacity afforded by  $P_G$ .