# **GRAPH - An readout ASIC for large MCP based detectors**

A. Seljak $^a$   $^e$   $^*$ , J. Vallerga $^b$ , G. Liu $^d$   $^f$ , R. Raffanti $^c$ , G. S. Varner $^f$

```

<sup>a</sup>Jozef Stefan Institute,

```

2575 Sand Hill Rd, Mailstop 0094, Menlo Park, California 94025, USA

Via Sommarive 18, 38123 Povo, Italy

E-mail: Andrej.Seljak@ijs.si

# ABSTRACT:

We present a programmable 16 channel, mixed signal, low power readout ASIC, having the project historically named Gigasample Recorder of Analog waveforms from a PHotodetector (GRAPH). It is designed to read large aperture single photon imaging detectors using micro channel plates for charge multiplication, and measuring the detector's response on crossed strips anodes to extrapolate the incoming photon position.

Each channel consists of a fast, low power and low noise charge sensitive amplifier, which provides a myriad of coarse and fine programmable options for gain and shaping settings. Further, the amplified signal is recorded using, to our knowledge novel, the Hybrid Universal sampLing Architecture (HULA), a mixed signal double buffer memory, that enables concurrent waveform recording, and selected event digitized data extraction. The sampling frequency is freely adjustable between few kHz up to 125 MHz, while the chip's internal digital memory holds a history 2048 samples for each channel, with a digital headroom of 12 bits.

An optimized region of interest sample-read algorithm allows to extract the information just around the event pulse peak, while selecting the next event, thus substantially reducing the operational dead time. The chip is designed in 130 nm TSMC CMOS technology, and its power consumption is around 47 mW per channel.

Jamova 39, 1000 Ljubljana, Slovenia

<sup>&</sup>lt;sup>b</sup>Space Sciences Laboratory, University of California,

<sup>7</sup> Gauss Way, Berkeley, CA 94720, USA

<sup>&</sup>lt;sup>c</sup>Techne Instruments,

<sup>4920</sup> Telegraph Ave, Unit. G, Oakland, CA 94609, USA

<sup>&</sup>lt;sup>d</sup>SLAC National Accelerator Laboratory,

<sup>&</sup>lt;sup>e</sup>Former - Fondazione Bruno Kessler - FBK,

<sup>&</sup>lt;sup>f</sup>Former - University of Hawai'i at Manoa, Department of Physics and Astronomy,

<sup>2505</sup> Correa rd., Honolulu, HI 96822, USA

<sup>‡</sup>Deceased

KEYWORDS: Instrumentation; Analog electronic circuits; Waveform sampling; Switched capacitor array; Mixed signal IC; Digital memory Front-end electronics for detector readout; Photon detectors (MCP, photomultipliers, HPDs); .

<sup>\*</sup>Corresponding author.

<sup>†,</sup>

## **Contents**

| 1. | Introduction            |                                   | 1  |

|----|-------------------------|-----------------------------------|----|

| 2. | GR                      | APH ASIC                          | 3  |

|    | 2.1                     | Architecture overview             | 3  |

|    | 2.2                     | Sampling windows and memory array | 4  |

|    | 2.3                     | Timebase generation circuit       | 5  |

|    | 2.4                     | Conversion controller             | 5  |

|    | 2.5                     | HULA operation                    | 6  |

|    | 2.6                     | Data readout                      | 7  |

|    | 2.7                     | Trigger section                   | 8  |

| 3. | Results                 |                                   | 9  |

| 4. | Summary and future work |                                   | 11 |

| 5. | Ack                     | 12                                |    |

|    |                         |                                   |    |

This paper is dedicated to the memory of Prof. Dr. Gary S. Varner. He will be missed, his legacy cherished.

# 1. Introduction

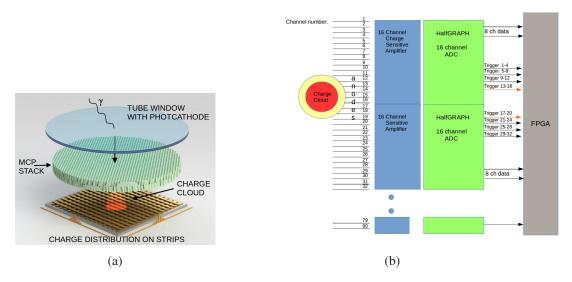

High resolution single photon imaging detectors aimed at operation in low photon flux, are sought after for future space missions such as HabEX, CETUS and LUOVIR to name a few examples, and more generally regarded for Ring Imaging Cherenkov Detectors for high energy physics experiments. The here presented example of a single photon sensitive detectors uses a photo-cathode for quantum conversion into photo-electrons. In a sealed (tubed) detector version[1], the photo-cathode would be usually deposited on the quartz entrance window of the enclosure, while for detectors that operate in free space, where vacuum is not an issue, and the entrance window is not needed, the Micro Channel Plate (MCP) itself can be coated with a photo-cathode of choice (Fig. 1a). Relying on chevron stacked MCPs for signal amplification to detectable levels, provides for long exposures having very low background noise on the images, compared to solid state counterparts. Furthermore, considering the recent MCP technological advancements, very large size and long lasting imaging detectors can be obtained.

In principle, when a high voltage is applied to the MCP, it creates an electric field that accelerates the quantum converted primary photo-electron along the micro pore, and at each collision on the walls, the multiplication effect takes place. The amount of charge exiting the MCP, namely

the signal, is related to the number of collisions induced by the primary photo electron inside the stacked MCP plate. Since the multiplication avalanche doesn't always begin at the same spot inside the micro pore, for a single photon the amount of charge may vary notably. Generally one can expect charge clouds containing 160 *femto* Coulombs of charge, or the equivalent of about 1M electrons (e<sup>-</sup>) per detected photon.

The charge cloud exiting the MCP is absorbed by an anode plane composed of an orthogonal array of 25  $\mu$ m strips (PXS), having a pitch of 625  $\mu$ m (Fig. 1a), each being connected to a readout channel. By measuring the lateral charge distribution, the impinging photon entrance position can be calculated from the center of mass of the charge cloud [2], [3]. The main desired detector specifications for future UV astronomy applications are to have a large aperture (10x10cm), have the pixel resolution of 20  $\mu$ m, being radiation hard, and most importantly, operate at very low power.

Previous cross strip MCP detectors that achieved sub 20 um FWHM spatial resolution had electronics that were bulky and power hungry with dedicated fast ADCs per channel. High power and bulky electronics are exactly what one wants to avoid in space based UV detectors where mass and power are a limited resource.

Our endeavor, to rise the Technology Readiness Level (TRL) of the detector's readout system from 4 to 6, lead us to initially design amplifiers and analog to digital converters separately using two different technologies. These chips were the CSAv3 (130 nm) [4], a 16 channel programmable amplifier, and the HalfGRAPH (250 nm)[5], a 16 channel giga sample per second waveform sampling and digitization ASIC. Both chips were used to construct a low power detector readout system [6] (Fig. 1b), which confirmed the proof of concept, reaching pixel resolution on the order of 30  $\mu$ m and power consumption of 0.5W/cm<sup>2</sup>, or dozen watts reading an area of 25 cm<sup>2</sup> [7]

Figure 1: (a) Schematic view of a detector using an MCP stack and XS anode readout. (b) Scalable readout system concept using event localized triggering ability [[5],[6].]

Considering scaling the detector to very large formats, the PXS approach works favorably in terms of power consumption[7]. By duplicating the amount of readout channels, hence duplicating the power consumption, the sensitive area quadruples. While the CSAv3 complied with the

requirements, the HalfGRAPH architecture could be further optimized. Therefore, we decided to integrate the 16 channel CSAv3 amplifiers along with a novel dedicated ADC structure into a single GRAPH ASIC in 130 nm [8].

In view toward space grade environmental specifications, aside the radiation hardness which are mission driven, and not specifically addressed here. The most concerning is the power consumption, as heat being very difficult to dissipate, and the system's signal to noise ratio capable to bring the desired pixel resolution smaller than 20 um FWHM. at low MCP bias voltages. Our previous work brought us to the conclusion, that the following parameters should be met in view of designing a new ASIC, and is summarized in table ??.

| Input channels              | 16                                                  |  |

|-----------------------------|-----------------------------------------------------|--|

| Input dynamic range         | 0 - 50 fC (300ke <sup>-</sup> )                     |  |

| Target detector capacitance | 5 <i>p</i> F                                        |  |

| Amplifier gain              | > 10 mV/fC                                          |  |

| Shaping time                | rise/fall time 30 ns, pulse contained within 100 ns |  |

| ENC                         | $<= 1000 \mathrm{e^-}$ at 5 pF detector capacitance |  |

| Sampling frequency          | > 100 <i>M</i> Hz                                   |  |

| ADC resolution              | 12-bit, system S/N in the order of 50 dB            |  |

| Event readout rate          | 1 Mevent/s/ASIC (1 event = 48 samples)              |  |

| Power consumption           | < 50 mW / channel                                   |  |

Table 1: General overview of system requirements

Space missions differ and in the technology selection there is no generic solution, but the choice falls on matching trade offs on many levels, to fit mission's purpose. In this respect, we note that there are at least two groups working on a similar endeavor. An implementation using a pixelated pattern, opposed to PXS, was under study using the Timepix [9], with an updated version with the Timepix4 ASIC [10], [11]. The other group uses the Beetle ASIC [12] to accomplish a similar endeavor using the PXS approach.

### 2. GRAPH ASIC

## 2.1 Architecture overview

Redesigning into an integrated system having amplifiers and ADCs required moving to a smaller node (250nm to 130nm), which has some technical constrains. A waveform sampling array is made of a large number of switches and capacitors, which begin to channel leak charge from the storage capacitors back to the input, hence loosing the correct sampled value. This effect was found in simulation to be in the range of a few mV/us. Despite short access and conversion times, opting for a random digitization moment of the event in the sampling array would have non-deterministic effects, hence produce large conversion errors. In order to be able to retain a high S/N ratio of the system, the time between sampling and conversion should remain constant for all chips running synchronously. We explore, to our knowledge, a somewhat novel ADC architectural concept using a mixed signal memory. We named it the Hybrid Universal sampLing Architecture (HULA).

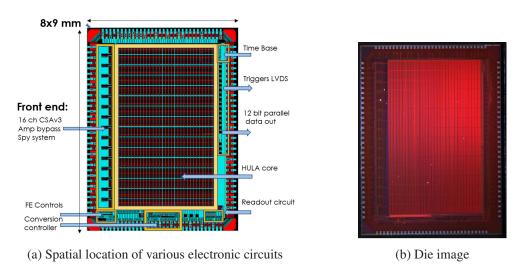

GRAPH ASIC [8] is a mixed signal 16 channel input, 12 bit digital data output system on chip designed for reading MCP detectors with crossed strip anodes. For operation it requires two 1.2 V power supply rails, a 2.5 V for the LVDS transceiver operation, while the analog and digital grounds are split. It is developed in TSMC 130nm technology on a die the size of roughly 8 by 9 mm and uses 128 interconnection pads.

The front end is composed of programmable CSAv3 [4] amplifiers with an additional circuit that allows bypassing the CSA, if the ASIC is used in another applications, and the amplified signal is then fed into the HULA ADC. In order to control the sampling and conversion, the Timebase circuit generates the sampling vector address from a single input clock pin. It also generates internal synchronization signals that govern the conversion. In addition, an independent read system mechanism is available, which minimizes the readout dead time for this particular case of use. The slow control system is composed of a 4 wire SPI like receiver, accepting 1.2V LVCMOS signals. Its command decoder accepts frames being 64 bit long, containing the targeting internal address space and values to control circuits for various settings and internal biasing voltages (DACs). Figure 2a depicts the internal structure of the ASIC and, Fig 2b the pictogram of the chip.

With the GRAPH ASIC redesign we address also some desired improvements on the system level, and these are:

- Reduce complexity and make it fully programmable (low pin count, low grade FPGA required)

- Improve the event readout rate

- Minimize the system's footprint to the point it could be scaled abutting smaller detectors

Figure 2: (a) ASIC layout (b) GRAPH ASIC image

## 2.2 Sampling windows and memory array

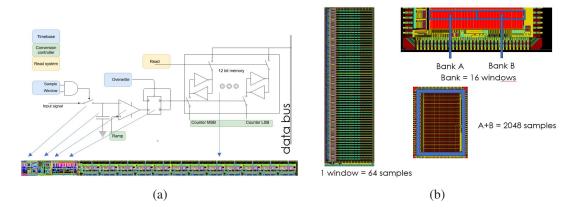

A single sample of the HULA architecture is built using a mixed signal memory, employing a small 30 fC capacitor for analog sampling, a comparator, and a 12 bit digital memory SRAM alike, shown in figure 3a. Once the sample acquires its analog value, a conversion using the Wilkinson

ADC approach will take place at some deterministic point in time. While in conversion, the 12 SRAM bits are connected to the bus and follow the counter value. As soon as the ramp value is above the signal in the capacitor, a D flip flop is set, which disconnects the 12 bit memory from the bus, retaining the last counter value. A separate bus is used to independently read the memory array.

A single sample is stacked into a so called vertically oriented window containing 64 samples, and there are two banks having 16 windows for each channel. Therefore the memory length of 2048 samples is available for every channel. The memory banks are stacked horizontally, while channels are stacked vertically 3b.

Figure 3: (a)One sample of a mixed mode memory (b) Window, Bank, Channel geometrical placement

### 2.3 Timebase generation circuit

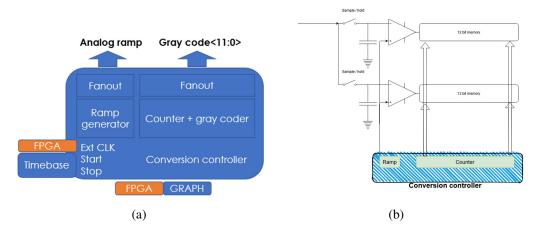

The Timebase generation circuit, figure 4a is composed of a self looped serial shift register being 64 bits in length, inside which a sample actuation signal of programmable width is let to circulate in a loop. When the external nCLR signal is released, the shift of this signal occurs driving the sampling action through the samples in the window at an externally provided clock. At each turnaround, a 5 bit counter increments by one, and its value represents the window which is addressed for sampling, figure 4b. The signal from the shift register is directly fanned out to all windows arrays, while the decoded value in the 5 bit counter selects the window undergoing sampling 3a. In addition, the Timebase extrapolates a few more signals necessary for internal synchronization. An AnB signal is sent off the the chip, when the transition from one bank to another happens and internal signals are set to control the conversion controller.

#### 2.4 Conversion controller

The main function of the conversion controller is to execute the conversion at a deterministic moment. It is composed of ramp generator, which relies on a programmable current source driven into a capacitor to create a voltage ramp 5a. A gray coded counter value is derived from a synchronous counter that revolves at the externally provided frequency clock. The 12 bit Gray code and analog ramp signal are further buffered for fanout over the 16 channels of the entire bank 5b. Hence the ASIC has two such controllers, one for each bank.

Figure 4: (a)Functional block diagram of the Timebase circuit (b) Sampling signal sequence diagram

Once the Timebase unit signals the conversion request, the conversion controller will sync the external clock with the start of the ramp, and initiate the counter. Conversely, when the conversion ends, the system self resets the counter, the ramp value and unlocks the memory allowing to be overwritten in the next iteration.

Figure 5: (a)Functional block diagram of the Conversion controller (b) Conversion controller Bank fan out

# 2.5 HULA operation

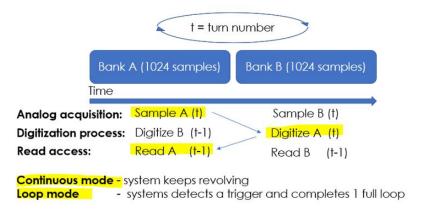

HULA operates on a continuously revolving pattern. Once the sampling starts, the analog signal is sampled in the first Bank. As soon as the first Bank A has completed sampling, the AnB signal changes, signaling the transition to the external world, and automatically starts to sample bank B and puts Bank A into conversion. When the Bank B has completed sampling, Bank A contains digitized data from the previous revolution which are available for the duration of new sampling period of Bank A, figure 6.

Considering there are 1024 samples in each Bank, selecting a sampling clock of 125 MHz will require  $8{,}192~\mu s$  to complete the sampling of one Bank. To reach 12 bit resolution in this time, the external clock shall run at least at 2 ns period, hence at 500~MHz, and the ramp should be adjusted to cover the operating headroom. This allows to set an arbitrary sampling frequency, if a lower

sampling rate is adequate. It also enables reading a much larger portion of the memory in the given conversion time slot, covering more events.

Two additional modes of operation are possible. One is the continuous mode, where the chip keeps overwriting data. And loop mode, when it detects a trigger, it completes one revolution, and at this point, the entire memory is available for reading.

Figure 6: HULA architecure opeartion

#### 2.6 Data readout

The mechanism for memory data readout is completely independent from sampling and conversion, and allows some flexibility in accessing the desired address. It is possible to read consecutive samples from the chosen address, while loading a new one, reducing dead time. This is achieved having a receiver composed of 3 serial inputs (channel,window, sample), a corresponding read clock and load confirmation. When an address is shifted in the system and loaded, the value is an offset added to a counter, which is driven by the read clock. At the rising edge of a clock cycle a new vector is decoded pointing to a single cell. This gets attached to the read bus and streamed to a 12 bit parallel output of the chip, which an FPGA latches at the opposite clock edge, figure 7a. Introducing a value of zero to all three registers, and continuing clocking, one would read sample 0 from channel 0, till the last sample of the channel 0. By continuing asserting the read clock, sample 0 of channel 1 would follow and so on. In our application, we load the address of interest, and make the next 6 clock cycles to load new address, while collecting requested data from the previous call. Such access is envisioned for pulse shape extraction. The maximum transmission frequency tested so far was 60 MHz, which would drain the entire memory in loop mode in about 0.5 ms, collecting some 50kB of data.

Figure 7: (a)Functional block diagram of the data readout mechanism (b) Communication sequence diagram

# 2.7 Trigger section

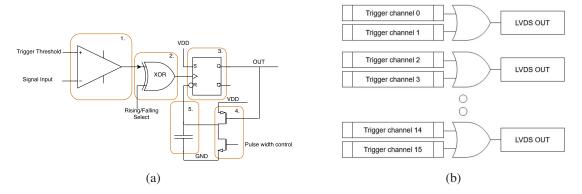

Unlike operating in loop mode, in continuous mode triggers are key for the selection of events to pull from GRAPH memory. Each channel has a trigger circuit composed of a programmable threshold, a logical selection for firing on rising or falling edge of the input signal, and a self reset logical signal (the actual trigger output), which pulse width can be set between a ns to few hundred ns by an internal DAC, figure 8a. Adjacent triggers are OR-ed and fanned out toward the FPGA via an LVDS output 8b. To a degree it allows to discriminate the pulse hit, by setting a common threshold, while setting the width differently. This configuration notably simplifies the required firmware. Ideally, the FPGA is only required to have an 11 bit counter (2048 sample space) being released by the nCLR signal as for all chips, and increments synchronously with the sampling clock. At trigger arrival the value is latched, and the readout processing sequence can estimate the events of interest to extrapolate the charge cloud signal form the MCP/anode. An additional possibility to enhance the functionality is by adding a TDC on the muxed triggers, and locate with better timming the absolute time of the photon arrival. By testing the system a sub ns time of arrival precision should be possible. An additional option, the software trigger, is also available, and can be initiated via the slow control serial register. Both trigger options would stop the ASIC in loop mode operation, as well as, both can be masked to be overruled.

Figure 8: (a) Channel trigger circuit (b) Trigger outputs arrangement

## 3. Results

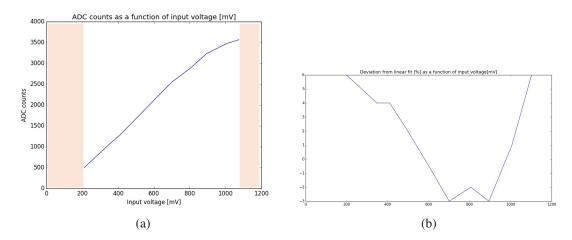

For testing the ASICs, a PCB board that can be attached to a detector was produced. This solution has currently 4 ASICs wire bonded directly onto the PCB along with a minimal set of low drop regulators and a subsets of dual inline connectors to connect to an external FPGA board. For testing, the sampling clock was set to 125MHz, and the Wilkinson conversion clock was set to 500 MHz. Initially, the CSA amplifier was skipped, and only the performance of the HULA core was examined by carefully tuning the conversion slope to match the pedestal offset on both Banks. Because the comparators in each memory cell cannot operate near the voltage supply rails, using a DC swap the usable ADC headroom was extracted. Although each ASIC is slightly different, we found all of them operate safely within a 800 mV headroom covered by some 3000 ADC counts. The INL has found to be of few percent, figures 9a,9b.

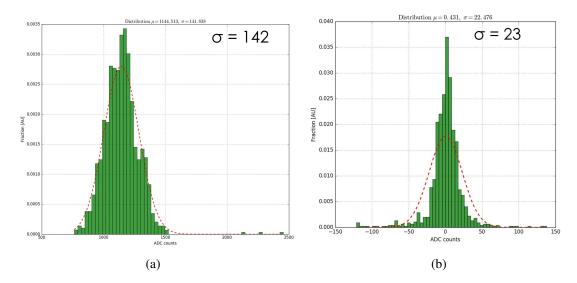

By applying a DC voltage of about 600 mV to the input, the recorded pedestal spread was found to be considerable, with a sigma of 142 counts, figure 10a This somewhat expected result comes from a combination of factors. These are the systematic production mismatch of the capacitors used in the sampling cell, the intrinsic firing point error of the comparator, and the location of cell itself inside the large memory array, as the ramp propagates through the fanout. A solid calibration method is to measure each cell about a 100 times and average its value. As a new measurement is taken, the averaged offset value is subtracted from the measurement. In doing so, the pedestal value is removed and the intrinsic offset of the cell is corrected reducing the spread to a sigma of 23 counts, figure 10b. The ADC has an SNR of 20log\*(3000/23) of around 42dB, with the sensitivity of about 6 mV. Although the system is set to use 12 bits of data the ENOB figure is more around 7.

Figure 9: (a) GRAPH ADC counts as a function of input voltage. (b) Measured linearity error.

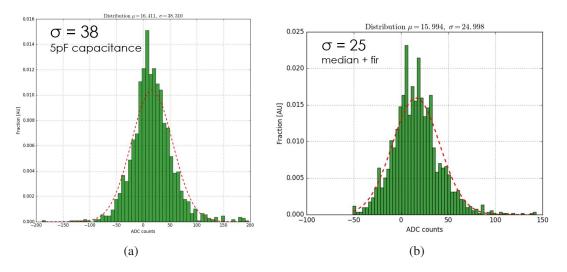

The system was connected to the detector, and the CSAv3 amplifiers were turned on having the calibration procedure being repeated. The amplifier noise generated by the 5 pF input capacitance has worsen the result to 38 ADC counts, figure 11a. Some of that was found that could be reduced by off line post processing the data using a combination of a median and FIR filter to some degree of success, figure 11b. None the less, the obtained raw results are very close to the specifications and expected performance.

Figure 10: (a) HULA noise contribution (b) Pedestal corrected HULA noise contribution

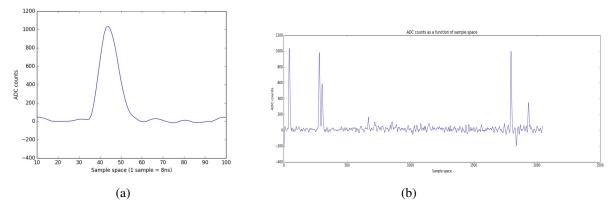

Finally, the MCP detector was setup, biased, and illuminated with a flux of mostly single photons. Plots showing the temporal response in ADC counts as a function of sample space are presented in figure 12.

Figure 11: (a)GRAPH ASIC noise contribution attached to the detector (b) Median and fir filter corrected result

Figure 12: (a) Single channel event in sample space (b) Multiple consecutive photon traces in sample space

# 4. Summary and future work

We developed the GRAPH ASIC, which enables the construction of a readout system intended to couple to a large area MCP single photon imaging detector, designated for future space applications. The test board was constructed and the ASIC performance evaluated. Furthermore initial test confirm the correct functionality as well as correct operation. In addition tests recording detector signals were carried out. Considering the low power consumption of 50mW per channel, an extrapolated value for a 8x8 cm detector requiring 128 channels per axis \*(16 ASICs) would yield a power consumption of 13 Watts FPGA excluded. In the future we look to test a new kind of firmware, that would only record events, by asserting a few clock cycles only when a signal is detected via triggers, and force conversion, if an arbitrary overdue time has passed to avoid losing the signal due to leakage. In this way, we aim to optimize the usage of the memory while preserving the sampling clock. Ultimately, an improbev version of HULA with a much better SNR could operate as an event sampler, digitize and data hold system.

The new revised version under consideration will address the noise values, as contributing sources aren't fully understood yet, the sampling leakage issue, and reduce the amount of communication lines required. One option is certainly to buffer and serialize data of selected events. This would open the possibility to attach 20 chips on a single FPGA to equip a 100x100mm detector.

# 5. Acknowledgments

We would like to thank NASA Strategic Astrophysics Technology program (NNX12AF46G) for financial support. We would also like to thank NALU scientific LLC for their invaluable help during the ASIC design verification process. We would like to thank Dr. Peter Orel, Vihtori Virta, and Matt Andrew and Nalu LLC for their support.

#### References

- [1] O. H. W. Siegmund et. al., "Development of sealed cross strip readout UV detectors, UV, X-Ray, and Gamma-Ray Space Instrumentation for Astronomy", XXII,11821, SPIE, 2021, 10.1117/12.2601037

- [2] J. Vallerga et al., "Cross strip anode readouts for large format, photon counting microchannel plate detectors: developing flight qualified prototypes of the detector and electronics", Proc. SPIE 9144, Space Telescopes and Instrumentation 2014: Ultraviolet to Gamma Ray, 91443J (July 25, 2014); doi:10.1117/12.2058412;

- [3] J. Vallerga et. al., "Centroiding algorithms for high speed crossed-strip readout of microchannel plate detectors", Nuclear Instruments and Methods in Physics, Research Section A: Accelerators, Spectrometers, Detectors and Associated equipment, Volume 633, Supplement 1, May 2011, Pages 255-258, 11th International Workshop on Radiation Imaging Detectors (IWORID)

- [4] A. Seljak et al., "A fast, low power and low noise charge sensitive amplifier ASIC for a UV imaging single photon detector", JINST\_001T\_0916; doi:10.1088/1748-0221/12/04/T04007

- [5] A. Seljak et al., "Prototype readout system for a multi Mpixels UV single-photon imaging detector capable of space flight operation", JINST\_T02003\_T02003; DOI: 10.1088/1748-0221/13/02/T02003

- [6] A. Seljak et al., "ASICs and Readout System for a multi Mpixel single photon UV imaging detector capable of space applications", PoS(TWEPP-17)025, DOI: https://doi.org/10.22323/1.313.0025

- [7] J. Vallerga et al., Development of a flight qualified 100 x 100 mm MCP UV detector using advanced cross strip anodes and associated ASIC electronics, Proc. SPIE 9905, Space Telescopes and Instrumentation 2016: Ultraviolet to Gamma Ray, 99053F (July 18, 2016); doi:10.1117/12.2233697

- [8] A. Seljak et al., "GRAPH ASIC, a readout chip for Multi Mpixel single photon imaging detector", -N-36-04 (1576), IEEE/NSS 2020 virtual conference, session: N-36 - Analog and Digital Circuits: fast timing and readouts. Date: Friday, 6 November, 2020, 8:54 AM

- [9] J. Vallerga et al., "Optical MCP image tube with a quad Timepix readout: initial performance characterization", JINST 9 C05055, DOI: 10.1088/1748-0221/9/05/C05055

- [10] M. Fiorini et al., "Development of a hybrid single-photon imaging detector with embedded CMOS pixelated anode", J. Phys.: Conf. Ser. 2374 012129, doi:10.1088/1742-6596/2374/1/012129

- [11] R. Ballabriga et al., "The Timepix4 analog front-end design: Lessons learnt on fundamental limits to noise and time resolution in highly segmented hybrid pixel detectors," Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, vol. 1045, pp. 167489, 2023, doi: https://doi.org/10.1016/j.nima.2022.167489.

- [12] S. Diebold et al., "UV MCP Detectors for WSO-UV: Cross Strip Anode and Readout Electronics," in IEEE Transactions on Nuclear Science, vol. 60, no. 2, pp. 918-922, April 2013, doi: 10.1109/TNS.2013.2248096.