# MicroNAS: Memory and Latency Constrained Hardware-Aware Neural Architecture Search for Time Series Classification on Microcontrollers

Tobias King<sup>1</sup> Yexu Zhou<sup>1</sup> Tobias Roddiger<sup>1</sup> Michael Beigl<sup>1</sup>

# Abstract

Designing domain specific neural networks is a time-consuming, error-prone, and expensive task. Neural Architecture Search (NAS) exists to simplify domain-specific model development but there is a gap in the literature for time series classification on microcontrollers. Therefore, we adapt the concept of differentiable neural architecture search (DNAS) to solve the time-series classification problem on resource-constrained microcontrollers (MCUs). We introduce MicroNAS, a domain-specific HW-NAS system integration of DNAS, Latency Lookup Tables, dynamic convolutions and a novel search space specifically designed for time-series classification on MCUs. The resulting system is hardware-aware and can generate neural network architectures that satisfy user-defined limits on the execution latency and peak memory consumption. Our extensive studies on different MCUs and standard benchmark datasets demonstrate that MicroNAS finds MCUtailored architectures that achieve performance (F1-score) near to state-of-the-art desktop models. We also show that our approach is superior in adhering to memory and latency constraints compared to domain-independent NAS baselines such as DARTS.

# 1. Introduction

MCUs are small, low-power computing systems that can be found in a wide range of devices, including medical equipment, consumer electronics, wearables and many more. Deploying machine learning models directly on microcontrollers enables applications such as predictive maintenance (Cao et al., 2020), human activity recognition (Rashid et al., 2022) or health monitoring (Abbas et al., 2018) to be always available without network connectivity while ensuring privacy (Chen and Ran, 2019). Many of these devices utilize sensors, such as, accelerometers, gyroscopes and more which generate time series data (Sehrawat and Gill, 2019).

The combination of sensors and microprocessors embedded in smart sensors creates the opportunity for offline, on-device data analysis which allows these devices to operate in privacy-critical, real-time and autonomous systems (Zhang et al., 2023). Due to the limited hardware of typical MCUs (e.g. 64 kB SRAM, 64 MHz CPU clock), it is not possible to run state-of-the-art time series classification architectures such as InceptionTime (Ismail Fawaz et al., 2020) or DeepConvLSTM (Ordóñez and Roggen, 2016) on these devices.

A common solution to deal with the limited resources of microcontrollers is to send the raw data to a server in the cloud, where state-of-the-art models can be executed and then transmit the result back to the microcontroller. For many reasons, this approach is not sustainable: network communication introduces uncertain latencies to the system preventing its use in real-time applications or scenarios where networking is not available, processing data on external servers creates a privacy risk. In addition, network communication is expensive for microcontrollers in terms of energy consumption. Another option is to manually design specific neural networks for individual use-cases. This is often done by domain experts with knowledge in the field of machine learning and is an error-prone and time-consuming process (Mendoza et al., 2016). To automate this design process, neural architecture search (NAS) can be applied to find suitable neural network architectures for specific use-cases. Existing state-of-the-art NAS-systems focus on generating neural network architectures for image classification (Liu et al., 2019b; Wu et al., 2019; Wan et al., 2020). Hardware-aware NAS systems (HW-NAS) which optimize classification accuracy and hardware utilization have also been implemented for image classification (Zhang and Zhou, 2021; Liberis et al., 2021; Cai et al., 2019). However, existing HW-NAS systems are not adapted to the time series classification task and utilize latency estimation methods that are not precise enough for highly constrained microcontrollers (Zhang and Zhou, 2021; Liberis et al., 2021; Wan

<sup>&</sup>lt;sup>1</sup>Karlsruhe Institute of Technology, Karlsruhe, Germany. Correspondence to: Tobias King <tobias.king@kit.edu>, Yexu Zhou <yexu.zhou@kit.edu>, Tobias Roddiger <tobias.roeddiger@kit.edu>, Michael Beigl <michael.beigl@kit.edu>.

#### et al., 2020).

To apply HW-NAS to time series classification, two main challenges need to be overcome. First, the shape of time series data differs fundamentally from image data which requires an adaptation of the search space. We solve this problem by introducing a novel, two stage search space, in which first Time-Reduce cells extract temporal context and in a second step, Sensor-Fusion cells allow for crosschannel interaction (Zhou et al., 2022). Depending on the window-size and the number of sensor-channels, we vary the number of cells in the search space to cover a wide range of time series datasets. Second, to be able to adhere to the resource constraints of MCUs and select the best architecture, a fine granular search space in combination with precise execution latency predictions is required. If the search space is to coarse, it may not be possible to find optimal architectures for the given task that still satisfy user imposed limits on the execution latency and peak memory consumption. Similarly, imprecise execution latency estimations make it impossible to determine when the maximum allowed execution latency is exceeded. We utilize a masking convolution approach adapted from (Wan et al., 2020) to create a fine granular search space by varying the number of filters in convolutional layers. To precisely estimate the execution latency of architectures in the search space, we employ a latency lookup table based approach (Wu et al., 2019). Wan et al. (2020) employ a technique called effective-shape-propagation in order to estimate the execution latency of architectures. This approach is not compatible with the lookup-table based approach but we overcome this limitation by linking these two techniques with an interpolation schema. In summary, this paper makes the following contributions:

- MicroNAS; the first hardware-aware neural architecture search (HW-NAS) system for time series classification tasks on embedded microcontrollers.

- Introduction of a time series classification specific search space suitable for datasets with varying window sizes and number of sensors. The search space contains two searchable cells that extract temporal information and allow for cross-channel interaction respectively.

- An automatic characterization method to calculate neural architecture execution latencies for microcontrollers based on a lookup table with an average error of ≈ ±1.59 ms, showing that this approach outperforms proxy latency metrics (≈ ±15.57 ms).

# 2. Background and Related Work

We first summarize time-series classification using deep learning approaches and then introduce existing state-of-theart neural architecture search systems.

## 2.1. Time Series Classification

In the recent past, deep learning based approaches have been used successfully for time series classification. Systems such as InceptionTime (Ismail Fawaz et al., 2020) and the system by Cui et al. (2016) feature CNN based architectures to aggregate temporal context on multiple scales. Other options include the use of RNNs or hybrid models consisting of both CNN and RNN layers (Mahmud et al., 2020; Ordóñez and Roggen, 2016). Due to computational complexity, using such systems on MCUs is not feasible. Therefore, neural networks specifically designed for the time-series classification task on microcontrollers must be developed (Dennis et al., 2019; Yang and Zhang, 2017). Inspired by the existing CNN system architectures, we develop our NAS search space. This space features searchable cells that are tailored for MCUs and, at the same time, can represent typical structures found in CNN time series classification systems.

#### 2.2. Neural Architecture Search

Early neural architecture search systems (NAS) (Zoph and Le, 2017) formulate the search as a reinforcement learning problem. While this approach produces novel, wellperforming architectures, the search takes long as each iteration of the REINFORCE-algorithm requires training a neural network until convergence with no weight sharing between architectures. To overcome this issue, super-networks have been introduced as search spaces, where each architecture exists as a subgraph, allowing for shared weights among them (Liu et al., 2019b; Pham et al., 2018). Brock et al. (2017) and Pham et al. (2018) show, that training the supernetwork is enough to emulate any architecture in the search space. Liu et al. (2019b) extend this idea by introducing Differentiable Neural Architecture Search (DNAS). DNAS utilizes a relaxation schema to make the search continuous, differentiable and, therefore, more resource efficient. In DNAS, the search space is also defined by a super-network, in which a layer has not one but multiple operations. The layer output l is then computed as a convex combination of the output of the operations o scaled by the architectural weights  $\alpha$ :  $l = \sum_{i} o_i * \alpha_i$ . During architecture search, the regular neural network weights and the architectural weights are jointly optimized using gradient descent. This allows for a structured and more efficient search. After training is complete, the architectural weights are used to identify the selected architecture. Due to its efficiency, we use DNAS as the basis for the search algorithm of MicroNAS.

Recently, NAS has been extended to be hardware aware (HW-NAS). Systems in this category not only optimize for classical performance metrics such as accuracy or precision

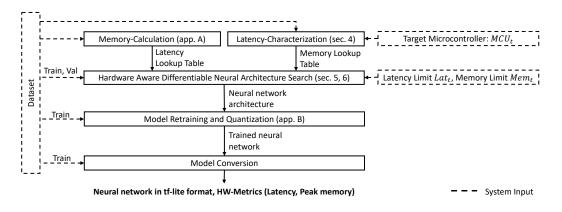

Figure 1. MicroNAS requires the dataset to be split into three different sets which are used at different stages in the pipeline. The user specifies the dataset to be used, the target MCU ( $MCU_t$ ) and the maximum allowed hardware utilization in terms of execution latency ( $Lat_t$ ) and peak memory consumption ( $Mem_t$ ). Output of the system is a corresponding neural network in the tf-lite format.

but also for hardware specific metrics such as execution latency, peak memory and energy consumption (Benmeziane et al., 2021). Optimizing the hardware utilization is especially important when targeting microcontrollers as these devices are typically severely resource constraint. Therefore, during architecture search time, the search algorithm needs to be able to estimate relevant hardware metrics for arbitrary architectures. For the peak memory consumption, analytical estimation can be used for precise calculation. In contrast, for the execution latency, many approaches exist (Benmeziane et al., 2021). Real-time latency measurements on the target hardware during architecture search provide precise measurements but prolong the search drastically (Benmeziane et al., 2021). Another common and much faster approach is to use the number of flops or similar metrics as a proxy for the execution latency (Wu et al., 2019; Liberis et al., 2021; Zhang and Zhou, 2021). While the authors of MicroNets (Zhang and Zhou, 2021) and  $\mu$ Nas (Liberis et al., 2021) claim the number of operations in a model to be a good proxy for the execution latency when targeting MCUs, Lai et al. (2018b) argue that this is not the case. A middle ground between the slow but precise on-device measurements during search and the fast but imprecise latency estimations using the number of operations, are lookup tables (Benmeziane et al., 2021). With the lookup table approach, operations in the search space are executed on the MCU once and can then be efficiently used during search time.

Existing NAS approaches that target time series data are concerned with classification (Rakhshani et al., 2020) and forecasting (Chen et al., 2021) but do not target MCUs and are not hardware aware. In contrast, HW-NAS systems which target MCUs are not concerned with time-series classification (Zhang and Zhou, 2021; Liberis et al., 2021). This underlines the need for a HW-NAS time series classification system that combines the techniques of differentiable neural architecture search and the lookup table based latency estimation approach.

# 3. System Overview

The system overview of MicroNAS can be seen in Figure 1. The input to the system consists of a time series dataset, an MCU to use  $(MCU_t)$  and user-defined limits on the execution latency  $(Lat_t)$  and peak memory consumption  $(Mem_t)$ . In a first step, the hardware utilization of each operator in the search space is obtained in an operation called characterization, shown in section 4. After characterization, HW-NAS is executed where a DNAS approach (section 6) is utilized to select a suitable architecture from our search space (section 5) for the dataset and  $MUC_t$  combination. The found architecture is then extracted from the search space and retrained from scratch using quantization aware training to maximize classification performance (Appendix B). Finally, the trained,  $int_{-8}$  quantized neural network is converted to the tf-lite format and can now be deployed on  $MCU_t$ .

# 4. Latency & Peak Memory Estimation

For MicroNAS to find architectures which obey user-defined limits on the execution latency and peak-memory consumption, it is necessary to estimate the actual execution latency and peak-memory consumption of individual architectures in the search space. To improve on flops-based proxy metrics for the execution latency, we introduce a lookup-table based approach. In Appendix A we then outline how to analytically estimate the peak-memory consumption as previously done by (Zhang and Zhou, 2021; Liberis et al., 2021).

#### 4.1. Latency Characterization

When calculating the execution latency of neural network architectures, the literature proposes to use the number of

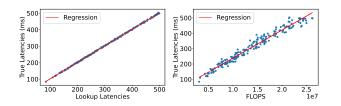

*Figure 2.* Execution latency of whole architectures from our search space. Left: Our lookup-table latency approach. MAE: 1.59 ms,  $R^2$ : 99.97 %. Right: Flops based estimate: MAE: 15.57 ms,  $R^2$ : 96.78 %.

operations in an architecture as a proxy metric (Liberis et al., 2021; Zhang and Zhou, 2021; Liberis and Lane, 2023). We argue for a lookup table based approach, in which we obtain the execution latency of each operator in our search space by executing it on the actual MCU. From this information, we can calculate the execution latency for arbitrary architectures in the search space. To determine the viability of this approach, we conduct our own experiment in which we compare our latency lookup table approach with a flopsbased proxy metric as seen in Figure 2. We executed the experiment using int\_8 quantized networks on the Nucleo-L552ZE-Q where we measure the actual execution latency by using the internal CPU-cycle counter on ARM-Cortex processors. Results can be seen in figure 2. Our lookup table approach achieves an  $R^2$ -score of 99.97 with a mean absolute error of 1.59 ms. The flops based latency estimation achieves an  $R^2$ -score of 96.78 and a mean absolute error of 15.57 ms. Therefore, we can conclude, that the lookup table approach is able to outperform the flops-based latency estimation approach.

# 5. Search Space

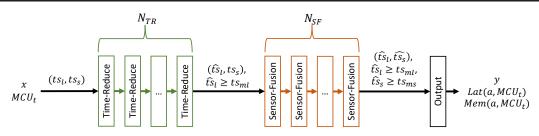

To accommodate the time-series classification task, we introduce a novel, MCU-tailored search space consisting of two types of architecture-searchable cells. This search-space is defined by a super-network, build from a linear stack of architecture-searchable cells. To support the time series classification task, two types of searchable cells are designed. First, Time-Reduce cells are utilized to extract temporal context from the incoming time series. In a second step, Sensor-Fusion cells allow for cross-channel interactions where information from multiple sensors can be fused. This two-step process is a common approach in the domain of time series classification (Cui et al., 2016; Ordóñez and Roggen, 2016; Liu et al., 2019a; Abedin et al., 2021; Zhou et al., 2022). Each of the searchable cells is hardware aware and therefore output their hardware metrics, the execution latency  $Lat(\alpha, MCU_t)$  and the peak memory consumption  $Mem(\alpha, MCU_t)$  which depend on the architectural weights  $\alpha$  and  $MUC_t$ . To adapt the search space dynamically to datasets with varying window sizes  $(ts_l)$  and number of sensor-channels  $(ts_s)$ , the number of cells is adapted automatically. The number of Time-Reduce cells is calculated according to:

$$N_{TR} = \left\lfloor log_2(\frac{ts_l}{ts_{ml}}) \right\rfloor$$

and the number of Sensor-Fusion cells is calculated according to:

$$N_{SF} = \left\lfloor \log_2 \left( \frac{ts_s}{ts_{ms}} \right) \right\rfloor (1 + sf_s)$$

$ts_{ml}$  is the minimum window size after the Time-Reduce cells while  $ts_{ms}$  is the minimum size of the sensordimension after the Sensor-Fusion cells. The parameter  $sf_s$  is user settable to increase the number of Sensor-Fusion cells which allows for deeper networks. The Sensor-Fusion cells can be configured with stride 1 or 2 while the number of cells with stride 2 is independent of the parameter  $sf_s$ . An overview of this search-space can be seen in Figure 3. To improve stability during training, dropout layers with dropout factor 0.3 are placed between all cells (not shown in figure).

## 5.1. Decision Groups

In DNAS, each searchable cell contains two sets of weights: The regular neural network weights w as well as the architectural weights  $\alpha$  indicating the architecture. These architectural weights are organized in decision groups. A decision group  $\alpha_i$  is a collection of architectural weights  $\alpha_{i,j}$ , used to make one-out-of-many decisions.  $\alpha_{i,j}$  denotes the *j*-th architectural weight in the *i*-th decision group. Each weight  $\alpha_{i,j}$  in a decision group gates a path in the cell and therefore, one-hot encoded decision groups define the cell-architecture. During search-time, a pseudo probability-function is applied to the decision group:

$$\hat{\alpha}_{i,j} = pseudo\_prob(\alpha_{i,j}) \tag{1}$$

After the search, each decision group will be one-hot encoded. This effectively discards all options which are assigned the zero value and therefore the final architecture is determined.

#### 5.2. Dynamic Convolutions

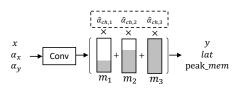

A dynamic convolution (Wan et al., 2020) is a convolution whose number of filters can be searched for efficiently by using weight sharing. We adapt this concept and couple it with an interpolation schema to make it compatible with our latency lookup table. In a dynamic convolution, first a convolution with the maximum number of allowed filters  $f_{max}$ is applied to the input x. The output of this convolution is then multiplied with a binary mask in the filter-dimension.

Figure 3. High-level overview over the search space. The raw, windowed time series x with shape  $(ts_l, ts_s)$  is propagated though  $N_{TR}$ Time-Reduce and  $N_{SF}$  many Sensor-fusion cells. The resulting time series is then of shape  $(\hat{ts}_l, \hat{ts}_s)$ . Class probabilities y and hardware metrics are output by the Output cell at the end of the network.

This mask is the weighted sum of several masks  $m_i$ , with architectural weights  $\hat{\alpha}_{y,i}$ :

$$y = conv(x) * \left(\sum_{i} \hat{\alpha}_{y,i} * m_i\right)$$

This formulation allows to efficiently search for the number of filters in a convolution by using the decision group  $\alpha_{u}$ . As the hardware utilization of a convolution also depends on the number of filters in the incoming time series, we need to take the decision group  $\alpha_x$ , responsible for the number of filters in the input into consideration. To reduce the cost of latency characterization, we introduce the granularity g with  $(f_{max} \mod g == 0)$ . This parameter controls how many filters are disabled by one mask  $m_i$ . To characterize a dynamic convolution, we must execute all possible combinations of number of input and number of output filters on the  $MCU_t$ . The introduction of g reduces the number of possible combinations from  $f_{max}^2$  to  $(f_{max}/g)^2$  which significantly reduces characterization cost. Finally, execution latency and peak memory consumption for a dynamic convolution can be calculated with the interpolation schema according to Equation 2. In the equation, the function HW(x, y) returns the execution latency and peak memory consumption for the dynamic convolution with x input and y output filters.

$$op_{hw} = \hat{\alpha}_{y}^{T} \cdot HW_{op} \cdot \hat{\alpha}_{x}$$

with

$$HW_{op} = \begin{bmatrix} HW(g_{x}, g_{y}) & \dots & HW(|\alpha_{x}|g_{x}, g_{y}) \\ \vdots & \ddots & \vdots \\ HW(g_{1}, |\alpha_{y}| * g_{y}) & \dots & HW(|\alpha_{x}|g_{x}, |\alpha_{y}|g_{y}) \end{bmatrix}$$

(2)

In the equation,  $g_y$  denotes the granularity corresponding to the output of the convolution while  $g_x$  corresponds to the granularity of the input. The same concept can be applied to the dynamic Add operations.

## 5.3. Cells

To accommodate the time series classification task, two types of searchable cells are designed. The Time-Reduce

Figure 4. Dynamic convolution with three different options (e.g.  $f_{max} = 24, g = 3$ ) for the number of filters. The binary masks  $(m_i)$  zero out certain filters in the output of the convolution. Grey areas are ones and white areas are zeros.h

cell aggregates information in the temporal domain while the Sensor-Fusion cell allows for cross channel interaction. After each convolution in the architecture, a ReLU activation function is applied (not shown in graphics).

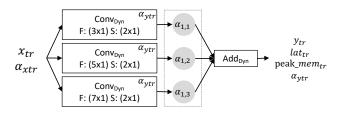

# 5.3.1. TIME-REDUCE CELL

The Time-Reduce cell shown in Figure 5 aggregates local context by applying strided convolutions in the temporal dimension while leaving the sensor-dimension untouched (Filter size:  $(\{3, 5, 7\} \times 1)$ ). This is done to reduce the window size of the propagated time series, to save on computational costs in subsequent cells but also to extract and fuse local initial features from the raw data (Zhou et al., 2022). The cell contains two decision groups.  $\alpha_1$  to choose one of the convolutions and  $\alpha_2$  to select the number of filters in that convolution. Input to this type of cell is a time series  $x_{tr}$  of shape  $(t_{in}, s_{in}, f_{in})$  while the output  $y_{tr}$  is of shape  $(t_{out}, s_{out}, f_{out}) = (0.5 \times t_{in}, s_{in}, f_{in})$  The cell also receives the decision group  $\alpha_{xtr}$  indicating the number of filters in  $x_{tr}$ .

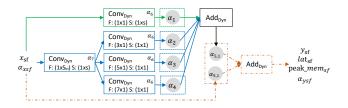

## 5.3.2. SENSOR-FUSION CELL

A common problem when dealing with time series data is the interaction between the different sensors (Bagnall et al., 2017; Zhou et al., 2022). To tackle this problem, the Sensor-Fusion cell, inspired by InceptionTime (Ismail Fawaz et al., 2020), seen in Figure 6 was designed. Input to the cell is a time series  $x_{sf}$  of shape  $(t_{in}, s_{in}, f_{in})$ . The cell can be configured with stride  $stride_{sf}$  to be equal to 1 or 2 which

Figure 5. Time-Reduce cell. Contains two decision groups.  $\alpha_1$  to choose a convolution and  $\alpha_{ytr}$  to search for the number of filters. *F* is the filter size while *S* is the stride configuration.

Figure 6. Sensor-Fusion cell. Consists of three pathways, can be configured with stride one or two and depending on that contains six or seven decision groups. F denotes the filter size while S denotes the stride configuration. The orange pathway is only active, when  $stride_{sf} = 1$ .

influences the output shape to be  $(t_{in}, s_{in}/stride_{sf}, f_{in})$ . When the stride equals one, three pathways through the layer exist, shown in green, blue and orange. The orange pathway (dashed) is an identity connection which can be used to skip the layer and is only included if the input and output of the layer have the same shape and is therefore omitted when the stride equals 2. In the main pathway through the cell (shown in blue), first, a dynamic convolution with filter size  $(1, S_{in})$ is applied to allow cross channel interaction by performing convolution across all sensor-channels. Then, in a next step, multiple convolutions with filter sizes  $(f, 1), f \in \{3, 5, 7\}$ are applied. Each of these convolutions can be individually turned on or off by the search algorithm using the decision groups  $\alpha_{2,3,4}$ . This allows features to be extracted simultaneously at different temporal scales if necessary. In figure 6, these decision groups are drawn with only one weight, although in reality, for each of the three convolutions, a second parallel zero-connection exists as an alternative which allows the individual selection process. In addition, a skipconnection (shown in green) can be added to the layer using  $\alpha_1$ . As all the pathways through the cell must output tensors with the same shape, the dynamic convolutions in the skipconnection and the dynamic convolutions in the main-block share their decision group  $\alpha_6$  to select the number of filters.

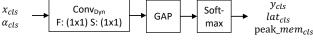

Figure 7. The output cell features a fixed architecture and is therefore not searchable. First, a dynamic convolution is applied to deal with the different number of channels in  $x_{cls}$ . Finally, global average pooling and a Softmax operation are utilized to output the class probabilities.

#### 5.3.3. OUTPUT CELL

The output cell as seen in Figure 7 has a no learnable architecture. It consists of a dynamic convolution where the number of filters is fixed to the number of classes. Finally, class probabilities ( $y_{cls}$ ) are output using a Global Average Pooling (GAP) and Softmax layer.

# 6. Search Algorithm

To search for a suitable architecture in the search space, we apply a modified version of the DNAS algorithm introduced in DARTS (Liu et al., 2019b). We adapt the algorithm to be hardware aware using a multi-objective loss to optimize the architectural weights  $\alpha$ . To force the individual decision groups to converge, we employ the Gumbel-Softmax-function (Jang et al., 2017) with decreasing temperature  $\tau$  as the *pseudo\_prob*-function. Therefore, we optimize the architectural weights  $\alpha$  using the loss-function shown in Equation 3.

$$\mathcal{L}(\alpha, w, MCU_t, Lat_t, Mem_t) = loss_{val}(\alpha, w) + loss_{lat}(\alpha, MCU_t, Lat_t)$$

(3)

+ loss\_{mem}(\alpha, MCU\_t, Mem\_t)

In the equation,  $loss_{val}$  denotes the cross-entropy loss on the validation dataset.  $loss_{lat}$  and  $loss_{mem}$  describe the losses caused by the hardware utilization which depend on the search-space configuration  $\alpha$ ,  $MCU_t$  and the user defined hardware limits  $Lat_t$  and  $Mem_t$ . The hardware loss functions are formulated as

$$\begin{split} & \text{loss}_{\text{lat}} = \gamma_{\text{lat}} \cdot \log\left(\frac{\text{Lat}(\alpha, \text{MCU}_t)}{Lat_t}\right) \cdot [\text{Lat}(\alpha, \text{MCU}_t) \geq \text{Lat}_t] \\ & \text{loss}_{\text{mem}} = \gamma_{\text{mem}} \cdot \log\left(\frac{\text{Mem}(\alpha, \text{MCU}_t)}{\text{Mem}_t}\right) \cdot [\text{Mem}(\alpha, \text{MCU}_t) \geq \text{Mem}_t] \end{split}$$

The parameter  $\gamma$  weights the importance of the individual loss-terms and needs to be set sufficiently high to ensure the user-defined hardware limits are not violated. The complete search-algorithm can be seen in Algorithm 1 where both sets of weights are optimized in an iterative fashion.

Algorithm 1 Search algorithm

1: for  $e \leftarrow 1$  to Epochs do 2: for  $b \leftarrow 1$  to Batches do 3:  $\alpha = \alpha - \eta_1 \nabla_{\alpha} \mathcal{L}(\alpha, w, m, Lat_t, Mem_t)$ 4:  $w = w - \eta_2 \nabla_w \mathcal{L}_{train}(\alpha, w)$ 5:  $\tau \leftarrow \tau \times \epsilon$ 6: end for 7: end for

# 7. Evaluation

To showcase MicroNAS, we utilize two established benchmark datasets from the field of human activity recognition. This section describes the evaluation of MicroNAS on two established benchmark datasets from the field of human activity recognition and displays the ability of MicroNAS to find suitable architectures under various latency and peak memory constraints. The UCI-HAR dataset (Reyes-Ortiz et al., 2016) features a window size of 128 and nine sensor channels. It was recorded with 50 Hz and features six classes. The SkodaR dataset (Zappi et al., 2012) features a window size of 64 data points, 30 sensor channels and was recorded with a sampling rate of 96 Hz. Evaluation was performed on the Nucleo-F446RE (Microelectronics, 2023) equipped with an NRF52832 (ARM Cortex-M4, 180 MHz CPU clock, 512 kB flash, 128 kB SRAM) and the NUCLEO-L552ZE-Q (STMicroelectronics, 2023) equipped with a STM32L552 (ARM Cortex-M33, 80 MHz CPU clock, 512 kB flash, 256 kB SRAM).

# 7.1. Setup

To demonstrate the ease of use of MicroNAS, the same hyperparameters were used for all the experiments. For the convolutions in the Time-Reduce cells,  $f_{max}$  was set to 16 and g was set to four. For the Sensor-Fusion cells,  $f_{max}$  was set to 64 and g to eight. For the number of cells,  $ts_{ml}$  was set to 16,  $ts_{ms}$  to five and  $sf_s$  to two. These settings were chosen to balance between the characterization cost to build the latency lookup table and search space flexibility. For the search algorithm, we set  $\epsilon$  to 0.995,  $\eta_{lat}$  to two and  $\eta_{mem}$  to four. With this setup the search-space for the UCI-HAR dataset contains  $\approx 10^{13}$  architecture and  $\approx 10^{22}$  for the SkodaR dataset.

# 7.2. MicroNAS under different Computational Resource Constraints

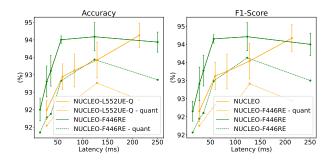

#### 7.2.1. LATENCY VS. PERFORMANCE

This experiment demonstrates the ability of MicroNAS to find architectures under different latency constraints for which we disable the loss caused by the peak-memory consumption. It is expected that the classification performance *Table 1.* Three architectures found by MicroNAS for the SkodaR dataset compared to SOTA classifiers (Mahmud et al., 2020; Ordóñez and Roggen, 2016; Zhou et al., 2022).

| Model         | Device          | LATENCY (MS)<br>PEAK MEMORY (B) | Accuracy<br>NON-QUANT<br>QUANT<br>(%) | F1-Score<br>NON-QUANT<br>QUANT<br>(%) |

|---------------|-----------------|---------------------------------|---------------------------------------|---------------------------------------|

| MICRONAS 1    | NUCLEO-F446RE   | 30.07<br>21504                  | 92.47<br>92.23                        | 91.40<br>91.24                        |

| MICRONAS 2    | NUCLEO-L552ZE-Q | 150.09<br>19392                 | 95.66<br>94.58                        | 93.77<br>92.33                        |

| MICRONAS 3    | NUCLEO-L552ZE-Q | 493.69<br>34560                 | 97.35<br>96.33                        | 96.46<br>95.30                        |

| DEEPCONVLSTM  | Desktop         | 1.1M<br>PARAMS                  | -                                     | 98.99                                 |

| TINYHAR       | DESKTOP         | 67K<br>params                   | -                                     | 98.82                                 |

| MAHMUD ET AL. | DESKTOP         | NOT AVAILABLE*                  | -                                     | 97<br>-                               |

| DARTS-SOFTMAX | INDEPENDENT     | NOT AVAILABLE*                  | FAILED                                | FAILED                                |

| DARTS-GUMBEL  | INDEPENDENT     | NOT AVAILABLE*                  | 96.84<br>95.04                        | 95.74<br>93.19                        |

\* DATA NOT AVAILABLE FROM THE SOURCE.

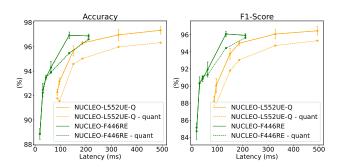

*Figure 8.* Trade-offs on the UCI-HAR dataset. Left: Accuracy, Right: F1-Score (Macro)

will increase as latency targets become higher which is also the cases, as seen in Figure 8 for the UCI-HAR dataset (Reyes-Ortiz et al., 2016) and Figure 9 for the SkodaR dataset (Zappi et al., 2012). It can also be seen, that lower target latencies decrease performance more severely on the Nucleo-L552ZE-Q as it is equipped with a weaker CPU.

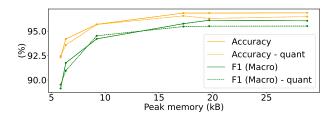

#### 7.2.2. PEAK MEMORY VS. PERFORMANCE

This experiment demonstrates the ability of MicroNAS to find architectures under different peak memory constraints for which we disable the loss caused by the execution latency. We expect performance to increase as more memory is allowed to be used which can be observed in Figure 10. As the TFLM-framework (David et al., 2021) is using the same amount of memory on every microcontroller, this experiment is independent of the microcontroller and is therefore only executed on the Nucleo-L552ZE-Q (STMicroelectronics, 2023).

*Figure 9.* Trade-offs on the SkodaR dataset. Left: Accuracy, Right: F1-Score (Macro)

Figure 10. Trade-off between peak memory consumption and Accuracy / F1-Score (Macro). Comparison on the SkodaR dataset.

*Table 2.* Three architectures found by MicroNAS for the UCI-HAR dataset compared to SOTA classifiers (Kolkar and Geetha, 2021; Dua et al., 2021). \*: Data not available from the source.

| Model         | Device          | LATENCY (MS)<br>Peak memory (B) | Accuracy<br>NON-QUANT<br>QUANT<br>(%) | F1-Score<br>NON-QUANT<br>QUANT<br>(%) |

|---------------|-----------------|---------------------------------|---------------------------------------|---------------------------------------|

| MICRONAS 1    | NUCLEO-F446RE   | 14.45<br>11520                  | 90.21<br>91.85                        | 92.66<br>92.07                        |

| MICRONAS 2    | NUCLEO-F446RE   | 123.84<br>15360                 | 94.59<br>93.93                        | 94.71<br>94.13                        |

| MICRONAS 3    | NUCLEO-L552ZE-Q | 213.57<br>15360                 | 94.63<br>92.78                        | 94.67<br>92.94                        |

| KOLKAR ET AL. | DESKTOP         | NOT AVAILABLE*                  | 96.83                                 | -                                     |

| DUA ET AL.    | DESKTOP         | NOT AVAILABLE*                  | 96.20                                 | 96.19                                 |

| DARTS-SOFTMAX | Independent     | NOT AVAILABLE*                  | 94.08<br>92.01                        | 94.28<br>92.35                        |

| DARTS-GUMBEL  | INDEPENDENT     | NOT AVAILABLE*                  | 95.40<br>92.97                        | 95.59<br>93.24                        |

\* DATA NOT AVAILABLE FROM THE SOURCE.

# 8. Discussion

In comparison to existing systems, MicroNAS is the first to bring time-series classification to microcontrollers using neural architecture search in a hardware aware fashion. As many IoT and wearable devices are equipped with a variety of time-series producing sensors, whose data must be processed, we expect many application scenarios to benefit from our presented methodology. Especially when user data needs to be processed privately, in real-time or a connection to a server in the cloud is not feasible.

#### 8.1. Comparison to the State-of-the-Art

To better understand the performance achieved by our system, we evaluate MicroNAS on state-of-the-art benchmark datasets SkodaR (Zappi et al., 2012) and UCI-HAR (Reyes-Ortiz et al., 2016). MicroNAS is able to achieve performances closes to the state-of-the-art when comparing against time series classification systems found in the literature although these systems are running on desktop computers while neural networks found by MicroNAS are running on MCUs. In addition, we compare MicroNAS to a DARTSbased baseline, where we replace the original search space with our own, to make it compatible to the time series classification task. For the *pseudo\_prob*-function we use the original Softmax implementation as well as the Gumbel-Softmax-function. The results for the SkodaR dataset(Zappi et al., 2012) can be found in Table 1 and for UCI-HAR (Reyes-Ortiz et al., 2016) in Table 2. Further comparisons to other NAS-systems are not possible because they do not target the problem of time-series classification and therefore have incompatible search spaces.

## 8.2. Limitations and Future Work

Besides the neural network architecture, sampling rate, window size, and sensor selection can also impact classification performance (Kim et al., 2021; Banos et al., 2014). To create a complete end-to-end time series classification search system for MCUs, the proposed system can be expanded to encompass these parameters in the search space.

# 9. Conclusion

This paper introduced MicroNAS, a first-of-its-kind hardware-aware neural architecture search (HW-NAS) system specifically designed for time series classification on resource constraint microcontrollers. By utilizing two type of searchable cells, MicroNAS can be used for various datasets which differ in the window-length and the number of sensors. This, coupled with the possibility to set limits on the execution latency and peak memory consumption makes the system usable in various application scenarios such as privacy critical or real-time systems. The used lookup-table latency estimation approach allows to precisely calculate the execution latency of architectures in the search space and therefore enables MicroNAS to be used in real-time systems. Our experimental results indicate, that for a variety of different hardware limits, MicroNAS is able to find a suitable neural network architecture while achieving classification performances close to state-of-the-art desktop models.

# References

- Nasir Abbas, Yan Zhang, Amir Taherkordi, and Tor Skeie. 2018. Mobile Edge Computing: A Survey. *IEEE Internet* of Things Journal 5, 1 (2018), 450–465. https:// doi.org/10.1109/JIOT.2017.2750180

- Alireza Abedin, Mahsa Ehsanpour, Qinfeng Shi, Hamid Rezatofighi, and Damith C. Ranasinghe. 2021. Attend and Discriminate: Beyond the State-of-the-Art for Human Activity Recognition Using Wearable Sensors. *Proc. ACM Interact. Mob. Wearable Ubiquitous Technol.* 5, 1, Article 1 (mar 2021), 22 pages. https: //doi.org/10.1145/3448083

- Anthony Bagnall, Jason Lines, Aaron Bostrom, James Large, and Eamonn Keogh. 2017. The great time series classification bake off: a review and experimental evaluation of recent algorithmic advances. *Data Mining and Knowledge Discovery* 31, 3 (01 May 2017), 606–660. https://doi.org/10.1007/s10618-016-0483-9

- Oresti Banos, Juan-Manuel Galvez, Miguel Damas, Hector Pomares, and Ignacio Rojas. 2014. Window Size Impact in Human Activity Recognition. Sensors 14, 4 (2014), 6474–6499. https://doi.org/10.3390/s140406474

- Hadjer Benmeziane, Kaoutar El Maghraoui, Hamza Ouarnoughi, Smail Niar, Martin Wistuba, and Naigang Wang. 2021. Hardware-Aware Neural Architecture Search: Survey and Taxonomy. In *Proceedings of the Thirtieth International Joint Conference on Artificial Intelligence, IJCAI-21*, Zhi-Hua Zhou (Ed.). International Joint Conferences on Artificial Intelligence Organization, 4322–4329. https://doi.org/10.24963/ ijcai.2021/592 Survey Track.

- Andrew Brock, Theodore Lim, James M. Ritchie, and Nick Weston. 2017. SMASH: One-Shot Model Architecture Search through HyperNetworks. *CoRR* abs/1708.05344 (2017). arXiv:1708.05344 http://arxiv.org/ abs/1708.05344

- Han Cai, Ligeng Zhu, and Song Han. 2019. ProxylessNAS: Direct Neural Architecture Search on Target Task and Hardware. arXiv:1812.00332 [cs.LG]

- Keyan Cao, Yefan Liu, Gongjie Meng, and Qimeng Sun. 2020. An Overview on Edge Computing Research. *IEEE Access* 8 (2020), 85714–85728. https://doi.org/ 10.1109/ACCESS.2020.2991734

- Donghui Chen, Ling Chen, Zongjiang Shang, Youdong Zhang, Bo Wen, and Chenghu Yang. 2021. Scale-Aware

Neural Architecture Search for Multivariate Time Series Forecasting. https://doi.org/10.48550/ ARXIV.2112.07459

- Jiasi Chen and Xukan Ran. 2019. Deep Learning With Edge Computing: A Review. *Proc. IEEE* 107, 8 (2019), 1655–1674. https://doi.org/10.1109/ JPROC.2019.2921977

- Zhicheng Cui, Wenlin Chen, and Yixin Chen. 2016. Multi-Scale Convolutional Neural Networks for Time Series Classification. https://doi.org/10.48550/ ARXIV.1603.06995

- Robert David, Jared Duke, Advait Jain, Vijay Janapa Reddi, Nat Jeffries, Jian Li, Nick Kreeger, Ian Nappier, Meghna Natraj, Tiezhen Wang, Pete Warden, and Rocky Rhodes. 2021. TensorFlow Lite Micro: Embedded Machine Learning for TinyML Systems. In *Proceedings of Machine Learning and Systems*, A. Smola, A. Dimakis, and I. Stoica (Eds.), Vol. 3. 800–811. https://proceedings. mlsys.org/paper/2021/file/ d2ddea18f00665ce8623e36bd4e3c7c5-Paper. pdf

- Don Dennis, Durmus Alp Emre Acar, Vikram Mandikal, Vinu Sankar Sadasivan, Venkatesh Saligrama, Harsha Vardhan Simhadri, and Prateek Jain. 2019.

Shallow RNN: Accurate Time-series Classification on Resource Constrained Devices. In Advances in Neural Information Processing Systems, H. Wallach, H. Larochelle, A. Beygelzimer, F. d'Alché-Buc, E. Fox, and R. Garnett (Eds.), Vol. 32. Curran Associates, Inc. https://proceedings.neurips. cc/paper\_files/paper/2019/file/ 76d7c0780ceb8fbf964c102ebc16d75f-Paper. pdf

- Nidhi Dua, Shiva Nand Singh, and Vijay Bhaskar Semwal. 2021. Multi-input CNN-GRU based human activity recognition using wearable sensors. *Computing* 103, 7 (01 Jul 2021), 1461–1478. https://doi.org/10.1007/ s00607-021-00928-8

- Hassan Ismail Fawaz, Benjamin Lucas, Germain Forestier, Charlotte Pelletier, Daniel F. Schmidt, Jonathan Weber, Geoffrey I. Webb, Lhassane Idoumghar, Pierre-Alain Muller, and François Petitjean. 2020. Inception-Time: Finding AlexNet for time series classification. *Data Mining and Knowledge Discovery* 34, 6 (01 Nov 2020), 1936–1962. https://doi.org/10.1007/ s10618-020-00710-y

- Eric Jang, Shixiang Gu, and Ben Poole. 2017. Categorical Reparameterization with Gumbel-Softmax. In 5th International Conference on Learning Representations,

ICLR 2017, Toulon, France, April 24-26, 2017, Conference Track Proceedings. OpenReview.net. https: //openreview.net/forum?id=rkE3y85ee

- Taehee Kim, Jongman Kim, Bummo Koo, Haneul Jung, Yejin Nam, Yunhee Chang, Sehoon Park, and Youngho Kim. 2021. Effects of Sampling Rate and Window Length on Motion Recognition Using sEMG Armband Module. *International Journal of Precision Engineering and Manufacturing* 22, 8 (2021), 1401–1411. https: //doi.org/10.1007/s12541-021-00546-6

- Ranjit Kolkar and V. Geetha. 2021. Human Activity Recognition in Smart Home using Deep Learning Techniques. In 2021 13th International Conference on Information & Communication Technology and System (ICTS). 230–234. https://doi.org/10.1109/ICTS52701.2021.9609044

- Liangzhen Lai, Naveen Suda, and Vikas Chandra. 2018a. CMSIS-NN: Efficient Neural Network Kernels for Arm Cortex-M CPUs. https://doi.org/10.48550/ ARXIV.1801.06601

- Liangzhen Lai, Naveen Suda, and Vikas Chandra. 2018b. Not All Ops Are Created Equal! https://doi. org/10.48550/ARXIV.1801.04326

- Edgar Liberis, Łukasz Dudziak, and Nicholas D. Lane. 2021. μNAS: Constrained Neural Architecture Search for Microcontrollers. In *Proceedings of the 1st Workshop on Machine Learning and Systems* (Online, United Kingdom) (*EuroMLSys '21*). Association for Computing Machinery, New York, NY, USA, 70–79. https: //doi.org/10.1145/3437984.3458836

- Edgar Liberis and Nicholas D. Lane. 2023. Differentiable Neural Network Pruning to Enable Smart Applications on Microcontrollers. *Proc. ACM Interact. Mob. Wearable Ubiquitous Technol.* 6, 4, Article 171 (jan 2023), 19 pages. https://doi.org/10.1145/3569468

- Chien-Liang Liu, Wen-Hoar Hsaio, and Yao-Chung Tu. 2019a. Time Series Classification With Multivariate Convolutional Neural Network. *IEEE Transactions on Industrial Electronics* 66, 6 (2019), 4788–4797. https: //doi.org/10.1109/TIE.2018.2864702

- Hanxiao Liu, Karen Simonyan, and Yiming Yang. 2019b. DARTS: Differentiable Architecture Search. arXiv:1806.09055 [cs.LG]

- Saif Mahmud, M. T. H. Tonmoy, Kishor Kumar Bhaumik, A. M. Rahman, M. A. Amin, M. Shoyaib, Muhammad Asif Hossain Khan, and A. Ali. 2020. Human Activity Recognition from Wearable Sensor Data Using Self-Attention. In ECAI 2020 - 24th European Conference

on Artificial Intelligence, 29 August-8 September 2020, Santiago de Compostela, Spain.

- Hector Mendoza, Aaron Klein, Matthias Feurer, Jost Tobias Springenberg, and Frank Hutter. 2016. Towards Automatically-Tuned Neural Networks. In Proceedings of the Workshop on Automatic Machine Learning (Proceedings of Machine Learning Research, Vol. 64), Frank Hutter, Lars Kotthoff, and Joaquin Vanschoren (Eds.). PMLR, New York, New York, USA, 58–65. https://proceedings.mlr.press/v64/mendoza\_towards\_2016.html

- ST Microelectronics. 2023. NUCLEO-F446RE STM32 Nucleo-64 development board with STM32F446RE MCU, supports Arduino and ST morpho connectivity -STMicroelectronics. https://www.st.com/en/ evaluation-tools/nucleo-f446re.html. (Accessed on 08/14/2023).

- Francisco Javier Ordóñez and Daniel Roggen. 2016. Deep Convolutional and LSTM Recurrent Neural Networks for Multimodal Wearable Activity Recognition. *Sensors* 16, 1 (2016). https://doi.org/10.3390/ s16010115

- Hieu Pham, Melody Guan, Barret Zoph, Quoc Le, and Jeff Dean. 2018. Efficient Neural Architecture Search via Parameters Sharing. In Proceedings of the 35th International Conference on Machine Learning (Proceedings of Machine Learning Research, Vol. 80), Jennifer Dy and Andreas Krause (Eds.). PMLR, 4095– 4104. https://proceedings.mlr.press/ v80/pham18a.html

- Hojjat Rakhshani, Hassan Ismail Fawaz, Lhassane Idoumghar, Germain Forestier, Julien Lepagnot, Jonathan Weber, Mathieu Brévilliers, and Pierre-Alain Muller. 2020. Neural Architecture Search for Time Series Classification. In 2020 International Joint Conference on Neural Networks (IJCNN). 1–8. https://doi.org/10. 1109/IJCNN48605.2020.9206721

- Nafiul Rashid, Berken Utku Demirel, and Mohammad Abdullah Al Faruque. 2022. AHAR: Adaptive CNN for Energy-Efficient Human Activity Recognition in Low-Power Edge Devices. *IEEE Internet of Things Journal* 9, 15 (2022), 13041–13051. https://doi.org/10. 1109/JIOT.2022.3140465

- Jorge-L. Reyes-Ortiz, Luca Oneto, Albert Samà, Xavier Parra, and Davide Anguita. 2016. Transition-Aware Human Activity Recognition Using Smartphones. *Neurocomputing* 171 (2016), 754–767. https://doi. org/10.1016/j.neucom.2015.07.085

- Deepti Sehrawat and Nasib Singh Gill. 2019. Smart Sensors: Analysis of Different Types of IoT Sensors. In 2019 3rd International Conference on Trends in Electronics and Informatics (ICOEI). 523–528. https://doi.org/ 10.1109/ICOEI.2019.8862778

- STMicroelectronics. 2023. NUCLEO-L552ZE-Q -STM32 Nucleo-144 development board. https: //www.st.com/en/evaluation-tools/ nucleo-1552ze-q.html. (Accessed on 05/31/2022).

- Alvin Wan, Xiaoliang Dai, Peizhao Zhang, Zijian He, Yuandong Tian, Saining Xie, Bichen Wu, Matthew Yu, Tao Xu, Kan Chen, Peter Vajda, and Joseph E. Gonzalez. 2020. FBNetV2: Differentiable Neural Architecture Search for Spatial and Channel Dimensions. In 2020 IEEE/CVF Conference on Computer Vision and Pattern Recognition (CVPR). 12962–12971. https://doi.org/10.1109/CVPR42600.2020.01298

- Bichen Wu, Xiaoliang Dai, Peizhao Zhang, Yanghan Wang, Fei Sun, Yiming Wu, Yuandong Tian, Peter Vajda, Yangqing Jia, and Kurt Keutzer. 2019. FBNet: Hardware-Aware Efficient ConvNet Design via Differentiable Neural Architecture Search. In 2019 IEEE/CVF Conference on Computer Vision and Pattern Recognition (CVPR). 10726–10734. https://doi.org/10.1109/CVPR.2019.01099

- Fan Yang and Lianyi Zhang. 2017. Real-time human activity classification by accelerometer embedded wearable devices. In 2017 4th International Conference on Systems and Informatics (ICSAI). 469–473. https: //doi.org/10.1109/ICSAI.2017.8248338

- Piero Zappi, Daniel Roggen, Elisabetta Farella, Gerhard Troester, and Luca Benini. 2012. Network-Level Power-Performance Trade-Off in Wearable Activity Recognition: A Dynamic Sensor Selection Approach. ACM Transactions on Embedded Computing Systems 11 (09 2012), 68:1–68:30. https://doi.org/10.1145/ 2345770.2345781

- Shuai Zhang and Xichuan Zhou. 2021. MicroNet: Realizing Micro Neural Network via Binarizing GhostNet. In 2021 6th International Conference on Intelligent Computing and Signal Processing (ICSP). 1340–1343. https://doi.org/10.1109/ ICSP51882.2021.9408972

- Zixuan Zhang, Luwei Wang, and Chengkuo Lee. 2023. Recent Advances in Artificial Intelligence Sensors. *Advanced Sensor Research* 2, 8 (2023), 2200072. https://doi.org/10.1002/adsr.202200072 arXiv:https://onlinelibrary.wiley.com/doi/pdf/10.1002/adsr.202200072

- Yexu Zhou, Haibin Zhao, Yiran Huang, Till Riedel, Michael Hefenbrock, and Michael Beigl. 2022. TinyHAR: A Lightweight Deep Learning Model Designed for Human Activity Recognition. In *Proceedings of the 2022* ACM International Symposium on Wearable Computers (Cambridge, United Kingdom) (ISWC '22). Association for Computing Machinery, New York, NY, USA, 89–93. https://doi.org/10.1145/3544794. 3558467

- Barret Zoph and Quoc V. Le. 2017. Neural Architecture Search with Reinforcement Learning. arXiv:1611.01578 [cs.LG]

# **A. Peak Memory Consumption**

For execution of the neural networks on the MCUs, we utilize the TensorFlow Light Micro Framework (TFLM) (David et al., 2021) together with the CMSIS-NN kernel library (Lai et al., 2018a) and  $int_{-8}$  quantization. To calculate the peak memory consumption of an architecture, the literature (Benmeziane et al., 2021; Zhang and Zhou, 2021) proposes to use analytical estimation methods which is also the strategy used in this paper. To execute an operation in a neural network, the input and output tensors of the operation need to be present in memory. In addition to that, some operations, e.g. from the CMSIS-NN kernel library (Lai et al., 2018a) require extra memory to perform the computation. When calculating the peak memory of a sequential model without parallel connections, it can be computed as the maximum over the memory requirements of each operation. In general, the required memory to perform an operation can be computed as stated in equation 4.

$$op_{mem}(op) = \sum_{i} mem(input_i) + mem(output) + extra_mem(op).$$

(4)

The function mem(x) calculates the memory required to store a tensor and considers the data format of it. When using  $int_8$  tensors, only one fourth of the memory is required in comparison to  $float_32$  tensors. The total memory required to run an operation can then be calculated by summing the memory requirements for the input and output tensors. On top of that some operations require extra memory to run which is considered in the calculation of the peak memory usage of an architecture (Lai et al., 2018a). In addition, the TFLM-framework needs additional memory to execute a neural network, which is not taken into account by this system.

# **B. Model Retraining and Quantization**

During architecture search, weight sharing between architectures is applied which allows for an efficient search but at the same time prevents a single architecture to obtain its optimal weights. Therefore, after an architecture has been found, this architecture is trained from scratch to achieve the maximum performance. Training is performed in a quantization aware fashion as we later deploy the resulting model to an MCU using  $int_8$  quantization. This greatly reduces computational cost on the microcontroller in terms of execution latency, peak memory consumption and storage requirements with only a minimal loss in classification performance.