# Development of 100 ps TDC based on Kintex 7 FPGA for the High Granular Neutron Time-of-Flight detector for the BM@N experiment

D. Finogeev<sup>\*,a</sup>, F. Guber<sup>a,b</sup>, A. Izvestnyy<sup>a</sup>, N. Karpushkin<sup>a</sup>, A. Makhnev<sup>a,b</sup>, S. Morozov<sup>a</sup>, and D. Serebryakov<sup>a</sup>

<sup>a</sup>Institute for Nuclear Research of the Russian Academy of Sciences, Moscow, Russia <sup>b</sup>Moscow Institute of Physics and Technology, Dolgoprudny, Russia

#### ABSTRACT

The prototype of TDC board has been developed for the new high granular time-of-flight neutron detector (HGND). The board is based on the standard LVDS 4x asynchronous oversampling using the xc7k160 FPGA with a 100 ps bin width. The HGND is being developed for the BM@N (Baryonic Matter at Nuclotron) experiment to identify neutrons and to measure their energies in heavy-ion collisions at ion beam energies up to 4 AGeV. The HGND consists of about 2000 scintillation detectors (cells) with size  $40 \times 40 \times 25 mm^3$  and light readout with EQR15 11-6060D-S photodetector. To measure the time resolution of the scintillation cells the two channels FPGA TDC board prototype with two scintillation cells were tested with electron beam of "Pakhra" syncrotron in LPI institute (Moscow, Russia). The measured cell time resolution is 146 ps which is in a good agreement with 142 ps time resolution measured with 12-bit @ 5 GS/s CAEN DT5742 digitizer. For the full HGND the TDC readout board with 3 such FPGAs will read 250 channels. In total eight such TDC boards will be used for full HGND at the BM@N experiment.

## 1 Introduction

The physics program of the BM@N fixed target experiment [1, 2] is aimed to study the Equation of State (EoS) of high-density nuclear matter created in heavy-ion collisions at beam energies up to 4 AGeV. The neutron flow at high density (2 - 4)  $\rho_0$  nuclear matter is expected to be sensitive probe to isospin part of the EoS. To measure the neutron flow the new high granular neutron time-of-flight detector (HGND) is under development at INR RAS, Moscow [3]. The HGND will identify high energy neutrons (up to 4 GeV) and measure their energies with energy resolution of a few percents precision and it will have high neutron detection efficiency.

The HGND consists of about 2000 plastic scintillation detectors (cells) with size  $40 \times 40 \times 25 mm^3$ . The SiPM (silicon photomultiplier) EQR15 11-6060D-S, with sensitive area  $6 \times 6 mm^2$  is used for light readout from each cell. The time resolution of cells made of JINR fast scintillators equipped with EQR15 11-6060D-S is about 120 ps [4]. Due to the high total number of electronics channels of the HGND, a multi-channel read-out system needs to be developed. The digital part of read-out is designed based on Kintex FPGA (Field Programmable Gate Array) chip with a 100 ps bin width TDC (Time to Digital Converter). The TDC is realized to perform precise timestamp and amplitude measurements using Time-over-Threshold (ToT) method. The FPGA based read-out has time synchronization with the White Rabbit [5] network and will be integrated in the BM@N common DAQ (data acquisition system).

# 2 TDC implementation in the FPGA

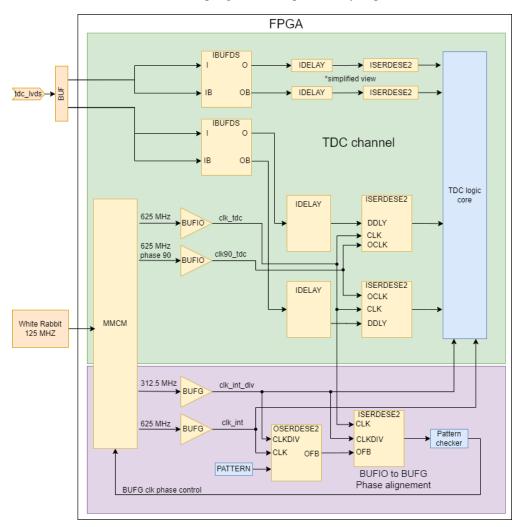

The TDC is based on the Kintex-7 input serial-to-parallel converter with oversampling capability and programmable delay. The design is based on Xilinx recommendations [6], and uses only documented features of the FPGA within its specifications. The simplified TDC schematic is presented in figure 1. The FPGA ISERDESE2 (serial-to-parallel converter) core is driven with 625 MHz clock. This converter has a so-called "oversample" mode, where input signal is sampled four times during each clock period. Sampling is performed with two clocks, precisely shifted by 90°. The ISERDES2 logic has three flip-flops in each sampling channel to minimize the metastability and to synchronize the

<sup>\*</sup> Corresponding author. Email: finogeev@inr.ru

samples at the output stage to one clock edge. The clocking of the flip-flops ensures that the time between sampling of the two connected flip-flops is not less than <sup>3</sup>/<sub>4</sub> of the clock period. With 625 MHz clock the sampling interval is 400ps.

To reach 100 ps time resolution of TDC, four channels with 400 ps sampling are used. The channels are time-shifted from each other by 100 ps with programmable delay core (IDELAY). Two differential input pairs (4 pins of the FPGA) are used to build one TDC channel. Precise sampling clocks are provided by a special clock buffer, BUFIO.

Figure 1: FPGA TDC clock scheme for single channel.

Two clock groups are managed by the Multi-Mode Clock Manager (MMCME2) core. Two outputs of the ISERDESE2 are sampled using fabric (general purpose) flip-flops, driven by the fabric clock, provided by global clock buffer (BUFG) and two outputs are sampled using BUFIO buffers propagated to ISERDESE2 cores. There is no way to calculate real phase shift between fabric clock signals and BUFIO clocks. Therefore, to set the required phase shift between two groups of clocks, one pair of parallel-to-serial converter (OSERDESE2), driven by BUFG and serial-to-parallel converter driven by BUFIO clocks is used. The phase alignment is performed by scanning the phase of the global clock while comparing OSERDESE2 output pattern with ISERDESE2 input pattern. The goal is to set the phase of the global clock in the middle point between two unstable phase ranges. Each FPGA bank has its own phase alignment because the BUFIO network is local in each bank. All MMCME2 cores use a single 125 MHz source clock provided by White Rabbit system synchronous to the experiment data acquisition, which allows absolute time measurements in all detectors in the BM@N experiment.

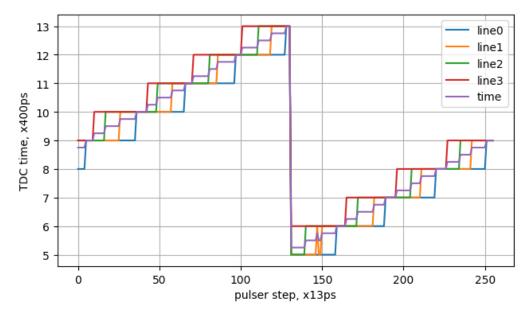

In order to decrease high processing frequency (625 MHz), two 4-bit samples from serial-to parallel converter are composed in 8-bit vector at half of the initial frequency. The vector's pattern represents the last 3.2 ns of the input signal. The outputs of the 4 sampling circuits are connected to the TDC logic core, which performs the final time calculations at 312.5 MHz clock frequency. The sampling results from all four circuits are shown in the figure 2. The minimum

detected pulse length for the current version of the TDC logic is 6.2 ns and the dead time is 9.6 ns. These values can be reduced down to 1.6 ns each if needed. The current values are sufficient for the HGND detector event rate and dead time and the performance will not be limited by the TDC readout.

The maximum number of the TDC channels that can be implemented in an FPGA is equal to a total number of available LVDS inputs and input logic (ILOGIC) resources. The Kintex 7 FPGA single bank allows to create 12 TDC channels: 24 LVDS input lines and 48 ILOGIC blocks of 50 available. One additional ISERDES2 - OSERDES2 pair is required in each FPGA bank for phase alignment. The xc7k160tffg676 FPGA will be used for the HGND detector readout board with approximately 84 TDC channels per FPGA. The single readout board with 3 FPGAs will hold 250 channels. In total 8 boards will provide all 2000 detector channels of the HGND.

Figure 2: Four TDC lines and resulting time dependence on the pulse time shift are shown. Pulses are generated by FPGA MMCM synchronous to TDC clock with the phase step of 12.5ps. The single scan pass was taken with a digital FPGA logic analyzer.

# **3** TDC time alignment

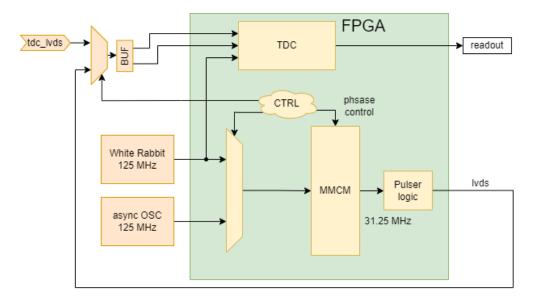

The input delay (IDELAY) FPGA primitive provides controllable delay for each TDC sampling circuit. The IDELAY block is controlled by the DLL (delay locked loop) in the IDELAYCTRL primitive. Each IDELAY block has the delay range from 0 to 31 steps. The DLL control clock with a frequency of 402.7 MHz sets the delay step value to 38.8 ps. Thus, it ensures the closest to 100 ps TDC relative lines delays:  $104 (13 \times 38.8 - 400)$ ,  $194 (5 \times 38.8)$  and  $298 (18 \times 38.8 - 400)$  ps available in FPGA PLL (phase locked loop) generated from the source clock of 125 MHz. The TDC alignment procedure is performed using an external LVDS multiplexer which connects each TDC channel to the pulse generator. The pulse generator is based on the FPGA MMCM block and it can generate pulses synchronously or asynchronously to the TDC clock with 12.5 ps/step precision phase shift. The schematic of the pulse generator for TDC calibration is presented in figure 3.

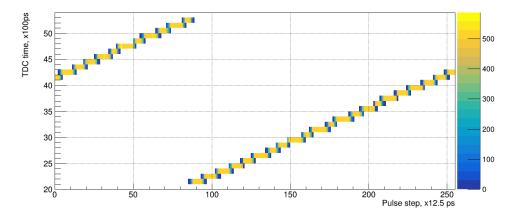

The main goal of the calibration procedure is to provide 100 ps relative TDC lines alignment with 200 ps shift in each LVDS pair. The delays between the TDC lines, which are higher than 400 ps, are aligned digitally in the logic. The TDC time scan with pulses synchronous to TDC clock with 12.5 ps step is presented in the figure 4. Such synchronous time scan is used for the differential nonlinearity correction performed in software in a semi-manual manner. The differential nonlinearity correction will be implemented later in FPGA and combined with the TDC delay calibration procedure.

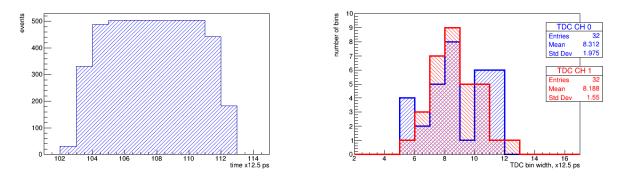

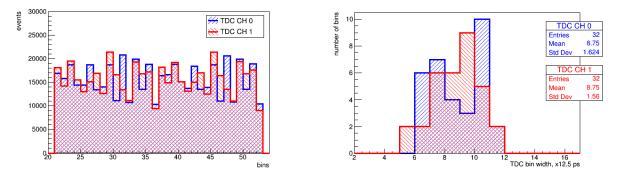

The typical TDC bin profile is shown in figure 5 (left). The distribution of bins width taken on the profile amplitude level of 30% for both channels is presented in figure 5 (right). The TDC bins width measured with pulses asynchronous to the TDC clock (code density test [7]) is presented in figure 6. The number of measured events in each TDC bin from pulses asynchronous to TDC clock is shown in the figure 6 (left). Considering that probability to have asynchronous pulse in the bin is directly proportional to the bin width. The bin width can be calculated with equation 1 where  $\tau_{bin}$  is the bin width,  $N_{bin}$  is the number of events collected in the bin, M is the total number of bins and  $N_{tot}$  is the total

Figure 3: The scheme of TDC calibration pulse generator.

Figure 4: The TDC time dependance on pulse time shift. Pulses are generated by FPGA MMCM synchronous to TDC clock, the time step is 12.5 ps. Data was taken with PC readout, 1000 events per single time shift step.

number of events in all bins. If all bins have the same number of events then all bins widths will be set to 100ps. The figure 6 (right) shows calculated TDC bins distribution. The method based on bin profile taken with synchronous pulses has the same result as the method of code density test taken with asynchronous pulses. Both measurements shows  $1.6 \times 12.5 = 20 \ ps$  RMS of the TDC bin width distribution. The main contribution to the TDC bin width distribution is the TDC line delay alignment step of 38.8 ps.

$$\tau_{bin} = \frac{N_{bin}M}{N_{tot}} \cdot 100ps \tag{1}$$

### 4 TDC and readout test

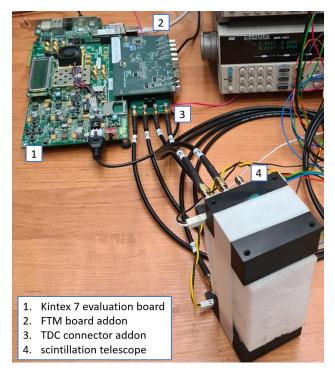

The Xilinx Evaluation board KC705 has been used for the FPGA TDC firmware developments. The FTM (FIT Test Module) board [8] with the TDC addon is connected to the FMC (FPGA Mezzanine Card) connectors. The TDC addon board holds SMA connectors and the LVDS lines multiplexers. The FPGA evaluation board sends the data to the PC via Ethernet using the IPbus FPGA core [9]. In order to test the TDC performance, the telescope setup consisting of the two scintillation detectors (cells) has been used. The cells of size  $40 \times 40 \times 25 \text{ mm}^3$  are placed at the distance of

Figure 5: The TDC bins width measured with pulses synchronous to the TDC clock. Left: Typical TDC bin profile taken with synchronous time scan. Right: the TDC bin width distribution for both TDC channels. The bin width value taken on the amplitude level is 30% in the bin profile.

Figure 6: The TDC bins width measured with pulses asynchronous to the TDC clock. Left: Asynchronous pulses distribution by TDC bins for both channels. Right: TDC bin width distribution calculated by considering that probability to have an asynchronous pulse in the bin is directly proportional to the bin width.

10 cm. Each cell contains the SiPM EQR15 11-6060D-S coupled with a scintillator produced at JINR. The SiPM is soldered on PCB with the preamplifier and the threshold comparator with LVDS output. Each channel of LVDS line is splitted on TDC addon to provide 4 single TDC lines. The photo of the test setup is shown in figure 7.

The time resolution measurements with the FPGA TDC prototype board were performed with the 280 MeV electron beam on the "Pakhra" synchrotron in LPI (Moscow, Russia). The time resolution was also measured using a 12-bit @ 5 GS/s CAEN DT5742 digitizer to read-out. The figure 8 shows the time difference distribution of two cells measured with CAEN digitizer (left) and the FPGA TDC prototype board (right). The single cell time resolution is  $201/\sqrt{2} = 142 \ ps$  (CAEN) and  $207/\sqrt{2} = 146 \ ps$  (TDC).

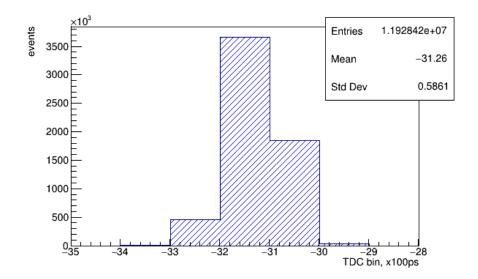

The time resolution of the FPGA TDC was measured with the data generator DG2040 (Cycle-to-Cycle Jitter 5ps). The delay scan between the two FPGA TDC channels was done with 10 ps step in the range from -3 to 3 ns. The corrected time difference distribution according to results of this scan is shown in figure 9. The RMS per channel is  $59/\sqrt{2} = 42 \ ps$ .

## 5 Conclusions

The FPGA TDC with a 100 ps bin width based on the Kintex-7 input serial-to-parallel converter with oversampling capability and programmable delay has been developed. The TDC design was developed with Xilinx recommendations, and it uses only documented features of the FPGA within its specifications. The time resolution of the TDC channel measured with the data generator DG2040 (Cycle-to-Cycle Jitter 5ps) is 42 ps. The developed TDC is based on the asynchronous oversampling with the FPGA primitive ISERDESE2. It shows good results in terms of time resolution and FPGA resources utilization, in comparison to the multi-phase clock sampling architecture of the FPGA TDC design [10]. The FPGA TDC board prototype was tested with scintillation detectors on electron beam of "Pakhra" synchrotron in LPI (Moscow, Russia). The measured time resolution of the scintillation detector with the FPGA TDC

Figure 7: The photo of the test setup.

Figure 8: The time difference distributions of two cells of telescope measured with CAEN digitizer (left) and the FPGA TDC prototype board (right).

board prototype is 146 ps which is in a good agreement with the time resolution measured with 12-bit @ 5 GS/s CAEN DT5742 digitizer (142ps). The developed TDC based on the xc7k160tffg676 FPGA will be used in the HGND readout boards for the BM@N experiment located on the Nuclotron extracted ion beams at JINR, Dubna, Russia.

## 6 Acknowledgements

This work was carried out at the Institute for Nuclear Research, Russian Academy of Sciences, and supported by the Russian Scientific Foundation grant №22-12-00132.

Figure 9: The time difference distribution between two FPGA TDC channels measured with the data generator DG2040 (Cycle-to-Cycle Jitter 5ps).

## References

- [1] Mikhail Kapishin. Heavy Ion BM@N and MPD Experiments at NICA. JPS Conf. Proc., 32:010093, 2020.

- [2] Peter Senger. The heavy-ion program at the upgraded Baryonic Matter@Nuclotron Experiment at NICA. *PoS*, CPOD2021:033, 2022.

- [3] F. Guber et al. Development of High Granular Neutron Time-of-Flight Detector for the BM@N experiment. 9 2023.

- [4] F. Guber, A. Ivashkin, N. Karpushkin, A. Makhnev, S. Morozov, D. Serebryakov, V. Baskov, and V. Polyansky. Measurement of Time Resolution of Scintillation Detectors with EQR-15 Silicon Photodetectors for the Time-of-Flight Neutron Detector of the BM@N Experiment. 9 2023.

- [5] J Serrano, P Alvarez, M Cattin, E Cota, J Lewis, Pedro Moreira, T Wlostowski, G. Gaderer, P. Loschmidt, J Dedic, R Bär, T Fleck, M Kreider, Cesar Prados, and S Rauch. The white rabbit project. 11 2009.

- [6] Marc Defossez. XAPP523: LVDS 4x Asynchronous Oversampling Using 7 Series FPGAs and Zynq-7000 AP SoCs. XILINX, v1.1 edition, May 2017.

- [7] Rui Machado, Jorge Cabral, and Filipe Serra Alves. Recent Developments and Challenges in FPGA-Based Time-to-Digital Converters. *IEEE Trans. Instrum. Measur.*, 68(11):4205–4221, 2019.

- [8] D. Finogeev, T. Karavicheva, D. Serebryakov, A. Tikhonov, W. H. Trzaska, and N. Vozniuk. Readout system of the ALICE Fast Interaction Trigger. *JINST*, 15(09):C09005, 2020.

- [9] C. Ghabrous Larrea, K. Harder, D. Newbold, D. Sankey, A. Rose, A. Thea, and T. Williams. IPbus: a flexible Ethernet-based control system for xTCA hardware. *JINST*, 10(02):C02019, 2015.

- [10] L. N. Cojocariu, D. Foulds-Holt, F. Keizer, V. M. Placinta, and S. Wotton. A multi-channel TDC-in-FPGA with 150 ps bins for time-resolved readout of Cherenkov photons. *Nucl. Instrum. Meth. A*, 1055:168483, 2023.