## Fabrication of a Silicon Electron Multiplier sensor using Metal Assisted Chemical Etching and its characterisation

Marius Mæhlum Halvorsen<sup>a,b,\*</sup>, Victor Coco<sup>a</sup>, Paula Collins<sup>a</sup>, Heidi Sandaker<sup>b</sup>, Lucia Romano<sup>c,d</sup>

<sup>a</sup>CERN EP-LBD, Esplanade des Particules 1, Meyrin, 1211, Switzerland

<sup>b</sup>University of Oslo, Department of Physics, , Oslo, 0315, Norway

<sup>c</sup>Institute for Biomedical Engineering, University and ETH Zürich, 8092, Zürich, Switzerland

<sup>d</sup>Paul Scherrer Institute, Forschungsstrasse 111, CH-5232, Villigen, Switzerland

### Abstract

The Silicon Electron Multiplier (SiEM) sensor is a novel sensor concept that enables charge multiplication by high electric fields generated by embedded metal electrodes within the sensor bulk. Metal assisted chemical etching (MacEtch) in gas phase with platinum as a catalyst has been used to fabricate test structures consisting of vertically aligned silicon pillars and strips on top of a silicon bulk. The pillars exceed 10  $\mu$ m in height with a diameter of 1.0  $\mu$ m and are arranged as a hexagonal lattice with a pitch of 1.5  $\mu$ m. Electrical characterisations through current – voltage measurements inside a scanning electron microscope and a climate chamber have demonstrated that the MacEtch process is compatible with active media and p–n junctions.

Keywords: Silicon sensors, Timing detectors, Silicon electron multiplier, Charge multiplication, Metal assisted chemical etching

### 1. Introduction

The next generation of innermost tracker detectors will need sensors that can cope with extreme radiation environments. Both the instantaneous and integrated luminosity will increase. Sensors in an FCC-hh environment will demand radiation hardess approaching  $1 \times 10^{18}$  1 MeV n<sub>eq</sub>cm<sup>-2</sup>, while needing to provide and maintain a time resolution of tens of pico seconds [1]. Today's most prominent silicon sensor technologies fall into the categories of planar sensors, Low Gain Avalanche Diodes (LGADs) and 3D sensors, which can all in principle provide a sufficient time resolution. Planar sensors have demonstrated operation and signal extraction at a fluence of  $1.6 \times 10^{17}$  1 MeV n<sub>eq</sub> cm<sup>-2</sup>, however the collected charge is significantly reduced due to trapping [2]. Time resolution below 100 ps is challenging to exploit using low power readout electronics due to the low signal and consequently relatively large jitter [3, 4]. The 3D sensors have a time resolution in the order of some tens of pico seconds as they benefit both from the large and fast signal due to the large charge generating volume and small drift distances, but have, however, a high capacitance and reduced fill factor for perpendicular tracks [5, 6, 7]. Lastly, LGADs have an excellent time resolution, but their gain degrades after irradiation and diminishes towards  $2.5 \times 10^{15}$  1 MeV n<sub>eq</sub> cm<sup>-2</sup>. For higher fluences, they display similar characteristics to planar detectors [8, 9].

The Silicon Electron Multiplier (SiEM) is a sensor concept that uses metal electrodes embedded within the silicon substrate. These electrodes can be biased to create high electric field regions in which charge multiplication occurs, providing large signals which can be read out with an excellent time resolution. Because the high field region is generated by metal electrodes rather than by doping, the gain is not expected to degrade by acceptor removal when the SiEM is irradiated. The bulk region where the charge is generated has no inefficient areas whatever the track angle. The SiEM's expected performance and properties were studied with the means of simulation in [10].

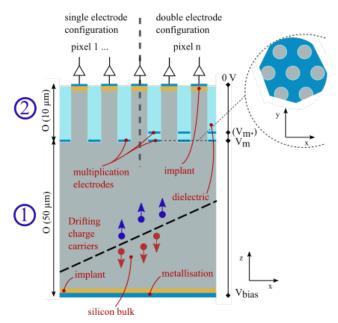

Figure 1 illustrates the implementation of the concept. It comprises a silicon bulk region  $\oplus$  and a region with silicon pillars and one or more multiplication electrodes D.

Based on the simulations in [10], the pillars should have a height of ~10  $\mu$ m, and be densely packed to minimize the charge carrier drift path inhomogeneities. This will also ease the full bulk depletion below the multiplication electrode. They should be thin, ~2  $\mu$ m, for the electric field not to attenuate too much towards the center of the pillar. The multiplication electrodes can be seen in dark blue colors at the bottom of the trenches. They can be made with different geometrical properties and operated with different biasing configurations. Two geometrical configurations have been studied in simulations, with both single and double multiplication electrodes.

In the single electrode configuration (Figure 1, left) the gain region is generated by the high field between the multiplication electrode biased at the potential  $V_m$  and the readout electrode at ground. In the double electrode configuration (Figure 1, right) a second buried multiplication electrode is added and biased at  $V_{m*}$ . The high electric field region is in this case created in the pillar by the difference in potential between the two buried electrodes. According to TCAD simulations, gain is achievable in both configurations, but the field configurations differ such that

<sup>\*</sup>Corresponding author at: CERN, Esplanade des Particules 1,1217 Meyrin, Switzerland. E-mail address: marius.maehlum.halvorsen@cern.ch

Preprint submitted to Nuclear Instrumentation Method A

the constraints on the materials are not the same. With the main voltage drop between  $V_m$  and  $V_{m*}$ , a high field would be generated inside the dielectric, between the electrodes, and a milder field inside the silicon, while a single electrode configuration would be the opposite. An optimal geometry for a single electrode configuration would be densely arranged tall pillars. They should be tall in order to have a long high field region, which would yield more charge multiplication, as discussed in [10]. However, they should not be too tall as the amount of siliconoxide interface charge increases which degrades the device performance. A double electrode geometry can similarly be optimised with the separation of the multiplication electrodes, and should not be too separated to maintain the benefits of the field configuration.

Figure 1: Schematic description of the SiEM sensor. It consists of a depleted silicon bulk region  $\oplus$  adjacent to a region  $\oslash$  made of silicon pillars (or strips). In between the pillars one or two metal electrodes can be implemented. The electrodes are biassed by  $V_m$  and  $V_m*$  and creates a high electric field region in  $\oslash$ . When an ionising particle passes through  $\bigoplus$ , primary electrons are generated and drift toward  $\oslash$  where they get enough energy for impact ionisation and induce an amplified signal while drifting towards the readout electrode.

Two methods are considered for fabrication: Metal Assisted Chemical Etching (MacEtch) and Deep Reactive Ion Etching (DRIE). The latter benefits from being a mature, industry standard technology, but has inherent defects such as ion induced defects and limitations due to scalloping, bottling, tapering, undercuts and aspect ratio dependent etching rate [11, 12]. Metal Assisted Chemical Etching on the other hand is a rather recent technology, discovered in 2000 [13]. It uses a metal catalyst to locally enhance the dissolution rate of silicon in the presence of an oxidant and an etchant. This accelerated etching gives an anisotropic pattern transfer that can yield very large aspect ratios (10 000:1) and small feature sizes (~10 nm) [14]. The process has applications such as grating fabrication for X-ray optics [14], photovoltaics [15], creating vias [16], and anode batteries [17]. To the best of the authors' knowledge, MacEtch structures have not been used, until now, in active media with pn junctions. I–V characteristics [18] and electrochemical properties [19] of MacEtch nanowires have been reported, indicating the phenomenon of charge carrier trapping at surface states.

The MacEtch process can be suitable for the SiEM not only because of the small feature sizes, but also due to the etching catalyst serving as a multiplication electrode during the electrical operation of the device. MacEtch could thus reduce the amount of processing steps, and would particularly be suitable for a single electrode configuration. In this paper the fabrication and characterisation of a SiEM demonstrator made with the MacEtch process is described.

### 2. Metal Assisted Chemical Etching for SiEM

In a MacEtch process, a metal mask, typically consisting of Au, Pt or Pd, is patterned onto a semiconductor substrate (Si) and works as catalyst for a local redox reaction occurring in presence of an acid etchant (HF) and an oxidant ( $H_2O_2$  or  $O_2$ ). On contact with the metal, the oxidant is reduced by injecting holes into the semiconductor substrate, changing the oxidation state of the substrate and enabling the subsequent removal of the substrate material by the etchant. The MacEtch of silicon can be realized using HF in liquid [13] or in vapor [14, 20] and different oxidants. In our experiment, the sample is normally placed above an HF containing solution, such that HF evaporates from the liquid tank and the oxidant is supplied from the air flow on the sample. The following reactions occur:

$$O_2 + 4 H^+ + 4 e^- \longrightarrow 2 H_2 O (at catalyst)$$

(1)

$$\text{Si} + 4 \text{h}^+ + 6 \text{HF} \longrightarrow \text{SiF}_6^{2-} + 6 \text{H}^+ (\text{at silicon})$$

(2)

Silicon can be dissolved directly (Eq. 2) forming fluorides species that are released as  $SiF_4$  in gas phase or via an indirect path, forming  $SiO_2$  [14]. As the Si is removed beneath the catalyst, the metal pattern sinks and contacts unreacted material, continuing the reaction to form a negative image of the metal mask.

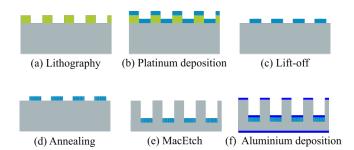

The main processing steps for the SiEM fabrication using MacEtch are summarised in Figure 2. The first step (a) is the pattern application by UV-lithography. This is followed by a metal thin film evaporation (b). After lift-off (c), there is an annealing step to dewet and make the catalyst adhere to the silicon, (d). In step (e) the sample is exposed to HF for the etching, and at the end of the fabrication, (f), a front and backside metallisation is performed for electrical contact.

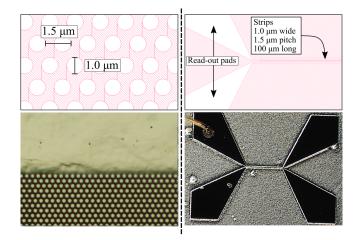

The fabrication was performed on a high resistivity (4– 8 k $\Omega$  cm) 200 µm thick n-type (1 0 0) wafer already implanted with boron at the frontside to form the p–n junction and phosphorous at the backside for ohmic contact. A direct write laser lithography system was used to pattern two different structures (*a*): circles of 1.0 µm diameter in an hexagonal lattice with a pitch of 1.5 µm and strip-like geometries with the same pitch and width, but terminated with read-out pad allowing easier bonding and probing. The same processing steps were followed for both patterns. The dimensions were chosen to benefit from

Figure 2: Overview of the main steps in the fabrication of the SiEM using MacEtch.

the MacEtch capabilities of small feature sizes and large aspect ratios, which would ease the depletion, give less lateral field attenuation inside the pillars and extended the high field regions.

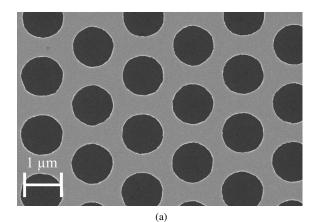

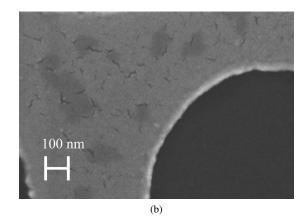

In this study Pt has been chosen as a catalyst due to its excellent catalytic activity, and good adhesion due to the formation of silicides (PtSi and  $Pt_2Si$ ) at the interface. The silicides are formed by annealing at the interface after lift-off, step (c) and (d). The thermal treatment also induceds the Pt to self-assemble, creating nano-pores, a phenomenon referred to as dewetting [21]. The nano-pores enable a more uniform mass transport of the reactants across the pattern, which leads to a more uniform etching. Dewetting is preferred on an insulating substrate, therefore Pt is evaporated onto the sample without the removal of the native oxide [14]. Scanning electron microscope (SEM) images of the sample after the Pt-deposition and lift-off can be seen in Figure 3a and the nano pores after dewetting can be seen in Figure 3b.

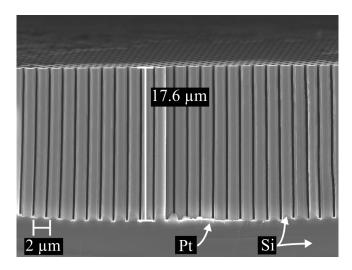

Previous work [14, 22] has demonstrated that geometries similar to what is needed for the SiEM can be produced both by etching in liquid and gas phase (step (e)). While liquid etching is generally more prevalent, gas etching has certain advantages. In particular, it prevents the agglomeration of nano-wires, produced by the nano-pores mentioned before, which could lean onto the pillars and distort the fields, make shorts or undesired electrical states. In addition, the broad parameter space allows the etching quality to be enhanced by tuning the temperature, the flow of oxygen supply and the etching composition to optimise the etch-rate uniformity and - remarkably - avoid micro-porosity [23], which would introduce undesired defects in the device. Etching in gas state is thus chosen for this production. The sample was mounted on a heated sample holder and suspended above a HF solution. The temperature was kept at 55 °C, which is found to be the best processing temperature considering etching uniformity, porosity reduction and agglomeration [14]. The resulting pillars after ~1 h etching can be seen in Figure 4.

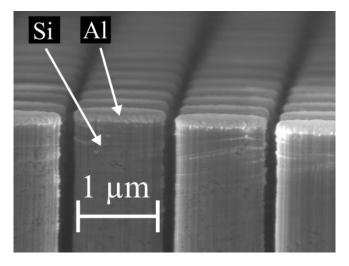

For the sensor prototype a front and backside metallisation is needed in order to contact, deplete and read out signals. It was achieved using evaporated aluminium, which can be seen in Figure 5. Such an evaporation of aluminium may leave residuals of aluminium close to the top of the pillars, which could be problematic if conducting channels cross and shorten the p– n junction. For a demonstrator this approach is sufficient, but alternative approaches could be applied for later productions,

Figure 3: (a) Plan view of platinum patterned silicon sample after lift-off. (b) Nano pores due to self assembly of Pt.

which are further discussed in Section 4. The native oxide was removed directly before the aluminium deposition in order to lower the metal–semiconductor interface barrier.

Figure 4: Cross section view of the silicon pillars after etching. The Pt thin film is visible at the bottom of the pillars.

Figure 5: Cross section view of the top part of the pillar with aluminium deposited.

Figure 6: Snapshots of lithography mask and plan view images at optical microscope of the fabricated pillars (left) and strips (right). One of the strip readoutpads is bonded to a carrier board through gold ball wire bonding.

### 3. Prototype details and electrical characterisation

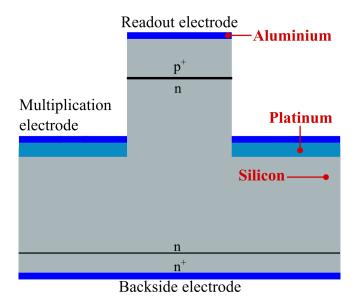

Images of the fabricated strips and pillars along with their patterns can be seen in Figure 6. The prototypes contain three electrical contact points: the readout electrode, the multiplication electrode and the backside electrode, mapping the single electrode configuration of Figure 1. The electrodes, doping and material composition of the prototype are illustrated in Figure 7. The readout and backside electrodes are deposited directly on the  $p^+$  and  $n^+$  implants, giving ohmic contacts. The multiplication electrodes consist of the platinum catalyst and evaporated aluminium. Pt and also Al in direct contact with high resistivity n-type silicon are known to make a rectifying contact, a Schottky contact [24].

Two setups have been used to assess the electrical properties of the structures through their current–voltage (I–V) characteristic. A probe system installed within a scanning electron microscope (SEM) was used after production of the sample. It allowed both the strips and pillar structures to be characterised.

Figure 7: Schematic illustration of the prototype with the material type and contacts described. Dimensions are not to scale.

The strip structures could be further investigated in an I–V setup installed in a climate chamber after the structure had been connected to a carrier board with gold ball bonding. Measurements from these two setups are presented in the following.

### 3.1. Measurements within SEM probe station

An SEM Zeiss Supra VP55 equipped with Kleindiek Nanotechnik micro-manipulators with sub-micrometer tungsten needles and a Keithley 236 source measure unit was used to probe the I–V characteristics of single pillars and of the strip structures.

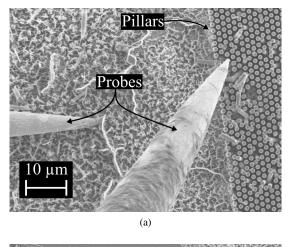

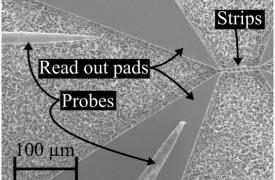

The sample was mounted on a glass plate to electrically isolate the sensor. The needles were lowered in several steps during which the focus was done successively on the needle tips and on the sample until contact with the sample was achieved. One needle was used to contact the readout electrode and one to contact the multiplication electrode. Once the needles were in place, the electron beam of the SEM was turned off in order to not interfere with the electrical characterisation of the structures. This biasing configuration was used to probe the multiplication region,  $\mathbb{Q}$  from Figure 1.

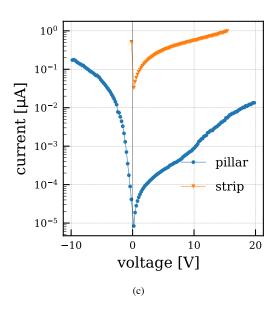

Figure 8a shows the probing of exactly one single pillar right before the I–V measurements were taken. The strip probing is shown in Figure 8b, where the needle was placed on the readout pad of the strip. The I–V measurements of these two structures are shown in Figure 8c. The current of both structures display similar trends, with a slow rise towards positive voltages (reverse bias) and a steeper rise in current towards negative voltages (forward bias), typical for diodes.

However, the currents are rather large and it is not possible to identify a region of saturation current as in a standard diode. The current consists of several contributions, in particular the bulk generated, oxide interface generated and impact ionisation generated ones. The bulk generated and oxide generated currents mainly depend on the generation rates of the defects, their

(b)

Figure 8: Measurements with probe station inside a scanning electron microscope. The images are taken just before the voltage scan. (a) shows the contact with a single pillar, and (b) shows the SEM image of the strip device. (c) shows the I–V curve for both the strip and pillar. The strip curve stops at lower voltages because it reaches compliance of 1  $\mu$ A quicker than the pillar. The positive output of the sourcemeter is applied on the multiplication electrode and a the negative on the readout electrode

concentrations and the depletion volume for bulk generated and interface area for interface generated currents. The impact ionisation current depends mainly on the electric field.

The rather high leakage current compared to conventional diodes [25] can be explained by the larger silicon–oxide interface areas and high defects concentration in these regions. These additional states at the interface would inject charge carriers into the system [26].

The observed increase in leakage current for both structures is likely to originate from impact ionisation. This is because an increase in potential, with the given biasing scheme, would mainly enhance the field between the readout and multiplication electrode and not extend the depleted volume meaningfully. According to TCAD simulations the strips and pillars are mostly depleted even before biasing.

Both desired and undesired impact ionisation can occur and contribute to the high leakage current. The latter can originate from imperfections in the pattern transfer, especially due to the dewetting that can give sharp edges and thus local high electric fields. Also the electrode edge in direct contact with the strips and pillars can give edge effects and avalanche regions in its proximity. The sharp edges could be smoothed by an additional oxidation step. It could also further separate the multiplication electrode from the pillar and strip which would reduce field extremities to give milder operation conditions inside the silicon.

Compared to the pillar, the strip gives a significant higher current,  $\sim 10^3$  times the magnitude. It can be explained by the much larger feature sizes, substantially affected by the read-out pad (see Figure 8b). However, the pure volumetric ratio of the strip and pillar is  $5.4 \times 10^5$ , which is larger than the measured difference. The oxide interface area ratio between the strip and pillar is  $2.1 \times 10^3$ , which corresponds more to the observed difference. This indicates that the surface generated current may dominate compared to the bulk. Further investigations with dedicated test structures are planned in order to better understand and separate the different current contributions.

### 3.2. One dimensional I–V characterisation in climate chamber

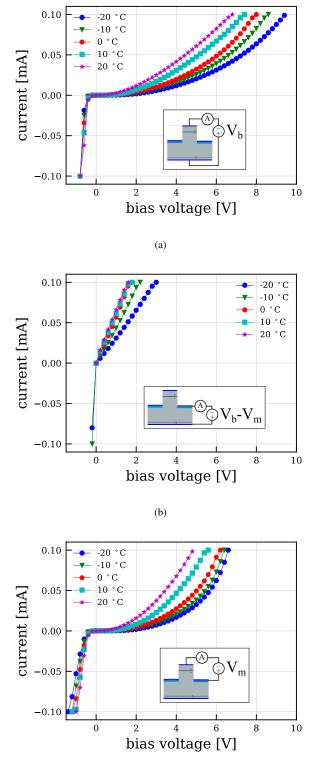

For the measurements in the climate chamber the readout pads of the strips were bonded to a carrier board by gold ball wire bonding, see right part in Figure 6. Their I–V characteristics were measured inside a climate chamber at five different temperatures, ranging from -20 °C to 20 °C. In this section, the I–V measurements of every possible two contact configuration, with the third contact left floating, are discussed. The measurements were taken using a Keithley 2410 sourcemeter and are shown in Figure 9.

Figure 9a shows the I–V between the readout electrode and backside electrode. It is expected to behave as a p–n junction and indeed it shows a much quicker increase in current towards negative voltages than positive voltages, typical of the p–n junction. It also shows a reduction of current with temperature, which is expected due to the lower generation rates.

Figure 9b shows the measurements while the multiplication and backside electrodes are biased. It is expected that in this case the currents display the characteristic of a Schottky diode, and indeed rectifying behaviour can be seen in the Figure 9b. In addition, compared to the I–V of the p–n junction discussed

(c)

Figure 9: I–V measurements between pairs of contacts at different temperatures. (a) Shows the I–V when biasing the readout and backside electrode. (b) Shows the I–V when biasing the multiplication and backside electrode. (c) Shows the I–V when biasing the readout and multiplication electrode. All measurement points until the ampermeter maximum current setting are displayed.

above, this current rises much more quickly. This is attributed to both the fact the electrode area is larger by a factor of around  $2 \times 10^3$ , and the fact the Schottky diodes inherently have larger leakage currents.

The last I-V characteristic measured is performed between the readout and multiplication electrode, thus the same as the one performed in the SEM. An equivalent representation of this system would be a p-n junction in series with a Schottky contact with the opposing polarity. The response and schematics of the system can be seen in Figure 9c. Again, the diode characteristic is clear. Compared to the p-n junction measurement using the readout and backside electrode in Figure 9a, the reverse bias currents rises faster and reaches the sourcemeter compliance of  $100 \,\mu\text{A}$  earlier. This can be attributed to the fact that in this structure the electric field mainly develops in the strip, between the readout and the multiplication electrodes. Thus the possible depth of the depleted region is 30 times smaller than when the readout and backside electrodes are biased. The field magnitude is thus expected to be higher, yielding more impact ionisation and thus larger current.

From the rectifying direction it can be seen that the p-n diode dominates the current characteristics. The Schottky diode is a majority carrier device whose forward I–V characteristic is mainly governed by thermionic emissions of electrons from the silicon conduction band to the metal. As most of the free electrons in the conduction band are evacuated due to the depletion, the Schottky forward current is limited by the reverse leakage current of the p-n junction.

It can be seen that towards negative voltages, the current drops are less abrupt than in figure 9a. This feature can be explained by the rectifying configuration of the Schottky contact, as it is in reverse mode once the p–n junction is in forward.

Compared to the measurements done in the SEM, the currents are substantially larger. Several factors can be influencing this difference. The SEM measurements were performed within three days after fabrication, while the ones measured in the climate chamber were measured a few months after production. During this time, growth of oxides and accumulation of defects at the interface can have occurred. In addition the gold ball wire bonding and mounting of sample onto the carrier board required some additional treatment steps (heating, dicing) that were not necessary in the SEM measurements. The samples originated from two different batches, made a few days apart, and small differences in the quality of, for instance, the metallisation and etching, can have occurred.

# 3.3. Two dimensional I–V characterisation inside climate chamber

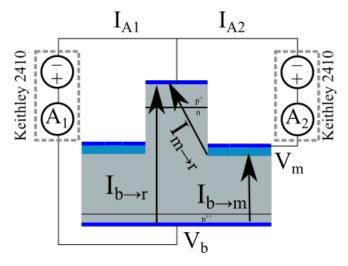

The SiEM sensor with a single amplification electrode is meant to be operated by choosing the backside electrode bias  $V_b$ such that the structure is depleted and the multiplication electrode bias  $V_m$  such that the field is large enough to generate impact ionisation and thus amplify the signal charge. Hence all three electrodes must be contacted for the operation of the device. The interplay and current response when all the three electrodes are contacted and biased must therefore be understood. To do so  $V_m$  and  $V_b$  are varied in a "2D" I–V characterisation with the readout electrode kept at ground potential.

Two Keithley 2410 sourcemeters were used to bias and measure the system. Their ground outputs were connected together to the readout electrode. One of the sourcemeters biases and measures the current  $I_{A_1}$  at the backside electrode while the other biases the multiplication electrode and measures  $I_{A_2}$ . The schematics of the measurement, the potentials and the measured currents can be seen in Figure 10. The arrows in the figure indicate the different current components present in the system, where  $I_{b\to m}$  designates the current that flows from the backside to the multiplication electrode,  $I_{b\to r}$  is the current that flows from the backside electrode to the readout electrode and  $I_{m\to r}$ that flows from the multiplication electrode to the readout electrode.

Figure 10: Illustration of the two dimensional I–V measurements, where two Keithley 2410 sourcemeters are connected together at ground on the readout electrode. One sourcemeter is connected to the multiplication electrode and the other to the backside electrode. The three current components are also indicated in the figure.

By adding the two measured currents  $I_{A_1}$  and  $I_{A_2}$  one gets

$$I_{A_1} + I_{A_2} = I_{m \to r} + I_{b \to r},$$

(3)

thus the total current flowing to the readout electrode, without the contributions from  $I_{b\to m}$ .

The voltage scan is performed by setting the backside electrode to a potential  $V_b$ , and then scan  $V_m$  from 0 V to  $V_b$ . It is not scanned further as  $V_b - V_m$  would be negative, which corresponds to forward mode of the pure Schottky diode, and an abrupt forward current as seen in Figure 9b. The measurements are performed inside a climate chamber at -20 °C.

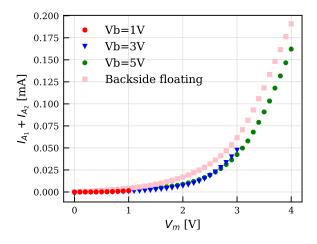

The total current through the readout electrode is plotted for the different bias configurations in Figure 11. The larger the bias voltage  $V_b$  on the backside electrode, the larger is the range under which the multiplication electrode can be biased without a forward bias to the pure Schottky diode. Increasing  $V_m$  increases the amount of impact ionisation in the strip and thus the current increases, following the argumentation in Section 3.1. On the other hand increasing  $V_b$  does not significantly increase

Figure 11: Two dimensional I–V measurements showing the total current through the readout electrode for a given  $V_b$ .

the current as it mainly impacts the region ① with relatively small fields. For all values of  $V_b$ , the total current at the readout is very close to the one when leaving the backside floating as in 9c. This shows further that the current at the readout electrode is dominated by the current in ② which is generated by the amplification of the charges in the strip due to the large electric field and defects along the strip interface.

The summed 2D voltage scans show a lower leakage current than the 1D voltage scan with the backside floating. One possible reason could be field modifications around the multiplication electrode due to the contribution of the backside electrode. Instead of a rather abrupt transition from the depleted region to the neutral region at the multiplication electrode edge, the field can extend further into the bulk and potentially give milder working conditions by the multiplication electrode. However further investigations both through simulations and experiments should be performed to better understand this observed effect.

### 4. Discussion and Future work

Results from the fabrication and characterisation of the Silicon Electron Multiplier sensor using Metal Assisted Chemical Etching have been presented demonstrating the fabrication approach along with the current response to different biasing configurations. Throughout the article possible shortcomings and new approaches have been introduced. This section aims to further discuss improvements and give an outlook for forthcoming studies of the SiEM.

*Metallisation:* A changed metallisation procedure could be implemented to avoid residual metal along the pillar wall that could potentially shorten the p–n junction. Approaches such as hot embossing of metal film [27] followed by a second lithography, or trench filling of dielectric before metal evaporation and a second lithography should limit this effect. These approaches would also allow several pillars to be grouped together, for instance to target a given readout ASIC pitch. Alternatively, a deep junction could be implemented into the starting wafer to ensure no metal channels cross the junction.

*Etching:* The silicon nano-wires, which result from the dewetting cracks in the Pt layer, can agglomerate when the aluminium is deposited. They can then lean onto the pillars, which could be a potential source of current noise. The nano-wires can however be minimised by increasing the Pt film thickness and etching in an oxygen rich environment, which should be used as a standard approach.

*Oxidation steps:* Sharp edges due to imperfections in pattern transfer and edge effects next to the multiplication electrode could be minimised by an oxidation step. This would smooth the interface, thus limiting both the high fields due to sharp edges and in addition separating the electrode from the etched out wall such that the fields and operation conditions in the silicon are milder.

*Pattern:* The first version of the pattern included a very large multiplication electrode. The extent of this electrode should be limited in future patterns to minimise the Schottky diode contribution.

*Material:* In the first production a high resistivity n-type wafer was used. A second production should use a p-type wafer in order to collect and multiply electrons.

*Measurements:* The next step of the electrical characterisation is to probe the sensor response to ionising radiation. Lasers and radioactive sources should be used to study pulse shapes, fill factor, collection efficiency and to make comparisons with simulations. A study should be performed to better understand the currents observed. Interface area scaling could be studied by using circular diode-like structures with different diameters. Defect spectroscopy, in particular between the multiplication electrode and readout electrode, should be performed to further understand the defects.

*Other fabrication approaches:* The production of a demonstrator using the Deep Reactive Ion Etching based process is currently ongoing. This approach has other constraints and benefits. There is no metal catalyst needed in the etching, which allows the introduction of a dielectric between the metal and silicon. Several electrodes can be introduced by consecutive deposition of metal and oxide layers. The same aspect ratios and feature sizes are however more challenging to achieve.

### 5. Conclusion

The first demonstrator of the Silicon Electron Multiplier sensor has been fabricated using metal assisted chemical etching (MacEtch). Electrical characterisations with two and three biasing points performed inside an SEM and a climate chamber have proven that the diode characteristics are preserved after processing, demonstrating the MacEtch compatibility with active media and a p–n junction.

### **Author Statement**

**Marius Mæhlum Halvorsen:** Investigation, Methodology, Writing - Original Draft, Visualization, Data Curation, Formal analysis.

**Victor Coco:** Supervision, Conceptualization, Funding acquisition, Writing - Review & Editing Paula Collins: Funding acquisition, Writing - Review & Editing

### Heidi Sandaker: Supervision

Lucia Romano: Supervision, Methodology, Project administration, Investigation, Resources, Writing - Review & Editing

### Acknowledgment

The authors thank the TOMCAT team with prof. M. Stampanoni (ETH Zurich) for facilitating the project at Paul Scherrer Institute; D. Marty, V. Guzenko, K. Vogelsang, K. Jefimovs for technical support in the PSI clean room facilities; Z. Shi, C. Lawley for useful discussions and help in the fabrication; A. Weber and D. Kazazis for support at SEM probe station; S. Tsujino for the source measure unit; C. Scarcella and J. Alozy for support with Gold Ball Wire Bonding; J. Haimberger for help useful discussions, help with measurements and careful proofreading; V. Gkougkousis for measurement software; M. van Beuzekom for useful discussions; CERN QARTlab for optical microscope. This work was funded by and carried out in the context of the CERN Strategic R&D Programme on Technologies for Future Experiment https://ep-rnd.web.cern.ch/ and has received funding from the European Union's Horizon 2020 Research and Innovation programme under GA no 101004761.

#### References

- [1]E. D. R. R. P. Group, The 2021 ECFA detector research and development roadmap, Tech. rep., Geneva (2020). doi:10.17181/CERN.XDPL.W2EX. URL https://cds.cern.ch/record/2784893

- [2]G. Kramberger, V. Cindro, I. Mandić, M. Mikuž, M. Zavrtanik, Charge collection studies on custom silicon detectors irradiated up to 1.6e17n<sub>e</sub>qcm<sup>-2</sup>, Journal of Instrumentation 8 (08) (2013) P08004. doi:10.1088/1748-0221/8/08/P08004.

URL https://dx.doi.org/10.1088/1748-0221/8/08/P08004

[3]N. Akchurin, V. Ciriolo, E. Currás, J. Damgov, M. Fernández, C. Gallrapp, L. Gray, A. Junkes, M. Mannelli, K. Martin Kwok, P. Meridiani, M. Moll, S. Nourbakhsh, S. Pigazzini, C. Scharf, P. Silva, G. Steinbrueck, T. T. de Fatis, I. Vila, On the timing performance of thin planar silicon sensors, Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment 859 (2017) 31–36. doi:https://doi.org/10.1016/j.nima.2017.03.065. URL https://www.sciencedirect.com/science/article/pii/

UKL https://www.scienceairect.com/science/article/pii/ S016890021730414X

- [4]G. A. Rinella, E. C. Gil, M. Fiorini, J. Kaplon, A. Kluge, F. Marchetto, M. E. M. Albarran, M. Morel, M. Noy, L. Perktold, S. Tiuraniem, B. Velghe, Test-beam results of a silicon pixel detector with time-over-threshold read-out having ultra-precise time resolution, Journal of Instrumentation 10 (12) (2015) P12016. doi:10.1088/1748-0221/10/12/P12016. URL https://dx.doi.org/10.1088/1748-0221/10/12/P12016

- [5]S. Parker, C. Kenney, J. Segal, 3d a proposed new architecture for solid-state radiation detectors, Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment 395 (3) (1997) 328–343, proceedings of the Third International Workshop on Semiconductor Pixel Detectors for Particles and X-rays. doi:https://doi.org/10.1016/S0168-9002(97)00694-3. URL https://www.sciencedirect.com/science/article/pii/ S0168900297006943

- [6]C. Betancourt, D. De Simone, G. Kramberger, M. Manna, G. Pellegrini, N. Serra, Time resolution of an irradiated 3d silicon pixel detector, Instruments 6 (1) (2022). doi:10.3390/instruments6010012. URL https://www.mdpi.com/2410-390X/6/1/12

- [7]G. Kramberger, V. Cindro, D. Flores, S. Hidalgo, B. Hiti, M. Manna, I. Mandić, M. Mikuž, D. Quirion, G. Pellegrini, M. Zavrtanik, Timing performance of small cell 3d silicon detectors, Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment 934 (2019) 26–32. doi:https://doi.org/10.1016/j.nima.2019.04.088. URL https://www.sciencedirect.com/science/article/pii/ S0168900219305704

- [8]G. Kramberger, M. Carulla, E. Cavallaro, V. Cindro, D. Flores, Z. Galloway, S. Grinstein, S. Hidalgo, V. Fadeyev, J. Lange, I. Mandic, G. Medin, A. Merlos, F. McKinney-Martinez, M. Mikuz, D. Quirion, G. Pellegrini, M. Petek, H.-W. Sadrozinski, M. Zavrtanik, Radiation hardness of thin low gain avalanche detectors, Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment 891 (11 2017). doi:10.1016/j.nima.2018.02.018.

- [9]E. L. Gkougkousis, L. C. Garcia, S. Grinstein, V. Coco, Comprehensive technology study of radiation hard lgads, Journal of Physics: Conference Series 2374 (1) (2022) 012175. doi:10.1088/1742-6596/2374/1/ 012175.

URL https://dx.doi.org/10.1088/1742-6596/2374/1/012175

- [10]M. M. Halvorsen, V. Coco, E. L. Gkougkousis, P. Collins, O. Girard, The silicon electron multiplier sensor, Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment 1041 (2022) 167325. doi:https://doi.org/10.1016/j.nima.2022.167325. URL https://www.sciencedirect.com/science/article/pii/ S0168900222006441

- [11]B. Wu, A. Kumar, S. Pamarthy, High aspect ratio silicon etch: A review, Journal of Applied Physics 108 (5), 051101 (09 2010). arXiv:https://pubs.aip.org/aip/jap/article-pdf/doi/ 10.1063/1.3474652/14067262/051101\\_1\\_online.pdf, doi:10.1063/1.3474652. URL https://doi.org/10.1063/1.3474652

- [12]S. Campbell, Fabrication Engineering at the Micro and Nanoscale, The Oxford Series in Electrical and Computer Engineering, OUP USA, 2008. URL https://books.google.ch/books?id=sUbhGAAACAAJ

- [13]X. Li, P. Bonn, Metal-assisted chemical etching in hf/h2o2 produces porous silicon, Applied Physics Letters 77 (16) (2000) 2572-2574. doi:10. 1063/1.1319191.

- [14]L. Romano, M. Kagias, J. Vila-Comamala, K. Jefimovs, L.-T. Tseng, V. A. Guzenko, M. Stampanoni, Metal assisted chemical etching of silicon in the gas phase: a nanofabrication platform for X-ray optics, Nanoscale Horiz. 5 (2020) 869–879. doi:10.1039/C9NH00709A.

URL http://dx.doi.org/10.1039/C9NH00709A

- [15]X. Li, Metal assisted chemical etching for high aspect ratio nanostructures: A review of characteristics and applications in photovoltaics, Current Opinion in Solid State and Materials Science 16 (2) (2012) 71–81, photonic Nanostructure Materials, Processing and Characterization. doi:https://doi.org/10.1016/j.cossms.2011.11.002. URL https://www.sciencedirect.com/science/article/pii/ S1359028611000830

- [16]L. Li, G. Zhang, C.-P. Wong, Formation of through silicon vias for silicon interposer in wafer level by metal-assisted chemical etching, IEEE Transactions on Components, Packaging and Manufacturing Technology 5 (8) (2015) 1039–1049. doi:10.1109/TCPMT.2015.2443728.

- [17]Z. Mihai-Robert, N. Hung, E. Moyen, Y. H. Lee, D. Pribat, Silicon nanowires for li-based battery anodes: A review, Journal of Materials Chemistry 1 (2013) 9566–9586. doi:10.1039/C3TA11714F.

- [18]R. Plugaru, E. Fakhri, C. Romanitan, I. Mihalache, G. Craciun, N. Plugaru, H. Árnason, M. Sultan, G. Nemnes, S. Ingvarsson, H. Svavarsson, A. Manolescu, Structure and electrical behavior of silicon nanowires prepared by mace process, Surfaces and Interfaces 33 (2022) 102167. doi:https://doi.org/10.1016/j.surfin.2022.102167. URL https://www.sciencedirect.com/science/article/pii/ S2468023022004357

- [19]F. Zaibi, I. Slama, N. Beshchasna, J. Opitz, M. Mkandawire, R. Chtourou, Effect of etching parameters on the electrochemical response of silicon nanowires, Journal of Applied Electrochemistry 52 (02 2022). doi:10.1007/s10800-021-01638-x.

- [20]L. L. Janavicius, J. A. Michaels, C. Chan, D. J. Sievers, X. Li, Programmable vapor-phase metal-assisted chemical etching for versatile

high-aspect ratio silicon nanomanufacturing, Applied Physics Reviews 10 (1) (2023) 011409. arXiv:https://pubs.aip.org/aip/apr/ article-pdf/doi/10.1063/5.0132116/16791936/011409\\_1\ \_online.pdf, doi:10.1063/5.0132116. URL https://doi.org/10.1063/5.0132116

- [21]S. Strobel, C. Kirkendall, J.-B. Chang, K. K. Berggren, Sub-10 nm structures on silicon by thermal dewetting of platinum, Nanotechnology 21 (50) (2010) 505301. doi:10.1088/0957-4484/21/50/505301.

URL https://dx.doi.org/10.1088/0957-4484/21/50/505301

- [22]L. Romano, J. Vila-Comamala, K. Jefimovs, M. Stampanoni, High-Aspect-Ratio Grating Microfabrication by Platinum-Assisted Chemical Etching and Gold Electroplating, Advanced Engineering Materials 22 (10) (2020) 2000258. arXiv:https:// onlinelibrary.wiley.com/doi/pdf/10.1002/adem.202000258, doi:https://doi.org/10.1002/adem.202000258. URL https://onlinelibrary.wiley.com/doi/abs/10.1002/ adem.202000258

- [23]O. J. Hildreth, D. R. Schmidt, Vapor phase metal-assisted chemical etching of silicon, Advanced Functional Materials 24 (24) (2014) 3827-3833. arXiv:https://onlinelibrary.wiley.com/doi/pdf/10.1002/adfm.201304129, doi:https://doi.org/10.1002/adfm.201304129.

URL https://onlinelibrary.wiley.com/doi/abs/10.1002/ adfm.201304129

- [24]S. Sze, K. Ng, Physics of Semiconductor Devices, Wiley, 2006. URL https://books.google.ch/books?id=o4unkmHBHb8C

- [25]A. Ruzin, S. Marunko, Current mechanisms in silicon pin structures processed with various technologies, Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment 492 (3) (2002) 411–422. doi:https://doi.org/10.1016/S0168-9002(02)01369-4. URL https://www.sciencedirect.com/science/article/pii/ S0168900202013694

- [26]S. Sze, Semiconductor Devices: Physics and Technology, Wiley, 2001.

- [27]L. Romano, J. Vila-Comamala, H. Schift, M. Stampanoni, K. Jefimovs, Hot embossing of Au- and Pb-based alloys for x-ray grating fabrication, Journal of Vacuum Science & Technology B 35 (6) (2017) 06G302. arXiv:https://pubs.aip.org/avs/jvb/article-pdf/ doi/10.1116/1.4991807/15869593/06g302\\_1\\_online.pdf, doi:10.1116/1.4991807.

- URL https://doi.org/10.1116/1.4991807