# Scalable communication for high-order stencil computations using CUDA-aware MPI\*

Johannes Pekkilä<sup>a,\*</sup>, Miikka S. Väisälä<sup>b</sup>, Maarit J. Käpylä<sup>a,c,d</sup>, Matthias Rheinhardt<sup>a</sup>, Oskar Lappi<sup>a,e</sup>

<sup>a</sup>Department of Computer Science, Aalto University, Konemiehentie 2, 02150 Espoo, Finland

<sup>b</sup>Academia Sinica, Institute of Astronomy and Astrophysics, Roosevelt Rd, 10617 Taipei, Taiwan

<sup>c</sup>Max Planck Institute for Solar System Research, Justus-von-Liebig-Weg 3, D-37077 Göttingen, Germany

<sup>d</sup>Nordita, KTH Royal Institute of Technology and Stockholm University, Roslagstullsbacken 23, SE-10691 Stockholm, Sweden

<sup>e</sup>Faculty of Science and Engineering, Åbo Akademi University, Tuomiokirkontori 3, 20500 Turku, Finland

#### **Abstract**

Modern compute nodes in high-performance computing provide a tremendous level of parallelism and processing power. However, as arithmetic performance has been observed to increase at a faster rate relative to memory and network bandwidths, optimizing data movement has become critical for achieving strong scaling in many communication-heavy applications. This performance gap has been further accentuated with the introduction of graphics processing units, which can provide by multiple factors higher throughput in data-parallel tasks than central processing units. In this work, we explore the computational aspects of iterative stencil loops and implement a generic communication scheme using CUDA-aware MPI, which we use to accelerate magnetohydrodynamics simulations based on high-order finite differences and third-order Runge-Kutta integration. We put particular focus on improving intra-node locality of workloads. Our GPU implementation scales strongly from one to 64 devices at 50%–87% of the expected efficiency based on a theoretical performance model. Compared with a multi-core CPU solver, our implementation exhibits 20–60× speedup and 9–12× improved energy efficiency in compute-bound benchmarks on 16 nodes.

*Keywords:* High-performance computing, Graphics processing units, Stencil computations, Computational physics, Magnetohydrodynamics

## 1. Introduction

Iterative stencil loops (ISLs) belong to a class of algorithms, in which data points are updated by sampling their neighborhood in a fixed pattern called a stencil. ISLs, or more generally, computations on a structured grid, have been identified as one of the major recurring computational patterns in high-performance computing (HPC) due to their prevalence in science and engineering [1]. Common applications include image processing [2, 3] and solving partial differential equations (PDEs) [4, 5]. Because each data point can be updated independently, ISLs can usually be processed efficiently on parallel computers.

Over the last ten years, compute nodes in HPC have been gradually shifting from homogeneous systems into systems housing multiple general-purpose processors and domain-specific accelerators; graphics processing units (GPUs) are the most commonly used ones. Of the TOP500 HPC systems, 27% house one or more NVIDIA GPUs per node [6]. As specialized co-processors, GPUs can provide multiple times higher throughput in data-parallel tasks than central processing units (CPUs)<sup>1</sup>, which makes them an attractive platform for ISLs.

In computational sciences, large stencils are often used to obtain sufficiently accurate results. For example in astrophysical fluid simulations, the fluids are frequently in a state of fully developed turbulence, and high-order difference schemes, high-resolution discretization, and double-precision arithmetic can be useful, or even mandatory, for discerning small-scale details. In large-scale simulations, data movement is a likely bottleneck, as the amount of communication decreases at a lower rate than computation when the number of parallel processors is increased. This will be elaborated on in Section 3.2.

Reducing the performance impact of data movement is a notable challenge. Wulf [11], Patterson [12], and others [13, 14], observed that arithmetic performance of microprocessors increases at a faster rate relative to the improvements in memory bandwidth, and bandwidth improves at a faster rate than memory access latency. The performance of network interconnects has followed a similar trend. In a ten-year span, the operational performance of a HPC node has increased 26-fold [6], whereas the network interconnect bandwidth has increased only 6.25-fold<sup>2</sup>. As network bandwidth is generally an order of magni-

Preprint submitted to Elsevier May 11, 2022

Optimization techniques for accelerating ISLs on a single GPU have been extensively studied in previous works [7, 8].

In computational sciences, large stencils are often used to

<sup>\*</sup>This work was supported by the Academy of Finland ReSoLVE Centre of Excellence (grant number 307411); the European Research Council (ERC) under the European Union's Horizon 2020 research and innovation programme (Project UniSDyn, grant agreement n:o 818665); and Theory within ASIAA from Academia Sinica.

<sup>\*</sup>Corresponding author

<sup>&</sup>lt;sup>1</sup>A Tesla V100-SXM2-32GB GPU provides an operational performance of 7.83 TFLOPS (floating-point operations per second) and 863 GiB/s off-chip memory bandwidth [9], whereas a 20-core Intel Xeon Gold 6230 CPU is capable of 1.25 TFLOPS and supplying data at a rate of 131 GiB/s [10].

<sup>&</sup>lt;sup>2</sup>Infiniband QDR (2007) and HDR (2017) [15].

Figure 1: Examples of two-dimensional stencils. The central cell (white) is updated by sampling the neighboring input points (gray). Here r = 2.

tude less than off-chip memory bandwidth, optimizing internode communication is critical for achieving efficient scaling to a large number of compute nodes.

In this work, we address two major challenges with data movement in large-scale applications. Firstly, we estimate the upper bound for communication performance of *d*-dimensional stencil computations by defining a communication cost function for idealized hardware and solving an integer program to find the minimum required communication time. Secondly, we implement a scalable communication scheme, in which data movement latencies are hidden by pipelining computation and communication. We apply our implementation to a practical simulation setup commonly used in fluid dynamics research and compare the achieved performance to the theoretical maximum. The simulation setup employs high-order discretizations in space and time based on finite differences and Runge-Kutta integration methods.

The structure of this paper is as follows. In Section 2, we introduce the terminology used throughout this work to discuss the computational aspects and scaling properties of ISLs. In Section 3.1, we describe the performance model used for finding theoretical performance limiters and evaluating the scaling of our implementation. In Sections 3.2 and 3.3, we present a communication cost function for stencil computations, find the upper bound for communication performance, and present the technical details of our implementation. We give a brief description of the magnetohydrodynamics solver used for benchmarks in Section 4. Finally, we present and discuss our results in Sections 5 and 6, and conclude the paper in Section 7.

# 2. Background

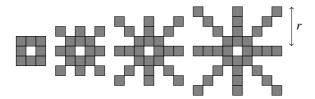

In ISLs, data points are updated by sampling their neighborhoods in a fixed memory access pattern, called a stencil (see Fig. 1). The radius r of a stencil is the maximal Chebyshev distance from c

$$r = \max_{s \in S} \left( \max_{i} |s_i - c_i| \right), \tag{1}$$

where  $c = (c_0, c_1, \ldots, c_d)$  is the spatial index of the point being updated and S the set of stencil points. The exact shape of a stencil depends on the application. In the simplest case, a stencil contains all the points within its radius  $S = \{s \in \mathbb{Z}^d : |s_i| \le r\}$ . In this work, we focus on stencils of this form and its subsets with the same radius.

Data points are stored in a *d*-dimensional array, usually representing a structured grid with regular connectivity. In this context, we refer to data points as cells. During an iteration

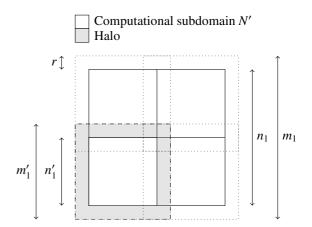

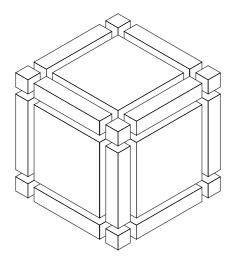

Figure 2: Illustration of the computational domain partitioned into four sub-domains. Boundaries of computational subdomains are marked with a solid line. A halo surrounds each subdomain, marked with a dotted line. One of the subgrids is highlighted with a dashed line for clarity.

step, the cells belonging to the computational domain are updated according to some stencil operation. When updating cells near the boundaries, some stencil points fall outside the computational domain. The set of these points is henceforth referred to as the *halo*. We use the term *grid* to denote the set of all cells that belong to either the halo or the computational domain.

We use d-tuples of the form  $\Phi = (\phi_1, \phi_2, \ldots, \phi_d)$  to denote domains, where  $\phi_i \in \mathbb{N}$  is the number of cells in dimension i and the total number of elements in  $\Phi$  is  $C_{\Phi} = \prod_{i=1}^{d} \phi_i$ . Using this notation, the domain of the grid is  $M = (n_1 + 2r, n_2 + 2r, \ldots, n_d + 2r)$ , where  $N = (n_1, n_2, \ldots, n_d)$  is the computational domain (see Fig. 2). When processing ISLs on distributed systems, N must be decomposed into  $C_P$  computational subdomains, with  $p_i$  subdomains in dimension i. Each computational subdomain N' is also surrounded by a halo, forming a subgrid M'. For simplicity, we assume all subdomains to have the same size and require, that each node is assigned exactly one subdomain. This enables us to regard  $C_P$  henceforth as the number of nodes. The number of cells in N' and M' can now be written as

$$C_{N'} = \prod_{i=1}^{d} \frac{n_i}{p_i}, \text{ and}$$

(2)

$$C_{M'} = \prod_{i=1}^{d} \left( \frac{n_i}{p_i} + 2r \right) . \tag{3}$$

When processing ISLs on two or more nodes, a portion of the halo, local to one node, overlaps with the computational subdomain assigned to a neighboring node. After each update of the neighboring subdomain, the data corresponding to the halo segment must be communicated back to the initial node. This is called a halo exchange, as communication happens both ways for nodes sharing a boundary.

## 2.1. Previous work

In previous work, we presented a library for accelerating ISLs on GPUs, called Astaroth [16]. It provides an application

programming interface to the GPU resources and a domain-specific language (DSL) for writing stencil kernels. Astaroth was inspired by an earlier proof-of-concept hydrodynamics solver presented in [17, 18], which was originally created for the purpose of exploring how to accelerate the computational methods used by the Pencil Code [19]. Later, the library was extended to support computations on multiple devices on a single node using CUDA peer-to-peer memory transfers [20]. In this work, we extend Astaroth to support computations on multiple nodes.

There are several libraries and frameworks designed for accelerating stencil codes. The one, which is closest related to Astaroth, is Physis [21], which has also been designed for accelerating stencil computations on GPUs and performs sourceto-source translation from a DSL to CUDA and MPI. However, communication is carried out explicitly via host memory. Another library close to our work is LibGeoDecomp [22], which is a mature, stencil-focused library supporting hierarchical geometric partitioning and load balancing on heterogeneous systems, including GPUs. Instead of a DSL, LibGeoDecomp provides C++ templates for describing the parameters for stencil kernels. Of PDE-specific libraries similar to our work, Fargo3D [23] is focused on accelerating MHD simulations, supports multiple GPUs and performs communication using CUDA-aware MPI. Instead of handling the memory of each GPU explicitly as in Astaroth, Fargo3D uses Unified Virtual Addressing (UVA) to manage the resources on a node. Yet another framework focused on advection-diffusion type problems is PyFR [24], which provides hierarchical and graph-based partitioning based on the Metis [25] and Scotch [26] software packages. The Cactus Framework has adopted a more generic approach, providing tools for large-scale parallelization of various types of tasks, including stencil computations [27, 28].

The main difference of Astaroth to existing libraries is its specialized focus on improving cache reuse in stencil computations, where the working set, that is, the data required to update a small group of cells, is too large to fit into the caches of a GPU. As such, Astaroth is especially suited for multiphysics simulations, which use high-order stencils, double precision, and require data from several coupled fields to update a cell. For more details on the single-GPU optimization techniques and code generation of Astaroth, we refer the reader to [16].

#### 3. Methodology

#### 3.1. Performance modeling

Performance models are useful for estimating theoretical performance limits, which can be used to determine whether further optimizations are needed or to calculate the expected scaling profile without having to queue for compute resources. In this section, we describe a simple performance model, which we use to find the upper bound for scaling performance. While the model has likely been introduced before, we are not aware of an established name.

In the following discussion, we use generic terminology and focus on ISL-specific definitions from Section 3.2 onward. We

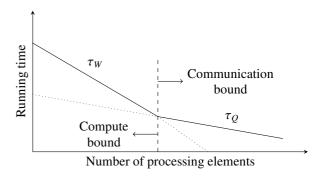

Figure 3: An example of the strong scaling profile produced with Eq. 4.

use the term *processing element* to refer to a generic computational unit that performs work in parallel, such as a node or a device. The terms *host* and *device* are used to refer to the CPU and GPU, respectively. Throughout this work, we use the term *CPU* to refer to the multi-core processor located on a single CPU socket. Finally, we use the term *communication* to refer to data movement within or between non-local memory systems.

As processing elements operate in parallel, the running time is the maximum time it takes for an element to complete its task. We denote the computational workload per processing element as W data items and the amount of communication as Q data items. Furthermore,  $\pi$  is the operational capability of the hardware as data item updates per second, and  $\beta$  the rate at which data elements can be communicated. The time taken by computation and communication is therefore  $\tau_W = W\pi^{-1}$  and  $\tau_Q = Q\beta^{-1}$ , respectively. In this work, we measure  $\pi$  empirically by benchmarking the program on a single device and calculate  $\beta$  based on the theoretical network bandwidth and the size of a data item.

As computation and communication must be carried out in parallel to achieve efficient scaling, the running time of an ideal implementation is  $\max{(\tau_W, \tau_Q)}$ . Taking inspiration from Amdahl's law, we further include a term  $\tau_0$  to capture the time taken in the sequential portion of the program. We use the term *sequential* to refer to computations that cannot be carried out in parallel with communication.

We can now model the running time as

$$\max\left(\tau_{W},\tau_{O}\right)+\tau_{0}.\tag{4}$$

In this form, the model produces a scaling profile that is familiar from multi-processor benchmarks, see Fig. 3. When the performance of a kernel is limited by compute performance, it is said to be compute bound. In this case,  $\tau_W > \tau_Q$ . The kernel is communication bound when the opposite is true. Alternatively, we can express the performance bounds in terms of operational intensity I = W/Q, where the limiter is compute performance if  $I > \pi/\beta$  [29].

## 3.2. Domain decomposition

There are two major considerations for implementing a communication scheme for distributed applications. Firstly, the problem domain must be decomposed into *P* subdomains, and

secondly, the subdomains must be assigned to processing elements. In this section, we use hierarchical geometric partitioning [30, 31] to find a decomposition and processor assignment for ISLs that minimize the communication surface area. In this approach, the partitioning is optimized recursively on each level of the processing element hierarchy. We consider two levels: node- and device-level. Furthermore, we assume that the network topology is a fat tree and the devices within a node are fully connected. These assumptions imply that the bandwidth between any pair of nodes, or devices within a node, is roughly the same and it is possible to form parallel connections to arbitrary many neighbors.

Ultimately, the goal is to balance workloads across processing elements and minimize data movement [32, 33]. If we consider Eq. 4 to model running time at sufficient accuracy, we can minimize the communication surface area of the critical path by solving the integer programming problem

$$\underset{P}{\arg\min\max} \left(\tau_{W}, \tau_{Q}\right) + \tau_{0}$$

subject to  $p_{i} \in \mathbb{N}, \prod_{i=1}^{d} p_{i} = C_{P}$ , (5)

where  $\max(\tau_W, \tau_Q) + \tau_0$  is the worst-case running time for processing a subdomain. Throughout this work, we use the term *optimal decomposition* to refer to P which solves Eq. 5. First, we assume for the sequential portion of the program  $\tau_0 = 0$ . This implies that all computation and communication can be carried out in parallel, which is approximately the case when the implementation is sufficiently pipelined.

Next, we define W and Q for ISLs. In the following proofs, we first find the optimal node-level decomposition, and later expand the reasoning to include heterogeneous nodes containing multiple devices. The amount of local work per update step for each node is

$$W = C_{N'} = \frac{C_N}{C_P} \,. \tag{6}$$

As W does not depend on the choice of the components of either N or P, we can focus on the case  $\tau_W < \tau_Q$ . Furthermore, as  $\beta$  is a constant, the objective function in Eq. 5 simplifies to Q. To simplify the definition of Q, we assume that  $p_i \geq 3$ ,  $\forall p_i \in P$ . If the boundaries are periodic, which is the case in our tests, then the following definition also holds when  $p_i \geq 2$ ,  $\forall p_i \in P$ . The number of cells communicated during a halo exchange per node in the worst case is

$$Q = 2(C_{M'} - C_{N'}) . (7)$$

The worst case behaviour is witnessed when all halo cells must be exchanged. This occurs when each of the boundaries of a computational subdomain faces another subdomain.

As W is inversely proportional to  $C_P$  with coefficient  $C_N$ , ISLs are expected to exhibit ideal scaling when the application is compute bound, that is,  $\tau_W \ge \tau_Q$ . We use the term *ideal scaling* to refer to the case, where the performance grows linearly with the number of processing elements at 100% efficiency. As Q scales at a slower rate in comparison to W, scaling efficiency is reduced when the performance is bound by data movement.

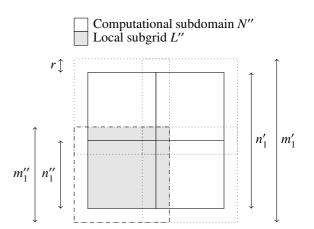

Figure 4: Illustration of an intra-node computational domain decomposed into four subdomains. Boundaries of computational subdomains are marked with a solid line. A halo surrounds each subdomain, marked with a dotted line. One of the subgrids is highlighted with a dashed line for clarity. The local subgrid consists of the cells that are available without inter-node communication.

For relatively low  $C_P$ , it is feasible to conduct an exhaustive search for the optimal decomposition. In other cases, a more sophisticated approach, such as using heuristics to reduce the search space, is likely needed. When using P as a static mapping, the solution can be stored in a lookup table for quick access. The optimal components of P for typical choices of N are listed in Appendix A. On node level, the workloads are inherently balanced, as we require that N' is the same for all nodes and the bandwidth between any pair is the same.

Next, we consider the case when a node contains multiple devices. The optimal decomposition can be found by recursively subdividing N' further to  $C_{P'}$  devices available on a node. We denote the sizes of the per-device grid and computational domain as  $C_{M''}$  and  $C_{N''}$ , respectively. Similar to the node-level definitions,

$$C_{N''} = \prod_{i=1}^{d} \frac{n'_i}{p'_i}$$

, and (8)

$$C_{M''} = \prod_{i=1}^{d} \left( \frac{n'_i}{p'_i} + 2r \right) . \tag{9}$$

For the rest of this section, we refer to N' as the computational domain and N'' as the computational subdomain.

To define the amount of communication performed via the intra-node communication fabric, we introduce the concept of a local subgrid L''. The local subgrid comprises the cells in the computational subdomain and the portion of the halo, that overlaps with the computational subdomain of any of the intra-node neighbors (see Fig. 4). The size of the local subgrid is

$$C_{L''} \ge \prod_{i=1}^{d} \left( \frac{n'_i}{p'_i} + r \cdot \mathbb{1}_{p'_i \ge 2} \right),$$

(10)

where  $\mathbb{1}_{p_i' \geq 2}$  is an indicator function. Intuitively, if  $p_i' \geq 2$ , then there is at least one intra-node boundary. As intra- and internode communication can be carried out in parallel, the total communication time per device is ideally

$$\max \left( \beta_{\text{inter}}^{-1} Q_{\text{inter}}, \, \beta_{\text{intra}}^{-1} Q_{\text{intra}} \right). \tag{11}$$

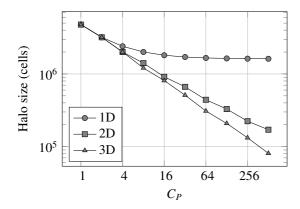

Figure 5: The size of the halo as a function of  $C_P$  in one-, two-, and three-dimensional decomposition schemes.

Furthermore,

$$Q_{\text{inter}} = C_{M''} - C_{L''} Q_{\text{intra}} = C_{L''} - C_{N''}.$$

(12)

The dominant factor in Eq. 11 is typically  $\beta_{\text{inter}}^{-1} Q_{inter}$ , as  $\beta_{\text{inter}}^{-1} > \beta_{\text{intra}}^{-1}$  almost always on modern systems and because

$$C_{M''} + C_{N''} > 2C_{L''} \tag{13}$$

holds for  $N, P \in \mathbb{N}^d$  and  $r \in \mathbb{N}$ , we have  $Q_{\text{inter}} > Q_{\text{intra}}$ . Therefore we can find the optimal intra-node decomposition by minimizing  $C_{M''} - C_{L''}$ . By defining  $C_{L''}$  as the lower bound for intra-node communication, minimizing  $C_{M''} - C_{L''}$  maximizes worst-case performance. The optimal intra-node decompositions for P' are listed in Appendix A.

We can compare the rate of decrease in communication of spatial decomposition schemes by varying the degrees of freedom of P. For example in a one-dimensional decomposition, regardless of the dimensionality of the grid, only one component of P is free while the others are bound to unity. The scaling of data movement in common spatial decomposition schemes is illustrated in Fig. 5. While a one-dimensional decomposition is easy to implement and scales reasonably well to a low number of nodes [20], it is clear that multi-dimensional decomposition is required for large-scale applications.

#### 3.3. Implementation

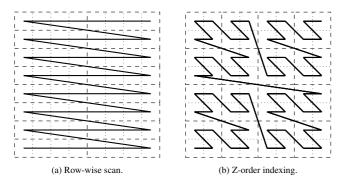

In our implementation, we subdivide the computational domain recursively along each axis in succession and use Z-order indexing [34] to map processors to subdomains (Fig. 6b). The partitioning is given by  $P^* = \text{morton}^{-1}(C_{P^*}-1)+(1,1,1)$ , where  $C_{P^*} = C_P C_{P'}$ . The function  $\text{morton}(\varphi) = i$  interleaves the binary representation of a multidimensional coordinate  $\varphi$  to obtain a one-dimensional index i, and  $\text{morton}^{-1}(i) = \varphi$  is its inverse operation. For example,  $\text{morton}^{-1}$  maps a binary index  $i = \text{abcdef}_2$  to coordinate  $\varphi = (\text{cf}_2, \text{be}_2, \text{ad}_2)$ .

The Z-order curve preserves locality to a relatively high degree, meaning that one-dimensional indices along the curve are likely mapped to multidimensional coordinates that are spatially nearby. If processes within a node are assigned contiguous MPI ranks, Z-order indexing can be used to enhance

intra-node locality of the subdomains. By comparison with the communication-optimal decomposition discussed in Section 3.2 and Appendix A, the Z-order mapping minimizes, or nearly minimizes, the data movement on the critical path in the case where  $n_x = n_y = n_z$  and  $C_{P'} = 4$ .

In contrast to more intuitive processor mappings, locality-preserving space-filling curves can provide better load balancing and reduced data movement. Consider the case where subdomains are assigned to processors in a row-wise scan pattern (Fig. 6a). In this case it is possible for neighboring processors to communicate a different amount of data to inter-node neighbors, which incurs a load imbalance. In the three-dimensional case,  $C_{P'} = 8$ ,  $C_P >> C_{P'}$ , and the dimensions of subdomains are equivalent, the number of faces shared with internode neighbors ranges from four to five. With Z-order indexing, each process has exactly three inter-node-facing edges. The amount of data communicated along the critical path is also larger with row-wise indexing, as the worst-case size of the halo segments is larger when decomposing the intra-node domain in one dimension instead of three.

The use of space-filling curves in large-scale computations has been explored by, for example, Tsuzuki [35] and Li [36]. It should be noted, however, that on practical hardware, pairing our communication cost function with an established graph-based partitioner, such as Scotch [26], may yield even higher-quality decompositions. In this work, we determine that Z-order mapping is sufficiently communication-efficient for our purposes, and leave rigorous comparisons with more established methods for future work.

Several MPI implementations, notably MVAPICH and OpenMPI, provide support for transfers to/from CUDA-allocated device memory. As memory transfers are routed automatically via the fastest communication fabric and the programmer can treat device pointers simply like host pointers, implementing device-to-device communication with CUDA-aware MPI is straightforward. However, special care is needed to ensure the correct pipelining of compute kernels and data transfers.

Furthermore, the GPUDirect remote direct memory access (RDMA) technology has been introduced to enable low-latency inter-node device-to-device communication directly via the network interface controller, bypassing host memory. However, due to lower bandwidth, device-to-device RDMA generally provides better performance only when sending small messages of size 32 KiB or less [37]. Larger messages are buffered through host memory in a pipelined fashion. Almost all messages sent in our implementation are above this threshold.

Executing memory and compute operations in parallel is necessary to hide communication latencies. On a single device, the CUDA API provides concurrency primitives, called streams, for managing the asynchronous execution of kernels. On the multi-node level, concurrency can be managed using the non-blocking variants of the send and receive functions provided by MPI.

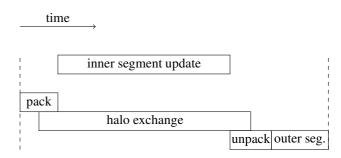

To carry out computation in parallel with communication, we divide the computational domain conceptually into one inner and several outer segments. The inner segment can be up-

Figure 6: The mapping of subdomains to devices using row-wise scan and twodimensional Z-order indexing. Device and node boundaries are indicated with dotted and dashed lines, respectively.

Figure 7: Halo segments. Each segment is sent to a unique neighbor. The inner and outer segments of the computational subdomain are not visible.

dated without information from the halo, while the outer segments can be updated only after communication has finished. In three-dimensional grid decompositions, the domain of the inner segment comprises  $(n'_x - 2r, n'_y - 2r, n'_z - 2r)$  cells. Similar to the inner and outer segments, we partition the halo into conceptual segments, where each segment overlaps with the computational domain of a distinct neighbor. The halo segments are illustrated in Fig. 7. From largest to smallest, we call the segments sides, edges, and corners. There are 6 side segments, 12 edge segments, and 8 corner segments. Each halo segment can be uniquely identified by the spatial index of its first element, which we use as a message tag. A segment at index  $s_i$  is mapped to the computational domain of the receiving device as  $s'_i = ((s_i - r) \mod n'_i) + r$ .

Before initiating halo exchange, the data elements corresponding to each segment are packed into a contiguous buffer. This has two advantages. Firstly, the bulk of memory operations is performed within the faster local memory and secondly, the throughput for sending a few larger messages is generally higher than sending several smaller ones. Two buffers are allocated corresponding to each segment in order to send and receive in parallel. The first buffer is used for packing and sending, and the second for receiving and unpacking. Each ISL it-

Figure 8: Functions applied during a single iteration. Synchronization is indicated with a dashed line. The time taken by each function is not to scale for illustrative purposes.

eration consists of the following steps.

- Inner segment update. Update cells in the inner segment.

- Packing. Pack outbound halo segments into contiguous buffers

- Halo exchange. Exchange halo segments with neighboring devices.

- Unpacking. Unpack inbound halo segments into the local halo.

- Outer segment update. Update cells in the outer segments

To execute packing, halo exchange, and unpacking in a pipelined fashion, each segment is associated with a distinct non-blocking CUDA stream. To exchange the segments, we use functions MPI\_Isend and MPI\_Irecv. The update of the inner segment is launched simultaneously with the halo exchange. Because the halo exchange depends on packed data being available, it is critical to ensure that packing completes before starting the inner segment update. This enables concurrency of computation and communication. We handle this by assigning higher priorities to packing streams, but one could alternatively add an additional synchronization step after packing.

After all data segments have been received, as indicated by the completion of MPI\_Waitall, we launch the kernels for updating the outer segments. The dependencies and execution order of these tasks are illustrated in Fig. 8. After each iteration, the devices are synchronized using cudaDeviceSynchronize and MPI\_Barrier. The implementation supports both single and double precision.

## 4. Implementation example: Magnetohydrodynamics

A particularly active domain of application for Astaroth is in astrophysical fluid dynamics, especially the study of magnetized astrophysical plasma dynamics in the magnetohydrodynamics (MHD) framework (for a general introduction of astrophysical MHD see e.g. [38]). MHD is based on the approximation, that if charged plasma particles are highly collisional,

Figure 9: Two-dimensional cuts of the stencils used to simulate magnetohydrodynamics in this work. Illustrated from left to right: second-, fourth-, sixth-, and eight-order stencils. See Eq. 14 for the definition of the three-dimensional shape.

resistivity is low, and the explored length and time scales are much larger than the ion gyroradius and their oscillation times, plasma can be modelled as a conducting fluid coupled with a magnetic field.

Astrophysical MHD problems are usually highly non-linear and require substantial computing resources because high resolutions in time and/or space, and long integration times, due to the vastly differing time scales of turbulence and the phenomena of interest, are required in realistic setups. In addition, problem sizes inflate when an extended parameter space has to be scanned. MHD has a wide range of applications in multiple astrophysical domains. It is used to study phenomena such as solar magnetic activity, the Earth's magnetosphere, interstellar medium, and star formation. The same methods can be also used in general fluid mechanics, because when neglecting the magnetic field, the MHD equations reduce to the standard equations of hydrodynamics.

The self-contained MHD code has been utilized in a recent work [20], with single-node parallelization, to explore the kinematic growth phase of turbulent MHD dynamos in the isothermal regime. Our MHD solver follows the approach of the *Pencil Code*: we use a non-conservative but high-order finite difference method to explore the non-linear problems. Our implementation supports 2nd-, 4th-, 6th-, and 8th-order central finite differences and time integration by a third-order Runge-Kutta (RK) method [39, 4]. The stencils used to compute the derivatives contain the points

$$S = \{z(x \pm y) : \{x, y\} \subset \{i, j, k, 0\}, |z| \le r, z \in \mathbb{Z}\},$$

(14)

where i, j, k is the standard basis of a 3D space. We use the term kth-order stencil to refer to stencils used to compute kth-order accurate central finite differences, where k = 2r. The related stencils are illustrated in Fig. 14. The full set of MHD equation is listed in Appendix B. For more details, we refer the reader to [16] and [20].

#### 5. Results

The tests were conducted on a cluster consisting of a total of 80 SuperServer 1029GQ-TVRT nodes connected in a fat tree network [40]. Each node houses two Intel Xeon Gold 6230 Cascade Lake 20-core processors running at 2.1 GHz and four Tesla V100-SXM2-32GB GV100GL (rev a1) GPUs running at 1.53 GHz. The stated thermal design power (TDP) of an Intel Xeon Gold 6230 CPU is 125 watts [10], and the stated

TDP of a GV100GL GPU is 300 watts [9]. Each GV100GL is connected to the other three GPUs via pairs of NVLink 2.0 connections, providing 91 GiB/s bidirectional bandwidth per pair. The total intra-node NVLink bandwidth per GPU is 270 GiB/s. Each node houses two Mellanox ConnectX-6 InfiniBand HDR100 MT28908 adapters, which provide 23 GiB/s bidirectional inter-node bandwidth per adapter [15]. Error-correcting codes (ECC) were enabled in all tests. We confirmed the transfer rates by measuring the time to transfer 12 MiB data blocks, which is the same size as the largest individual halo segment transferred in simulations employing 256³ cells. The effective device-to-device intra-node bandwidth was 86 GiB/s and internode bandwidth 40.8 GiB/s.

Astaroth [41], commit 3804e72, was compiled using GCC 8.3.0, CUDA toolkit 10.1.168, and OpenMPI 4.0.3. One MPI task was assigned per GPU. Each multi-core CPU controlled two GPUs closest to it in the node topology and a pair of GPUs shared access to one network interface controller. The rendezvous protocol used by the Unified Communication X (UCX) framework was configured by setting UCX\_RNDV\_THRESH=16384, UCX\_RNDV\_SCHEME=get\_zcopy, and UCX\_MAX\_RNDV\_RAILS=1, as this gave the best performance on the tested hardware. It should be noted, that the optimal configuration for the rendezvous protocol is system specific.

To evaluate whether our implementation is competitive with established work used in production, we compared the scaling performance of Astaroth with that of Pencil Code [19], commit 7ddde40. The simulation setup is available at [42].

The Pencil Code (PC) was benchmarked on two clusters: Puhti and Mahti. The Puhti benchmarks were run on a CPUonly partition of the same cluster as the GPU tests, which also houses two Intel Xeon Gold 6230 processors but only one Mellanox HDR100 network interface controller (NIC) per node. The effective bidirectional inter-node bandwidth in our experiments was roughly 20 GiB/s. The network topology of the Puhti system is a fat tree [43]. A compute node on the Mahti system houses two AMD Rome 7H12 64-core CPUs running at 2.6 GHz, where each multi-core CPU is split into 4 NUMA domains and the TDP of a single CPU is 280 watts [44], 256 GiB memory, and a single Mellanox HDR200 NIC. The network topology on Mahti is Dragonfly+ [45]. The effective bidirectional inter-node bandwidth was roughly 39 GiB/s. We compiled PC using the highest optimization level (02) recommended for production runs and used compilers tuned for the clusters. On Puhti, we used Intel compiler version 19.0.4 and HPCX-MPI 2.4.0, and on Mahti, Intel compiler 19.1.1 and OpenMPI 4.0.3. We refer to PC benchmarks run on the respective systems as PC-Puhti and PC-Mahti hereafter.

Pencil Code was chosen for comparison due to the following reasons: First, it is a mature MHD-solver widely used for production in large-scale astrophysical simulations [46]. Secondly, Astaroth and Pencil Code use the exact same methods and equations in their MHD solvers. Thirdly, comparing CPU and GPU scaling gives us an indicator, whether GPU-applications can be competitive with established CPU solvers in large-scale HPC applications in terms of throughput and energy

efficiency. The perceived bottleneck of CPU-GPU communication has been a cause of concern. Fourthly, Pencil Code uses simple axis-wise partitioning supplied by the user and row-wise scan indexing to map subdomains to processors, in contrast to Astaroth's Z-order mapping that favors the assignment of intranode neighbors to nearby subdomains. Finally, CPU and GPU applications both use the same communication fabric and implementing a communication scheme for either architecture is code-wise nearly identical. While computation throughput is higher on GPUs in our test case, communication-wise there is little difference with CPU applications.

In the benchmarks, we measured the time to complete a third-order Runge-Kutta integration step. The simulation variables were initialized to random values in the range [0, 1] and the timestep was set to a constant  $\delta t = 1.19209 \times 10^{-7}$ . The simulation was run for 100 warm-up steps before measuring the running time of 1000 integration steps. As an exception, we timed only 100 steps in tests which included  $\geq 512^3$  cells due to longer integration times. Double precision was used in all tests.

We verified the results by comparing the simulation state after an integration step with a model solution, which was obtained with a single-core CPU solver logically equivalent with the GPU solver. For a model value m, the unit in the last place (ulp) is

$$\epsilon = 2^{\lfloor \log_2 |m| \rfloor - p + 1} \,, \tag{15}$$

where p is the precision of the floating-point number. For double-precision, p = 53. The absolute error in ulps for a candidate value e is calculated as

$$\frac{|m-c|}{\epsilon} \,. \tag{16}$$

We verified the solver on 1–16 devices in problem sets consisting of  $256^3$  cells. In all cases, the maximum absolute error was  $\leq 2$  ulps. We deemed this to be within acceptable limits, as slight round-off errors are expected to accumulate when rounded intermediate values are used in calculations.

We tested our implementation in six benchmarks. In all of the following figures, the performance is shown as the median time per cell per integration step, where each step comprises three ISL iterations. Sixth-order stencils were used unless otherwise mentioned. We confirmed that processes within a node were assigned contiguous MPI ranks as assumed in Section 3.3.

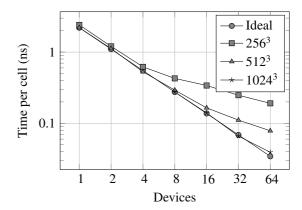

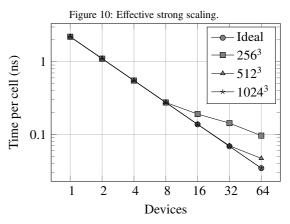

Firstly, we measured the effective integration time per cell for various grid sizes (Fig. 10). For problem sizes consisting of  $256^3$ ,  $512^3$ , and  $1024^3$  cells, we saw scaling to 64 devices at 18%, 43%, and 87% parallel efficiency, respectively, compared to ideal scaling. Theoretical strong scaling, calculated using the performance model discussed in Section 3.1, is shown in Fig. 11. We used  $\pi^{-1} = 2.2$  ns as the computational performance, which we determined empirically by measuring the integration step time on a single device. The communication performance  $\beta^{-1} = 3.9$  ns was determined theoretically based on the cell size in bytes and the maximum network bandwidth of 46 GiB/s. Compared with the theoretical model, the effective performance was 50%, 59%, and 87% of the theoretical maximum on 64 devices. Our implementation exhibited near-ideal

Figure 11: Theoretical strong scaling.

scaling when compute-bound, whereas there was a notable drop in scaling efficiency when communication started to dominate.

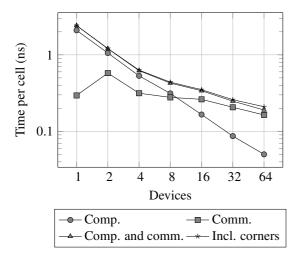

In our second test, we isolated computation and communication to study the performance of the system further. Our results are presented in Fig. 12. As can be seen, communication on a single node (up to four devices) is completely hidden, which is enabled by the relatively high device-to-device bandwidth and the devices being fully connected within a node. Inter-node communication is more sensitive to increases in the amount of communicated data. The portion of the halo communicated to inter-node neighbors increases gradually from 1 to 8 nodes (4 to 32 devices). This can be seen as a stagnation in communication times between 4 to 16 devices. The effect from 16 to 32 devices is significantly weaker and no longer visible. Ideally, the measured integration time is the maximum of computation and communication times. This is not the case, and we can see an overhead of roughly 15-20% compared to communication and communication benchmarked individually. The overhead is likely caused by the sequential portion of our implementation. We also measured the overhead caused by synchronization, which was 0.02–2% of the integration time. The stencils used in this work did not require the communication of the corner halo segments, but this is not the case for all applications. For completeness, the benchmark employing the communication of the corner segments is also shown. The corner segments were small enough to trigger RDMA. The added communication of the corner halo segments increased running

Figure 12: Compute and communication times measured separately in a 256<sup>3</sup>-cell simulation. The overhead caused by synchronization is negligible and has been left out for clarity.

Figure 13: Weak scaling.

times roughly by 0.03-10%.

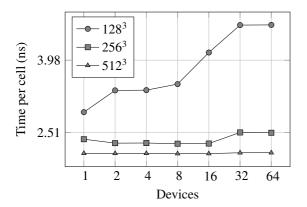

In our third test, we measured weak scaling by assigning each device the same amount of work (Fig. 13). The interconnect boundaries are clearly visible in the figure. The onset of intra-node communication can be seen as the transition between one and two devices, and the onset of inter-node communication between four and eight. The proportion of the node-level halo communicated to inter-node neighbors increases gradually from four devices, reaching the maximum at 32 devices (8 nodes).

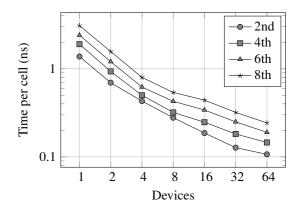

In our fourth test, we measured scaling of varying stencil orders in a 256<sup>3</sup>-cell simulation (Fig. 14). As expected, low-order stencil computations require less communication and scale more efficiently than higher-order ones. Second-order stencils scale relatively efficiently to 32 devices, whereas 8th-order stencils computations become bandwidth-bound at 8 devices.

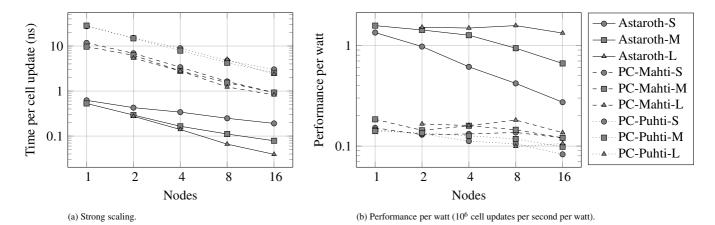

In our fifth test, we compared the strong scaling of Astaroth and PC (Fig. 15a). To produce fair benchmarks, PC-Puhti was used with grid dimensions 280<sup>3</sup>, 520<sup>3</sup>, and 1040<sup>3</sup>, which were multiples of the per-node core count and close to the dimensions 256<sup>3</sup>, 512<sup>3</sup>, and 1024<sup>3</sup> used with Astaroth and PC-Mahti.

Figure 14: Strong scaling of varying stencil orders.

For clarity, we use the terms *small*, *medium*, and *large* to denote the benchmarks using  $256^3$  or  $280^3$ ,  $512^3$  or  $520^3$ , and  $1024^3$  or  $1040^3$  cells, respectively. For decompositions, we chose common-sense processor numbers in the x, y, and z directions, based on the recommendations of the PC developers and its user manual. However, as the decomposition must be supplied by the user and trying each possible permutation was not feasible within the bounds of this work, our PC benchmarks may not present the best performance possible.

On a single node, Astaroth exhibited a  $18-53\times$  speedup compared to PC. On 16 nodes, the speedups with Astaroth in the small, medium, and large benchmarks were  $4-15\times$ ,  $11-32\times$ , and  $20-60\times$ , respectively. The scaling efficiency of PC remained relatively high in all tests.

In our final test (Fig. 15b), we measured the energy efficiency of the implementations in terms of cell updates per second per watt. On a single node, we saw  $8-11\times$  improved energy efficiency with Astroth compared to PC, whereas on 16 nodes, the energy efficiency improved  $2-3\times$ ,  $5-6\times$ , and  $9-12\times$  in the small, medium, and large benchmarks, respectively.

#### 6. Discussion

The landscape of high-performance computing is evolving: modern compute nodes are heterogeneous, housing multiple specialized accelerators that can provide several times higher throughput in domain-specific tasks. As network bandwidth and latency lag behind operational performance, communication-heavy applications must be carefully tuned to reduce data movement to enable efficient scaling to a large number of nodes.

In this work, we have addressed the main questions regarding the implementation of large-scale ISL-based physical simulations on HPC nodes containing multiple GPU devices. By Z-order-based partitioning, and executing computation and communication in parallel, our implementation scaled to 16 nodes at  $\geq 50\%$  efficiency compared to the theoretically achievable performance.

Compared with traditional CPU computations, GPUs can provide competitive throughput and energy efficiency in multinode applications despite additional device-to-host and host-

Figure 15: A performance comparison of Astaroth and Pencil Code (PC-Mahti, PC-Puhti) in 6th-order stencil computations. A cell update entails the full integration step. The grid sizes *small* (S), *medium* (M), and *large* (L) have been abbreviated for clarity.

to-device communication latency (Figs. 15a and 15b). When comparing the operational performance and memory bandwidth available on a single HPC node as used in this work, we expect that GPUs can provide an order of magnitude higher throughput in equivalently optimized data-parallel programs when the performance is bound by compute. In large-scale computations, the benefits of using GPUs diminish when the network bandwidth becomes the performance limiter. Furthermore on a single node using PC-Puhti, we expected a speedup of roughly 13× with Astaroth based on the available memory bandwidth. Instead, we measured a speedup of 44–53×, which suggests that the CPU solver was not fully optimized.

On current hardware in the test cases presented in this work, the benefits of GPUDirect RDMA in high-order stencil computations are modest, as the majority of the messages are above the 32 KiB threshold (Fig. 12, communication with and without corners). We expect to see more notable benefits from RDMA in larger-scale simulations, where each subgrid contains  $\leq 32^3$  cells.

In previous work, we spawned a single process per node, and used CUDA peer-to-peer memory transfers and one-dimensional decomposition for intra-node communication instead of MPI [20]. In this work, we saw no notable performance difference in single-node performance between our previous implementation and our implementation with multiple processes and MPI. The integration time per cell was 0.65 ns in previous work, in contrast to 0.53 ns measured in this work. This was expected, as both implementations were compute bound in our tests. Further tests with smaller grid sizes are required to see whether there is a difference when the performance is bound by bandwidth.

Our work has the following limitations. Firstly, we assumed that the bandwidth between any pair of nodes, or devices within a node, is always the same. This holds if the network topology is a fat tree and the devices within a node are fully connected. However, further analysis may be needed to find the optimal decomposition on more complex interconnect topologies. Furthermore, in our model, we assumed that communication can be carried out simultaneously with all neighbors. This is gen-

erally not the case on current hardware and the communication cost function should be extended to take this into account for more precise scaling estimates.

Secondly, our performance model does not account for the communication overhead, or latency, which can take a significant part of the communication time if message sizes are especially small. In this work where large messages were used, we deemed the model to provide sufficiently robust performance estimates.

Thirdly, our implementation is not fully pipelined, which implies lower parallel efficiency in all test cases. This is caused by starting the update of the outer computational segments only after all communication has finished. Scaling efficiency could be improved with a more fine-grained communication scheme, in which the update of an outer segment is started immediately after its data dependencies have been satisfied [47].

Fourthly, while Morton order indexing provides a good approximation of the optimal decomposition in our test case on an ideal machine, it may not be communication-optimal on practical hardware. Graph-based algorithms for optimizing network communication is a well-studied field [26] and integrating this knowledge into Astaroth is a subject of future work.

As the performance of our implementation was  $\geq 50\%$ the theoretical maximum, more aggressive techniques to reduce data movement are required to see significant improvements in scaling efficiency. One such technique, albeit controversial, is real-time data compression. Lossless compression would reduce data movement without loss of precision, however, achieving satisfactory throughput and compression ratio with noisy data may be difficult. Lossy compression typically provides better compression ratios than lossless compression, but may require tuning in accuracy-sensitive applications. A simple form of lossy compression is mixed precision, supported for example by GROMACS [48], where lower precision is used in calculations where it is known not to result an a catastrophic loss in accuracy. More sophisticated approaches have also been suggested, for example by Lindstrom [49], where four-fold lossy compression in shock hydrodynamics simulations was reported to result in a relative error of 0.06% after 1000 timesteps.

There has been notable interest towards hardware-accelerated compression [50, 51], as it could provide higher throughput than software implementations. Preliminary studies have also been conducted on using machine learning to reconstruct physically accurate turbulent flows from low-resolution data [52, 53].

Whether the disproportional growth of operational, memory, and network performance continues is an open question. At the current rate, the performance of all implementations will eventually become bound by data movement. However, the offchip memory bottleneck has been notably alleviated, but not eliminated, with the introduction of 3D-stacked CMOS technology [54]. Technologies based on silicon photonics are expected to bring similar improvements to network performance [55]. Moreover, the physical limits for transistor densities in siliconbased microprocessors are expected to be encountered around 2025 [56, 57]. As the die size cannot be increased indefinitely to fit more transistors due to lower manufacturing efficiency and issues with heat dissipation [51], new technologies are needed to see continued improvements in operational performance. Several technologies have been suggested, such as graphene-based microprocessors and integrating multiple GPU modules on a single package [58].

Until physical manufacturing limits can be overcome, we expect to see increased use of domain-specific accelerators, such as GPUs, TPUs, and ASICs, due to their ability to provide higher throughput and energy efficiency with existing manufacturing technologies than general-purpose processors. In this light, we believe that data movement will continue to be a major challenge in large-scale computations.

#### 7. Conclusion

Computing centers have started to incorporate specialized accelerators to HPC nodes to improve throughput and power efficiency in domain-specific tasks. This has further increased the gap between computational performance and the rate at which data can be transferred via the network. To enable efficient scaling to multiple nodes in communication-heavy applications, minimizing inter- and intra-node communication is of utmost priority.

In this work, we presented an analysis of the scaling of iterative stencil loops and applied established techniques to implement a scalable multi-GPU communication scheme, which we evaluated in high-order MHD simulations. In our benchmarks, we saw that the per-node performance improvement from GPUs outweighs the added device-to-host and host-to-device communication latencies, and that strong scaling to at least 64 GPUs is possible at high efficiency with sufficiently large problem sizes. Because inter-node bandwidth is an expensive resource, improving intra-node data locality and reducing overall data movement, even at the cost of redundant computations, is likely required to see more efficient scaling in communication-bound problems.

#### Acknowledgements

This study is a product of Astaroth collaboration. The authors thank Fredrik Robertsén (CSC) for valuable discussion and technical support. J.P., M.J.K., and M.R. acknowledge the support of the Academy of Finland ReSoLVE Centre of Excellence (grant number 307411). This project has received funding from the European Research Council (ERC) under the European Union's Horizon 2020 research and innovation programme (Project UniSDyn, grant agreement n:o 818665). M.V. acknowledges funding support for Theory within ASIAA from Academia Sinica.

#### References

- [1] K. Asanovíc, R. Bodik, J. Demmel, T. Keaveny, K. Keutzer, J. Kubiatowicz, N. Morgan, D. Patterson, K. Sen, J. Wawrzynek, D. Wessel, K. Yelick, A view of the parallel computing landscape, Communications of the ACM 52 (10) (2009) 56–67. doi:10.1145/1562764.1562783.

- [2] R. T. Mullapudi, V. Vasista, U. Bondhugula, PolyMage: Automatic optimization for image processing pipelines, ACM SIGARCH Computer Architecture News 43 (1) (2015) 429–443. doi:10.1145/2786763.2694364.

- [3] J. Ragan-Kelley, Decoupling algorithms from the organization of computation for hig Ph.D. thesis, Massachusetts Institute of Technology, MA, USA (2014). URL http://hdl.handle.net/1721.1/89996

- [4] A. Brandenburg, Computational aspects of astrophysical MHD and turbulence, Advances in Nonlinear Dynamos 9 (2003) 269–344. doi:10.1201/9780203493137.

- [5] D. E. Keyes, L. C. Mcinnes, C. Woodward, W. Gropp, E. Myra, M. Pernice, J. Bell, J. Brown, A. Clo, J. Connors, E. Constantinescu, D. Estep, K. Evans, C. Farhat, A. Hakim, G. Hammond, G. Hansen, J. Hill, T. Isaac, X. Jiao, K. Jordan, D. Kaushik, E. Kaxiras, A. Koniges, K. Lee, A. Lott, Q. Lu, J. Magerlein, R. Maxwell, M. Mccourt, M. Mehl, R. Pawlowski, A. P. Randles, D. Reynolds, B. Rivière, U. Rüde, T. Scheibe, J. Shadid, B. Sheehan, M. Shephard, A. Siegel, B. Smith, X. Tang, C. Wilson, B. Wohlmuth, Multiphysics simulations: Challenges and opportunities, International Journal of High Performance Computing Applications 27 (1) (2013) 4–83. doi:10.1177/1094342012468181.

- [6] TOP500, TOP500 List June 2020 (2020). URL www.top500.org

- [7] M. Christen, O. Schenk, H. Burkhart, Patus: A code generation and autotuning framework for parallel iterative stencil computations on modern microarchitectures, in: 2011 IEEE International Parallel & Distributed Processing Symposium, 2011, pp. 676–687. doi:10.1109/IPDPS.2011.70.

- [8] K. Datta, M. Murphy, V. Volkov, S. Williams, J. Carter, L. Oliker, D. Patterson, J. Shalf, K. Yelick, Stencil computation optimization and autotuning on state-of-the-art multicore architectures, in: Proceedings of the 2008 ACM/IEEE Conference on Supercomputing, IEEE Press, Piscataway, NJ, USA, 2008, pp. 4:1–4:12. doi:10.1109/SC.2008.5222004.

- [9] NVIDIA, Santa Clara, CA, USA, NVIDIA Tesla V100 GPU Architecture (2017).

- URL https://images.nvidia.com/content/volta-architecture/pdf/volt

[10] Intel, Santa Clara, CA, USA, Intel Xeon Gold 6230 Processor (2019).

URL https://ark.intel.com/content/www/us/en/ark/products/192437/i

- [11] W. A. Wulf, S. A. McKee, Hitting the memory wall: Implications of the obvious, SIGARCH Comput. Archit. News 23 (1) (1995) 20–24. doi:10.1145/216585.216588.

- [12] D. A. Patterson, Latency lags bandwith, Commun. ACM 47 (10) (2004) 71–75. doi:10.1145/1022594.1022596.

- [13] K. Asanovíc, R. Bodik, B. C. Catanzaro, J. J. Gebis, P. Husbands, K. Keutzer, D. A. Patterson, W. L. Plishker, J. Shalf, S. W. Williams, K. A. Yelick, The landscape of parallel computing research: A view from Berkeley, Tech. Rep. UCB/EECS-2006-183, EECS Department, University of California, Berkeley (2006).

- $URL\ http://www2.eecs.berkeley.edu/Pubs/TechRpts/2006/EECS-2006-18$

- [14] J. L. Hennessy, D. A. Patterson, Computer Architecture: A Quantitative Approach, 5th Edition, Morgan Kaufmann Publishers, Burlington, MA, USA, 2011.

- [15] Lenovo, Beijing, China, ThinkSystem Mellanox ConnectX-6 HDR InfiniBand Adaptits in mesh-indexings, in: Fundamentals of Computation Theory,  $URL\; \texttt{https://lenovopress.com/lp1195.pdf}$

- Master's thesis, Aalto University School of Science, Espoo, Finland (2019).

- URL http://urn.fi/URN:NBN:fi:aalto-201906233993

- [17] J. Pekkilä, M. Väisälä, M. Käpylä, P. Käpylä, O. Anjum, Methods for compressible fluid simulation on GPUs using high-order finite differences, Computer Physics Communications 217 (2017) 11-22. doi:10.1016/j.cpc.2017.03.011.

- Ph.D. thesis, University of Helsinki, Helsinki, Finland (2017). URL http://urn.fi/URN:ISBN:978-951-51-2778-5

- [19] A. Brandenburg, on behalf of the Pencil Code Collaboration, Pencil Code (2020). doi:10.5281/zenodo.3961647.

- [20] M. S. Väisälä, J. Pekkilä, M. J. Käpylä, M. Rheinhardt, H. Shang, R. Krasnopolsky, Interaction of large- and small-scale dynamos in isotropic turbulent flows from GPU-accelerated simulations, The Astrophysical Journal 907 (2021) 83. doi:10.3847/1538-4357/abceca.

- [21] N. Maruyama, K. Sato, T. Nomura, S. Matsuoka, Physis: An implicitly parallel programming model for stencil computations on large-scale GPU-accelerated supercomputers, in: SC '11: Proceedings of 2011 International Conference for High Performance Computing, Networking, Storage and Analysis, 2011, pp. 1-12. doi:10.1145/2063384.2063398

- [22] A. Schäfer, D. Fey, LibGeoDecomp: A grid-enabled library for geometric decomposition codes, in: Proceedings of the 15th European PVM/MPI Users' Group Meeting on Recent Advances in Parallel Virtual Machine and Message Passing Interface, Springer-Verlag, Berlin, Heidelberg, 2008, pp. 285–294.  $\verb"doi:10.1007/978-3-540-87475-1\cdot \_39.$

- [23] P. Benítez-Llambay, F. S. Masset, FARGO3D: A new GPU-oriented MHD code, The Astrophysical Journal Supplement Series 223 (1) (2016) 11. doi:10.3847/0067-0049/223/1/11.

- [24] F. Witherden, A. Farrington, P. Vincent, PyFR: An open source framework for solving advection-diffusion type problems on streaming architectures using the flux reconstruction approach, Computer Physics Communications 185 (11) (2014) 3028 doi:10.1016/j.cpc.2014.07.011.

- [25] G. Karypis, V. Kumar, A fast and high quality multilevel scheme for partitioning irregular graphs, SIAM Journal on Scientific Computing 20 (1) (1998) 359-392. doi:10.1137/S1064827595287997.

- [26] F. Pellegrini, J. Roman, SCOTCH: A software package for static mapping by dual recursive bipartitioning of process and architecture graphs, in: Proceedings of the International Conference and Exhibition on High-Performance Computing and Networking, HPCN Europe 1996, Springer-Verlag, Berlin, Heidelberg, 1996, p. 493-498. doi:10.1007/3-540-61142-8\\_588.

- [27] T. Goodale, G. Allen, G. Lanfermann, J. Massó, T. Radke, E. Seidel, J. Shalf, The Cactus framework and toolkit: Design and applications, in: High Performance Computing for Computational Science -VECPAR 2002, Springer-Verlag, Berlin, Heidelberg, 2003, pp. 197–227. doi:10.1007/3-540-36569-9\\_13.

- [28] J. Tao, M. Blazewicz, S. R. Brandt, Using GPUs to accelerate stencilbased computation kernels for the development of large scale scientific applications on heterogeneous systems, in: Proceedings of the 17th ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming, PPoPP '12, Association for Computing Machinery, New York, NY, USA, 2012, p. 287-288. doi:10.1145/2145816.2145857.

- [29] S. Williams, A. Waterman, D. Patterson, Roofline: An insightful visual performance model for multicore architectures, Communications of the ACM 52 (4) (2009) 65-76. doi:10.1145/1498765.1498785.

- [30] J. D. Teresco, J. Faik, J. E. Flaherty, Hierarchical partitioning and dynamic load balancing for scientific computation, in: Applied Parallel Computing. State of the Art in Scientific Computing, Springer Berlin Heidelberg, Berlin, Heidelberg, 2006, pp. 911–920.  $doi:10.1007/11558958\_110.$

- [31] G. Zheng, A. Bhatelé, E. Meneses, L. V. Kalé, Periodic hierarchical load balancing for large supercomputers, The International Journal

- of High Performance Computing Applications 25 (4) (2011) 371-385. doi:10.1177/1094342010394383

- [32] R. Niedermeier, K. Reinhardt, P. Sanders, Towards optimal local-Springer Berlin Heidelberg, Berlin, Heidelberg, 1997, pp. 364-375. doi:10.1007/BFb0036198.

- [16] J. Pekkilä, Astaroth: A library for stencil computations on graphics processing [ht]s,J. Hungershöfer, J.-M. Wierum, On the quality of partitions based on space-filling curves, in: Computational Science - ICCS 2002, Springer Berlin Heidelberg, Berlin, Heidelberg, 2002, pp. 36-45.  $doi:10.1007/3-540-47789-6\_4.$

- [34] G. Morton, A computer oriented geodetic data base and a new technique in file seque Tech. rep., IBM (1966). URL https://dominoweb.draco.res.ibm.com/Odabf9473b9c86d48525779800

- [35] S. Tsuzuki, T. Aoki, Effective dynamic load balance using space-filling [18] M. S. Väisälä, Magnetic phenomena of the interstellar medium in theory and observationves for large-scale SPH simulations on GPU-rich supercomputers, in: 2016 7th Workshop on Latest Advances in Scalable Algorithms for Large-Scale Systems, 2016, pp. 1-8. doi:10.1109/ScalA.2016.005.

- [36] S. Li, Y. Zhang, T. Hoefler, Cache-oblivious MPI all-to-all communications based on Morton order, IEEE Transactions on Parallel and Distributed Systems 29 (3) (2018) 542-555. doi:10.1109/TPDS.2017.2768413.

- [37] S. Potluri, K. Hamidouche, A. Venkatesh, D. Bureddy, D. K. Panda, Efficient inter-node MPI communication using GPUDirect RDMA for InfiniBand clusters with NVIDIA GPUs, in: 2013 42nd International Conference on Parallel Processing, 2013, pp. 80-89. doi:10.1109/ICPP.2013.17.

- [38] F. H. Shu, The physics of astrophysics. Volume II: Gas dynamics., University Science books, 1992.

- [39] J. Williamson, Low-storage Runge-Kutta schemes. Journal of Computational Physics 35 (1) (1980)48 - 56doi:10.1016/0021-9991(80)90033-9

- San CA, USA Super Micro Computer. Inc.. Jose. Supermicro SuperServer 1029GQ-TRT, 1029GQ-TNRT, 1029GQ-TXRT, 1029GQ-T

- URL https://www.supermicro.com/manuals/superserver/1U/MNL-2009.pd [41] Astroinformatics group, Department of computer science, Espoo, Finland, Astaroth Repository (2020).

$URL\; \verb|https://bitbucket.org/jpekkila/astaroth|$

- Astroinformatics group, Department of computer science, Espoo, Finland, Pencil Code Artifacts (2021).  $URL\ {\tt bitbucket.org/jpekkila/pekkila-2021-artifacts}$

- [43] C. E. Leiserson, Fat-trees: Universal networks for hardware-efficient supercomputing IEEE Transactions on Computers C-34 (10) (1985) 892-901. doi:10.1109/TC.1985.6312192. URL http://ieeexplore.ieee.org/document/6312192/

- [44] Advanced Micro USA. Devices, Santa Clara. AMD EPYCTM 7002 Series Processors (2020). URL https://www.amd.com/system/files/documents/AMD-EPYC-7002-Series

- [45] A. Shpiner, Z. Haramaty, S. Eliad, V. Zdornov, B. Gafni, E. Zahavi, Dragonfly+: Low Cost Topology for Scaling Datacenters, in: 2017 IEEE 3rd International Workshop on High-Performance Interconnection Networks in the Exascale and Big-Data Era (HiPINEB), IEEE, Austin, TX, USA, 2017, pp. 1-8. doi:10.1109/HiPINEB.2017.11. URL http://ieeexplore.ieee.org/document/7885210/

- [46] A. Brandenburg, on behalf of the Pencil Code Collaboration, Scientific usage of the Pencil Code (2020). doi:10.5281/zenodo.3947506.

- [47] O. Lappi, A task scheduler for Astaroth, the astrophysics simulation framework, Master's thesis, Åbo Akademi, Turku, Finland (2021). URL https://urn.fi/URN:NBN:fi-fe2021050428868

- [48] M. J. Abraham, T. Murtola, R. Schulz, S. Páll, J. C. Smith, B. Hess, E. Lindahl, GROMACS: High performance molecular simulations through multi-level parallelism from laptops to supercomputers. SoftwareX 1-2 (2015) 19 - 25. doi:10.1016/j.softx.2015.06.001.

- [49] P. Lindstrom, Fixed-rate compressed floating-point arrays, IEEE Transactions on Visualization and Computer Graphics 20 (12) (2014) 2674–2683. doi:10.1109/TVCG.2014.2346458.

- [50] J. Fowers, J. Kim, D. Burger, S. Hauck, A scalable high-bandwidth architecture for lossless compression on FPGAs, in: 2015 IEEE 23rd Annual International Symposium on Field-Programmable Custom Computing Machines, 2015, pp. 52-59. doi:10.1109/FCCM.2015.46.

- [51] M. Khavari Tavana, Y. Sun, N. Bohm Agostini, D. Kaeli, Exploiting adap-

- tive data compression to improve performance and energy-efficiency of compute workloads in multi-GPU systems, in: 2019 IEEE International Parallel and Distributed Processing Symposium (IPDPS), 2019, pp. 664–674. doi:10.1109/IPDPS.2019.00075.

- [52] A. Güemes, S. Discetti, A. Ianiro, B. Sirmacek, H. Azizpour, R. Vinuesa, From coarse wall measurements to turbulent velocity fields through deep learning, Physics of Fluids 33 (7) (2021) 075121. doi:10.1063/5.0058346.

- [53] H. Kim, J. Kim, S. Won, C. Lee, Unsupervised deep learning for superresolution reconstruction of turbulence, Journal of Fluid Mechanics 910 (2021) A29. doi:10.1017/jfm.2020.1028.

- [54] P. Jacob, A. Zia, O. Erdogan, P. M. Belemjian, J. Kim, M. Chu, R. P. Kraft, J. F. McDonald, K. Bernstein, Mitigating memory wall effects in high-clock-rate and multicore CMOS 3-D processor memory stacks, Proceedings of the IEEE 97 (1) (2009) 108–122. doi:10.1109/JPROC.2008.2007472.

- [55] S. Rumley, D. Nikolova, R. Hendry, Q. Li, D. Calhoun, K. Bergman, Silicon photonics for exascale systems, Journal of Lightwave Technology 33 (3) (2015) 547–562. doi:10.1109/JLT.2014.2363947.

- [56] M. M. Waldrop, The chips are down for Moore's law, Nat. 530 (7589) (2016) 144–147. doi:10.1038/530144a.

- [57] J. Shalf, The future of computing beyond Moore's law, Philosophical Transactions of the Royal Society A: Mathematical, Physical and Engineering Sciences 378 (2166) (2020) 20190061. doi:10.1098/rsta.2019.0061.

- [58] A. Arunkumar, E. Bolotin, B. Cho, U. Milic, E. Ebrahimi, O. Villa, A. Jaleel, C.-J. Wu, D. Nellans, MCM-GPU: Multi-chip-module GPUs for continued performance scalability, in: Proceedings of the 44th Annual International Symposium on Computer Architecture, ISCA '17, Association for Computing Machinery, New York, NY, USA, 2017, p. 320–332. doi:10.1145/3079856.3080231.

Table A.1: Values of P that solve Eq. 5 for typical three-dimensional problem

(a) N = (512, 512, 512).

| $C_P$                        | $p_0$ | $p_1$ | $p_2$ |

|------------------------------|-------|-------|-------|

| 1                            | 1     | 1     | 1     |

| 2                            | 2     | 1     | 1     |

| 4                            | 2     | 2     | 1     |

| 8                            | 2     | 2     | 2     |

| 16                           | 4     | 2     | 2     |

| 32                           | 4     | 4     | 2     |

| 64                           | 4     | 4     | 4     |

| (b) $N = (1024, 512, 512)$ . |       |       |       |

| (b) <i>N</i> | =(1024, | 512, | 512). |

|--------------|---------|------|-------|

|              |         |      |       |

| $C_P$ | $p_0$ | $p_1$ | $p_2$ |

|-------|-------|-------|-------|

| 1     | 1     | 1     | 1     |

| 2     | 2     | 1     | 1     |

| 4     | 4     | 1     | 1     |

| 8     | 4     | 2     | 1     |

| 16    | 4     | 2     | 2     |

| 32    | 8     | 2     | 2     |

| 64    | 8     | 4     | 2     |

(c) N = (1024, 1024, 512).

| $C_P$ | $p_0$ | $p_1$ | $p_2$ |

|-------|-------|-------|-------|

| 1     | 1     | 1     | 1     |

| 2     | 2     | 1     | 1     |

| 4     | 2     | 2     | 1     |

| 8     | 4     | 2     | 1     |

| 16    | 4     | 4     | 1     |

| 32    | 4     | 4     | 2     |

| 64    | 8     | 4     | 2     |

## **Appendix A: Decomposition**

Solutions to Eq. 5 for typical problem sizes, in which the stencil contains all points within its radius and the boundaries are periodic. We evaluated each valid decomposition using a brute-force search. Only one decomposition is listed if there is more than one solution. The optimal inter-node level decompositions *P* are shown in Table A.1. Intra-node level decompositions P' are shown in Table A.2.

Table A.2: Values of P' that solve Eq. 5 adapted for intra-node communication for typical three-dimensional problem sizes.

(a)

$$N' = (512, 512, 512)$$

.

| $C_P'$  | $p_0$ | $p_1$  | $p_2$ |

|---------|-------|--------|-------|

| 1       | 1     | 1      | 1     |

| 2       | 2     | 1      | 1     |

| 4       | 2     | 2      | 1     |

| 8       | 2     | 2      | 2     |

| 16      | 4     | 2      | 2     |

| 32      | 4     | 4      | 2     |

| 64      | 4     | 4      | 4     |

| (L) A7/ | (10)  | 14 512 | £10\  |

(b) N' = (1024, 512, 512).

| $C_P'$                         | $p_0$ | $p_1$ | $p_2$ |

|--------------------------------|-------|-------|-------|

| 1                              | 1     | 1     | 1     |

| 2                              | 2     | 1     | 1     |

| 4                              | 2     | 2     | 1     |

| 8                              | 2     | 2     | 2     |

| 16                             | 4     | 2     | 2     |

| 32                             | 8     | 2     | 2     |

| 64                             | 8     | 4     | 2     |

| (c) $N' = (1024, 1024, 512)$ . |       |       |       |

| $C_P'$ | $p_0$ | $p_1$ | $p_2$ |

|--------|-------|-------|-------|

| 1      | 1     | 1     | 1     |

| 2      | 2     | 1     | 1     |

| 4      | 2     | 2     | 1     |

| 8      | 2     | 2     | 2     |

| 16     | 4     | 2     | 2     |

| 32     | 4     | 4     | 2     |

| 64     | 8     | 4     | 2     |

## **Appendix B: MHD equations**

The basic physical quantities updated during each Runge-Kutta timestep are shown in Table B.1. We use the standard non-ideal MHD equations in non-conservative form:

$$\frac{D \ln \rho}{Dt} = -\nabla \cdot \mathbf{u} ;$$

$$\frac{D\mathbf{u}}{Dt} = -c_s^2 \nabla \left(\frac{s}{c_p} + \ln \rho\right) + \frac{\mathbf{j} \times \mathbf{B}}{\rho}$$

$$+ \nu \left[\nabla^2 \mathbf{u} + \frac{1}{3} \nabla (\nabla \cdot \mathbf{u}) + 2\mathbf{S} \cdot \nabla \ln \rho\right]$$

$$+ \zeta \nabla (\nabla \cdot \mathbf{u}) .$$

(B.1)

$$\rho T \frac{Ds}{Dt} = \mathcal{H} - \mathcal{C} + \nabla \cdot (K\nabla T) + \eta \mu_0 \mathbf{j}^2$$

$$+ 2\rho \nu \mathbf{S} \otimes \mathbf{S} + \zeta \rho (\nabla \cdot \mathbf{u})^2 .$$

(B.3)

$$\frac{\partial \mathbf{A}}{\partial t} = \mathbf{u} \times \mathbf{B} + \eta \nabla^2 \mathbf{A} . \tag{B.4}$$

See Table B.2 for symbol explanations. We refer the reader to [4] for a more detailed discussion on the physical system and related computational aspects.

Table B.1: Basic physical quantities solved for.

| Field                     | Symbol       |

|---------------------------|--------------|

| Logarithmic density       | $\ln  ho$    |

| Velocity                  | u            |

| Specific entropy          | S            |

| Magnetic vector potential | $\mathbf{A}$ |

Table B.2: Other symbols.

| D 111                                       | G 1 1                                                  |

|---------------------------------------------|--------------------------------------------------------|

| Description                                 | Symbol                                                 |

| Laplace operator                            | $ abla^2$                                              |

| Curl operator                               | abla	imes                                              |

| Advective derivative                        | $D/Dt = \partial/\partial t + \mathbf{u} \cdot \nabla$ |

| Magnetic field                              | $\mathbf{B} = \nabla \times \mathbf{A}$                |

| Magnetic diffusivity                        | $\eta$                                                 |

| Magnetic vacuum permeability                | $\mu_0$                                                |

| Electric current density                    | $\mathbf{j} = \mu_0^{-1} \nabla \times \mathbf{B}$     |

| Traceless rate-of-shear tensor              | S                                                      |

| Specific heat capacity at constant pressure | $c_p$                                                  |

| Specific heat capacity at constant volume   | $c_v$                                                  |

| Kinematic viscosity                         | ν                                                      |

| Bulk viscosity                              | ζ                                                      |

| Adiabatic speed of sound                    | $c_s$                                                  |

| Adiabatic index                             | γ                                                      |

| Explicit heating term                       | ${\mathscr H}$                                         |

| Explicit cooling term                       | $\mathscr{C}$                                          |

| Radiative thermal conductivity              | K                                                      |

| Temperature                                 | T                                                      |