# Multi-state MRAM cells for hardware neuromorphic computing

Piotr Rzeszut,<sup>1, a)</sup> Jakub Chęciński,<sup>1</sup> Ireneusz Brzozowski,<sup>1</sup> Sławomir Ziętek,<sup>1</sup> Witold Skowroński,<sup>1</sup> and Tomasz Stobiecki<sup>1, 2</sup>

<sup>1)</sup>AGH University of Science and Technology, Institute of Electronics,

Al. Mickiewicza 30, 30-059 Kraków, Poland

<sup>2)</sup>AGH University of Science and Technology, Faculty of Physics and Applied Computer Science,

Al. Mickiewicza 30, 30-059 Kraków, Poland

(Dated: 9 February 2021)

Magnetic tunnel junctions (MTJ) have been successfully applied in various sensing application and digital information storage technologies. Currently, a number of new potential applications of MTJs are being actively studied, including high-frequency electronics, energy harvesting or random number generators. Recently, MTJs have been also proposed in designs of a new platforms for unconventional or bio-inspired computing. In the present work, it is shown that serially connected MTJs forming a multi-state memory cell can be used in a hardware implementation of a neural computing device. A behavioral model of the multi-cell is proposed based on the experimentally determined MTJ parameters. The main purpose of the multi-cell is the formation of the quantized weights of the network, which can be programmed using the proposed electronic circuit. Multi-cells are connected to CMOS-based summing amplifier and sigmoid function generator, forming an artificial neuron. The operation of the designed network is tested using a recognition of the hand-written digits in  $20 \times 20$  pixel matrix and shows detection ratio comparable to the software algorithm, using the weight stored in a multi-cell consisting of four MTJs or more.

#### I. INTRODUCTION

Unconventional computing architectures such as artificial neural networks (ANN) have superior properties over conventional CMOS-based circuits in solving a number of computational problems, e.g., image or voice recognition, navigation, optimization and prediction<sup>1-5</sup>. As a concept, neural networks have been proved to be fast, flexible and energyefficient. However, their digital implementation uses large amount of resources<sup>6</sup>, which leads to high area needed to implement them. An alternative solution, opposite to the digital implementation, is to use analog-based circuits, where signals are represented as continuous voltage values rather than quantized bits<sup>7-10</sup>. In such implementations, a key element is a programmable resistive element, such as memristor<sup>11</sup>, which can act as a weight in an artificial neuron. Using a solely digital implementation of a neural network may lead to high resource and energy consumption. On the contrary, using mixed digital and analog electronic circuits may enable more compact and energy efficient solution. In a number of the proposed analog ANN implementations, neuron behavior was mimicked by a resistive RAM (RRAM) element<sup>12</sup>, whose resistance change originated from the conductor/insulator transition<sup>7</sup>. However, cells based on resistive or phase-change technology suffer from limited durability and may degrade over time and subsequent programming cycles<sup>13</sup>. On the contrary, spintronic elements such as memristors, nano-oscillators<sup>14</sup> or probabilistic bit<sup>15</sup>, based on magnetic tunnel junctions (MTJ), which rely on the magnetisation switching or dynamics, do not have such endurance issues, are compatible with the CMOS technology and have been already shown to exhibit superior biomimetic properties<sup>16</sup>. In addition, recent theoretical works have predicted that neural networks are able to work efficiently not only with weights represented by real numbers but also with binary or quantized values<sup>17-19</sup>.

Recently, we have proposed a design of multi-state spin transfer torque magnetic random access memory (STT-MRAM) cells<sup>20</sup>, which may be used in neuromorphic computing schemes as synapses<sup>21–26</sup> or as a standard multi-state memory unit. In this paper, we present a fully functional hardware implementation design of a neural network, which needs no additional components for operation, except for input and output devices. The design of a single synapse is based on multi-bit STT-MRAM cells, interconnected with a minimal set of transistors forming amplifiers in conventional CMOS technology. The entire network is made of neurons arranged in four layers. The operation principle of the proposed neural network is validated using handwritten digits recognition task utilizing MNIST<sup>27</sup> database.

### **II. EXPERIMENTAL AND CIRCUIT LEVEL SIMULATIONS**

In order to perform simulations of the proposed neural network prior to the fabrication process, critical parameters of serially connected MTJs forming a programmable memristor device are needed. In theory, such parameters could ultimately be derived from a fully-developed simulation of an MTJ dynamics, based on the Landau-Lifshitz-Gilbert equation. However, this would require an introduction of multiple assumptions on physical parameters such as magnetic anisotropy, spin-current polarization or temperature dependence, making the obtained result less general. On the other hand, the only thing that an MRAM cell needs in order to operate as a neural network weight is it's transfer function - or, equivalently, the resistance vs. voltage (R(V)) loop. Since our aim is to model the behavior of a realistic ANN consisting of thousands of individual MTJs, we find it less computationally expensive and more universal to model R(V) loops directly, following the approach described below. We will show that this approach is

<sup>&</sup>lt;sup>a)</sup>Electronic mail: piotrva@agh.edu.pl

corroborated by experimental data and that it provides a robust foundation for building a functional ANN.

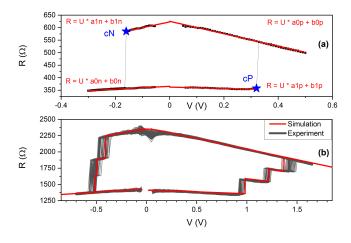

# 1. Modeling of single MTJ R(V) curve

A typical R(V) loop of an MTJ may be approximated using four linear functions (resistance vs. bias voltage dependence in each MTJ state) and two threshold points (switching voltages) as presented in Fig. 1. In addition, in the case of a real MTJ the following parameters are related to each other: a1n = -a1p = a1, b1n = b1p = b1, a0n = -a0p = a0 and b0n = b0p = b0. Moreover, a current resistance state (high or low resistance) has to be included. Using such a model of the R(V) curve allows also to calculate other transport curves, including V(I). The proposed model corresponds to all MTJs that were investigated during the study.

FIG. 1. (a) Experimental R(V) dependence (solid points) and the model consisting of four lines and two critical points (stars) presenting a single MTJ behaviour. (b) A representative simulation result of three serially-connected MTJs (solid line) together with a series of exemplary measurements (gray-scale lines) of a two-bit multicell. Parameters of a single MTJ were used to model the multi-cell characteristics.

Due to the bias dependence of a tunneling magnetoresistance effect<sup>28</sup>, the resistance of an MTJ varies with voltage (thus V(I) is not linear) and there is no direct way of calculating R(V) transport curve for serially connected MTJs. Instead, V(I) may be calculated using Kirchhoff's law, due to the fact that in serially connected MTJs the current is constant, while total voltage is a sum of the voltage drops on each element<sup>29</sup>. In order to determine a resistance for a given voltage V, the following steps are performed<sup>30</sup>:

- 1. Start with a given state of all MTJs and current I = 0

- 2. Increase current by a small step  $I = I + \Delta I$

- 3. For each MTJ:

- (a) Check if critical current for the given state was reached:

- (b) If *yes*, set *I* to 0, change state of the element and go to 2. If *no*, continue.

TABLE I. Expected values and standard deviation of parameters used for simulations

| Param. | Unit     | μ       | σ      |

|--------|----------|---------|--------|

| a1     | $A^{-1}$ | -310    | 3      |

| b1     | Ω        | 665     | 12     |

| a0     | $A^{-1}$ | -30     | 3      |

| b0     | Ω        | 360     | 12     |

| cN     | Α        | -3.1e-4 | 1.5e-5 |

| cP     | Α        | 8.0e-4  | 1.5e-5 |

|        |          |         |        |

- (c) Calculate voltage  $V_i$  on the MTJ for given I

- 4. Calculate total voltage  $V_t = \sum_{i=1}^N V_i$

- 5. If total voltage  $V_t \ge V$ , the solution was found and the algorithm ends. Otherwise, return to step 2.

Depending on the polarity of the applied voltage, the sign of  $\Delta I$  may be the same or opposite to the sign of applied *V*. The value of  $\Delta I$  should be as small as possible for a given computation time limit. By repeating the process for each requested *V*, a full I(V) and R(V) curve can be calculated.

Our approach makes it very straightforward to account for the fact that real-life MTJs are never fully identical, but instead have slightly different dynamical behavior due to fabrication imperfections and partially stochastic nature of the current induced magnetisation switching process<sup>31</sup>. Thanks to the fact that the operational principle of each multi-MTJ cell is described by it's R(V) curve, it is sufficient to represent this variation by choosing slightly different R(V) parameters for each cell at the beginning of the simulation.

To verify the proposed model, a series of measurements of R(V) curve on three different elements were repeated several tens of times for each element, and the data was used to obtain parameters of the model. Then, a series of measurements of these MTJs connected in series were performed. The comparison of experimental data and simulation results of the exact same MTJs is presented in Fig. 1 (b). One can see that the simulation results follow the experimental dependence closely, with even multistep-switching from high- to low-resistance state being reproduced.

In order to predict behavior of a mutli-cell, measurements of R(V) loops for a few tens of fabricated MTJs were conducted and analysed. Next, for each measurement (Fig. 1(a), the model was fitted, resulting in estimation of fabrication parameters and process yield. Across the sample these parameters represented a normal distribution and, therefore, the expected values  $\mu$  and their standard deviation  $\sigma$  may be used to model each parameter.

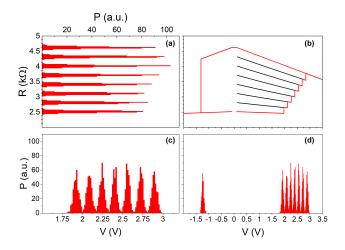

The parameters presented in Tab. I were used to simulate a mutli-cell composed of seven serially connected MTJs, where eight stable resistance states may be observed. After repeating the simulation 300 times, distribution of the switching (write) voltages and resistances were calculated (Fig. 2). A clear separation between stable resistance levels (readout values) as well as between write voltages were observed.

FIG. 2. Simulation results for seven serially connected MTJs with given parameter spread. (a) Spread of readout resistances for the simulation. (b) Representative write-read-erase curves. Red line represents full write-read-erease cycle, while black ones represent write-read cycles while programming subsequent values. (c) Spread of positive write voltages for the simulation. (d) Spread of all write voltages for the simulation.

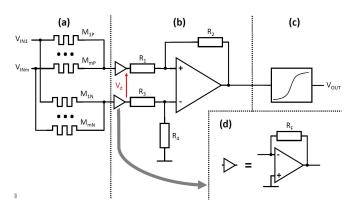

#### A. Electronic neuron

After the analysis of the multi-cell, which may be used as programmable resistor for performing weighted sum operation for many input voltages, we turn to the artificial neuron design. A schematic diagram of the proposed neuron is presented in Fig. 3. Inputs and output  $(V_{INm}, V_{OUT})$  are provided as bipolar analog signals. To enable positive and negative weights, each of the signal inputs uses a pair of programmable MTJ multi-cells ( $M_{mP}$  and  $M_{mN}$ ). In the case when the multicell resistances meet the condition  $M_{mP} < M_{mN}$ , a positive weight is achieved, whereas for the case of  $M_{mP} > M_{mN}$  a negative weight value is realised. An alternative design with multiple MTJs connected in series with a separate select transistors has been proposed recently in Ref. 32. For an equal mutli-cells' resistances, a zero weight is provided, which is equivalent to the situation when an input is disconnected from the synapse. The summing amplifier architecture is being used in order to realise addition operation while reducing footprint of the synapse. A differential amplifier converts differential voltage to a single bipolar signal, which is transformed using a non-linear (sigmoid) function. This voltage may be used as the input of the next synapse, or as the output of the network. Additionally, to provide a constant bias, a standard input with constant voltage may be used, where the level of this constant bias is determined in the same way as weights for other functional inputs.

#### B. Neural network circuit

The electrical circuit realizing proposed neural network was designed in a standard CMOS technology – UMC 180 nm. To

FIG. 3. The proposed neuron design with multi-cells. The circuit consist of (a) a set of memristors for quantized weight purpose, (b) differential amplifier with summing amplifiers (d) at input and (c) sigmoid function block.

program the demanded resistance of seven serially connected MTJs, a voltage of about 3.25 V is needed, so input/output (I/O) 3.3 V transistors were used to design a circuit for MTJs programming purpose, while for other circuits, a standard 1.8 V transistors were used. An individual neuron circuit is composed of three parts. At the input, two resistive networks consisting of memristors realise a multiplication of input voltages and coefficients - Fig. 3(a). Next, the obtained voltage is amplified to the demanded value in a differential amplifier - Fig. 3(b). Finally, the third part is a sigmoid function block, which realises the activation function - Fig. 3(c). The circuit for memristors programming is designed using I/O transistors (not shown) and consists of high voltage switches and digital elements to control them.

The differential voltage  $V_d$  generated by the divider network (Fig. 3(a)) connected to a pair of summing amplifiers (Fig. 3(d)) can be expressed as:

$$V_d = -R_f(\sum_{i=1}^m V_{INi}(G_{iP} - G_{iN}))$$

where:

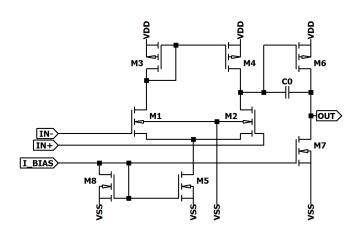

$$G_{iX} = \frac{1}{M_{iX}}$$

The operational amplifier, presented in Fig. 4 was designed as two stage circuit consisting of a differential pair M1, M2 with a current mirror load M3, M4 biased by M5 with a current of 1  $\mu$ A. The output stage M6, M7 provide appropriate amplification and output current. The total current consumed by the operational amplifier is about 12  $\mu$ A and amplification with an open loop of around 74 dB. Dimensions of transistors were chosen in such a way to obtain the smallest area possible while meeting the required electrical parameters.

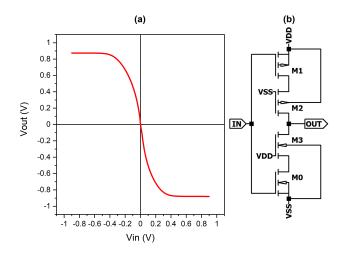

The final stage of the neuron is a circuit, which performs activation functions and has sigmoidal transfer characteristic, presented in Fig. 5(b). It is designed as a modified inverter<sup>33</sup>. Transistors M2 and M3 work as resistors, moving operating point of transistors M0 and M1 to the linear region. Finally,

FIG. 4. A proposed differential amplifier circuit.

FIG. 5. (a) A transfer function of a sigmoid-generating inverter realized by (b) the proposed inverter circuit.

the circuit realizes the transfer characteristic shown in Fig. 5(a). Minimum length of channels were used (180 nm, except for M3, which uses 750 nm), while their width was chosen to obtain required characteristics and output current necessary to drive the next stage. Therefore, the width of M0 and M3 is  $1.2 \,\mu$ m, M1 is  $4.56 \,\mu$ m, and M2 is  $1.12 \,\mu$ m.

# III. RESULTS AND DISCUSSION

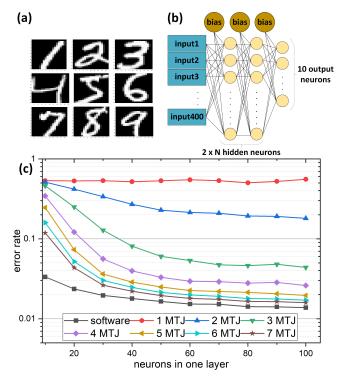

To evaluate the performance of the multi-bit MTJ cellbased ANN a set of classification tasks using the MNIST dataset of handwritten digits (Fig.6(a)) was prepared. The conceptual architecture used for the network is shown in Fig. 6(b) and consists of the input layer, two hidden layers containing *N* neurons each and the output layer. The network was

FIG. 6. Simulated neural network based on multi-bit MRAM cells. Handwritten digits from MNIST database (a) are recognized by a standard neural network with architecture shown in (b), where black lines represent network weights and yellow circles represent individual neurons. After training, weights calculated by software are replaced by discretized values corresponding to 1-7 serial MTJs MRAM cells, which affects the network performance (c).

trained using the standard scaled conjugate gradient method and cross-entropy error metrics, with *tanh* activation function for every layer except the last one, where the *softmax* function was used. Then, its performance was evaluated on a testing subset that has been drawn randomly from the input data and has not participated in training. This procedure was repeated 50 times in total, with training and testing subsets being reshuffled each time, leading to an average error estimate for each network size.

Having established the benchmark network, the evaluation of our MTJ-based design was performed. The original floataccuracy weights between different neurons were replaced by a discrete version corresponding to multi-state MTJ synapses and characteristics of designed amplifier and activation function circuit were applied to the model. The new weights were calculated using simulated conductance data (as described in Sec. II) and rescaled by tuning amplifiers' gains to match the desired value range for the neurons. Then, the performance of the network was re-evaluated on the testing data subset. The results are presented in Fig. 6(c). It can be seen that, as long as the number of MTJs used per multi-state cell exceeds three, the performance of the MTJ-based solution is comparable to the original software version, with differences being only incremental in character.

# IV. SUMMARY

The presented architecture of full hardware artificial neural network proves to be an effective way of performing neuromorphic computing. Compared to other solutions, it utilizes standard MTJs that are compatible with STT-MRAM technology, which has been recently developed for mass production. Additionally, MTJs in such application are very stable over time and they exhibit high endurance in terms of reprogramming, comparing to low-energy barrier MTJs used in probabilistic computing. Moreoever, the presented solution enables more efficient computing, as devices may benefit from a multi-state memristor. To validate this, the artificial CMOS-based neuron was designed, consisting of multi-cell based synapses, differential amplifiers and sigmoid function generator. It was shown that the quantized-weight approach enables the developement of a functional artificial neural network, capable of solving recognition problems with accuracy level similar to the benchmark software model.

# ACKNOWLEDGEMENT

We would like to thank PhD J. Wrona from Singulus Technologies AG for MTJ multilayer deposition. Scientific work funded from budgetary funds for science in 2017-2018, as a research project under the "Diamond Grant" program (Grant No. 0048/DIA/2017/46). W.S. acknowledges support by the Polish National Center for Research and Development grant No.LIDER/467/L-6/14/NCBR/2015. T.S. acknowledges the SPINORBITRONICS grant No. 2016/23/B/ST3/01430. The nano-fabrication process was performed at Academic Centre for Materials and Nanotechnology (ACMiN) of AGH University of Science and Technology.

- <sup>1</sup>J. Fu, H. Zheng, and T. Mei, "Look closer to see better: Recurrent attention convolutional neural network for fine-grained image recognition," in *Proceedings of the IEEE conference on computer vision and pattern recognition* (2017) pp. 4438–4446.

- <sup>2</sup>G. K. Venayagamoorthy, V. Moonasar, and K. Sandrasegaran, "Voice recognition using neural networks," in *Proceedings of the 1998 South African Symposium on Communications and Signal Processing-COMSIG'98 (Cat. No. 98EX214)* (IEEE, 1998) pp. 29–32.

- <sup>3</sup>Y. Zhang, S. Li, and H. Guo, "A type of biased consensus-based distributed neural network for path planning," Nonlinear Dynamics **89**, 1803–1815 (2017).

- <sup>4</sup>K. Muralitharan, R. Sakthivel, and R. Vishnuvarthan, "Neural network based optimization approach for energy demand prediction in smart grid," Neurocomputing **273**, 199–208 (2018).

- <sup>5</sup>K. Abhishek, M. Singh, S. Ghosh, and A. Anand, "Weather forecasting model using artificial neural network," Proceedia Technology 4, 311–318 (2012).

- <sup>6</sup>E. Nurvitadhi, D. Sheffield, J. Sim, A. Mishra, G. Venkatesh, and D. Marr, "Accelerating binarized neural networks: Comparison of FPGA, CPU, GPU, and ASIC," in 2016 International Conference on Field-Programmable Technology (FPT) (IEEE, 2016) pp. 77–84.

- <sup>7</sup>P. Yao, H. Wu, B. Gao, J. Tang, Q. Zhang, W. Zhang, J. J. Yang, and H. Qian, "Fully hardware-implemented memristor convolutional neural network," Nature **577**, 641–646 (2020).

- <sup>8</sup>P. Yao, H. Wu, B. Gao, S. B. Eryilmaz, X. Huang, W. Zhang, Q. Zhang, N. Deng, L. Shi, H.-S. P. Wong, *et al.*, "Face classification using electronic synapses," Nature communications **8**, 1–8 (2017).

- <sup>9</sup>S. Yu, "Neuro-inspired computing with emerging nonvolatile memorys," Proceedings of the IEEE **106**, 260–285 (2018).

- <sup>10</sup>S. Ambrogio, P. Narayanan, H. Tsai, R. M. Shelby, I. Boybat, C. di Nolfo, S. Sidler, M. Giordano, M. Bodini, N. C. Farinha, *et al.*, "Equivalentaccuracy accelerated neural-network training using analogue memory," Nature **558**, 60–67 (2018).

- <sup>11</sup>D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," nature 453, 80–83 (2008).

- <sup>12</sup>G. W. Burr, R. M. Shelby, A. Sebastian, S. Kim, S. Kim, S. Sidler, K. Virwani, M. Ishii, P. Narayanan, A. Fumarola, L. L. Sanches, I. Boybat, M. L. Gallo, K. Moon, J. Woo, H. Hwang, and Y. Leblebici, "Neuromorphic computing using non-volatile memory," Advances in Physics: X 2, 89–124 (2017).

- <sup>13</sup>Q. Wu, W. Banerjee, J. Cao, Z. Ji, L. Li, and M. Liu, "Improvement of durability and switching speed by incorporating nanocrystals in the HfOx based resistive random access memory devices," Applied Physics Letters **113**, 023105 (2018).

- <sup>14</sup>J. Grollier, D. Querlioz, and M. D. Stiles, "Spintronic nanodevices for bioinspired computing," Proceedings of the IEEE **104**, 2024–2039 (2016).

- <sup>15</sup>W. A. Borders, A. Z. Pervaiz, S. Fukami, K. Y. Camsari, H. Ohno, and S. Datta, "Integer factorization using stochastic magnetic tunnel junctions," Nature **573**, 390–393 (2019).

- <sup>16</sup>M. Romera, P. Talatchian, S. Tsunegi, F. Abreu Araujo, V. Cros, P. Bortolotti, J. Trastoy, K. Yakushiji, A. Fukushima, H. Kubota, S. Yuasa, M. Ernoult, D. Vodenicarevic, T. Hirtzlin, N. Locatelli, D. Querlioz, and J. Grollier, "Vowel recognition with four coupled spin-torque nanooscillators," Nature **563**, 230–234 (2018).

- <sup>17</sup>B. Moons, K. Goetschalckx, N. Van Berckelaer, and M. Verhelst, "Minimum energy quantized neural networks," in 2017 51st Asilomar Conference on Signals, Systems, and Computers (IEEE, 2017) pp. 1921–1925.

- <sup>18</sup>I. Hubara, M. Courbariaux, D. Soudry, R. El-Yaniv, and Y. Bengio, "Quantized neural networks: Training neural networks with low precision weights and activations," The Journal of Machine Learning Research 18, 6869–6898 (2017).

- <sup>19</sup>T. G. Toledo, B. Perach, D. Soudry, and S. Kvatinsky, "MTJ-Based Hardware Synapse Design for Quantized Deep Neural Networks," arXiv preprint arXiv:1912.12636 (2019).

- <sup>20</sup>P. Rzeszut, W. Skowroński, S. Ziętek, J. Wrona, and T. Stobiecki, "Multi-bit MRAM storage cells utilizing serially connected perpendicular magnetic tunnel junctions," Journal of Applied Physics **125**, 223907 (2019).

- <sup>21</sup>D. Zhang, L. Zeng, K. Cao, M. Wang, S. Peng, Y. Zhang, Y. Zhang, J.-O. Klein, Y. Wang, and W. Zhao, "All spin artificial neural networks based on compound spintronic synapse and neuron," IEEE transactions on biomedical circuits and systems **10**, 828–836 (2016).

- <sup>22</sup>J. Torrejon, M. Riou, F. A. Araujo, S. Tsunegi, G. Khalsa, D. Querlioz, P. Bortolotti, V. Cros, K. Yakushiji, A. Fukushima, *et al.*, "Neuromorphic computing with nanoscale spintronic oscillators," Nature **547**, 428 (2017).

- <sup>23</sup>S. Lequeux, J. Sampaio, V. Cros, K. Yakushiji, A. Fukushima, R. Matsumoto, H. Kubota, S. Yuasa, and J. Grollier, "A magnetic synapse: multilevel spin-torque memristor with perpendicular anisotropy," Scientific reports 6, 31510 (2016).

- <sup>24</sup>C. Sung, H. Hwang, and I. K. Yoo, "Perspective: A review on memristive hardware for neuromorphic computation," Journal of Applied Physics **124**, 151903 (2018).

- <sup>25</sup>O. Sulymenko, O. Prokopenko, I. Lisenkov, J. Åkerman, V. Tyberkevych, A. N. Slavin, and R. Khymyn, "Ultra-fast logic devices using artificial "neurons" based on antiferromagnetic pulse generators," Journal of Applied Physics **124**, 152115 (2018).

- <sup>26</sup>S. Fukami and H. Ohno, "Perspective: Spintronic synapse for artificial neural network," Journal of Applied Physics **124**, 151904 (2018).

- <sup>27</sup>L. Deng, "The mnist database of handwritten digit images for machine learning research [best of the web]," IEEE Signal Processing Magazine 29, 141–142 (2012).

- <sup>28</sup>J. Sun and D. Ralph, "Magnetoresistance and spin-transfer torque in magnetic tunnel junctions," Journal of Magnetism and Magnetic Materials **320**, 1227 – 1237 (2008).

- <sup>29</sup>S. Fiorentini, R. L. de Orio, S. Selberherr, J. Ender, W. Goes, and V. Sverdlov, "Analysis of switching under fixed voltage and fixed current in perpendicular stt-mram," IEEE Journal of the Electron Devices Society 8, 1249–1256 (2020).

- <sup>30</sup>P. Rzeszut, W. Skowroński, S. Ziętek, J. Chęciński, J. Wrona, and T. Stobiecki, "Serspin simulation source code in matlab," https://gitlab. com/spin-electronics-agh/serspin-simulation, accessed: 2020-01-30.

- <sup>31</sup>A. Fukushima, T. Seki, K. Yakushiji, H. Kubota, H. Imamura, S. Yuasa, and K. Ando, "Spin dice: A scalable truly random number generator based on spintronics," Applied Physics Express 7, 083001 (2014).

- <sup>32</sup>A. Amirany, M. H. Moaiyeri, and K. Jafari, "Nonvolatile associative memory design based on spintronic synapses and cntfet neurons," IEEE Transactions on Emerging Topics in Computing, 1–1 (2020).

- <sup>33</sup>G. Khodabandehloo, M. Mirhassani, and M. Ahmadi, "Analog implementation of a novel resistive-type sigmoidal neuron," IEEE Transactions on Very Large Scale Integration (VLSI) Systems **20**, 750–754 (2012).