# T-count Optimized Quantum Circuits for Bilinear Interpolation

Abstract—Quantum circuits for basic image processing functions such as bilinear interpolation are required to implement image processing algorithms on quantum computers. In this work, we propose quantum circuits for the bilinear interpolation of NEQR encoded images based on Clifford+T gates. Quantum circuits for the scale up operation and scale down operation are illustrated. The proposed quantum circuits are based on quantum Clifford+T gates and are optimized for T-count. Quantum circuits based on Clifford+T gates can be made fault tolerant but the T gate is very costly to implement. As a result, reducing T-count is an important optimization goal. The proposed quantum bilinear interpolation circuits are based on (i) a quantum adder, (ii) a proposed quantum subtractor, and (iii) a quantum multiplication circuit. Further, both designs are compared and shown to be superior to existing work in terms of T-count. The proposed quantum bilinear interpolation circuits for the scale down operation and for the scale up operation each have a 92.52% improvement in terms of T-count compared to the existing work.

### I. INTRODUCTION

Quantum computing has promising applications in number theory, encryption, search, scientific computation and image processing. For example quantum algorithms have been proposed for image orientation problems, image pattern recognition and image template matching [1] [2]. Quantum image representations and image manipulation are required in the quantum circuit implementations of image processing quantum algorithms. Thus, researchers have proposed quantum image representations such as the Flexible Representation of Quantum Images (FRQI) [3] and the Novel Enhanced Quantum Representation (NEQR) [4]. Further, quantum circuits for image operations such as translation, geometric transformation and bilinear interpolation have also been developed [5] [6] [7]. If these quantum circuits are based on Clifford+T gates, they can be made fault tolerant with error correcting codes permitting reliable and scalable quantum computation [8] [9] [10] [11] [12]. The Clifford+T gate family is illustrated in [8]. The T gate is very costly to implement compared to the Clifford gates making T-count an important optimization goal [9] [8] [10] [11] [12].

The design of quantum circuits for operations such as interpolation for NEQR images has been addressed in the literature [5]. The existing bilinear interpolation quantum circuits are based on (i) a quantum subtractor, (ii) a quantum addition circuit, (iii) a quantum multiplication circuit, and (iv)

a quantum division circuit. The work in [5] also proposes a color information retrieval scheme based on quantum oracles operating as lookup tables. While an interesting design, the bilinear interpolation circuits in [5] suffers from significant T gate cost because the design is based on quantum arithmetic circuits that have high T-count. Further, the circuits suffer from added overhead due to extra quantum arithmetic operations which can be minimized.

To overcome the limitations of the existing designs, this work presents quantum circuits for bilinear interpolation of NEQR encoded images based on Clifford+T gates. Quantum circuits for the scale up operation and scale down operation are illustrated. The proposed quantum bilinear interpolation circuits are based on: (i) a quantum adder, (ii) a proposed quantum subtractor and (iii) a quantum multiplication circuit. The proposed quantum bilinear interpolation circuits do not require a quantum division circuit. The proposed quantum bilinear interpolation circuits are compared and shown to be superior to the existing work in terms of T-count and number of arithmetic units used. This paper is organized as follows: Section II discusses the Clifford+T gate set and discusses the novel enhanced quantum representation (NEQR). Section III illustrates the quantum adder, proposed quantum subtractor and quantum multiplication circuit used in the proposed bilinear interpolation circuits. In Section IV, the design of the proposed quantum bilinear interpolation circuit for the scale down operation is presented and compared to the existing work. Lastly, in Section V, the design of the proposed quantum bilinear interpolation circuit for the scale up operation is presented and compared to the existing work.

### II. BACKGROUND

#### A. Quantum Gates

Fault tolerant implementation of quantum circuits is of interest to researchers because physical quantum computers are prone to noise errors [8] [9] [12]. Recently, researchers have implemented quantum logic gates and circuits with the Clifford+T gate set because they can be made fault tolerant [8] [9] [10] [11] [12]. The set of gates that make up the Clifford+T gate family is illustrated in [8]. The bilinear interpolation circuits proposed in this work are composed of the NOT gate, the Feynman (CNOT) gate, the temporary logical- AND gate

(a) The temporary logical-AND gate and its Clifford+T gate implementation. This Clifford+T gate implementation of the temporary logical-AND gate has a T-count of 4.  $|A\rangle$  is an ancillae in the state  $\frac{1}{\sqrt{2}}(|0\rangle+e^{\frac{i-\pi}{4}}|1\rangle)$ .

(b) The uncomputation gate and its Clifford+T gate implementation. This Clifford+T gate implementation of the uncomputation gate has a T-count of 0.

Fig. 1: The quantum gates presented in [14] used in this work. These gates are derived from the designs in [13]. Quantum gate and graphical representations are shown.

and uncomputation gate. The CNOT gate and the NOT gate are in the set of gates that make up the Clifford+T gate family [8]. The temporary logical-AND gate and uncomputation gate must be constructed from Clifford+T gates and are presented in [14]. These gates are based on the designs in [13]. The temporary logical-AND gate is a 3 input, 3 output logic gate and has the mapping  $A, B, \frac{1}{\sqrt{2}}(|0\rangle + e^{\frac{i \cdot \pi}{4}}|1\rangle)$  to  $A, B, A \cdot B$ . The Clifford+T gate implementation of the temporary logical-AND gate is shown in Figure 1a. The input labeled  $|A\rangle$  in Figure 1a is an ancillae in the state shown in expression 1:

$$\frac{1}{\sqrt{2}}(|0\rangle + e^{\frac{i \cdot \pi}{4}}|1\rangle) \tag{1}$$

By using the ancillae set to  $|A\rangle$ , the temporary logical-AND gate designed in [13] can be realized on three qubits instead of four [14].

The uncomputation gate is a 3 input, 3 output logic gate and has the mapping  $A,B,A\cdot B$  to A,B,0. The third input qubit can be restored to an ancillae after measurement for use in later computation. The Clifford+T gate implementation of the uncomputation gate is shown in Figure 1b. A Toffoli gate can be realized from the temporary logical-AND gate and uncomputation gate [13]. The Toffoli gate implementation is shown in Figure 2.

Evaluating quantum circuit performance in terms of the number of T gates (T-count) is of interest because the fault tolerant implementation of the T gate is significantly more costly than the fault tolerant implementation costs of the other Clifford+T gates [9] [8] [10] [11] [12]. By using the logical-AND gate and the uncomputation gate to realize quantum arithmetic circuits, our proposed bilinear interpolation circuits reduce the number of T gates used.

Fig. 2: The Toffoli gate and its Clifford+T gate implementation [13]. This Clifford+T gate implementation of the Toffoli gate has a T-count of 4.  $|A\rangle$  is an ancillae in the state  $\frac{1}{\sqrt{2}}(|0\rangle + e^{\frac{i \cdot \pi}{4}}|1\rangle)$ .

### B. Novel Enhanced Quantum Representation (NEQR)

An image must be represented as qubits. Researchers have proposed several methods to represent both color and greyscale images on a quantum computer [4] [3]. In this work, we use the Novel Enhanced Quantum Representation (NEQR) presented in [4]. NEQR is a means to represent greyscale images on a quantum machine. For a given image, each pixel is represented with expression 2:

$$|Y\rangle|X\rangle|C\rangle \tag{2}$$

Where  $|Y\rangle$  and  $|X\rangle$  are quantum registers that contain the x and y coordinates of the image and  $|C\rangle$  contains the greyscale color of the pixel. Quantum registers  $|Y\rangle$  and  $|X\rangle$  are of size n and the color information quantum register  $|C\rangle$  is of size q to store the needed color information [4] [5]. NEQR improves the existing encoding scheme FRQI (Flexible Representation of Quantum Images) because the image color information is represented as multiple qubits in the computational basis as opposed to a single qubit in superposition. NEQR benefits from faster image preparation, accurate color measurement and easier implementation of quantum image processing circuits compared to FRQI [4].

# III. DESIGN OF QUANTUM CIRCUITS USED IN PROPOSED BILINEAR INTERPOLATION CIRCUITS

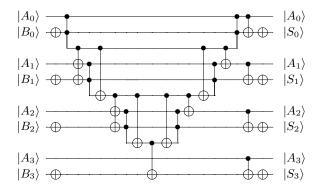

The proposed quantum bilinear interpolation circuits are based on: (i) a quantum adder, (ii) a proposed quantum subtractor and (iii) a quantum multiplication circuit. The circuit designs of the quantum adder, quantum subtractor and quantum multiplier are discussed below:

- Quantum Adder: We use the quantum ripple carry adder presented in [14] in this work. The quantum adder is based on the ripple carry adder design in [15]. The quantum circuit takes two n bit inputs A and B. At the end of computation, the input A emerges unchanged and the input B is transformed to the sum B + A. The quantum adder saves T gates by using the logical-AND gate and the uncomputation gate implementations shown in Section II. The design of the quantum addition circuit is illustrated in [14].

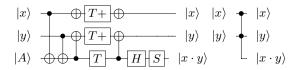

- Proposed Quantum Subtractor: We propose a quantum subtraction circuit in this work. The proposed quantum subtraction circuit is shown in Figure 3.

Fig. 3: Proposed quantum subtraction circuit for four qubit operands.

To save T gates, the proposed quantum subtraction circuit is based on the quantum ripple carry adder presented in [14]. To get the ripple carry adder to perform subtraction, we use the design approach presented in [16]. As shown in Figure 3, the input B is complemented before being applied to the quantum ripple carry adder. Thus, the ripple carry adder calculates  $\bar{B}+A$ . Afterward, the qubits that originally held B are complemented again. As a result, the quantum subtractor calculates  $(\bar{B}+A)$  at the end of computation.  $(\bar{B}+A)$  is equivalent to B-A [16]. While the example in Figure 3 is sized for 4 qubit operands, the proposed quantum subtraction circuit design can be extended to any operand size.

• Quantum Multiplier: We use the quantum integer multiplication circuit presented in [17] in this work. The quantum multiplication circuit takes two n bit inputs a and b. At the end of computation, the inputs a and b emerges unchanged and the product  $b \cdot a$  is generated on ancillae. To save T gates, we use the conditional adder presented in [14] in the multiplication circuit. The quantum conditional adder circuit described in [14] takes two n bit inputs a and b and a 1 bit input control. When the control = 1, the circuit calculates b + a and when control = 0 the circuit performs no computation.

### IV. DESIGN OF THE PROPOSED BILINEAR INTERPOLATION CIRCUIT FOR THE SCALE DOWN OPERATION

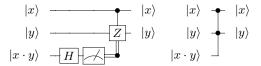

The proposed quantum circuit for bilinear interpolation is shown in Figure 4 for the case of a scaling down an image by an integer value n. Scaling down an image by an integer value n results in reducing the original y and x positions of each pixel by  $2^n$ . Inputs to the proposed quantum circuit is the original pixel positions y and x stored in m bit quantum registers  $|Y\rangle, |X\rangle$ , respectively, along with the corresponding original pixel color information  $C_{Y,X}$  stored in quantum register  $|C_{Y,X}\rangle$ . Inputs also include the pixel color information for adjacent pixels at locations (y+1,x), (y,x+1) and (y+1,x+1). The color information for these adjacent pixels are stored in quantum registers  $|C_{Y+1,X}\rangle, |C_{Y,X+1}\rangle$  and  $|C_{Y+1,X+1}\rangle$  respectively. At the end of computation, the

circuitry returns the position information for the scaled pixel in quantum registers  $|\overline{Y}\rangle$  and  $|\overline{X}\rangle$  as well as the corresponding color of the scaled pixel in quantum register  $|C_{\overline{Y},\overline{X}}\rangle$ .

Our proposed design calculates the position information for the scaled pixel without quantum gates. To reduce an image by a value n, the original position value is divided by  $2^n$ . We accomplish this division by assigning the values at locations  $|Y_{m-1}\rangle$  through  $|Y_n\rangle$  of quantum register  $|Y\rangle$  and locations  $|X_{m-1}\rangle$  through  $|X_n\rangle$  of quantum register  $|X\rangle$  to the output position registers  $|\overline{Y}\rangle$  and  $|\overline{X}\rangle$ , respectively. Thus, we eliminate the need to use a division circuit.

To calculate the color information for the scaled pixel, our proposed quantum circuit must perform the calculation shown in expression 3:

$$\begin{bmatrix} (2^{n} - (\overline{Y} \cdot 2^{n} - Y) \cdot (2^{n} - (\overline{X} \cdot 2^{n} - X) \cdot C_{Y,X} + \\ (\overline{Y} \cdot 2^{n} - Y) \cdot (2^{n} - (\overline{X} \cdot 2^{n} - X) \cdot C_{Y+1,X} + \\ (2^{n} - (\overline{Y} \cdot 2^{n} - Y) \cdot (\overline{X} \cdot 2^{n} - X) \cdot C_{Y,X+1} + \\ (\overline{Y} \cdot 2^{n} - Y) \cdot (\overline{X} \cdot 2^{n} - X) \cdot C_{Y+1,X+1} \end{bmatrix} \div 2^{2 \cdot n}$$

(3)

Where  $(\overline{Y} \cdot 2^n - Y)$  corresponds to locations  $|Y_{n-1}\rangle$  through  $|Y_0\rangle$  of quantum register  $|Y\rangle$  and  $(\overline{X} \cdot 2^n - X)$  corresponds to locations  $|X_{n-1}\rangle$  through  $|X_0\rangle$  of quantum register  $|X\rangle$ .

To perform this computation, the proposed bilinear interpolation circuit requires a quantum multiplication circuit, a quantum addition circuit and a quantum subtraction circuit. Our circuit computes equation 3 by executing the following algorithm:

- Step 1: Copy (<del>Y</del> · 2<sup>n</sup> − Y) and (<del>X</del> · 2<sup>n</sup> − X) to ancillae with CNOT gates.

- Step 2: Calculate  $2^n-(\overline{Y}\cdot 2^n-Y)$  and  $2^n-(\overline{X}\cdot 2^n-X)$  with quantum subtraction circuits.

- Step 3: Calculate the products  $(2^n-(\overline{Y}\cdot 2^n-Y)\cdot (2^n-(\overline{X}\cdot 2^n-X), (\overline{Y}\cdot 2^n-Y)\cdot (2^n-(\overline{X}\cdot 2^n-X), (2^n-(\overline{Y}\cdot 2^n-X), (2^n-(\overline{Y}\cdot 2^n-Y)\cdot (\overline{X}\cdot 2^n-X))$  and  $(2^n-(\overline{Y}\cdot 2^n-Y)\cdot (\overline{X}\cdot 2^n-X))$  with quantum multiplication circuits.

- Step 4: Calculate the product terms  $(2^n (\overline{Y} \cdot 2^n Y) \cdot (2^n (\overline{X} \cdot 2^n X) \cdot C_{Y,X}, (\overline{Y} \cdot 2^n Y) \cdot (2^n (\overline{X} \cdot 2^n X) \cdot C_{Y+1,X}, (2^n (\overline{Y} \cdot 2^n Y) \cdot (\overline{X} \cdot 2^n X) \cdot C_{Y,X+1}$  and  $(2^n (\overline{Y} \cdot 2^n Y) \cdot (\overline{X} \cdot 2^n X) \cdot C_{Y+1,X+1}$  with quantum multiplication circuits.

- Step 5: Complete the calculation of equation 3 with quantum addition circuits.

The values at locations  $2 \cdot n - 1$  through 0 of the quantum register with the result of Step 5 are not a part of the new pixel's color information  $\left(C_{\overline{Y},\overline{X}}\right)$ . By not assigning these locations to the quantum register containing the new pixel's color information  $\left|C_{\overline{Y},\overline{X}}\right\rangle$  we eliminate the need to use quantum division circuits. The remaining locations are the new pixel's color information  $\left(C_{\overline{Y},\overline{X}}\right)$  and will be assigned to the quantum register containing the new pixel's color information  $\left|C_{\overline{Y},\overline{X}}\right\rangle$ .

Fig. 4: Proposed quantum bilinear interpolation circuit for the scale down operation. The image is scaled down by a value n.

TABLE I: Comparison of the Bilinear Interpolation Circuits for the Scale Down Operation in Terms of Number of Functional Blocks Used

| Component  | 1 | proposed |

|------------|---|----------|

| Adder      | 3 | 3        |

| Subtractor | 4 | 2        |

| Divider    | 2 | 0*       |

| Multiplier | 8 | 8        |

<sup>1</sup> is the design in [5]

## A. Cost Analysis of the Proposed Bilinear Interpolation Circuit for the Scale Down Operation

Table I shows the comparison between the proposed quantum circuit for bilinear interpolation and the existing work in terms of total number of arithmetic operations. Through careful layout of functional blocks in our proposed quantum circuit for bilinear interpolation we remove 2 quantum subtraction circuits from our design. By not assigning locations  $2 \cdot n - 1$  through 0 of the quantum register containing the result of equation 3 to the quantum register containing the new pixel's color information  $\left|C_{\overline{Y},\overline{X}}\right>$  we eliminate the need to use quantum division circuits.

Comparison of the T-count between the proposed quantum bilinear interpolation circuit for the scale down operation and the existing work in [5] is shown in Table II. The design in [5] has a T-count of order  $\approx \mathcal{O}(n^2)$ . The proposed design's T-

count is of order  $\mathcal{O}(n^2)$ . To calculate the T-count of the existing design in [5], we determined the T-counts for the quantum circuits used in the design. We determined that to calculate equation 3, the design in [5] uses a quantum addition circuit with a T-count of  $28 \cdot n - 14$ , a quantum subtraction circuit with a T-count of  $28 \cdot n - 14$ , a quantum multiplication circuit with T-count of  $7 \cdot n^2 + \sum_{i=1}^{log_2(n)} \frac{n}{2^i} \cdot \left(14 \cdot \left(n+i-2^{i-1}\right) - 14\right)$  and a quantum division circuit with a T-count of  $\approx 400 \cdot n^2$ . We compute the T-count for the proposed work and the existing design by multiplying the T-count for each quantum functional block by the number of times it is used and then sum the result. Table I shows the number of functional blocks used by the design in [5].

Table II shows that the proposed quantum circuit for bilinear interpolation have an improvement ratio of  $\approx 92.52\%$  in terms of T-count when performing the scale down operation. Our proposed quantum bilinear interpolation circuits save T gates by (i) using T gate efficient functional blocks and (ii) reducing the number of required functional blocks to calculate the new pixel's color information (see equation 3). Our proposed designs are based on the quantum arithmetic circuits illustrated in Section III. As a result, our proposed bilinear interpolation quantum circuit is based on a quantum addition circuit with a T-count of  $4 \cdot n$ , a novel quantum subtraction circuit with a T-count of  $8 \cdot n^2 - 4 \cdot n$ .

### V. DESIGN OF THE PROPOSED BILINEAR INTERPOLATION CIRCUITS FOR THE SCALE UP OPERATION

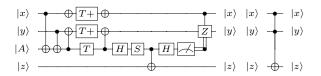

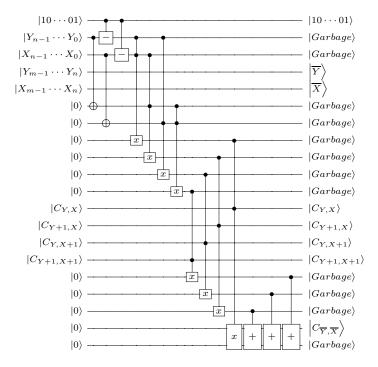

The proposed quantum circuit for bilinear interpolation is shown in Figure 5 for the case of a scaling up an image by an integer value n. Scaling up an image by an integer value n results in increasing the original y and x positions of each pixel by  $2^n$ . Inputs to the proposed quantum circuit is the original pixel positions y and x stored in m bit quantum registers  $|Y\rangle$ ,  $|X\rangle$ , respectively, along with the corresponding original pixel color information  $C_{Y,X}$  stored in quantum register  $|C_{Y,X}\rangle$ . Inputs also include the pixel color information for adjacent original pixels at locations (y + 1, x), (y, x + 1)and (y+1,x+1). The color information for these adjacent pixels are stored in quantum registers  $|C_{Y+1,X}\rangle$ ,  $|C_{Y,X+1}\rangle$ and  $|C_{Y+1,X+1}\rangle$  respectively. At the end of computation, the circuitry returns the position information for the scaled pixel in quantum registers  $|\overline{Y}\rangle$  and  $|\overline{X}\rangle$  as well as the corresponding color of the scaled pixel in quantum register  $|C_{\overline{Y}}|$ .

To scale up an image by a value n, the position value is multiplied by  $2^n$ . By concatenating n ancillae set to 0 to quantum registers  $|X\rangle$  and  $|Y\rangle$  such that they have the values  $X_{m-1}\cdots X_00\cdots 0$  and  $Y_{m-1}\cdots Y_00\cdots 0$  we eliminate the need to use a quantum multiplication circuit. These combined registers now contain the position information  $\overline{Y}$  and  $\overline{X}$ , respectively, for the scaled up pixel.

To calculate the color information for the scaled pixel, our proposed quantum circuit must calculate equation 4.

<sup>\*</sup> Our proposed design does not require a divider.

TABLE II: T Gate Comparison of the Bilinear Interpolation Circuits for the Scale Down Operation

|          | T-count                                                                                                                                         | % impr. w.r.t. 1  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 1        | $856 \cdot n^2 + 196 \cdot n - 98 + 8 \cdot \sum_{i=1}^{\log_2(n)} \frac{n}{2^i} \cdot \left(14 \cdot \left(n + i - 2^{i-1}\right) - 14\right)$ | -                 |

| Proposed | $64 \cdot \overline{n^2 - 12} \cdot \overline{n - 8}$                                                                                           | $\approx 92.52\%$ |

1 is the design in [5]

Fig. 5: Proposed quantum bilinear interpolation circuit for the scale up operation. The image is scaled up by a value n. The notation m + n - 1: n means quantum register locations m+n-1 through n for the output image position registers  $|\overline{Y}\rangle$  and  $|\overline{X}\rangle$ . The notation n-1:0 means quantum register locations n-1 through 0 for the output image position registers  $|\overline{Y}\rangle$  and  $|\overline{X}\rangle$ .

$$\begin{bmatrix}

\left(2^{m} - \frac{\overline{Y}}{2^{n}}\right) \cdot \left(2^{m} - \frac{\overline{X}}{2^{n}}\right) \cdot C_{Y,X} + \\

\left(\frac{\overline{Y}}{2^{n}}\right) \cdot \left(2^{m} - \left(\frac{\overline{X}}{2^{n}}\right) \cdot C_{Y+1,X} + \\

\left(2^{m} - \frac{\overline{Y}}{2^{n}}\right) \cdot \left(\frac{\overline{X}}{2^{n}}\right) \cdot C_{Y,X+1} + \\

\left(\frac{\overline{Y}}{2^{n}}\right) \cdot \left(\frac{\overline{X}}{2^{n}}\right) \cdot C_{Y+1,X+1}

\end{bmatrix} \div 2^{2 \cdot m} \tag{4}$$

Where,  $\frac{\overline{Y}}{2^n}$  corresponds to locations  $\left|\overline{Y_{m+n-1}}\right\rangle$  through  $\left|\overline{Y_{n-1}}\right\rangle$  of the combined position register  $\left|\overline{Y}\right\rangle$  and  $(\overline{X}-X\cdot 2^n)$ ) corresponds to locations  $\left|\overline{X_{m+n-1}}\right\rangle$  through  $\left|\overline{X_{n-1}}\right\rangle$  of the combined position register  $|\overline{X}\rangle$  [5]. The values at locations  $|\overline{Y_{m+n-1}}\rangle$  through  $|\overline{Y_{n-1}}\rangle$  and at locations  $|\overline{X_{m+n-1}}\rangle$ through  $|\overline{X_{n-1}}\rangle$  correspond to the original y and x positions of the pixel.

To perform this computation, the proposed bilinear interpolation circuit requires a quantum multiplication circuit, a

quantum addition circuit, and a quantum subtraction circuit. Our circuit computes equation 4 by executing an algorithm identical to the proposed scale down circuit. The algorithm our quantum bilinear interpolation circuit for the scale up operation implements is as follows:

- Step 1: Copy  $\frac{\overline{Y}}{2^n}$  and  $\frac{\overline{X}}{2^n}$  to ancillae with CNOT gates. Step 2: Calculate  $2^m-\frac{\overline{Y}}{2^n}$  and  $2^m-\frac{\overline{Y}}{2^n}$  with quantum subtraction circuits.

- Step 3: Calculate the products  $\left(2^m \frac{\overline{Y}}{2^n}\right) \cdot \left(2^m \frac{\overline{X}}{2^n}\right)$ ,  $\left(\frac{\overline{Y}}{2^n}\right) \cdot \left(2^m \frac{\overline{X}}{2^n}\right)$ ,  $\left(2^m \frac{\overline{Y}}{2^n}\right) \cdot \left(\frac{\overline{X}}{2^n}\right)$  and  $\left(\frac{\overline{Y}}{2^n}\right) \cdot \left(\frac{\overline{X}}{2^n}\right)$  with quantum multiplication circuits.

- Step 4: Calculate the product terms  $\left(2^m \frac{\overline{Y}}{2^n}\right)$ .  $\begin{pmatrix} 2^m - \frac{\overline{X}}{2^n} \end{pmatrix} \cdot C_{Y,X}, \quad \begin{pmatrix} \frac{\overline{Y}}{2^n} \end{pmatrix} \cdot (2^m - \begin{pmatrix} \frac{\overline{X}}{2^n} \end{pmatrix} \cdot C_{Y+1,X}, \\ \begin{pmatrix} 2^m - \frac{\overline{Y}}{2^n} \end{pmatrix} \cdot \begin{pmatrix} \frac{\overline{X}}{2^n} \end{pmatrix} \cdot C_{Y,X+1} \text{ and } \begin{pmatrix} \frac{\overline{Y}}{2^n} \end{pmatrix} \cdot \begin{pmatrix} \frac{\overline{X}}{2^n} \end{pmatrix} \cdot C_{Y+1,X+1}$  with quantum multiplication circuits.

- Step 5: Complete the calculation of equation 4 with quantum addition circuits.

The values at locations  $2 \cdot m - 1$  through 0 of the quantum register with the result of Step 5 are not a part of the new pixel's color information  $(C_{\overline{Y},\overline{X}})$ . By not assigning these locations to the quantum register containing the new pixel's color information  $\left|C_{\overline{Y},\overline{X}}\right\rangle$  we eliminate the need to use quantum division circuits. The remaining locations are the new pixel's color information  $\left(C_{\overline{Y},\overline{X}}\right)$  and will be assigned to the quantum register containing the new pixel's color information

A. Cost Analysis of the Proposed Bilinear Interpolation Circuit for the Scale Up Operation

TABLE III: Comparison of the Bilinear Interpolation Circuits for the Scale Up Operation in Terms of Number of Functional Blocks Used

| Component  | 1 | proposed |

|------------|---|----------|

| Adder      | 3 | 3        |

| Subtractor | 4 | 2        |

| Divider    | 2 | 0*       |

| Multiplier | 8 | 8        |

1 is the design in [5]

Table III shows the comparison between the proposed quantum circuit for bilinear interpolation and the existing work in terms of total number of arithmetic operations. Through

<sup>\*</sup> Our proposed design does not require a divider.

TABLE IV: T Gate Comparison of Bilinear Interpolation Circuits for the Scale Up Operation

|          | T-count                                                                                                                                         | % impr. w.r.t. 1  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 1        | $856 \cdot n^2 + 196 \cdot n - 98 + 8 \cdot \sum_{i=1}^{\log_2(n)} \frac{n}{2^i} \cdot \left(14 \cdot \left(n + i - 2^{i-1}\right) - 14\right)$ | -                 |

| Proposed | $64 \cdot n^2 - 12 \cdot n - 8$                                                                                                                 | $\approx 92.52\%$ |

1 is the design in [5]

careful layout of functional blocks in our proposed quantum circuit for bilinear interpolation we remove 2 quantum subtraction circuits from our design. Further, by not assigning locations  $2 \cdot m - 1$  through 0 of the quantum register containing the result of equation 4 to the quantum register containing the new pixel's color information  $\left|C_{\overline{Y},\overline{X}}\right>$  we eliminate the need to use quantum division circuits.

Comparison of the T-count between the proposed quantum bilinear interpolation circuit for the scale up operation and the existing work in [5] is shown in Table IV. The design in [5] has a T-count of order  $\approx \mathcal{O}(n^2)$ . The proposed design's T-count is of order  $\mathcal{O}(n^2)$ . To calculate the T-count of the existing design in [5], we determined the T-counts for the quantum circuits used in the design. We determined that to calculate equation 3, the design in [5] uses a quantum addition circuit with a T-count of  $28 \cdot n - 14$ , a quantum subtraction circuit with a T-count of  $28 \cdot n - 14$ , a quantum multiplication circuit with a T-count of  $7 \cdot n^2 + \sum_{i=1}^{log_2(n)} \frac{n}{2^i} \cdot (14 \cdot (n+i-2^{i-1})-14)$ ,  $8 \cdot n^2 - 4 \cdot n$  and a quantum division circuit with a T-count of  $\approx 400 \cdot n^2$ . We compute the T-count for the proposed work and the existing design by multiplying the T-count for each quantum functional block by the number of times it is used and then sum the result.

Table IV shows that the proposed quantum circuit for bilinear interpolation has an improvement ratio of  $\approx 92.52\%$  in terms of T-count when performing the scale up operation. Our proposed quantum bilinear interpolation circuit reduces T-count by (i) using T gate efficient functional blocks and (ii) reducing the number of required functional blocks to calculate the new pixel's color information (see equation 3). Our proposed designs are based on the quantum arithmetic circuits illustrated in Section III. As a result, our proposed bilinear interpolation quantum circuit is based on a quantum addition circuit with a T-count of  $4 \cdot n$ , a novel quantum subtraction circuit with a T-count of  $4 \cdot n - 4$  and a quantum multiplication circuit with a T-count of  $8 \cdot n^2 - 4 \cdot n$ .

#### VI. CONCLUSION

In this work, we presented T-count efficient quantum circuits for bilinear interpolation. Proposed quantum circuits for the scale up operation and scale down operation are illustrated. The building blocks used in our proposed quantum bilinear interpolation circuits (quantum adder, proposed quantum subtractor and quantum multiplication circuit) are also shown. The proposed quantum bilinear interpolation circuits are compared and achieve significant T-count savings compared to the existing work. They are also shown to require fewer quantum arithmetic circuits compared to the existing work. We conclude

that the proposed quantum bilinear interpolation circuits can be integrated in a larger quantum image processing circuit for NEQR encoded images where T-count is of primary concern.

#### REFERENCES

- G. Beach, C. Lomont, and C. Cohen, "Quantum image processing (quip)," vol. 2003-. Institute of Electrical and Electronics Engineers Inc., 2004, pp. 39–44.

- [2] S. Caraiman and V. Manta, "Image processing using quantum computing," in System Theory, Control and Computing (ICSTCC), 2012 16th International Conference on. IEEE, October 2012, pp. 1–6.

- [3] P. Q. Le, F. Dong, and K. Hirota, "A flexible representation of quantum images for polynomial preparation, image compression, and processing operations," *Quantum Information Processing*, vol. 10, no. 1, pp. 63–84, Feb 2011. [Online]. Available: https://doi.org/10.1007/s11128-010-0177-y

- [4] Y. Zhang, K. Lu, Y. Gao, and M. Wang, "Neqr: a novel enhanced quantum representation of digital images," *Quantum Information Processing*, vol. 12, no. 8, pp. 2833–2860, Aug 2013. [Online]. Available: https://doi.org/10.1007/s11128-013-0567-z

- [5] R.-G. Zhou, W. Hu, P. Fan, and H. Ian, "Quantum realization of the bilinear interpolation method for NEQR," *Scientific Reports*, vol. 7, no. 1, 2017.

- [6] N. Jiang and L. Wang, "Quantum image scaling using nearest neighbor interpolation," *Quantum Information Processing*, vol. 14, no. 5, pp. 1559–1571, 2015.

- [7] F. Yan, K. Chen, S. Venegas-Andraca, and J. Zhao, "Quantum image rotation by an arbitrary angle," *Quantum Information Processing*, vol. 16, no. 11, pp. 1–20, 2017. [Online]. Available: http://search.proquest.com/docview/1950084195/?pq-origsite=primo

- [8] M. Amy, D. Maslov, M. Mosca, and M. Roetteler, "A meet-in-the-middle algorithm for fast synthesis of depth-optimal quantum circuits," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 32, no. 6, pp. 818–830, June 2013.

- [9] A. Paler, I. Polian, K. Nemoto, and S. J. Devitt, "Fault-tolerant, high-level quantum circuits: form, compilation and description," *Quantum Science and Technology*, vol. 2, no. 2, p. 025003, 2017. [Online]. Available: http://stacks.iop.org/2058-9565/2/i=2/a=025003

- [10] M. Howard and E. Campbell, "Application of a resource theory for magic states to fault-tolerant quantum computing," *Physical review letters*, vol. 118, no. 9, 2017.

- [11] X. Zhou, D. W. Leung, and I. L. Chuang, "Methodology for quantum logic gate construction," *Phys. Rev. A*, vol. 62, p. 052316, Oct 2000. [Online]. Available: https://link.aps.org/doi/10.1103/PhysRevA.62.052316

- [12] S. Bravyi and A. Kitaev, "Universal quantum computation with ideal clifford gates and noisy ancillas," *Phys. Rev.* A, vol. 71, p. 022316, Feb 2005. [Online]. Available: https://link.aps.org/doi/10.1103/PhysRevA.71.022316

- [13] C. Jones, "Low-overhead constructions for the fault-tolerant toffoli gate," *Phys. Rev. A*, vol. 87, p. 022328, Feb 2013. [Online]. Available: https://link.aps.org/doi/10.1103/PhysRevA.87.022328

- [14] C. Gidney, "Halving the cost of quantum addition," Quantum, vol. 2, p. 74, Jun. 2018. [Online]. Available: https://doi.org/10.22331/q-2018-06-18-74

- [15] S. A. Cuccaro, T. G. Draper, S. A. Kutin, and D. Petrie Moulton, "A new quantum ripple-carry addition circuit," *eprint arXiv:quant-ph/0410184*, Oct. 2004. [Online]. Available: https://arxiv.org/abs/quant-ph/0410184

- [16] H. Thapliyal, "Mapping of subtractor and adder-subtractor circuits on reversible quantum gates," in *Transactions on Computational Science XXVII.* Springer, 2016, pp. 10–34.

- [17] E. Muñoz-Coreas and H. Thapliyal, "T-count Optimized Design of Quantum Integer Multiplication," ArXiv: 1706.05113, Jun. 2017.