# The D0 Silicon Microstrip Tracker

- S.N. Ahmed, R. Angstadt, M. Aoki, B. Åsman, S. Austin, L. Bagby,

- E. Barberis, ad P. Baringer, aa A. Bean, aa A. Bischoff, F. Blekman, T.A. Bolton, ab

- C. Boswell, M. Bowden, F. Browning, D. Buchholz, S. Burdin, D. Butler,

- H. Cease, S. Choi, A.R. Clark, J. Clutter, A. Cooper, W.E. Cooper,

- M. Corcoran, an S.J. de Jong, M. Demarteau, R. Demina, S. Desai, G. Derylo,

- J. Ellison, P. Ermolov, J. Fagan, J. Fast, F. Filthaut, J. Foglesong, V

- H. Fox, C.F. Galea, J. Gardner, R.J. Genik II, C.E. Gerber, Y. Gershtein, af

- K. Gounder, S. Grinstein, W. Gu, P. Gutierrez, K. H. Haggerty, R.E. Hall, q

- S. Hagopian, R. Hance, K. Harder, P. Heger, A.P. Heinson, U. Heintz, ac

- G. Hesketh, ad D. Hover, aa J. Howell, M. Hrycyk, I. Iashviliag M. Johnson,

- H. Jöstlein, V. A. Juste, V. W. Kahl, E. Kajfasz, D. Karmanov, S. Kesisoglou, am

- A. Khanov, al J. King, aa S. Kleinfelder, J. Kowalski, K. Krempetz, M. Kubantsev, ab

- Y. Kulik, G. Landsberg, M. A. Leflat, F. Lehner, V. R. Lipton, H.S. Mao, Mao, M. Lipton, Lipton, M. Lipton, G. Landsberg, M. Leflat, F. Lehner, V. R. Lipton, M. Lipt

- M. Martin, J. Mateski, M. Matulik, M. McKenna, A. Melnitchouk, ae

- M. Merkin, D. Mihalcea, O. Milgrome, H.E. Montgomery, S. Moua,

- N.A. Naumann, A. Nomerotski, D. Olis, D.C. O'Neil G.J. Otero y Garzón, A.

- N. Parua<sup>z</sup> J. Pawlak, <sup>v</sup> M. Petteni, <sup>n</sup> B. Quinn, <sup>ae</sup> P.A. Rapidis, <sup>h</sup> P. Ratzmann, <sup>v</sup>

- F. Rizatdinova, al M. Roco, R. Rucinski, V. Rykalin, H. Schellman,

- W. Schmitt, G. Sellberg, C. Serritella, E. Shabalina, R.A. Sidwell, ab

- V. Simak, E. Smith, B. Squires, N.R. Stanton, G. Steinbrück, Ah

- J. Strandberg,  $^k$  S. Strandberg,  $^k$  M. Strauss,  $^{ak}$  S. Stredde,  $^v$  A. Toukhtarov,  $^v$

- S.M. Tripathi, T.G. Trippe, D. Tsybychev, aj M. Utes, P. van Gemmeren,

- M. Vaz, M. Weber, D.A. Wijngaarden, J. Wish, J. Womersley, R. Yarema,

- Z. Ye $^v$  A. Zieminski, $^z$ ,  $\ddagger$  T. Zimmerman, $^v$  E.G. Zverev, $^j$

<sup>&</sup>lt;sup>a</sup> Universidad de Buenos Aires, Buenos Aires, Argentina

- <sup>b</sup>LAFEX, Centro Brasileiro de Pesquisas Físicas, Rio de Janeiro, Brazil

- <sup>c</sup> Simon Fraser University, Burnaby, British Columbia, Canada

- <sup>d</sup>Institute of High Energy Physics, Beijing, People's Republic of China

- <sup>e</sup>Czech Technical University, Prague, Czech Republic

- f CPPM, Aix-Marseille Université, IN2P3-CNRS, Marseille, France

- <sup>9</sup>Physikalisches Institut, Universität Freiburg, Freiburg, Germany

- <sup>h</sup>National Center for Scientific Research, "Demokritos", Athens, Greece

- <sup>i</sup>Radboud University Nijmegen/NIKHEF, Nijmegen, The Netherlands

- <sup>j</sup> Moscow State University, Moscow, Russia

- <sup>k</sup>Stockholm University, Stockholm, Sweden

- <sup>1</sup>STFC Rutherford Appleton Laboratory, Chilton, United Kingdom.

- <sup>m</sup>Lancaster University, Lancaster, United Kingdom

- <sup>n</sup>Imperial College, London, United Kingdom

- <sup>o</sup>Radio Astronomy Laboratory, University of California Berkeley, Berkeley, California 94720, USA

- <sup>p</sup>Lawrence Berkeley National Laboratory and University of California Berkeley, Berkeley, California 94720, USA

- <sup>q</sup>California State University Fresno, Fresno, California 93740, USA

- <sup>r</sup> University of California Davis, Davis, California 95616, USA

- <sup>s</sup> University of California Riverside, Riverside, California 92521, USA

- <sup>t</sup> University of California Irvine, Irvine California, 92697, USA

- <sup>u</sup>Florida State University, Tallahassee, Florida 32306, USA

- <sup>v</sup> Fermi National Accelerator Laboratory, Batavia, Illinois 60510, USA

- <sup>w</sup> University of Illinois at Chicago, Chicago, Illinois 60607, USA

- <sup>x</sup>Northern Illinois University, DeKalb, Illinois 60115, USA

- <sup>y</sup>Northwestern University, Evanston, Illinois 60208, USA

- <sup>z</sup> Indiana University, Bloomington, Indiana 47405, USA

- <sup>aa</sup> University of Kansas, Lawrence, Kansas 66045, USA

- <sup>ab</sup> Kansas State University, Manhattan, Kansas 66506, USA

- ac Boston University, Boston, Massachusetts 02215, USA

- ad Northeastern University, Boston, Massachusetts 02115, USA

- ae University of Mississippi, University, Mississippi 38677, USA

- $^{af}$  Rutgers University, Piscataway, New Jersey 08855, USA

- <sup>ag</sup> State University of New York, Buffalo, New York 14260, USA

- <sup>ah</sup> Columbia University, New York, New York 10027, USA

- ai University of Rochester, Rochester, New York 14627, USA

- $^{aj}\,State$  University of New York, ?Stony Brook,? Stony Brook, New York 11794, USA

- ak University of Oklahoma, Norman, Oklahoma 73019, USA

- al Oklahoma State University, Stillwater, Oklahoma 74078, USA

- $^{am}$  Brown University, Providence, Rhode Island 02912, USA

- <sup>an</sup>Rice University, Houston, Texas 77005, USA

- ao Visitor from University of Zurich, Zurich, Switzerland

## Abstract

This paper describes the mechanical design, the readout chain, the production, testing and the installation of the Silicon Microstrip Tracker of the D0 experiment at the Fermilab Tevatron collider. In addition, description of the performance of the detector during the experiment data collection between 2001 and 2010 is provided.

# Contents

| 1   | Introduction                         | 1  |

|-----|--------------------------------------|----|

| 2   | General Overview                     | 4  |

| 3   | Mechanical Structure and Environment | 7  |

| 3.1 | Introduction                         | 7  |

| 3.2 | Ladders and Barrels                  | 8  |

| 3.3 | F-Disk and F-Wedge Structure         | 15 |

| 3.4 | Module Support                       | 16 |

| 3.5 | H-Disk and H-Wedge Structure         | 16 |

| 3.6 | Cooling                              | 17 |

| 3.7 | Half-Cylinder and Cover              | 19 |

| 3.8 | Run IIa Beam Pipe                    | 21 |

| 4   | Electronics                          | 22 |

| 4.1 | Introduction                         | 22 |

| 4.2 | Low Noise Design                     | 23 |

| 4.3 | SVXIIe Chip                          | 25 |

| 4.4 | High Density Interconnect            | 30 |

| 4.5 | Low Mass Cables and Adapter Card     | 31 |

| 4.6 | Interface Board                      | 32 |

| 4.7 | Sequencer Controller                 | 32 |

| 4.8 | SVXIIe Sequencer                     | 33 |

| 4.9 | VME Readout Buffer                   | 34 |

| 5   | Silicon Sensors                      | 37 |

| 5.1 | Barrel Sensors                       | 38 |

| 5.2 | Disk Sensors                         | 39 |

| 5.3 | Sensor Production and Testing                              | 39 |

|-----|------------------------------------------------------------|----|

| 5.4 | Micro-discharge                                            | 41 |

| 6   | Production of Ladders and Wedges                           | 44 |

| 6.1 | Production of 3-, 6-, and 9-chip Ladders                   | 44 |

| 6.2 | F-Disk Wedge Production                                    | 51 |

| 6.3 | H-Disk Wedge Production                                    | 53 |

| 7   | Testing of Ladders and Wedges                              | 55 |

| 7.1 | Testing Sequence                                           | 55 |

| 7.2 | Testing of the SVXIIe Chips                                | 55 |

| 7.3 | Testing of Bare HDIs                                       | 56 |

| 7.4 | PC Based Test Stands                                       | 57 |

| 7.5 | Testing of Detector Modules                                | 59 |

| 7.6 | Burn-in Tests                                              | 62 |

| 7.7 | Laser Test                                                 | 64 |

| 7.8 | Diagnosis and Repair of Defective Modules                  | 66 |

| 7.9 | Electrical Grading and Characteristics of Detector Modules | 68 |

| 8   | Assembly of the Central Detector                           | 70 |

| 8.1 | The Barrel Assembly                                        | 70 |

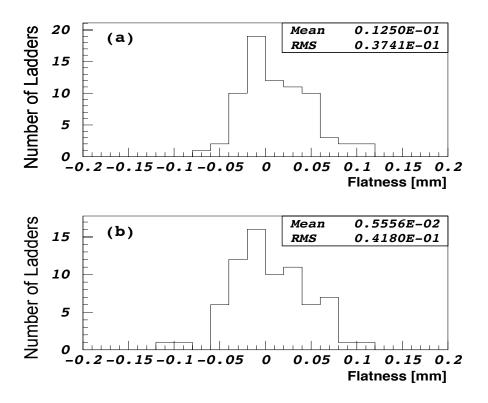

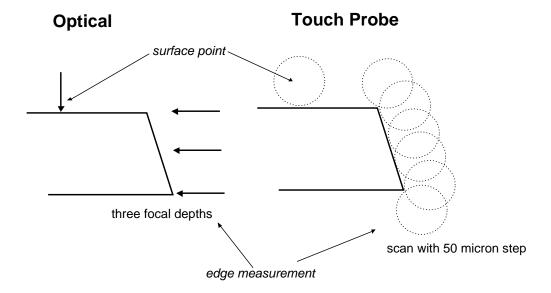

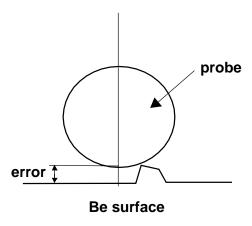

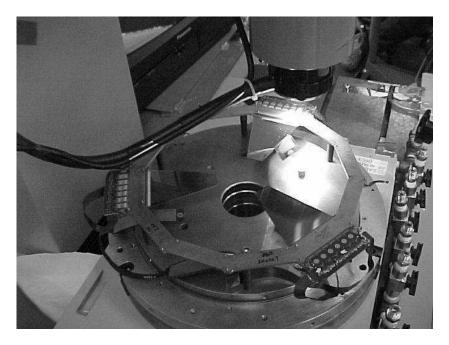

| 8.2 | Measurements of Ladders                                    | 72 |

| 8.3 | Assembly and Survey Procedures                             | 74 |

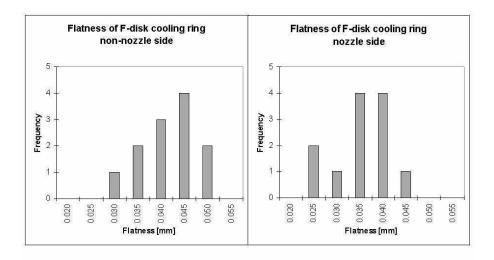

| 8.4 | The F-disk Assembly                                        | 78 |

| 8.5 | Mating of Barrels to Disks and End-disk Assemblies         | 81 |

| 9   | Installation of the Detector                               | 83 |

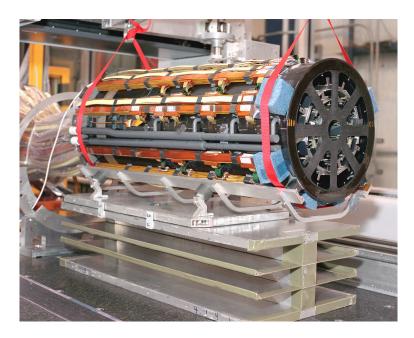

| 9.1 | Transportation and Installation of the Barrel Detector     | 83 |

| 10  | Performance and Lifetime                                   | 86 |

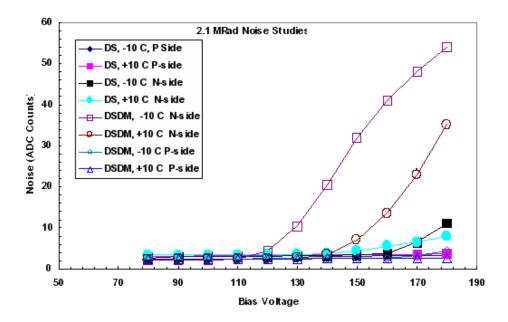

| 10.1 | Noise in the F-wedges             | 88 |

|------|-----------------------------------|----|

| 10.2 | Performance of the Readout System | 89 |

| 10.3 | Radiation Damage                  | 92 |

| 11   | Conclusion                        | 98 |

| Refe | rences                            | 99 |

### 1 Introduction

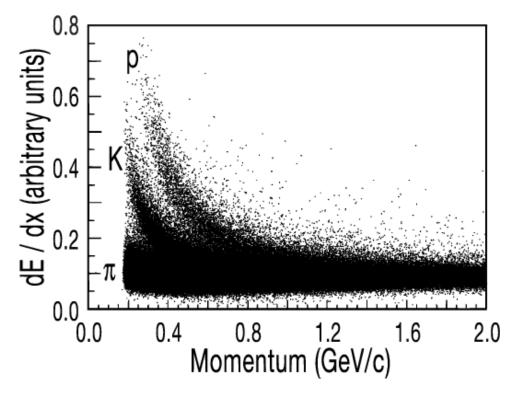

The D0 detector [1] is one of the two detectors at the Tevatron accelerator at Fermilab. The detector performed extraordinarily well in Run I (1992-1996), as demonstrated by the discovery of the top quark [2] and many other published physics results [3].

During Run I, the Tevatron operated using six bunches each of protons and anti-protons with 3500 ns between bunch crossings. In Run II, started in 2001, it is operated with 36 bunches of protons and anti-protons with a bunch spacing of 396 ns. The instantaneous luminosity exceeds  $4 \times 10^{32}$  cm<sup>-2</sup>s<sup>-1</sup>, and more than 12 fb<sup>-1</sup> of data are expected to be delivered in Run II. The center-of-mass energy is 1.96 TeV in Run II compared to 1.8 TeV in Run I.

With the expected increase in the Tevatron luminosity and the experience gained in operating the D0 detector and in analyzing data from Run I, the D0 collaboration upgraded the detector [4] to ensure the full exploitation of the physics opportunities in Tevatron Run II.

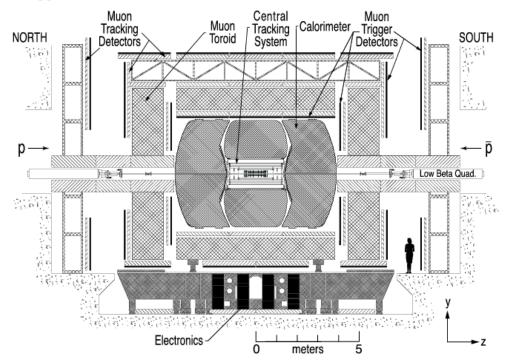

Fig. 1. Cross sectional view of the Run II D0 detector.

Figure 1 shows a cross sectional view of the Run II D0 detector. This upgrade includes faster electronics to match the reduced bunch crossing interval, upgrades of the muon system [5], and new central and forward preshower detectors to improve  $e/\gamma$  identification. Most important is a completely new central tracking system, illustrated in Fig. 2. A 2T axial magnetic field is provided by a  $\approx 2.6\,\mathrm{m}$  long superconducting solenoid magnet with  $\approx 0.5\,\mathrm{m}$

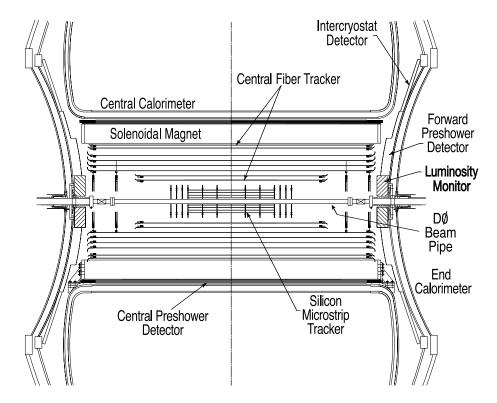

Fig. 2. Cross sectional view of the Run IIa D0 tracking system.

inner radius. The solenoid encloses a scintillating fiber tracker and a silicon microstrip tracker. The Central Fiber Tracker (CFT) consists of eight concentric barrels of scintillating fibers with axial and  $\pm 3^{0}$  stereo read out. The Silicon Microstrip Tracker (SMT) is situated inside the CFT.

Since Run II has a higher instantaneous luminosity than Run I, the trigger system was also upgraded. This new system is formed by three distinct levels. The first stage, Level 1, comprises a collection of hardware trigger elements which reduces the input rate of 2MHz to approximately 2kHz. The Level 2 trigger system reduces the rate further by a factor of two. In this second stage, hardware engines and embedded microprocessors associated with specific subdetectors provide information to a global processor which constructs a trigger decision based on individual objects as well as object correlations. The SMT is one of the subdetectors taking part in the Level 2 trigger. This so called Silicon Track Trigger (STT) is further described in Ref. [6]. Events that passed Level 1 and Level 2 are sent to the Level 3 trigger farm for real time reconstruction, reducing the rate to 50 Hz.

The purpose of this paper is to provide a description of the D0 Silicon Microstrip Tracker built for Run II. In 2006 the dector was upgraded with an extra layer of silicon which was added close to the beam pipe. This is called layer 0 and is described in Ref. [7]. Furthermore the most forward and backwards disks seen in Fig. 2 where removed. The period before this upgrade is referred to as Run IIa and the period after as Run IIb. In the following section

a general overview of the detector is given. Section 3 provides an overview of the mechanical aspects of the tracker, including a description of the cooling. This is followed by a section on the readout system. In Sec. 5, silicon wafer production and testing are described. The two following sections are about the production and quality control of the various detector components. The detector assembly is described in Sec. 8, and in Sec. 9, the installation is described. The paper concludes by summarizing some aspects of the performance of the detector.

In the description of the detector a right-handed coordinate system is used. The z-axis is along the proton beam direction and the y-axis is upward, as illustrated in Fig. 1. The angles  $\phi$  and  $\theta$  are the azimuthal and polar angles, respectively. The r coordinate denotes the perpendicular distance from the z axis.

### 2 General Overview

The design goal of the SMT was to provide both tracking and vertexing over the full pseudorapidity  $(\eta)^1$  coverage of the calorimeter and muon systems.

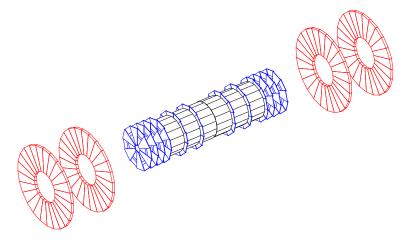

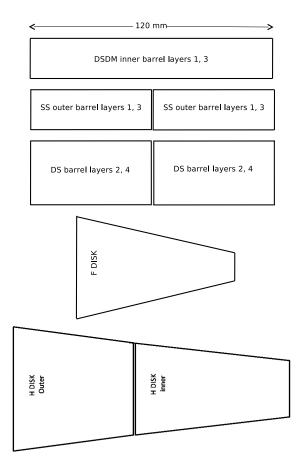

Several of the Tevatron machine parameters had a large effect on the SMT design. The luminosity sets a scale for the radiation damage expected over the life of the detector, which in turn dictates the operating temperature. The bunch spacing sets the design parameters for the electronics and readout, as well as the probability that multiple interactions occur in a single crossing. The length of the interaction region sets the length scale of the device. With a long interaction region of about 25 cm rms, it is difficult to deploy detectors such that the tracks are generally perpendicular to detector surfaces for all  $\eta$ . This feature led to the hybrid system shown in Fig. 3, with barrel detectors measuring primarily the r- $\phi$  coordinate and disk detectors which measure r-z as well as r- $\phi$ . Thus verticies for high  $|\eta|$  particles are reconstructed in three dimensions by the disks, and verticies of particles at small values of  $|\eta|$  are measured in the barrels. This design poses difficult mechanical challenges in the arrangement of the detector types to provide space for cooling and cables while minimizing dead areas.

Fig. 3. Isometric view of the Run IIa D0 silicon tracker.

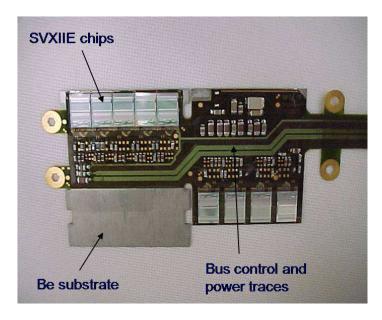

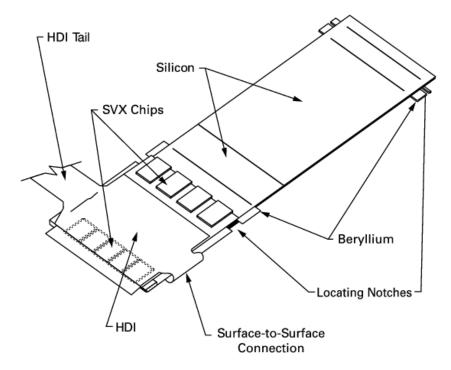

The design of the SMT was also influenced by the requirements of minimal mass, a precise alignment between sensors and support structures, and adequate thermal performance of the silicon modules in both the barrels and the disks. The barrel/disk design made it necessary to have the front-end electronics attached to the sensor structures. All these design constraints of the barrel silicon modules, called the ladders, led to a layout of the basic detector unit with approximately rectangular beryllium substrates with one (single-sided

<sup>&</sup>lt;sup>1</sup> The pseudorapidity is defined as  $\eta = -\ln\left[\tan(\frac{1}{2}\theta)\right]$  where  $\theta$  is the polar angle relative to the proton beam axis.

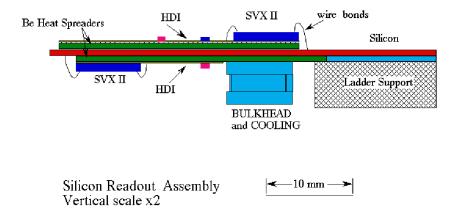

sensors) or two (double-sided sensors) silicon surfaces glued to them. The beryllium substrates conduct heat from sensors and their on-board readout to cooling and support bulkheads. They also include features which provide precise alignment of ladder sensors to the bulkhead. A printed flex circuit, called the High Density Interconnect (HDI), carrying the readout chips and passive electronics components, was laminated onto the beryllium. A long flexible tail, called the pigtail, of the HDI allowed easy routing of the data and supply lines through the barrel structures. The readout chip, called the SVXIIe chip [8] provides 128 channels, each including a preamplifier, a 32 cell deep analog pipeline, and an 8 bit ADC.

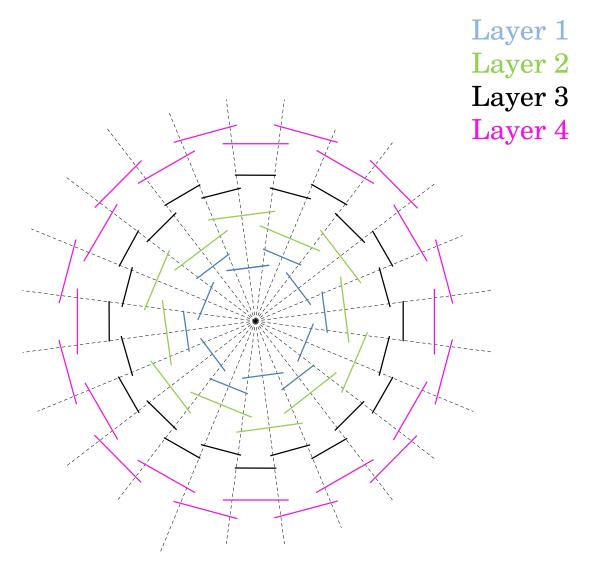

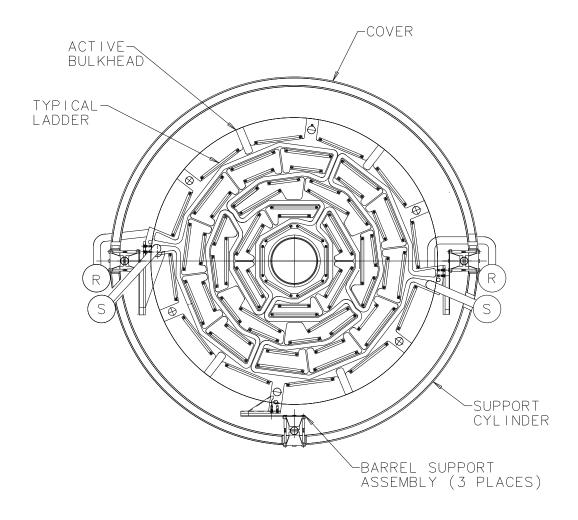

Each of the six barrels is 12 cm long and has 72 ladders arranged in four layers, with each layer having two sub-layers at slightly different radii to provide azimuthal overlap, as illustrated in Fig. 4. The two outer barrels have 36 single-sided (SS) and 36 double-sided 2° stereo (DS) ladders. The four inner barrels have 36 double-sided double-metal (DSDM) 90° stereo and 36 double-sided 2° stereo ladders. Figure 5 shows the locations of the different sensors in the six barrels. In the text the ladders are often referred to as 3-chip (SS), 6-chip (DSDM), and 9-chip (DS) ladders according to the number of SVXIIe chips mounted on them. The ladders are mounted between two precision-machined beryllium bulkheads. The bulkhead that supports the sides of the ladders carrying the readout electronics is equipped with cooling channels.

Each barrel is capped with a disk of wedge detectors, called the F-disks. The F-disks comprise twelve wedges made of double-sided silicon wafers with trapezoidals shapes. The stereo angle of the F-wedges is 30°. The n-side is connected to 6 readout chips and the p-side to 8 chips. To provide further coverage at intermediate  $|\eta|$ , the central system is completed with a set of three F-disks on each end of the barrel assembly. Each disk is rotated by 7.5° with respect to its neighboring disk.

In both the far-forward and far-backward region, two large diameter disks, called the H-disks, provide tracking information. The H-disks are made of 24 pairs of single-sided detectors glued back to back, giving a stereo angle of 15°. Each detector is read out by 6 chips. Since these disks give the last track-measuring points before the end calorimeters, the mass constraints on these detectors are more relaxed than for the F-disks or barrel ladders. This allowed the use of back-to-back single-sided detectors in a less compact package than the F-disks. The H-disks were designed to improve momentum resolution for tracks up to  $|\eta| = 3$ .

For both the F-disks and the H-disks, the wedges are mounted and aligned on beryllium rings which include cooling channels. The barrels together with the F-disks are precisely mounted on two carbon fiber cylinders which meet at the nominal interaction point in the D0 detector. The four H-disks are individually

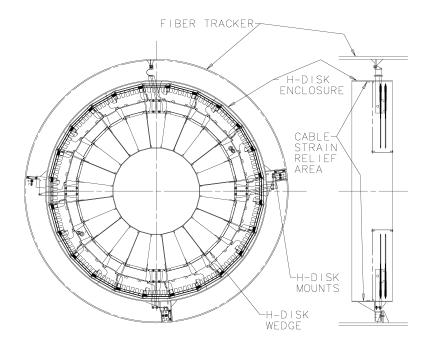

$\mbox{Fig. 4. Arrangement of barrel modules in } r-\phi.$  mounted on carbon fiber cylinders.

Table  $\, 1 \, \text{summarizes the SMT design parameters}.$

|         | Barrel 6 | Barrel 5 | Barrel 4 | Barrel 3 | Barrel 2 | Barrel 1 |

|---------|----------|----------|----------|----------|----------|----------|

| Layer 4 | DS       | DS       | DS       | DS       | DS       | DS       |

| Layer 3 | SS       | DSDM     | DSDM     | DSDM     | DSDM     | SS       |

| Layer 2 | DS       | DS       | DS       | DS       | DS       | DS       |

| Layer 1 | SS       | DSDM     | DSDM     | DSDM     | DSDM     | SS       |

beampipe

Fig. 5. The locations of the different types of ladders.

Table 1 SMT design parameters (module refers to both ladders and wedges).

|              | Barrels           | F-disks           | H-disks           |

|--------------|-------------------|-------------------|-------------------|

| Layers/Discs | 4                 | 12                | 4                 |

| Channels     | 387,072           | 258,048           | 147,456           |

| Modules      | 432               | 144               | 96 pairs          |

| Si area      | $1.4\mathrm{m}^2$ | $0.4\mathrm{m}^2$ | $1.2\mathrm{m}^2$ |

| Inner radius | $2.7\mathrm{cm}$  | $2.6\mathrm{cm}$  | $9.6\mathrm{cm}$  |

| Outer radius | $9.4\mathrm{cm}$  | $10.5\mathrm{cm}$ | $23.6\mathrm{cm}$ |

### 3 Mechanical Structure and Environment

### 3.1 Introduction

The SMT requires mechanical structures and enclosures that provide accurate positioning of the detector elements and an acceptable operating environment for the silicon. To allow optimal reconstruction of trajectories, the positions of detector elements must be known well enough that uncertainties in their positions contribute negligibly to track reconstruction inaccuracies. This placed requirements upon the position stability and upon the accuracy with which positions need to be known.

Each barrel is 120 mm long and 201 mm in diameter. The ladders are parallel to the beam pipe. The wedges are held in disks in which the planes of the wedges are normal to the beam line. The two types of disks, F-disks and H-

disks, have active regions with outer diameter of 206.4 mm and of 470.1 mm, respectively, measured along the center-lines of the sensors. Six of the F-disks are interleaved with and attached to barrels to form disk/barrel modules. The remaining disks are located at the ends of the barrel region, three F-disk and two H-disks at either end. The fiducial length of the central disk-barrel region is approximately 766 mm, the fiducial length including the F-disks is approximately 1066 mm and that including the H-disks is approximately 2432 mm. The central silicon detector, including cabling and mechanical structures, fits into a 360 mm diameter region. Including readout structures and protective enclosures but excluding mount structures, the total diameter of the H-disks is approximately 488 mm.

To limit the effects of multiple scattering and the production of secondary particles and showers, it is important that the amount of material, in the mechanical structure measured in radiation lengths, is minimized. This implies the use of large radiation length materials and the minimization of the mass of the support structure in a way consistent with other design requirements.

Both the disk-barrel modules and the end F-disks are supported from two carbon-fiber-laminate cylinders of combined length approximately 1660 mm. The two cylinders are butted against one another but electrically insulated from each another at z=0. In turn, they are supported from the inner surface of the innermost CFT barrel. Removable portions of the cylinders allowed modules to be installed. The cylinders also provide support for cables, cable connections, and coolant distribution manifolds. Each H-disk structure is independently supported from the inner surface of the innermost CFT barrel at large z via leaf-spring, ball-and-cone kinematic mounts.

In the SMT region, the beam pipe consists of a beryllium cylinder with an outer diameter of 38.1 mm and an overall length of 2378 mm.

To control noise and leakage currents in the high radiation environment, sensors are indirectly cooled by forced flow of an ethylene glycol-water mixture. The coolant temperature is typically  $-8^{\circ}$ C.

#### 3.2 Ladders and Barrels

Barrel silicon sensors are mounted on ladders which serve four purposes:

- (1) They fix the relative positions of pairs of silicon sensors and provide features which allow the sensors to be accurately positioned in the barrel.

- (2) They aid in flattening the sensors and in maintaining flatness.

- (3) They hold the HDIs.

- (4) They provide a path by which the silicon and HDI components can be

cooled.

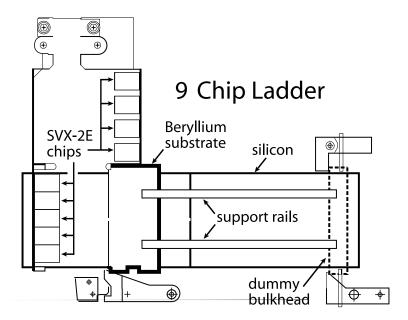

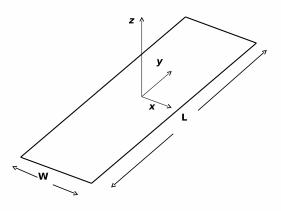

As mentioned in Sec. 2, three different types of ladders are used: 3-chip ladders, 6-chip ladders which have the same width as the 3-chip ladders, and 9-chip ladders which are wider. While the sensors for the 6-chip ladders are 120 mm long, the 3-chip and 9-chip ladders are made of two 60 mm long rectangular silicon sensors mounted end-to-end. A silicon barrel comprises four ladder layers at different radii; each layer consists of an inner and an outer sub-layer. A summary of ladder dimensions is given in Table 2.

Table 2 Ladder dimensions (mm)

| Ladder type               | 3-chip  | 6-chip  | 9-chip  |

|---------------------------|---------|---------|---------|

| Single/double sided       | S       | D       | D       |

| Stereo Angle (degrees)    | none    | 90      | 2       |

| Silicon thickness         | 0.300   | 0.300   | 0.300   |

| Length of each sensor     | 60.0    | 120.0   | 60.0    |

| Overall length            | 120.125 | 120.125 | 120.125 |

| Length of active portions | 116.7   | 116.7   | 116.7   |

| Silicon width             | 21.2    | 21.2    | 34.0    |

| Active width              | 19.2    | 19.2    | 32.0    |

| Maximum HDI width         | 25.2    | 25.2    | 38.0    |

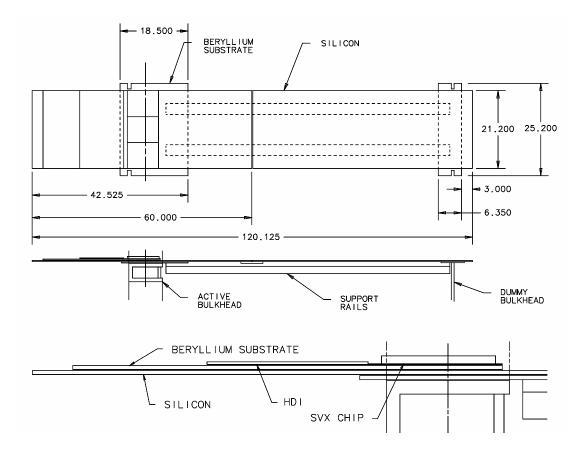

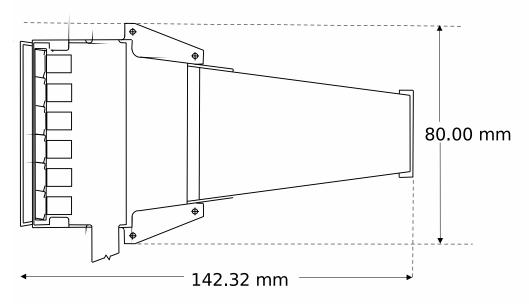

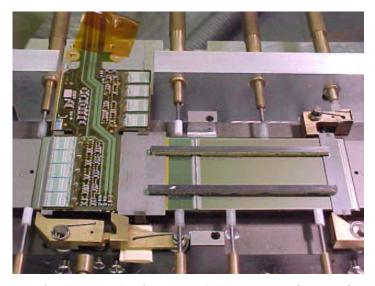

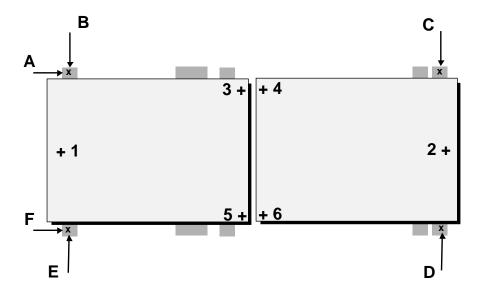

The mechanical structure of a 3-chip ladder is shown in Fig. 6. Two rails, each made of a fiber composite-Rohacell foam sandwich, interconnect and support the silicon sensors. A layer of carbon-boron hybrid fibers plus a layer of carbon fibers was used for each fiber composite to closely match the thermal expansion of the silicon sensors. At the HDI end, the rails were bonded to the 0.40 mm thick beryllium substrate which provides reinforcement in the HDI region and aids in conducting heat from the HDI components. This beryllium piece, along with another piece near the opposite end of the ladder, also provides features used in positioning and holding the ladder.

The ladders were positioned between two bulkheads, a cooled, active, bulkhead and an uncooled, passive, bulkhead. Radial positions of the silicon are shown in Table 3 and Fig. 7. The ladders are grouped into 24 equal  $\phi$  towers centered on the layer 3 ladders as shown in Fig. 4. Layers 1 and 2, the two innermost layers, have half as many ladders as layer 3. The  $\phi$  positions of ladders in layers 1 and 2 have been chosen to cover two towers. Each tower includes portions of 4 ladders.

Fig. 6. Mechanical structure of the 3-Chip ladder with dimensions given in mm. The bottom picture is a blow-up of the HDI area shown in the middle picture. The bulkheads are part of the support structure and not part of the ladder.

Several considerations drove the choice of ladder location on the bulkheads.

- (1) Adequate overlap between adjacent ladders was provided to ensure complete  $\phi$  coverage within each layer. This places restrictions on the maximum average radius of a layer, given the active widths and numbers of ladders.

- (2) Sufficient space was provided between layers to permit ladder installation. The overall radial space for installing ladders is indicated in Tables 4 and 5. The minimum bulkhead layer-to-layer radial clearance is 10.25 mm, allowing 1.73 mm clearance on both surfaces of an installed ladder, assuming a ladder already in place on the opposite sub-layer surface.

- (3) The space needed for a  $3.175\,\mathrm{mm} \times 7.366\,\mathrm{mm}$  cooling channel placed a lower bound on the sub-layer radial spacing.

- (4) A minimum space of 5.516 mm was left between inner and outer sub-layer ladder mounting surfaces for cables. Components which extend from the ladder surfaces reduce the clear space for cables to about 2.7 mm.

Table 3 Ladder silicon radial positions along each ladders centerline.

| Layer | Sub-layer | Ladders/  | R (mm) |

|-------|-----------|-----------|--------|

|       |           | sub-layer |        |

| 1     | Inner     | 6         | 27.15  |

|       | Outer     | 6         | 36.45  |

| 2     | Inner     | 6         | 45.50  |

|       | Outer     | 6         | 55.54  |

| 3     | Inner     | 12        | 67.68  |

|       | Outer     | 12        | 75.82  |

| 4     | Inner     | 12        | 91.01  |

|       | Outer     | 12        | 100.51 |

Table 4

Total radial height of a ladder from the bottom up.

| Element                 | Radial      |  |

|-------------------------|-------------|--|

|                         | height (mm) |  |

| Rail                    | 2.757       |  |

| Adhesive                | 0.075       |  |

| Silicon sensor          | 0.300       |  |

| Adhesive                | 0.075       |  |

| Beryllium               | 0.406       |  |

| Adhesive                | 0.075       |  |

| HDI under chips         | 0.117       |  |

| Adhesive                | 0.075       |  |

| SVXIIe chip             | 0.381       |  |

| Wire-bonds (above chip) | 0.500       |  |

| Total                   | 4.761       |  |

(5) Space between adjacent ladders of a sub-layer was left for a 9.4 mm wide layer-to-layer coolant connection. This limits the minimum radius of a layer, given ladder physical widths and the number of ladders in the

Fig. 7. Ladder positions on the active bulkhead. Four manifolds, two supply and two return, are indicated in the figure with S and R.

layer.

Final machining of the active and passive bulkheads of a barrel was done with the bulkheads clamped together as a unit. This ensured that bulkhead ladder mounting surfaces and mounting features match on each pair of bulkheads and helped ensure that installed ladders would be parallel to the beam line. Mounting surfaces were machined to a flatness of approximately  $25\,\mu\mathrm{m}$ , and the mounting surfaces on the  $9.525\,\mathrm{mm}$  thick active bulkhead were made perpendicular to the plane of the bulkhead to  $25\,\mu\mathrm{m}$ . This establishes a maximum ladder slope at the active bulkhead of  $25/9525=2.6\,\mathrm{mrad}$ . Assuming this slope, perfect alignment of the active and passive bulkheads, and the appropriate elastic properties of a ladder, implies about  $53\,\mu\mathrm{m}$  maximum radial deflection of the ladder from a straight line.

Table 5 Radial heights above the bulkhead mounting surface for an installed ladder.

| Element                | Radial      |  |

|------------------------|-------------|--|

|                        | height (mm) |  |

| Adhesive               | 0.051       |  |

| Beryllium              | 0.406       |  |

| Adhesive               | 0.075       |  |

| Silicon sensor         | 0.300       |  |

| Adhesive               | 0.075       |  |

| Beryllium              | 0.406       |  |

| Adhesive               | 0.075       |  |

| HDI under chips        | 0.117       |  |

| Adhesive               | 0.075       |  |

| SVXIIe chip            | 0.381       |  |

| Wire-bonds above chips | 0.500       |  |

| Total                  | 2.461       |  |

Ladders were positioned laterally with the aid of posts on the active and passive bulkheads which extend from the bulkhead mounting surfaces and engage notches in the ladder beryllium. Only the beryllium piece closest to the bulkhead mounting surface and the edges of the posts closest to the ladder centerline were used for this purpose. Clearances between notches in the beryllium piece of the ladder and the posts were chosen so that ladders could be placed on each bulkhead with a transverse accuracy of  $\pm 6\,\mu\mathrm{m}$ . Malleable pins through holes in the posts hold the ladder in place. In addition, the outermost layer ladders were glued in place to provide a rigid coupling between the active and passive bulkheads. The ladders play a very important structural role in the barrels. Each barrel is a complete, internally aligned unit. All barrel positioning was done with respect to the active bulkhead. The passive bulkhead is held and accurately positioned by the ladders and sets only the relative positions of ladders.

The barrel structure formed by the ladders and bulkheads must be sufficiently stiff that internal alignment criteria are satisfied under forces from the cables, the coolant connections, and thermal contraction. The required stiffness is provided without the use of additional structural members, by fastening ladders to the bulkheads with epoxy. The total barrel structure has a torsional

Fig. 8. Barrel cable paths.

compliance of  $0.11 \,\mu\text{m/N}\cdot\text{m}$  assuming that the passive bulkhead positions ladders relative to each other only in r and  $\phi$ . Uncontrolled forces on the barrels are approximately 1 N. This leads to a negligible shift in ladder  $\phi$  positions. Shear stresses in the most highly stressed epoxy joints with a 1 N force applied to the passive bulkhead at a radius of 100 mm are  $0.0050 \,\text{MPa}$ , a factor of more than 1300 below the shear strength of the electrically and thermally conductive adhesive used (e.g., TraCon 2902 silver-filled epoxy).

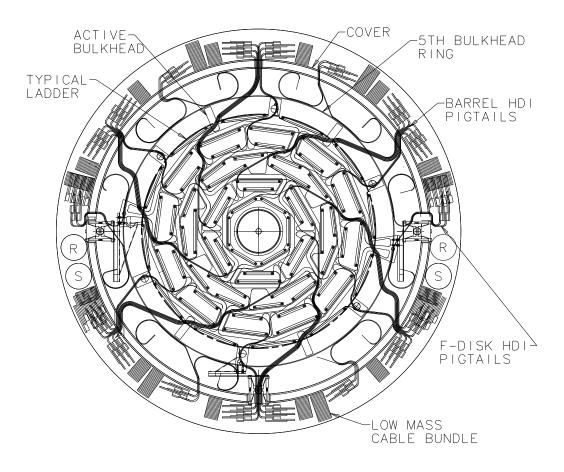

The pigtails that emerge at the HDI edge follow paths between and around ladders to the outer radius of the barrel, penetrate the support half-cylinder or its covers, and connect to low mass cables mounted on the outside. An extra bulkhead ring, made of carbon fiber composite, is provided at a radius of about 130 mm to anchor the cables. The cables are grouped at this ring into bundles which are brought through the half-cylinder and its covers at 2:00, 4:00, 6:00, 8:00, 10:00, and 12:00 o'clock as shown in Fig. 8.

Fig. 9. F-disk detectors.

### 3.3 F-Disk and F-Wedge Structure

As mentioned in Sec. 2, each barrel is accompanied by an F-disk, and three more F-disks each are installed in the forward and backward regions. The schematic for an F-disk is shown in Fig. 9. It contains 12 double-sided wedges which are installed with alternating p- and n-sides. The dodecagon support structure is made of beryllium and has a cross-section of  $15.7\,\mathrm{mm} \times 2.5\,\mathrm{mm}$ . A  $7.5\,\mathrm{mm} \times 1.0\,\mathrm{mm}$  channel in the beryllium provides a path for coolant flow to cool the wedges. Disks are oriented so that the wedges match the barrel towers.

The disk thickness contributes to the z-gap between adjacent barrels. To minimize this thickness, the HDI was placed at the outer periphery of the wedge. The thickness of the structure is  $4.850\,\mathrm{mm}$  at the detector sensor and  $6.322\,\mathrm{mm}$  at the SVXIIe chips, including 1 mm for two sets of wire-bonds. With additional clearance to avoid potential interference and accommodate thickness

variations, the interleaved disks fit within a barrel-to-barrel gap of about 8 mm.

A disk was attached to the active bulkhead of each barrel to form a disk/barrel module. This permitted the disk and barrel to be accurately matched and to be installed as a unit. Each of the interleaved disks was attached to a barrel at three points spaced evenly in  $\phi$ . The posts are permanently attached to the beryllium disk support structure.

### 3.4 Module Support

The disk/barrel modules and end disks were mounted from the support half-cylinders in a way which adequately resists the known gravitational forces and the somewhat variable forces from cabling and coolant connections. Provided that temperature variations are sufficiently independent of  $\phi$ , thermal contraction effects are predictable. The thermal expansion coefficient of beryllium, 11.6 ppm/°C, leads to a radial contraction of 21  $\mu$ m for a 100 mm radius structure which is cooled from 23°C to 5°C. Since the connections from disks and disk/barrel modules to the support half-cylinder are all nearly identical, the vertical center-lines of these structures move together and good relative alignment is maintained.

The support half-cylinder is described in Sec. 3.7. Carbon fiber composite mounts attached to the active bulkheads connect disk/barrel modules to the half-cylinder at 3:00, 6:00, and 9:00 o'clock as shown in Fig. 7. The 3:00 and 9:00 o'clock mounts control y and z positions, while the 6:00 o'clock mount controls x and z positions. Pairs of leaf springs allow motion in one direction while remaining stiff in the other two directions. A sapphire ball between the half-cylinder portion of the coupling and the barrel portion of the coupling permitted angular orientations to be matched during assembly; four screws around the ball allowed for adjustment and locking of the angular orientation.

#### 3.5 H-Disk and H-Wedge Structure

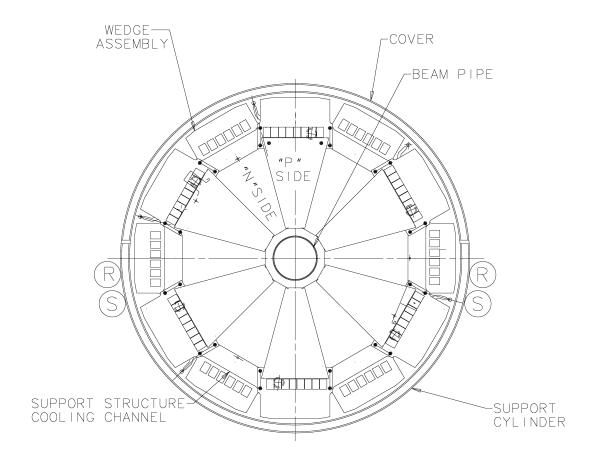

An H-disk is shown in Fig. 10. It contains 24 wedges which alternate on each surface of a beryllium cooling pipe. Four disks were deployed for Run IIa, at  $z \approx \pm 100$  and  $\pm 121$  cm. In Run IIb the two outermost disks were removed. Within a disk, the alternating wedges are separated by 9.1 mm in z and the sensors are separated by  $\approx 1.2$  mm within a wedge. The disks are supported by a ball-and-cone mount from the CFT carbon fiber support cylinder. The disk supports were installed and aligned on the CFT support cylinder using a coordinate measuring machine during the assembly of the CFT to insure precise alignment during installation of the disk assemblies in D0.

Fig. 10. H-disk assembly.

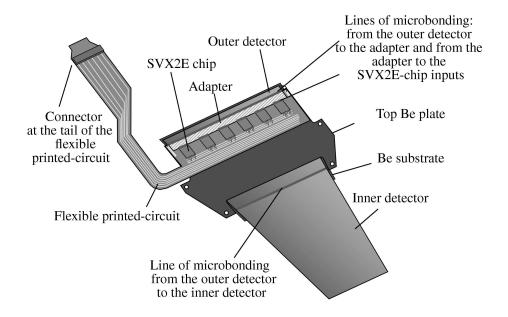

An H-wedge was fabricated from two back-to-back, single-sided, detector assemblies (Fig. 11). The inner and outer radii at the wedge centerline are 9.61 cm and 23.6 cm, respectively. The detector pair is supported by a beryllium plate, which also forms the wedge support for attachment to the beryllium cooling ring. Front and back detectors on a wedge were aligned using a specially fabricated dual microscope alignment system.

#### 3.6 Cooling

The heat to be removed from detector-mounted readout electronics is summarized in Table 6. The combined power dissipation for the SVXIIe chips and other HDI components is about 3 mW per channel. Heat loss in the cabling brings the total power dissipation to about 2400 W.

The ethylene glycol/water cooling was chosen because of the favorable heat capacity of water and the simplicity of water systems. The cooling system consists of a reservoir, pump, flow control valve, de-ionizer, vacuum system, supply lines, return lines, and instrumentation. The pump circulates approximately 60 l/min of coolant. At this flow rate, the barrels, disks, and manifolds produce an aggregate pressure drop of 55 kPa. To prevent coolant from leaking

Fig. 11. H-wedge assembly.

Table 6 Detector power dissipation (watts).

| Elements       | Dissipation     | Number of           | Dissipation         |

|----------------|-----------------|---------------------|---------------------|

|                | (watts)         | Modules             | (watts)             |

| Barrel         |                 |                     |                     |

| 3 chip         | 1.15 per ladder | 36 per outer barrel | 41 per outer barrel |

| 6 chip         | 2.30 per ladder | 36 per inner barrel | 83 per inner barrel |

| 9 chip         | 3.46.per ladder | 36 per barrel       | 124 per barrel      |

| F-disks        | 5.38 per wedges | 12 per disk         | 65 per disk         |

| H-disks        | 2.30 per wedges | 48 per disk         | 110 per disk        |

| Outer barrels  | 165 per barrel  | 2 barrels           | 331                 |

| Inner barrels  | 207 per barrel  | 4 barrels           | 826                 |

| F-Disks        | 65 per disk     | 12 disks            | 778                 |

| H-Disks        | 110 per disk    | 4 disks             | 442                 |

| Detector total |                 |                     | 2377                |

onto the detector components if leaks occur, the coolant pressure of the supply manifold at the detector is maintained at about  $90\,\mathrm{kPa}$ . This pressure is achieved with an open bath on the suction side of the system from which fluid

is drawn through the detector; the pressure drop in the piping to the detector and elevation difference between the open bath and the detector determine the pressure at the inlet to the detector. The pump is located at the floor of the collision hall to take advantage of the available heat to ensure adequate pressure on the suction side of the pump to avoid cavitation in the pump.

With 30% ethylene glycol/water mixture the system is operating at  $-8^{\circ}$ C. The temperature within sensors varies with location from approximately  $-5^{\circ}$ C to  $+2^{\circ}$ C. The cooling system was designed to allow temperature to be lowered another 7°C if compensation for the effects of radiation damage proves to be necessary.

Four coolant manifolds, two supply and two return, provide coolant flow to the barrels and disks. Each barrel requires two supply and two return connections, as shown in Fig. 7. The cooling channel of each layer of a barrel bulkhead is divided into equal left and right portions. The left portions of all layers are connected in series between the left supply and return manifolds. Similarly, the right portions are connected in series between the right supply and return manifolds. Layer-to-layer connections were machined as part of the bulkhead beryllium structure.

Disk coolant flow is divided between equal length upper and lower paths. The two paths share coolant connections at 3:00 and 9:00 o'clock. To equalize flow rates in the supply and return manifolds, the flow direction is reversed from one disk to the next. A set of supply and return manifolds is located on the outer surface of the half-cylinder near 3:30 o'clock; a second set is located near 8:30 o'clock. The supply manifolds enter the half-cylinder region as 15.875 mm inside diameter (ID) lines. Approximately 700 mm along the half-cylinder, after supplying the end disks and the first barrel/disk module, both lines reduce to 12.7 mm. The return manifolds have the same configuration, starting as 12.7 mm ID pipe and then increasing to 15.875 mm ID pipe between the second and third barrel/disk modules. This configuration of reducing supply manifold size and increasing return manifold size produces evenly divided flow to the detectors. The manifolds are fabricated from thin-walled PVC pipe. Coolant connections from the disks and disk/barrel modules to the manifolds were made with flexible tubing.

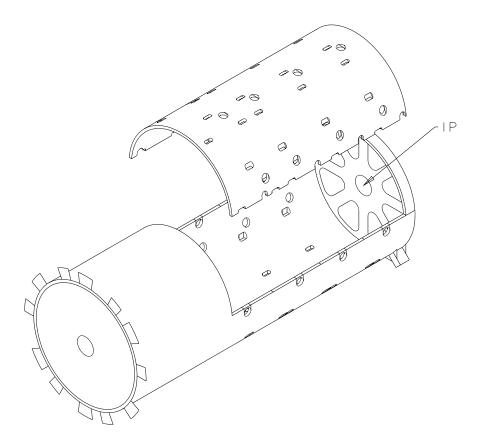

### 3.7 Half-Cylinder and Cover

Carbon fiber half-cylinders (Fig. 12) provide accurate and stable support of detector elements. The half-cylinders are 1.1 m long, have an inside radius of 145 mm, and outside radius of 153 mm. The half-cylinders consist of 0.9 mm thick inner and outer shells joined by 0.4 mm thick webs. The webs are spaced

Fig. 12. Support half-cylinder and cover. IP denotes the nominal central interaction point. The holes seen on the barrel are where the cables and cooling lines pass through it. The structure on the left disk is support for the cables.

every  $25.65 \,\mathrm{mm}$  in z. The outer ends of the half-cylinders are closed by  $2 \,\mathrm{mm}$  thick full circular membranes which have appropriate openings for the beam pipe, cables, and coolant manifolds. The inner ends, near  $z{=}0$ , have  $0.5 \,\mathrm{mm}$  disks with large wedge-shaped cutouts to reduce mass in this critical region. A third circular membrane is present just beyond the outermost F-disk assembly.

The support half-cylinders were made from high modulus (900 MPa) carbon fiber prepreg plies. The high modulus carbon fiber has a low thermal expansion coefficient, high stiffness to mass ratio, reasonable cost, and acceptable fabrication properties. A low coefficient of thermal expansion ensures that temperature gradients do not cause significant displacement of detector elements in the face of the large thermal gradients from the coexistence of cooled surfaces and hot electronic chip modules. The high modulus minimizes deflections caused by gravitational, cabling, and coolant connection forces. Multiple high modulus carbon fiber plies are combined at specific angles to achieve a thermal expansion coefficient of approximately 0.9 ppm/°C. The elastic mod-

ulus of the laminate is approximately  $124\,\mathrm{GPa}$  ( $18\times10^6\,\mathrm{psi}$ ). This provides a stiffness to radiation length ratio which is five times that of steel and three times that of aluminum. The high modulus carbon fiber is an excellent electrical conductor for the frequencies of concern for electronic noise (up to  $1\,\mathrm{MHz}$ ). The outer surface of the half-cylinder is wrapped with 2" wide aluminum foil tape near the outer end to provide a connection from the carbon fiber to the electronics ground.

Finite element analysis, confirmed by analytical calculations, give a maximum half-cylinder deflection of  $100\,\mu\mathrm{m}$  and rotations about the x-axis of  $70\,\mu\mathrm{rad}$  at the locations of the first and last barrels. Only a fraction of this maximum deflection occurs over the length of the silicon tracker itself. Final alignment of each barrel/disk and end-disk assembly were done after the half-cylinders were fully loaded (including cables) with the cylinders supported off their final mounting points so errors due to cylinder deflection were effectively removed.

The shells and webs were made as separate components from several layers of unidirectional carbon fiber prepreg tape. Each component was formed and cured at an elevated temperature. The components were assembled to form the half-cylinder structures using room temperature curing epoxy.

The half-cylinders are supported from the CFT near z=0 and at z=830 mm. At the inner end the cylinders have two feet located at  $\pm 45^{\circ}$  from the bottom with spherical ceramic ends resting in reinforced mounting points attached to the inner wall of the CFT.

Covers for the half-cylinder provide a thermal barrier, mechanical and light protection, electrostatic shielding, and a mounting surface for the low mass data cables. The covers have the same mechanical configuration as the half-cylinders of an inner and an outer skin coupled with thin radial webs. Holes are provided to allow alignment of the completed assembly.

### 3.8 Run IIa Beam Pipe

The part of the Tevatron Run IIa beam pipe that passes through the SMT has a 38.1 mm outside diameter and a 0.508 mm thick wall. Bellows and knife-edge flanges are provided at each end of the 2.578 m long beam pipe assembly. The Run IIb beam pipe is described in [7].

The beryllium beam pipe was fabricated by rolling a beryllium sheet into a round cylindrical shape and joining the edges with a vertical strip, providing four fillet locations for brazing. All beryllium to beryllium, and beryllium to stainless steel joints are brazed with an aluminum filler material.

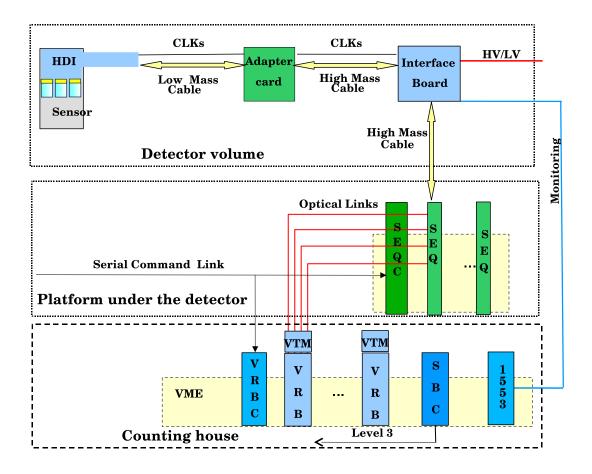

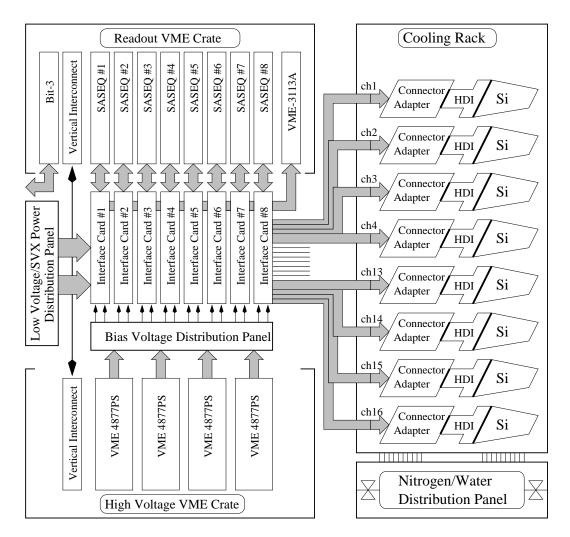

Fig. 13. D0 SMT readout system.

### 4 Electronics

### 4.1 Introduction

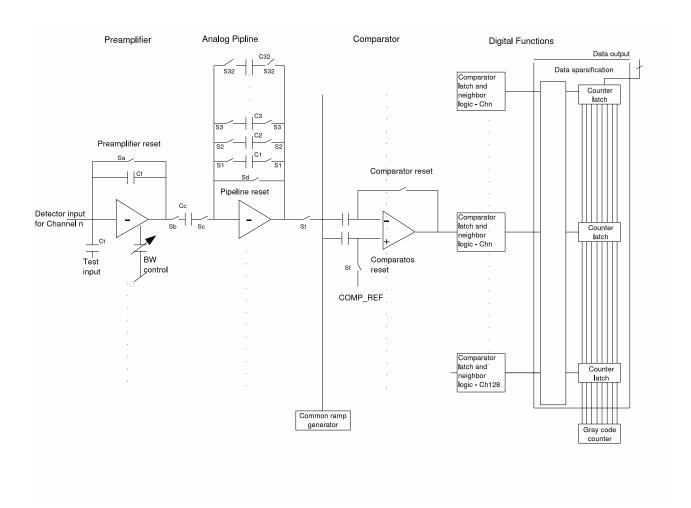

The data acquisition and readout system for the SMT is responsible for gathering the charge from the silicon sensors, digitizing these data, and sending it to the D0 data acquisition system. The MIL-STD-1553 connection [9] to the D0 Control System provides the ability to download and monitor the readout electronics. The readout system is depicted in the block diagram shown in Fig. 13. The locations of the components are also indicated in the figure.

The electronics design for the SMT was dictated by the physics needs of the experiment, the engineering resources that were available, and the chip technology. The SVXIIe chip has 128 channels and a 32 deep pipeline delay to allow time for trigger formation; it can operate with 132 ns bunch spacing. The chips are mounted on the HDI, a polyimide hybrid. One HDI supports between three and nine chips depending on the sensor arrangement. The pigtail on the HDI allows the chip signals to be routed to the outer edge of the detector before installing a connector.

From the connector at the outer edge, a special polyimide cable, called the low mass cable, carries the signals for a distance of about 3 m to a small passive circuit board referred to as the adapter card. The adapter card interfaces the low mass cable to an 80-conductor 3M pleated foil cable. Two low mass cables are connected to each 80-conductor cable. Signal dispersion in this two-cable combination limits the combined length to about 15 m. The 15 m point is at the base of the liquid argon calorimeters. Since there is not enough space in this area to house the readout, a repeater board, called the interface board, was installed to retransmit the signals to the electronics area under the detector. The power supplies for the SMT are also located on the side of the central calorimeter cryostat near the interface board.

The repeated signals are sent to a sequencer module (SEQ) located under the detector on the D0 platform. The sequencer generates the sequences to download parameters into the SVXIIe chips, to put the chips into data acquisition mode, and to have the chips digitize and read out data in response to a trigger. During readout, the sequencer sends serialized data over a fiber optic link to a VME module, called a VME Read Out Buffer (VRB) [10]. The optical data are converted to 20-bit parallel data words by the VRB Transition Module (VTM) before reaching the VRB. The VRB buffers the data from each Level 1 triggers and waits for a Level 2 trigger accept. If one occurs, data are sent over the back plane to a VME readout controller and then sent over ethernet to the Level 3 processor farm.

The following sections provide more detailed descriptions of the various components and the reasons for the design choices.

### 4.2 Low Noise Design

Designing a precision, small-signal-level detector involves a complex interplay of mechanical and electrical design constraints. Many of the mechanical components are electrical conductors so they also have an affect on the electrical performance of the detector. The main goals were to minimize induced noise in the calorimeter, properly ground the beryllium mounting plates, and eliminate ground loops and other unwanted current paths through the detector.

The SMT is situated in the center of the calorimeter and many components are mounted on the calorimeter cryostat so preventing noise pick up required careful design. It was decided not to take additional triggers while the SMT was digitizing and reading out data, which means that when a Level 1 trigger occurs, all further Level 1 triggers are inhibited until all the data is read out from the current trigger. This results in Level 1 dead time for each Level 1 accept. The design of the SMT was simplified by this decision since the calorimeter signals are already stored in the calorimeter readout electronics when the SVXIIe digitization starts. In fact, many of the design choices such as single-ended output from the SVXIIe and unshielded low mass cables would not have worked with simultaneous acquisition and digitization. Tests have shown that SMT digitization and readout generates noise signals in the calorimeter.

The only SMT signal that is active during calorimeter data taking is the clock, which is carefully shielded. The signal is sent differentially on a small, high quality coaxial cable using RF connectors. The pair of coaxial lines that are in the calorimeter bore are housed in a single braided shield, and both lines are terminated on the HDI. There is no observable noise from the clock system.

The second area of concern was the grounding of the beryllium plates. There are two important grounds for these plates. The first is the connection to the HDI. If this ground connection is not properly made, the beryllium will act as a floating capacitor, and any voltage induced on the plate will spread over the entire plate and then capacitively couple into the readout channels. This ground is achieved by bonding the ground plane on the back of the HDI directly to the beryllium with conductive epoxy. The other concern was the double sided detectors. These modules have beryllium plates on each side of the sensor, so they form a parallel plate capacitor with the sensor in the center. Any ground loop through this capacitor will induce noise into the sensor. The original solution was to use silver epoxy to form a conducting bridge between the two pieces of beryllium. There is no direct contact in this case, so the connection is dependent on the silver epoxy. Some of these bonds became resistive so all of the modules were repaired by wiring the pieces together. The wire attachments to the beryllium were made with indium solder.

The final issue was ground loops through the SMT. The SMT is read out from both ends, and each end is locally grounded. A potential difference might occur between the two ends and current will then flow in any path connecting one end of the detector to the other. If this current flows through the signal path, the detector will see this current as noise. Therefore an electrical break was made at z=0 for both the detector structure and the cooling path. The cooling pipes were also electrically isolated by plastic tubes at both entrances to the SMT detector.

The common ground point for each half of the SMT was achieved by an aluminum ring which was constructed on the face of the calorimeter with all the adapter cards mounted on it. The ring was electrically isolated from the calorimeter and the adapter cards were all grounded to the ring. The ground connection to the SMT is made through the parallel combination of all the low mass cables.

### 4.3 SVXIIe Chip

The SVXIIe chip [8] is a 128 channel, full custom, mixed analog and digital integrated circuit. The main parameters are listed in Table 7.

Table 7 SVXIIe properties.

| SVXIIe Property                  | Value                       |

|----------------------------------|-----------------------------|

| Process technology               | 1.2 micron CMOS             |

| Chip size                        | 6.3 by 8.7 mm               |

| Number of channels               | 128                         |

| Maximum interaction rate         | 132 ns between interactions |

| Detector input capacitance       | 10 to 35 pF                 |

| Number of bits in ADC            | variable up to 8 bits       |

| Number of pipeline stages        | 32                          |

| Preamp dynamic range             | 240 pC                      |

| Wilkenson ADC clock frequency    | Maximum of 53 MHz           |

| Readout clock frequency          | Maximum of 26.5 MHz         |

| On chip zero suppression         | Yes                         |

| On chip test pulser              | Yes                         |

| Daisy chained operation          | Yes                         |

| Simultaneous trigger and readout | No                          |

The chip was designed by a collaboration of engineers at Fermilab and Lawrence Berkeley Laboratory, and it was fabricated in the UTMC radiation hard  $1.2 \,\mu\mathrm{m}$  CMOS technology. Each channel consists of an integrating preamplifier which converts charge to voltage, a 32 deep pipeline which is implemented as a string of 32 capacitors, and an 8 bit Wilkensen type ADC. A simplified diagram of

one of the channels is shown in Fig. 14. All 128 channels are connected to a data readout section which can either read out all channels, just those above a digitally set threshold, or those above threshold plus one channel on either side of those above threshold. The latter mode can cross chip boundaries to adjacent chips mounted on the same HDI. The integrator integrates charge continuously until it is reset, but the charge into each pipeline capacitor is only the increment in charge between beam crossings. This means that there is a correlated double sampler between the integrator and the pipeline, so that only the change in charge between the previous beam crossing and the current beam crossing is put into a pipeline capacitor. The pipeline is controlled by two counters which are configured as ring counters which means that the pipeline is a ring of capacitors. There is a write counter which points to the next available capacitor in the ring. When a new beam crossing occurs, the value of the input signal is written into the capacitor pointed to by the write counter. The read counter is identical to the write counter, but it is delayed by a down-loadable pipeline delay. The beam crossing clock that samples the charge also steps the write pointer and the read pointer ring counters. If there is a trigger, the counters are stopped and the capacitor pointed to by the read counter is digitized and read out.

The SVXIIe was designed to minimize both power consumption and detector mass. It consumes approximately 3 mW per channel and has only 19 connections to the outside world. This small number of connections was achieved by making the function of many of the lines mode dependent. For example, the 8 bit readout bus is used for control functions in all modes but readout.

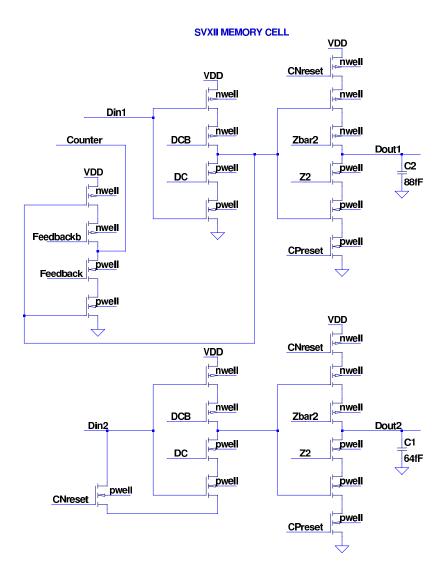

A portion of the SVXIIe schematic containing the dynamic memory cell is shown in Fig. 15.

The chip has four modes of operation with only one mode active at a time. This means that it is not possible for the chip to acquire data at the same time it is digitizing or reading out other data.

The first mode is the download mode where settable parameters are loaded into the chip. There are 190 bits in the download register for each chip. The download is implemented as a long serial shift register using only two chip pads called top neighbor and bottom neighbor and the clock. Data are shifted into the top neighbor pad and out of the bottom neighbor pad. The output from the last chip's bottom neighbor is read back into the sequencer. Thus, a three chip HDI requires sending 570 bits over the MIL-STD-1553 link [9]. The chip does not have a read command to read the data back. The data shift through the chip string two or more times and the sequencer compares the read-back data to the input.

The second mode is acquire. In this mode, every time a clock pulse arrives, the

Fig. 14. A block diagram of a single channel of the SVXIIe chip.

chip samples the change in charge on the input capacitor and stores the data into a pipeline capacitor. The ring counter pointers are incremented and the process is repeated. There is no specific trigger line. When a trigger occurs, the sequencer stops the beam crossing clock and changes the mode to digitize. The correct capacitor to digitize is pointed to by the read counter.

Digitization is accomplished by transferring the charge from the selected capacitor onto a capacitor connected to a comparator. The pipeline capacitor is then reset and the offset voltage is subtracted from the charge on the comparator capacitor. This minimizes any offsets that may be present in the pipeline. Actual digitization is accomplished by putting a linear voltage ramp on the other input to the comparator and starting a counter at the same time. The 53 MHz digitization clock increments this counter on both edges of the clock pulse giving an effective clock rate of 106 MHz. When the ramp voltage reaches the input value, the counter is stopped.

The final mode is readout. The counter values are shifted into a pipeline and the pipeline is compressed if zero suppression is enabled. Since the chip is

Fig. 15. A portion of the SVXIIe schematic showing the dynamic memory cell.

designed to be used in a multi-chip configuration, the readout bus is configured as a tri-state bus during readout. Control of the bus is passed between chips through the top neighbor and the bottom neighbor connections. A signal on the top neighbor during readout gives the chip control of the output bus. When it is finished it signals the bottom neighbor to give control to the next chip or, if it is the last chip, to tell the sequencer that readout is done.

Once the pipeline has been compressed and the chip has control of the output

bus, the data is read out, one byte at a time. A 7 bit channel ID and an 8 bit data word are read out on each cycle. The clock is run at one-half of the normal 53 MHz, and data is read out on both edges of the clock. This reduces the bandwidth requirement on the readout cable but it places severe restrictions on the clock duty cycle. Small changes in the clock duty cycle can cause one edge of the data strobe to be missed which then interchanges the channel ID and data for the rest of the readout. In sparsification mode, when only channels over a threshold are read out, this error is not easily detected.

The SVXIIe has a sophisticated method for testing itself and the entire down-stream readout electronics. The test circuit, called cal\_inject, consists of a capacitor connected by a switch to each of the front end channels at the input to the preamplifier. The switch is activated through a transition on bus line 7 in acquire mode. The 128 bit cal\_inject mask (1 bit per channel) is a down-loadable parameter so all possible patterns can be generated. The pulse amplitude can either be set by an external source or from an internal one that is controlled by a 3 bit DAC. The DAC setting is also a down-loadable parameter.

All of the power connections are at the back of the chip, including the power for the front end amplifiers. The chip's metal layers have too-high resistance for the front end amplifiers to get enough power. A row of double wire bonds was made along exposed sections of the upper metal layer connections for front end amplifier power to reduce this resistence by creating parallel paths for current flow. The spacing of the exposed sections kept the wire bond distances reliably short.

Even though the average chip power consumption is low, the current varies by nearly a factor of two between an idle state and readout, so if there is no local monitoring of the voltage by the power supply, often referred to as remote sensing, there could be a substantial change in chip voltage. The layout of the system makes remote sensing quite difficult. One supply feeds a large number of HDIs. Two HDIs are fed through the 80-conductor cables. These cables have many different lengths since they had to be as short as possible in order to fit in the space between the central and end cryostats. Finally, the number of chips varies between HDIs. The best option was to locate the power supplies as close to the detector as possible. The place with adequate space was at the base of the central calorimeter near the interface boards. The local magnetic field is about 200 G at this location, so the power supplies had to have magnetic shielding. In addition, safe practice required fusing each power line for each of the three voltages for groups of four strings of SVXIIe chips. This required a fuse panel with about 40 fuses at four locations at the base of the calorimeter.

Fig. 16. An HDI for a 9-chip detector (prior to folding and lamination).

## 4.4 High Density Interconnect

The HDI is a two-layer flexible printed circuit with  $50 \,\mu\mathrm{m}$  polyimide with  $125 \,\mu\mathrm{m}$  line spacing and  $50 \,\mu\mathrm{m}$  vias. The circuits are laminated to beryllium heat spreaders. One HDI and its beryllium substrate are epoxied directly to one silicon sensor. Precision notches machined into the heat spreaders provided the alignment of the silicon ladders on the bulkhead. The HDI consists of SVXIIe chips, resistors, capacitors, and an interface circuit, which are mounted in the area which are in direct contact with the silicon sensor. The SVXIIe chips are wire bonded directly to the sensors. The second part of the HDI, the pigtail, is the extension of the signal and power traces to the outer radius of the silicon detector region.

A picture of an HDI for a 9-chip detector is shown in Fig. 16.

Multiple layer polyimide circuits with very fine spacings are difficult to make because the polyimide stretches easily. A ceramic HDI would require several layers to provide the required number of signal, power, and ground planes. The small number of connections on the SVXIIe and clever use of wire bonds made it possible to make a polyimide HDI with only two layers. The output bus and control lines were laid out in a row of parallel lines in front of the string of chips. Connections from each chip to the different lines were made

by running the wire bond over the intervening traces. Bypass capacitors were mounted outside the bus lines and longer wire bonds were used to connect to the capacitors. Thus, the equivalent of a multilayer circuit was made with wire bonds. The longest wire bonds approach the maximum allowable length so if there were many more lines to connect, this method would not have worked.

Six different types of HDIs were needed to accommodate the various detector and readout geometries. In the case of double-sided ladder detectors, a single circuit contained the readout for both the p- and n-sides with the polyimide folded over to sandwich the sensor. The double-sided F-wedges have one separate HDI on each side. A single HDI would have implied daisy-chaining 14 readout chips, which was considered too risky in case of a chip failure and too expensive in terms of readout time. The barrel detectors employ 9-chip HDIs for the double-sided ladders, 6-chip HDIs for the 90-degree stereo ladders, and 3-chip HDIs for the single sided ladders. The F-wedges are read out by an 8-chip HDI for the p-side, and a 6-chip HDI for the n-side. Each single H-wedge is read out with one 6-chip HDI.

All HDIs have the same functionality. They provide one 8-bit data bus connecting all of the SVXIIe chips to the data path interface circuit, distribute the differential input clock and single-ended mode control signals to all the SVXIIe chips, distribute the various analog voltages required by the SVXIIe chips, and silicon bias, and provide monitoring of the temperature of the beryllium heat spreader.

#### 4.5 Low Mass Cables and Adapter Card

The HDI readout cables are routed between the ladders in the barrel to a larger radius outside of the barrel vertex volume. There the pigtails are trimmed to length and attached to the low-mass cables. The low-mass cables are flex-circuit striplines, to minimize the amount of material in the sensitive volume. They were fabricated by Honeywell [11] and carry the digital signals and power between the hybrids and the adapter cards. To minimize any deterioration of the clock signals, the clock signals are brought to the hybrids through minicoaxial cables. Signal traces and broad power and ground traces are located on both sides of a polyimide dielectric about  $100\,\mu\mathrm{m}$  thick. The low-mass cables are routed along the half-cylinder and coupled to the 80-conductor pleated foil cables at a ring of adapter cards located between the calorimeter cryostats. Each adapter card takes the signals from two HDIs and, without further signal processing, launches them on the high quality 80-conductor pleated foil cable to the interface board. The clock signals are carried by separate coaxial cables attached to the 80-conductor cable.

## 4.6 Interface Board

The interface board serves as a repeater for the signals between the SVXIIe and the sequencer. Each board handles up to eight detector modules. It also provides the distribution of the bias voltage to the sensors, allows remote control (on/off) of the power for the SVXIIe chips, and provides monitoring of the chip voltages, and currents.

The interface boards are housed in eight 9U×280 mm crates with custom backplanes, using 16–18 slots per crate. Two crates are placed at each of four locations at the base of the central calorimeter.

Temperatures of the beryllium heat spreaders are monitored on the interface board. A jumper on the interface board provides a selectable temperature trip at 40°C or 65°C. The circuit is designed not to trip due to an open or short circuit. Calibration is adjusted by a trim resistor and is accurate to about 1°C.

The current limiters circuits for the HDI power connections were designed to trip at 0.7 A in order to protect the wire bonds. Response time is a few ms. The time constant for integrated signals (output of the current monitor) is of order 100 ms to avoid trips on glitches. Each HDI power line is monitored, in total 24 current limiter circuits per board.

The high voltage (HV) control for the detector bias is provided by the HDI enable circuit and photovoltaic relays (no moving parts) on the interface board. There are two HV lines provided for each HDI to allow operation of double-sided sensors in split mode. HV is supplied via a 34-conductor twist-and-flat strip cable to a connector on the backplane. For single-sided detectors, the primary bias voltage is grounded and the secondary bias has a positive voltage. For double-sided detectors the primary bias is at  $+\mathrm{HV/2}$  or less and the secondary bias at  $-\mathrm{HV/2}$  or greater. This allows for asymmetric breakdown characteristics. The ground reference is the HDI ground. Bias current from groups of four HDIs can be measured via the MIL-STD-1553 interface at any time.

#### 4.7 Sequencer Controller

The sequencer controller (SEQC) is a 9U×340 mm Eurostyle module residing in each sequencer crate, used to give coarse timing commands to the SVXIIe sequencers which control acquisition and readout of the SVXIIe chips. It is designed to be plugged into slot 1 of the custom sequencer backplanes.

The controller receives beam crossing timing and triggering information via

a single coaxial cable called the Serial Command Link which originates at the Trigger Framework<sup>2</sup>. Information from this link is interpreted and transformed into general SVXIIe data acquisition commands that go to each sequencer via the backplane. These commands are encoded onto a serial link called the NRZ (non-return-to-zero) link which is a 7-bit repetitive code sent on dedicated backplane lines to each sequencer slot. These lines are used in conjunction with a dedicated differential 53 MHz clock sent to each sequencer slot. The seven bits are the framing bit, the crossing bit, four bits for an encoded data command, and the parity bit. The seven bit structure was chosen to remain synchronous with the Tevatron beam structure. A new code packet is sent every 132 ns. The framing bit is always set high and is monitored by a state machine to ensure that the link is synchronized. The crossing bit is only set if there is beam for that particular 132 ns period. The sixteen possible encoded data commands include commands such as Acquire, Preamp Reset, Level 1 Accept, Digitize, Readout, and Readout Abort.

The NRZ link has an adjustable delay system to synchronize the crossing command with actual beam crossings so that SVXIIe charge acquisition happens at the optimal time with respect to beam. There are three delays, 132 ns, 18.8 ns, and 2 ns steps, writable from a MIL-STD-1553 serial communication link. This MIL-STD-1553 link is also used to set various diagnostic modes.

To prevent missed triggers, the SEQC sends a Busy signal back to the Trigger Framework based on a logical OR of busy signals from the sequencers. This is necessary because the SVXIIe chips may operate in sparsification mode, reading out only the channels over threshold, and readout may end at various times after a trigger. Since there is only one buffer on the SVXIIe, a new trigger may be accepted only after readout has finished.

A Diagnostic mode is provided to exercise the data acquisition system if the Trigger Framework signals are not operational. This mode is exercised via MIL-STD-1553 link.

#### 4.8 SVXIIe Sequencer

The basic task of the SVXIIe sequencers is to coordinate data acquisition in the SVXIIe chips and serialize the resulting data onto high speed fibers to be sent to data storage.

The sequencers are 9U×340 mm circuit boards that reside in slots 2 through

The Trigger Framework gathers digital information from each of the specific Level 1 trigger devices and chooses whether a particular event is to be accepted for further examination.

21 in six Eurocard crates on the detector platform. Geographic addressing is designed into the backplane for each slot for MIL-STD-1553 Remote Terminal identification. Each sequencer is connected to an interface board via four 50-conductor 3M pleated-foil cables, a VRB via four optical fibers for data readout, the SEQC via the backplane, and the control system via the MIL-STD-1553 link which is also plugged into the backplane.

In initialize mode, the sequencers interpret data from the MIL-STD-1553 data bus and then clock the appropriate download data pattern into the chips. This pattern is readable from the chips only by shifting new data into the chips so a simultaneous download of all chips on an HDI must occur. In acquire mode, the sequencers advance the pipeline clock with each beam crossing, and the SVXIIe chips' preamplifiers are reset during beam gaps. When a trigger occurs, a specific complex manipulation of the control signals occurs which extracts charge out of the correct pipeline cell, and then the sequencer sends a 53 MHz clock which the chip uses to digitize this charge for each channel. In readout mode, clocks are sent to the SVXIIe chip at 26.5 MHz, and the chip then sends alternately channel ID and data back to the sequencer. The sequencer serializes this data into a 1.062 Gb/s data stream, adds header and trailer information, and sends it via optical fiber to the VRBs in the counting house.

Diagnostic features are interfaced to the MIL-STD-1553 bus and include a snapshot register to read the current state of important SVXIIe control lines and a built-in logic analyzer that records the same control lines for about 75  $\mu$ s after a selectable trigger. A pattern of 64 words may be written via the MIL-STD-1553 link and sent to the VRBs for testing the gigabit links. The Finisar laser [12] drivers' diagnostic links may be read via MIL-STD-1553, monitoring power output, temperature, and other parameters. Other MIL-STD-1553 link registers include SVXIIe chip power on/off control, module serial number, and a remote programming register.

An optional Readout Abort feature is used to guard against system hangups from non-responding chips. Normally the sequencers use the Priority\_Out handshake signal from the last chip in a chain to determine when readout is finished. If this handshake ever fails, a  $45\,\mu\mathrm{s}$  timeout in the SEQC propagates to the sequencers and puts the system back in acquire mode, and Busy is released.

### 4.9 VME Readout Buffer

The VME Readout Buffer (VRB) is a 9U×400 mm multiport memory that buffers the data for transfer to the higher level data acquisition system. It

contains ten independent input ports and a common VME output port. For SMT operation, eight channels on each board are used.

The VRB acts as a buffer as data wait for the conclusion from the second decision level (Level 2) of the hardware trigger system [4]. Buffer management is provided by an external System Controller (VRBC) through a dedicated control port. A controller serves up to 12 VRB modules in one VME crate.

The VRB receives data via serial optical connections from the sequencers via the VTM which converts the optical signal to an electrical signal. Input data is accepted at an aggregate rate of approximately 500 MBytes/s on eight (bytewide) channels. The output rate is limited by VME transfer speeds and by the number of VRB modules sharing the VME bus. For SVXIIe chip applications, the VRB inputs data at the accept rate of a few kHz from the first decision level (Level 1) of the hardware trigger, and outputs data at the Level 2 accept rate of less than 1 kHz.

The VRB Control Logic performs three basic functions: receive and process messages from the system controller, return status signals to the system controller, and manage the general flow of data to and from the VRB buffers. The Control Logic will respond to a message by asserting a status signal, typically within 200 ns.

Upon a Level 1 trigger accept, the VRBC supplies the VRB with a buffer number to store the input data. When the VRB Control Logic receives a message specifying the next input buffer, it looks up the buffer starting address in the shared memory, and broadcasts this information to the Receive Logic for all channels. The input data is pushed to the VRB from the sequencer. The event data from an SVXIIe chip is logically organized by words (2 bytes). The first bytes of each data stream contain a header inserted by the sequencer to identify the data source. This is followed by a block of data from each SVXIIe chip containing the chip ID, status, and up to 128 pairs of channel number and data. The VRB input FIFO (First In First Out memory configuration) will accept data until it recognizes an End Of Record word. When all event data is received, the VRB Control Logic will read the individual byte counts from each Receive Logic block and generate a global byte count for the event. The global byte count is available to a VME Scan Processor so that it can perform a single block read operation to obtain all data for the event. When all the channels transmitting data to a VRB are done, the VRB will inform the VRBC. This is accomplished by releasing a busy signal on a dedicated line of control bus. The busy line is an open collector signal that can be driven low by any of the VRBs in the crate. The transfer of the data from the SVXIIe to the Level 2 buffer is finished when all VRBs have released signal on this line.

Following a Level 2 Accept, the VRBC supplies the VRB with a buffer number

for data output. Events that are accepted by the Level 2 trigger are copied to the VME output data FIFO. For events rejected by the Level 2 trigger, the VRBC re-uses the buffer number, causing the previous event data to be overwritten.

#### 5 Silicon Sensors

The SMT detector uses a combination of single-sided, double-sided, and double-sided double-metal silicon sensors.

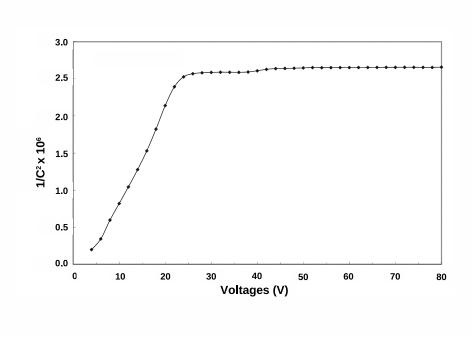

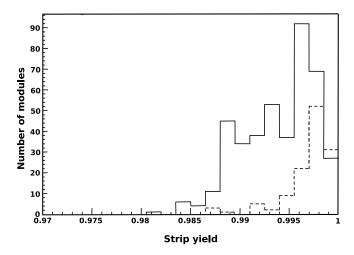

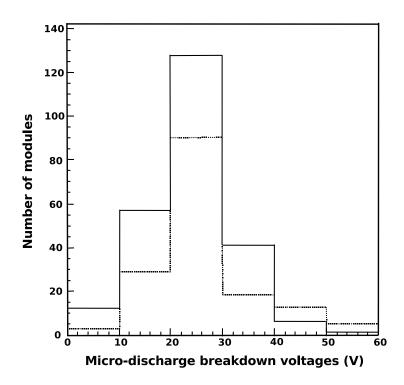

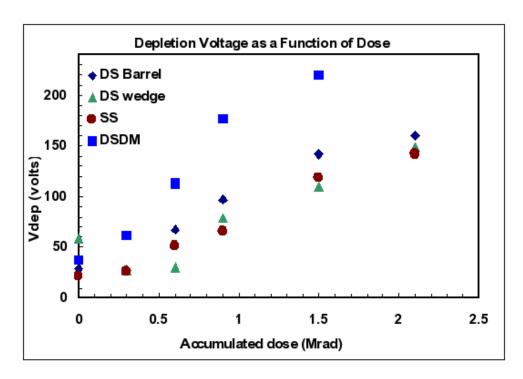

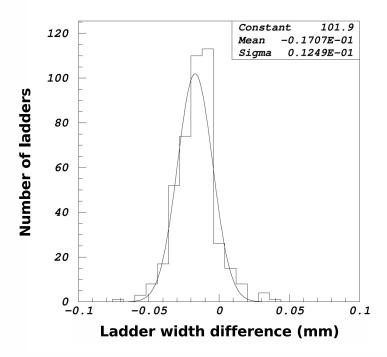

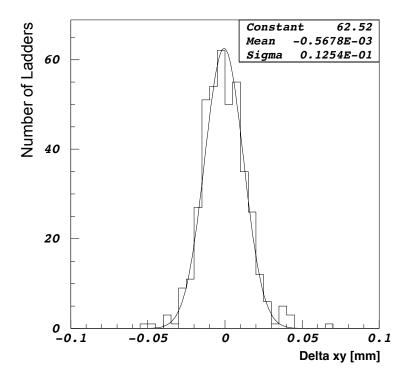

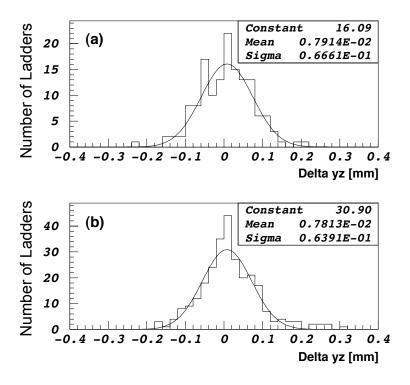

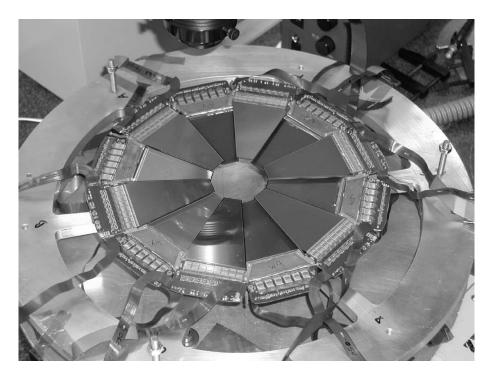

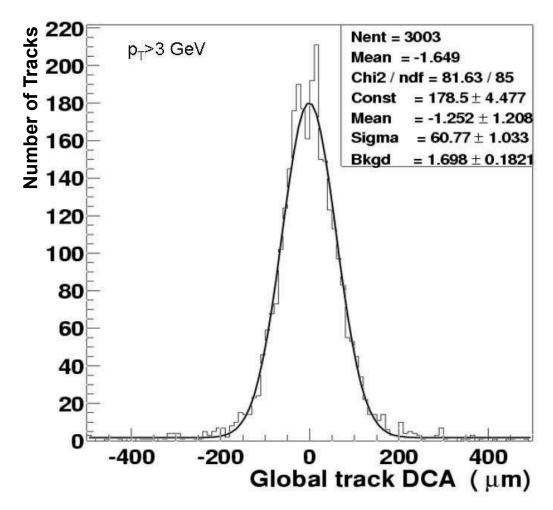

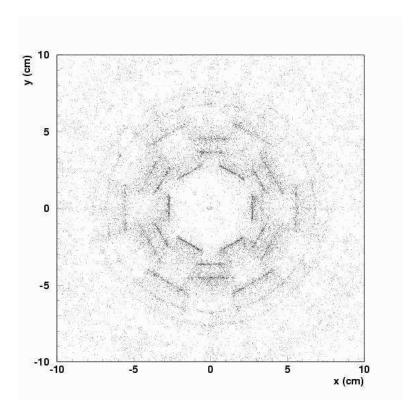

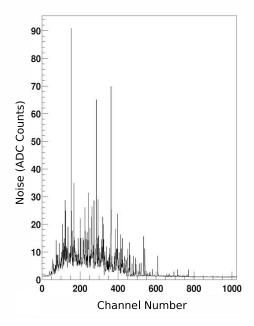

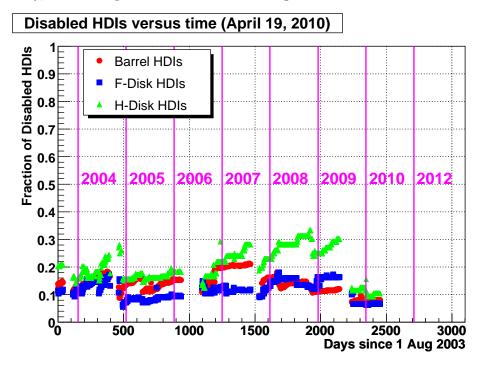

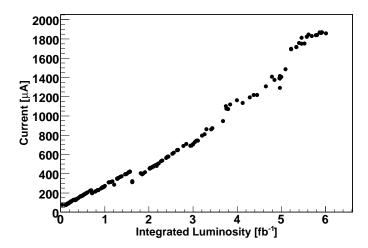

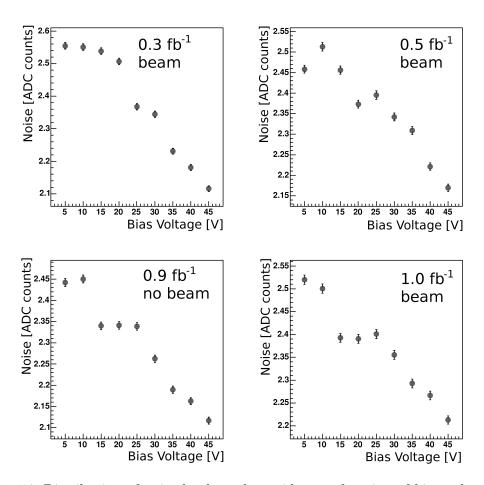

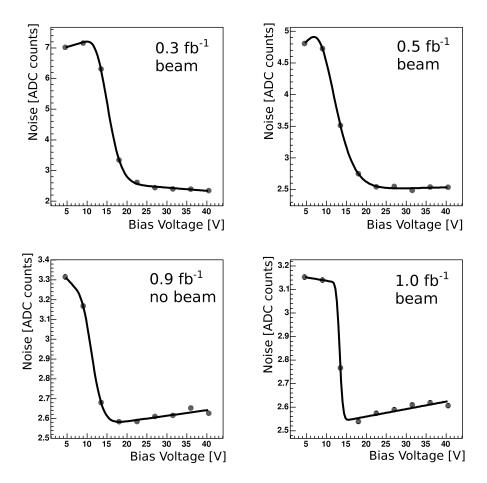

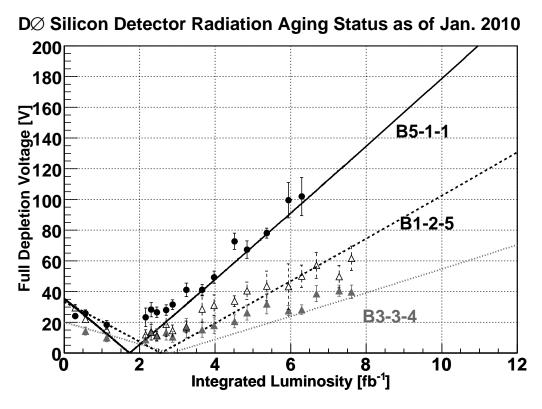

Single-sided and double-sided devices were produced from high resistivity 4" silicon wafers with crystal orientation < 111 > and < 100 >. The double-sided double-metal detectors were manufactured using < 100 > 6" wafers. Isolation on the n-side of all double-sided devices is provided by p-stop implants. AC coupling aluminization was specified to be  $2\,\mu{\rm m}$  inside the strip to limit edge fields which might cause micro-discharge breakdown. All traces are biased using poly-silicon resistors.