# Accurate GPU Memory Prediction for Deep Learning Jobs through Dynamic Analysis

Jiabo Shi

Yehia Elkhatib

Abstract—The benefits of Deep Learning (DL) impose significant pressure on GPU resources, particularly within GPU cluster, where Out-Of-Memory (OOM) errors present a primary impediment to model training and efficient resource utilization. Conventional OOM estimation techniques, relying either on static graph analysis or direct GPU memory profiling, suffer from inherent limitations: static analysis often fails to capture model dynamics, whereas GPU-based profiling intensifies contention for scarce GPU resources. To overcome these constraints, VeritasEst emerges. It is an innovative, entirely CPU-based analysis tool capable of accurately predicting the peak GPU memory required for DL training tasks without accessing the target GPU. This "offline" prediction capability is VeritasEst's core advantage, allowing accurate memory footprint information to be obtained before task scheduling, thereby effectively preventing OOM and optimizing GPU allocation. Its performance was validated through thousands of experimental runs across convolutional neural network (CNN) models: compared to baseline GPU memory estimators, VeritasEst significantly reduces the relative error by 84%, lowers the estimation failure probability by 73%. VeritasEst represents a key step towards efficient and predictable DL training in resource-constrained environments.

*Index Terms*—Deep Learning, Memory Management, Program Analysis,

# I. INTRODUCTION

The field of Deep Learning (DL) is witnessing rapid growth, with Deep Neural Network (DNN) models finding broad application across diverse sectors, including autonomous driving [1], speech recognition [2], and image generation [3], where they have demonstrated performance levels comparable to those of humans in various domains [4]. Consequently, technology companies are increasing investments in high-performance computing infrastructure, particularly Graphics Processing Units (GPUs) to accelerate model training. This surge in demand has created notable GPU scarcity; even leading AI companies, such as OpenAI, are facing challenges in securing adequate GPU resources [5].

Furthermore, companies use computing clusters to optimize the utilization of GPUs. However, contrary to expectations, debugging tasks that should ideally be handled locally are also being transferred to clusters due to the absence of local GPU support. Avoiding potential runtime out-of-memory (OOM) issues is a key focus of these debugging efforts. Previous studies [6], [7] provide evidence that GPU clusters in Microsoft and Meta are experiencing OOM problems, with 9% of DL training tasks failing due to OOM. This problem further exacerbates the scarcity of GPUs. Using expensive GPUs for OOM error detection is highly inefficient and wasteful.

Recently, strategies for dealing with OOM problems in clusters fall primarily into two categories. The first strategy, which includes approaches like AntMan [8], employs offloading techniques [9], [10] to move tensors that exceed the maximum memory capacity of the GPU to the host RAM. However,

this technique has a limitation: permanent partial memory on RAM affects training performance when the task's memory consumption exceeds the device's maximum capacity, and it does not fully address the OOM problem. The second strategy, which we are focusing on, aims to address the OOM problem by predicting the peak GPU memory usage in advance, *e.g.*, [11]–[15], to determine whether the requested GPU can meet the training requirements, essentially resolving the OOM issue before it occurs, and helping the clusters conserve GPU resources.

Solutions for estimating peak GPU memory face three main challenges. The first key challenge is understanding when memory is being allocated and freed during a training task. Previous works, like Gao et al. [11] and Liu et al. [13], focused on static analysis of the computational graph but faced limitations due to the lack of dynamic and detailed memory tracking, especially for operations like gradient zeroing and altering the optimizer.

Second, a frequent misunderstanding in DL model training is the assumption that the tensor memory footprint directly reflects GPU memory usage. In PyTorch, the default memory allocator for CUDA, CUDACachingAllocator [16], is used for memory management. This allocator can cause differences between the sizes of the tensors and the actual memory allocated to the GPU. Consequently, to accurately assess peak GPU memory usage, it is necessary to consider the allocator's behavior rather than considering only the tensor sizes.

The third challenge is whether GPU memory estimation can be performed without relying on expensive GPU hardware, which makes it feasible to perform estimation on any server without access to specialized hardware.

In this paper, we propose *VeritasEst*, a GPU memory estimator that can utilize CPU-based profiling data to infer the peak memory required for training a model on a GPU. This estimator is based on three principal observations: (i) the execution sequence of high-level code, such as Python, remains consistent across CPU and GPU, differing merely in the low-level kernel implementation, such as ATen [17]; (ii) the optimized operators in recent versions of PyTorch demonstrate comparable memory usage on both CPU and GPU; and (iii) consistent memory allocation and deallocation sequences yield predictable outcomes across CPU and GPU when managed by the same allocator.

We implemented VeritasEst and evaluated its performance extensively in a total of thousands of experiment runs. We evaluated VeritasEst with convolutional neural network (CNN) models, five optimizers, varying batch sizes, resulting in a 5.46% relative error, and a 13.59% probability of estimation failure. Compared with three state-of-the-art GPU memory estimators [11], [12], [15], VeritasEst decreases the relative error by 84.32%, the probability of estimation failure by 73.44%.

This study makes the following contributions.

- We propose a novel solution that can not only accurately dynamically estimate GPU peak memory consumption for DL model training tasks, but also provide additional memory change trace during training, requiring only a CPU (§III). Additionally, VeritasEst's is open source.

- 2) We offer a GPU memory sequence of model training tasks for all memory simulators by performing a thorough analysis of CPU-based profiling data generated by the PyTorch Profiler (§III-C).

#### II. BACKGROUND

## A. Out-of-Memory Issues

Previous studies [6], [7] have shown that GPU clusters at both Microsoft and Meta are experiencing OOM issues, which cause approximately 9% of deep learning training tasks to fail due to OOM. Additionally, an independent empirical study that examined 2,716 Stack Overflow posts identified OOM as one of six major deep learning error-related issues [18]. OOM challenges are common in the field of system resource management, particularly concerning DL training, due to the limited GPU memory available compared to the high memory demands of model training. Several factors, including batch size, choice of the optimizer, and even small code alterations, can affect memory usage during training. The studies [11], [13], [14] proposed static analysis methods to estimate the maximum GPU memory usage by utilizing a computation graph or static data extracted from a model. However, developing and training models is not static but rather dynamic, with the aim of optimizing the model's performance by tuning the code. A dynamic GPU memory estimator is a handy tool for preventing OOM or efficient resource management.

#### B. Memory Consumption

Typically, there are two main types of memory consumption in a PyTorch training job: the memory consumed by Tensors and the memory consumed by a memory allocator, termed Segments.

1) Tensors: refer to memory blocks used to store tensors during model training or inference in PyTorch, including model parameters, activations, gradients, etc. During forward and backward propagations, the tensors consume memory and their memory requirements are influenced by factors such as model architecture, batch size, data precision, etc. Notably, the tensor memory blocks are not directly allocated from a GPU. Instead, tensor memory blocks are allocated from segments that are blocks of GPU memory previously allocated and cached by the allocator.

2) Segments: are memory blocks that are requested from GPU and managed by the CUDACachingAllocator. Segments are relatively larger blocks, and all memory requests from DL model training tasks actually request a fitted memory block from it. The allocator retains the deallocated memory blocks used by tensors within segments for reuse instead of releasing it back to the GPU. When segment memory is insufficient, a new segment is requested from the GPU. Thus, GPU memory consumption is denoted as the total memory size of segments requested by the allocator. All previous studies [12], [14], [15] overlook the importance of a memory allocator to estimate GPU memory consumption during training.

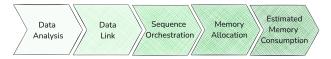

Fig. 1: Workflow of VeritasEst Memory Estimator.

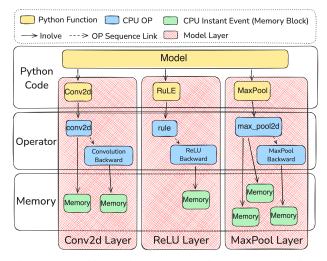

Fig. 2: A call hierarchical structure diagram showing links between memory blocks, operators, and layers.

## C. Sequence of Memory Activities

The sequence of memory allocation and deallocation activities is a critical factor in determining memory consumption. Different sequences may induce varying levels of fragmentation, thereby directly influencing the overall memory usage of deep learning models. As mentioned in Section II-A, the studies [11], [13] consistently utilize static memory sequences, whereas the research studies [12], [14], [15] did not take into account of memory sequences in their memory estimation processes.

#### III. DESIGN

As GPU characteristics are expensive and scarce, we proposed VeritasEst, a CPU-based memory estimator that uses a CPU that is anywhere ready to profile training tasks, enabling prediction of GPU memory requirements and eliminating the need for GPUs during neither development nor execution. Its major objective is to accurately predict peak GPU memory usage, referred to as the minimum runnable GPU memory, during DL model training on GPUs, with the goal of preventing OOM issues and optimizing GPU memory usage. Moreover, the current version is specific for PyTorch [19], which is a well-known DL framework that is widely used in both research and industry.

Due to their distinct hardware architectures, memory allocation functions differ significantly when a DL model is trained on CPUs versus GPUs. To address this challenge, we have developed techniques to extrapolate from CPU profiling to accurately estimate GPU requirements based on a set of key principles outlined below:

1) **Sequence:** PyTorch must ensure compatibility with various processors also known as *kernels*, such as CPU, GPU, and XPU. To achieve this, it employs a dispatch mechanism that separates the implementation in high-level languages

## Algorithm 1: cpu instant event Grouping

| 0                            |                                 |                     | 10                 |  |

|------------------------------|---------------------------------|---------------------|--------------------|--|

| Data: cpu_instant_event Data |                                 |                     |                    |  |

| <b>Result:</b>               | Set of Time-based               | l Memory            | Block              |  |

| $addr_m$                     | $ap \leftarrow \{\};$           |                     |                    |  |

| $node_m$                     | $ap \leftarrow \{\};$           |                     |                    |  |

| $data \leftarrow g$          | get_sorted_cpu_ev               | ent_data(           | );                 |  |

| foreach                      | $trace \in data \ \mathbf{do}$  |                     |                    |  |

| adda                         | $r \leftarrow get_addr(trac$    | ee);                |                    |  |

| if ad                        | ddr∉addr_map t                  | then                |                    |  |

|                              | $block \leftarrow create_m$     | emory_bl            | ock(trace);        |  |

|                              | $addr_map[addr]$                | $\leftarrow block;$ |                    |  |

| else                         |                                 |                     |                    |  |

|                              | $addr_map[addr]$                | .mark_as            | _free(trace);      |  |

|                              | $block \leftarrow addr_math{a}$ |                     |                    |  |

|                              | $node\_map[block]$              | .alloc_tim          | ne].append(block); |  |

|                              |                                 | _                   |                    |  |

|                              | $remaining \in add$             | - 1                 |                    |  |

|                              | $c\_time \leftarrow remain$     |                     |                    |  |

| $\lfloor nod$                | $e\_map[alloc\_tim]$            | e].append           | l(remaining);      |  |

|                              |                                 | (                   | ).                 |  |

**return** sort\_by\_alloc\_time(node\_map);

like Python from the actual execution code [17] within the kernel, thus maintaining their independence. Therefore, the function call sequence during an identical DL training task remains consistent between CPU and GPU.

- 2) Memory: All fundamental C++ operators in PyTorch are optimized to manage memory efficiently regardless of the target kernel.<sup>1</sup> This means that the memory usage for most operators are expected to be comparable, if not identical, for training on either the CPU or GPU.

- 3) Allocation: A memory allocator handles all real memory allocation activities. Whenever any operator requires to acquire or free a memory block, the associated function in the allocator is invoked. This indicates that memory allocation can be fully predictable when a properly ordered memory input is provided.

Building on the aforementioned principles, VeritasEst follows the workflow shown in Fig. 1. Initially, the data analysis phase (§III-A) ensures that all data are prepared for subsequent use. Next, the data link phase (§III-B) identifies all memory activities necessary for each layer of the model. The sequence orchestration phase (§III-C) then corrects the timing of the memory activities to align them more closely with the GPU memory activities. In the final step, the memory allocation phase ensures that all memory blocks are adjusted to the correct rounded-up sizes and allocated to the appropriate segments. Moreover, it also guarantees that all segments are computed to the designed size by an algorithm before requesting the size from the GPU.

The allocator is highly adaptable and can be replaced by any allocator defined by the user. In this study, we use the Python implementation of the CUDACachingAllocator simulator with the Best Fit with Coalescing (BFC) algorithm [20] as the default memory allocation method.

## A. Data Analysis

Our primary data source is the log of events created by the PyTorch Profiler [21]. This phase ensures that all data are

<sup>1</sup>Such as aten::mkldnn\_convolution for CPU kernels and aten::cudnn convolution for CUDA kernels.

structured in specific formats that are conducive to sequential analysis. From the 24 types of events provided in JSON format, we rely on four event types only, as follows.

1) python\_function: provides linkage details, such as parent and current Python function IDs, helping to construct a function call graph to identify a hierarchy within the training task. In particular, the traces of these Python functions clearly indicate the PyTorch layers that are invoked, such as VGG16, Conv2d, or ReLU. As python\_function events contain clear linking details, they can readily be arranged into a tree structure, preserving only the information related to the PyTorch layer in the data structure.

2) cpu\_op: provides extensive metadata regarding operators, encompassing input size, input type, and sequence number. The sequence number is the pivotal attribute in this additional information because it is used to link operators that are created during forward and backward propagation of the same layer. Unlike python\_function, cpu\_op does not furnish direct linkage metadata that would assist in constructing a stack tree. Therefore, we employ the fundamental concept of the interval tree algorithm to organize time-based CPU operators, with only the root nodes of the operators used after it.

3) user\_annotation: is designed to spotlight specific code in profiling data. In PyTorch, the official source code marks key codes such as profiler.step, optimizer.zero\_grad, and optimizer.step. The profiler.step marks the start of a new profiling cycle, facilitating analysis by breaking down profile data into multiple iterations. The optimizer.step initiates a parameter update, marking the beginning of updates after all propagation. optimizer.zero\_grad helps to locate a time point when the gradients from the current or previous iteration are zeroed.

4) cpu instant event: presents memory allocation and deallocation metadata, including memory address, size, total allocated, and total reserved. We refer to this as "memory activity". It is crucial to record the lifecycle of each memory block carefully from profiling data in order to provide accurate memory sequence data to the allocator. The key task is to establish correct associations between the allocation and the deallocation memory activities. Each single memory address could be reused multiple times throughout the training process; therefore, an association based on addresses alone is not feasible. Thus, we sequentially analyze all memory activities and apply Algorithm 1 to bind each memory activity accurately. This process generates a set of new memory blocks, which details allocation time, deallocation time, size in bytes, etc. Each new block connects two memory activities, one for allocation and one for deallocation. A block remains permanent if it has only one activity.

#### B. Data Link

The linking phase determines all required memory blocks for each layer within the model by constructing a call hierarchy. As shown in Fig. 2, this procedure begins with Python functions (yellow blocks) accessing the memory blocks (green blocks) through intermediary operators (blue blocks). Notably, memory blocks are associated only when they are generated at the execution time of each operator of each model layer. Due to the lack of a straightforward link between any two types of metadata, we rely exclusively on timestamps to correlate Python functions, operators, and memory blocks. To establish a connection between python\_function and cpu\_op, the start and end times of each layer, excluding wrapper layers<sup>2</sup> are utilized to determine all operators generated in that time period. Some operators in the search results may have a sequence number attribute, indicating that they are associated with one or more operators involved in gradient computation during the backward propagation phase. Because the connections between the forward and backward operators have already been established during data analysis, we can easily include the corresponding backward operators within the layer and store them as part of the backward operators. If multiple sequence numbers appear in the search output, all operators linked to those sequence numbers are included.

The link between cpu op and the memory blocks generated during the data analysis phase is established in the same way as described in the preceding paragraph. Furthermore, by analyzing the memory operations of each model's layer on both the CPU and GPU, we determine that the memory retained is identical for each layer in the CPU and GPU. However, the temporary memory allocations within the CPU training task for the same layer exceed those in the GPU. Due to optimization issues in layer function implementations on the CPU, the layer function may create an additional variable to store data passed by its caller and delete the original one. This creates an extra memory block during this value-assigning process, causing memory fluctuations. To address this, we determine if a memory block's deallocating time falls within the execution timeframe of an operator. If so, we can filter those blocks that are allocated and freed within the operator execution time range. We can, thus, focus on the memory blocks that remain after an operator finishes.

# C. Sequence Orchestration

The objective of the orchestration phase is to construct a memory sequence that is closer to that on the GPU by aligning and rearranging memory allocation and deallocation timings.

1) Model: refers to memory blocks that are loaded during a model transfer stage, which is triggered by model.to(kernel). However, this part of memory information is not contained in CPU-based profiling data. Therefore, we assume that during the model transfer phase, the overall memory consumption is equivalent to the memory used by the gradients. This assumption has been validated through experiments that analyze memory data obtained from the PyTorch Snapshot Profiler [23], a tool that can disclose memory activities directly from the PyTorch CUDACachingAllocator. The results show that the error ranges from 0% to a maximum of 1.2%, supporting the use of gradient sizes to allocate all required memory blocks. Since the memory allocated for the model is persistent, deallocation times are unnecessary. Additionally, to resolve sequence mismatches, as backward propagation generates memory in reverse order of model loading, the allocation order is corrected accordingly.

2) Batch Data: refers to a subset of the dataset processed collectively in a single iteration. Consequently, memory blocks associated with batch data exist only for the duration of an iteration and are consistently relocated before the next one is loaded. The VeritasEst obtains batch data memory directly from the PyTorch

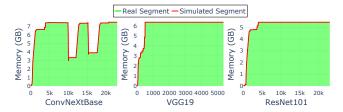

Fig. 3: A comparison of memory allocation between the snapshot real and allocator simulation segments.

dataloader [24]. The time required for memory allocation and deallocation is actually the same as the duration of the iteration.

3) Gradients: refer to memory blocks allocated during backward propagation, utilized to minimize loss value during an optimization phase. These memory blocks are treated as temporary memory allocations when training on a CPU, implying that the memory blocks are released shortly after allocation. However, in GPU-based training, the release of this memory is controlled by the optimizer.zero\_grad function. To address this issue, the free time of all memory blocks for each layer is adjusted to the call time of the next optimizer.zero\_grad in iterations. In the absence of an optimizer.zero\_grad call in the following iteration, the memory blocks of all gradients remain allocated until optimizer.zero\_grad is eventually called.

4) Optimizer: refers to a collection of memory blocks produced during the execution span of an optimizer.step. Since optimizers such as Adam [25] maintain extra memory blocks that have the same dimensions as the parameters of the model, VeritasEst excludes all memory blocks whose sizes do not match any of the model parameters' memory sizes. All memory blocks generated at this stage are labeled as permanent memory, lasting until the epoch is complete.

5) Repetitive Iterations: VeritasEst is capable of generating memory sequences for multiple iterations due to the repetitive iteration characteristics of DL [26]–[29]. When the Stochastic Gradient Descent (SGD) [30] optimizer is used, a memory sequence from a single iteration can accurately estimate the peak memory usage for the training task. However, for other optimizers like Adam, the first iteration often generates additional permanent memory blocks during the optimization phase, making it less accurate to predict peak memory usage based on the memory sequence of a single iteration. To accommodate a wide range of scenarios, xMen, by default, generates memory sequences for two iterations as input for the allocator.

### IV. EVALUATION

This section evaluates the effectiveness of VeritasEst against three state-of-the-art baselines that employ distinct approaches to address the challenge of accurately estimating GPU memory usage. The evaluation was conducted through two separate experiments using the execution methodology described in Section IV-C. The first experiment (§IV-D) used the Analysis of Variance (ANOVA) method [37] to analyze the relative error and examine the relationship between the probability of failed estimations, runtime, and median relative error.

<sup>&</sup>lt;sup>2</sup>Such as a bottleneck layer in ResNet [22].

TABLE I: The models and optimizers used in the experiments.

| Model                   | Release Year | Optimizers |

|-------------------------|--------------|------------|

| VGG11 [31]              | 2014         |            |

| VGG16 [31]              | "            |            |

| VGG19 [31]              | "            |            |

| ResNet50 [22]           | 2016         |            |

| ResNet101 [22]          | "            |            |

| ResNet152 [22]          | "            |            |

| MobileNetV2 [32]        | 2018         | Adam       |

| MobileNetV3(Small) [33] | 2019         | SGD        |

| MobileNetV3(Large) [33] | "            | Adagrad    |

| MnasNet [34]            | "            | RMSprop    |

| RegNetX(400MF) [35]     | 2020         | AdamW      |

| RegNetX(32GF) [35]      | "            |            |

| RegNetY(400MF) [35]     | "            |            |

| RegNetY(32GF) [35]      | "            |            |

| ConvNeXt(Tiny) [36]     | 2022         |            |

| ConvNeXt(Base) [36]     | "            |            |

## A. Baselines

In establishing a robust foundation for comparative analysis, we carefully selected baselines from the literature encompassing diverse methodologies: static analysis, DL-based prediction, and direct GPU utilization. As a representative static analysis approach, we employed DNNmem [11], which combines a memory allocator with static analysis. While both SchedTune [12] and TBEM [13] use data-driven, pre-trained DL models for memory prediction, we selected SchedTune due to the availability of its source code, facilitating reproducibility. Finally, we included LLMem [15] as a recent approach that utilizes direct GPU interaction. We deemed Horus [14] less relevant to our comparative study owing to its primary focus being on FLOPS utilization and it only having a relatively simplistic memory estimation strategy. We refer the reader to Section V for a detailed inspection of these and other related works.

For consistency, all evaluation plots use the following color scheme: blue for VeritasEst, red for DNNMem, green for Sched-Tune, and purple for LLMem. Unless otherwise stated, 'memory size' refers to the segment memory as described in Section II-B2.

#### B. Experimental Setup

The experiments were conducted on a server equipped with a 24-core Intel i9 CPU with 128GB RAM, and two GPUs: a GeForce 4070Ti with 12GB of memory and a GeForce 4060 with 8GB of memory. To ensure consistency and reliability for each experiment run, we utilized container technology with an official PyTorch image (pytorch:2.3.1-cuda12.1-cudnn8-devel) as the base to build an image of an experimental environment with all the necessary Python dependencies. During each run, a new container was initiated to ensure isolation and independence. In addition, each GPU was dedicated to a single run, ensuring that only one process fully occupied a GPU at any time. Additionally, we configured the CUBLAS workspace size and CUFFT plan size to zero within PyTorch to maintain consistent experimental conditions and avoid unintentional caching effects.

Table I lists the models and optimizers used in our experiments, with a consistent input shape of [channels: 3, width: 86, height: 86]. The 4070Ti GPU was connected to a monitor that used 127MB of GPU memory, while a terminal for running the evaluation script required an extra 112MB, plus approximately

TABLE II: Notations used in the evaluation experiments.

| Notation                        | Definition                                                                                                                                                                                                                             |  |  |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| j                               | One test configuration, including model, optimizer, etc.                                                                                                                                                                               |  |  |

| i                               | Verification Round: 1 <sup>st</sup> or 2 <sup>nd</sup>                                                                                                                                                                                 |  |  |

| d                               | The index of the target GPU device, $d \in \{0,1\}$                                                                                                                                                                                    |  |  |

| e                               | The estimator                                                                                                                                                                                                                          |  |  |

| N                               | The number of performed runs                                                                                                                                                                                                           |  |  |

| $M_d^{\mathrm{init}}$           | The amount of memory used on device $d$ for the duration of the experiment                                                                                                                                                             |  |  |

| $M_d^{\max}$                    | The memory capacity of device d                                                                                                                                                                                                        |  |  |

| $M_{jid}^{\mathrm{peak}}$       | The peak memory usage as recorded by NVML during training with configuration $j$ on device $d$ at the $i$ <sup>th</sup> validation                                                                                                     |  |  |

| $\hat{M}_{jde}^{\mathrm{peak}}$ | The peak memory usage as predicted by estimator $e$ using configuration $j$ and memory capacity of device $d$                                                                                                                          |  |  |

| $\hat{OOM}_{jde}$               | Boolean prediction of OOM occurrence by estimator $e$ using configuration $j$ on device $d$                                                                                                                                            |  |  |

| $OOM_{jid}$                     | Boolean indicating actual OOM occurrence during training with configuration $j$ on device $d$ at $i$ <sup>th</sup> validation                                                                                                          |  |  |

| $C_{jide}$                      | Boolean indicating whether the prediction $O\hat{O}M_{jde}$ matches<br>the actual $OOM_{jdi}$ at the 1 <sup>st</sup> validation. In the 2 <sup>nd</sup> validation,<br>$C_{jde1}$ is utilized to further assess its estimation status. |  |  |

| error <sub>jide</sub>           | The error of $M_{jid}^{\text{peak}}$ relative to $\hat{M}_{jde}^{\text{peak}}$                                                                                                                                                         |  |  |

| error <sub>jide</sub>           | The median of a set of error <sub>jide</sub>                                                                                                                                                                                           |  |  |

15MB of initial memory per GPU. Thus, each GPU had a fixed initial amount of memory in all the experiments, denoted as  $M_d^{\text{init}}$ .

## C. Methodology

The notations used here are summarized in Table II.

Each run indicates a test configuration, j, performed once for the four estimators, denoted as e. The configuration comprises the model, optimizer, batch size, and when zero\_grad is called during training, at two positions: the first to call zero\_grad immediately before backward propagation and another at the start of each iteration. Furthermore, each run was divided into two validation steps, denoted as i, to evaluate the performance of each estimator separately: **Initial validation:** determines whether submitting tasks leads to an OOM error when training on a GPU with the maximum memory of the device; and

**Subsequent validation:** focuses on the precision of the estimated peak memory and determines whether training causes OOM when using the estimated peak memory predicted by the estimator as the maximum runnable GPU memory.

1) Initial validation: aims to verify whether a predicted OOM result aligns with the actual OOM scenario and to compute the relative error, which follows these steps: (i) Estimated peak memory: predicts the peak GPU memory  $\hat{M}_{jde}^{\text{peak}}$  during training based on a configuration j and the maximum memory capacity of the device d. (ii) Estimated OOM: uses (1) to determine the estimated  $OOM_{jde}$ . (iii) Actual OOM: run task with configuration j on device d to determine<sup>3</sup> whether training occurs  $OOM_{jd1}$ , expressed as (2). Meanwhile, NVIDIA NVML [38] measures the actual peak memory  $M_{jd1}^{\text{peak}}$ . (iv) Estimation Correctness: uses (3) to verify the correctness  $C_{jde1}$ . (v) Relative error: uses (5) to calculate error<sub>jde1</sub>.

$$\hat{\text{OOM}}_{jde} = \begin{cases} 1, & \hat{M}_{jde}^{\text{peak}} > M_d^{\text{max}} \\ 0, & \hat{M}_{jde}^{\text{peak}} \le M_d^{\text{max}} \end{cases}$$

(1)

$^{3}$ We limit each run to ten iterations, as peak memory tends to stabilize after a few iterations (*cf.* Section III-C5).

$$OOM_{jid} = \begin{cases} 1, & True \\ 0, & False \end{cases}$$

(2)

$$C_{jde1} = \begin{cases} 1, & O\hat{O}M_{jde} = OOM_{jd1}, \\ 0, & O\hat{O}M_{jde} \neq OOM_{jd1}. \end{cases}$$

(3)

$$C_{jde2} = \begin{cases} 1, & C_{jde1} = 1 \land \text{OOM}_{jd2} = 0\\ 1, & C_{jde1} = 1 \land \text{OOM}_{jd1} = 1\\ 0, & otherwise \end{cases}$$

(4)

$$\operatorname{error}_{jide} = \frac{\|\hat{M}_{jde}^{\text{peak}} - M_{jid}^{\text{peak}}\|}{M_{iid}^{\text{peak}}}$$

(5)

2) Subsequent validation: aims to determine whether training task with configuration j on target device d encounters an OOM issue when using the estimated peak memory predicted by the estimator as the maximum runnable GPU memory. Then, it verifies the accuracy of the estimated peak memory as follows: (i) **Set maximum memory**: uses  $M_d^{\text{init}} + \hat{M}_{jde}^{\text{peak}}$  as maximum runnable memory to limit usage on the target device d. We use  $M_d^{\text{max}}$  if this sum exceeds  $M_d^{\text{max}}$ . (ii) **Actual OOM**: run task with configuration j on device d to determine<sup>3</sup> whether training occurs  $OOM_{jd2}$ , expressed as (2) and measures actual peak memory  $M_{jd2}^{\text{peak}}$  similarly to the initial validation. (iii) **Estimation Correctness**: uses (4) to verify the correctness  $C_{ide2}$ . (iv) **Relative error**: uses (5) to calculate error<sub>ide2</sub>.

## D. ANOVA Experiment

We paired all models and optimizers (Table I) with 16 different batch sizes [10, 530, step: 40] to form 1,120 unique experimental configurations. Each configuration was repeated three times on an NVIDIA GeForce 4060 to minimize the impact of outliers (only 38 failures from a total of 3,360 runs). Each outcome contained four evaluation results generated by the three baselines and VeritasEst. Data were categorized into five groups, with each group representing results derived from training with a particular optimizer. Due to space limitations, we focus on two optimizers, SGD and Adam, which were also used as default optimizers in the evaluation sections of other baselines [11], [12], [15]. The results from the other three optimizers were very similar to those obtained with Adam.

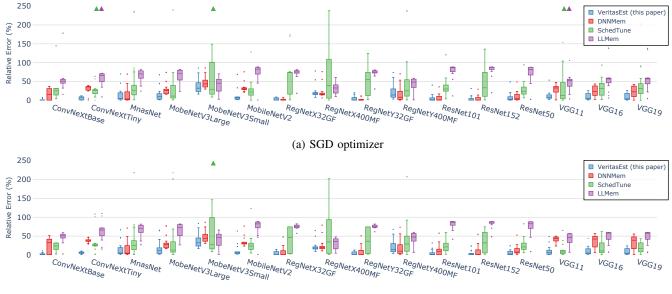

1) Relative error: The plots in Fig. 4 illustrate  $\operatorname{error}_{jde1}$  across various models, typically comprising 42 records per box. Fig. 4a shows the relative error when SGD is used as an optimizer in a training task. VeritasEst consistently outperforms the baselines, having a lower median relative error in 8 of 16 models. The error for VeritasEst ranges from 0.17% to 32.56%, with an overall median error of 6.68%. The most competitive baseline is DNNMem, yet VeritasEst achieves a lower overall median error compared to that of DNNMem (16.76%). In contrast, SchedTune and LLmem exhibit notable error variability in this experiment, with SchedTune's maximum error reaching 387.44% and LLmem's 306.69%.

Fig. 4b is the equivalent with SGD as the default optimizer. Again, VeritasEst maintains its performance with an overall median error of 5.93%. This is attributed to the evaluation of its dynamic memory mechanism throughout the training, which enables the capacity to capture the memory that Adam introduces during

the optimization process accurately. In contrast, DNNMem has worse accuracy at 23.60% owing to it employing static memory analysis. Furthermore, SchedTune maintains its high variability in this experiment, with a maximum relative error of 278.48%. However, LLmem's maximum relative error decreases to 110.03%.

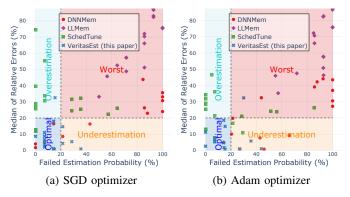

2) Probability of failed estimation: Since the relative error does not indicate the probability of estimation failure for the estimator, this section uses Fig. 5 to depict the relationship between the probability of estimation failure  $(P_{je2})$  on the x-axis, as defined in (6), and the median relative error (error<sub>jde2</sub>) on the y-axis, as defined in (7). Each marker represents 42 results.

$$P_{jie} = \frac{N - \sum_{n=1}^{N} C_{jide}}{N} \tag{6}$$

$$\operatorname{error}_{jide} = \operatorname{median}(\operatorname{error}_{jide})$$

(7)

We chose 20% as the threshold value for both axes to divide the plot into quadrants in order to distinguish acceptable estimation performance. A median relative error and failure probability below 20% are considered satisfactory, whereas those above indicate predictive risk. Each quadrant represents a distinct classification or condition: (i) Bottom left is the optimal quadrant, indicating that the results in this region have a reduced probability of estimation failure, with the estimated peak memory close to the actual value. (ii) Bottom right is the underestimation quadrant, where the results show a high probability of failure due to insufficient estimated peak memory for model training. In other words, the estimator predicts peak memory well but is not suitable to avoid OOM. (iii) Top left represents the overestimation quadrant, where results in this area have a lower probability of estimation failure, despite exhibiting a high relative error. Although it can potentially prevent OOM to some extent, results in this quadrant often inaccurately assess a model in an OOM condition, even when memory is available during training. (iv) Finally, **Top right** features the *worst* results, *i.e.*, those with both high relative error and high probability of estimation failure.

Fig. 5a presents the results of the four estimators using the SGD optimizer. Overall, VeritasEst performs robustly in terms of median relative error and estimation failure probability. Most of the results of VeritasEst are in the optimal quadrant, with four in the underestimation quadrant and one in the overestimation. By contrast, SchedTune's results predominantly lie in the overestimation quadrant, which can be attributed to its notable error variability. DNNMem, while exhibiting excellent performance in the preceding performance experiment, shows polarized results, with part of its results falling in the optimal quadrant, and seven results positioned in the worst quadrant including four that demonstrate a prediction failure rate of 100%. Finally, LLMem, consistent with its performance in the relative error experiment, shows unsatisfactory results.

Fig. 5b depicts the results obtained using the Adam optimizer, which are not dissimilar to those in Fig. 5a. Most of the VeritasEst results remain in the optimal quadrant, except for one point that lies in the worst quadrant rather than the overestimation quadrant. Despite this, it is still closer to the origin than many other points. SchedTune and LLMem exhibited results very similar to those with SGD. DNNMem, on the other hand, demonstrated substantial differences; the results that were

(b) Adam optimizer

Fig. 4: Relative error between predicted and actual memory usage in different models by estimators. Symbol  $\blacktriangle$  denotes outliers exceeding 250%; color follows the estimator legend.

Fig. 5: Four-quadrant analysis of estimator performance through failed estimation probability and median relative error. Quadrants: Bottom left is optimal; bottom right underestimation; top left overestimation; and top right worst.

originally in the optimal quadrant underwent a pronounced rightward shift, leaving only one point in the optimal quadrant. The majority of the remaining data points migrated to the underestimation and worst quadrants, owing to the limited insights made available through static analysis.

3) Runtime: The average runtime of VeritasEst (10.98 seconds) is longer than LLMem (5.40 seconds) and SchedTune (1.55 seconds), but DNNMem is the slowest (61.08 seconds). This performance difference stems from the fact that both VeritasEst and DNNMem employ data analytical methods to predict memory usage, leading to an increased processing time as the number of layers increases. In contrast, SchedTune achieves the fastest runtime by employing pre-trained models for direct estimation, and LLMem's runtime is only slightly slower than that of SchedTune because it gathers memory usage data directly using GPUs.

# V. RELATED WORK

Accurately measuring DL task requirements in the cloud is essential for preventing OOM errors and promoting efficient resource management. Numerous studies in the distributed systems literature have explored approaches such as static task requirement estimation, DL modeling, and resource scheduling to address the OOM issue. We now survey these.

## A. GPU Memory Estimator

Recent studies have explored GPU memory estimation during model training from various perspectives. Xiao et al. [26] introduced a memory estimation method in Gandiva, employing online profiling to track GPU memory use and pinpoint peak and low usage moments. Gao et al. [11] introduced DNNMem. It provides systematic estimates of GPU memory consumption by simulating memory-related activities in a memory allocator, derived from static analysis of the computational graph of DL models and user-defined cost functions. Horus [14] estimates GPU memory utilization considering four key factors: batch size, number of activations, gradients, and parameters, along with initialization overhead, to calculate the total memory requirement for a DL job. TBEM [13] estimates GPU memory consumption using a hybrid approach that combines the static analysis of computation graphs and dynamic testing in real environments with GPUs. In contrast, SchedTune [12] utilizes machine learning to estimate the maximum GPU memory requirements for DL tasks considering both model-specific features and GPU characteristics. Kim et al. [15] proposed LLMem that estimates GPU memory usage by incorporating comprehensive evaluations of model architectures, fine-tuning strategies, and distributed computation dynamics, thereby facilitating precise peak memory

predictions. Unlike VeritasEst, solutions such as DNNMem and TBEM overlook the effect of user code on memory sequences in their predictions, sticking to static computation graphs. This limits their ability to adjust to changes from user code modifications. Moreover, only DNNMem accounts for the impact of the memory allocator, as VeritasEst does.

### B. OOM-awareness

We now examine an alternative methodology for the prediction of GPU memory consumption to mitigate OOM issues. The main work here is AntMan [8], which constructs a universal memory management layer based on GPU memory and RAM allocators. This allows AntMan to allocate partial model tensors into RAM if the GPU is running out of memory. This solution has been demonstrated to be highly effective for GPU sharing. However, if a training task itself exceeds the maximum memory capacity of the selected GPU, the portion of memory that exceeds the GPU limit will remain permanently in the RAM, leading to degraded training performance and wasted resources. By contrast, VeritasEst can accurately predict GPU memory requirements to determine whether the selected GPU is suitable for the current task in advance. Furthermore, VeritasEst can provide additional information on the resource management system for a more precise plan.

## VI. CONCLUSION

The toughest challenge in determining the memory consumption for model training is the scarcity of GPU resources. In this work, we reframed the initial research problem from "How to predict memory consumption with minimal GPU usage" to "How to predict memory consumption without using a GPU at all." This shift was driven by the realization that even minimal GPU usage for prediction purposes still leads to resource contention and inefficiencies. Prediction tasks submitted to GPU queues not only face delays due to limited availability but also contribute to congestion, increasing the load on the scheduler and complicating task allocation, thereby impacting the overall efficiency of resource management. This also leads to higher financial expenditures due to the cost of GPU resources.

Inspired by previous studies [39], [40], we propose VeritasEst as a tool that uses CPU-based analysis to predict the memory consumption required for model training on a GPU, allowing operation completely without a GPU. It addresses the aforementioned challenges, as CPUs are readily available and low-cost in both local and cluster environments. VeritasEst offers dual benefits for clusters: it eases cluster load by allowing users to precisely estimate memory consumption without resubmitting tasks, and it refines scheduling strategies by providing additional memory criteria to help increase resource allocation efficiency and prevent resource wastage on tasks prone to OOM errors.

The experiments indicate that our approach has a mere 5.46% median relative error with only a 13.59% chance of estimation failure and an average run time 11.72s. It also conserves an average of 4.55 GB of GPU memory from each estimation, significantly promoting GPU memory utilization. Notably, 95% of its scores are 0.21 or lower when applying the second validation results. Compared to three state-of-the-art baselines, VeritasEst decreases the median relative error by 84.32%, the average probability of estimation failure by 73.44%, and the runtime by 50.16%.

Although PyTorch was used primarily in our experiments, the estimation methodology is applicable to other DL frameworks. Future work will address underestimations related to GPU cache data, improve VeritasEst's performance, and extend its capabilities to support distributed training and estimate memory usage for large language models (LLMs) during fine-tuning, all while maintaining GPU-free estimation.

#### REFERENCES

- S. Grigorescu, B. Trasnea, T. Cocias, and G. Macesanu, "A survey of deep learning techniques for autonomous driving," *Journal of Field Robotics*, vol. 37, no. 3, pp. 362–386, Apr. 2020.

W. Xiong, L. Wu, F. Alleva, J. Droppo, X. Huang, and A. Stolcke,

- [2] W. Xiong, L. Wu, F. Alleva, J. Droppo, X. Huang, and A. Stolcke, "The Microsoft 2017 Conversational Speech Recognition System," in *International Conference on Acoustics, Speech and Signal Processing* (*ICASSP*). IEEE, Apr. 2018, pp. 5934–5938.

- [3] S.-Y. Wang, O. Wang, R. Zhang, A. Owens, and A. A. Efros, "CNNgenerated images are surprisingly easy to spot... for now," in *Proceedings* of the IEEE/CVF Conference on Computer Vision and Pattern Recognition (CVPR), June 2020.

- [4] A. Guerriero, R. Pietrantuono, and S. Russo, "Iterative Assessment and Improvement of DNN Operational Accuracy," in *IEEE/ACM International Conference on Software Engineering: New Ideas and Emerging Results* (*ICSE-NIER*), 2023, pp. 43–48.

- H. Raza, "OpenAI's plans according to Sam Altman," May 2023. [Online]. Available: https://website-754fwhahs-humanloopml.vercel.app/blog/open\_ ai\_talk

- [6] R. Cheng, C. Cai, S. Yilmaz, R. Mitra, M. Bag, M. Ghosh, and T. Xu, "Towards GPU Memory Efficiency for Distributed Training at Scale," in Symposium on Cloud Computing (SoCC). ACM, Oct. 2023, pp. 281–297.

- [7] R. Zhang, W. Xiao, H. Zhang, Y. Liu, H. Lin, and M. Yang, "An empirical study on program failures of deep learning jobs," in ACM/IEEE International Conference on Software Engineering (ICSE). ACM, Jun. 2020, pp. 1159–1170.

- [8] W. Xiao, S. Ren, Y. Li, Y. Zhang, P. Hou, Z. Li, Y. Feng, W. Lin, and Y. Jia, "AntMan: Dynamic scaling on GPU clusters for deep learning," in Symposium on Operating Systems Design and Implementation (OSDI). USENIX, Nov. 2020, pp. 533–548.

- [9] Z. Li, Q. Cao, Y. Chen, and W. Yan, "CoTrain: Efficient Scheduling for Large-Model Training upon GPU and CPU in Parallel," in *International Conference on Parallel Processing (ICPP)*. ACM, Aug. 2023, pp. 92–101.

- [10] J. Ren, S. Rajbhandari, R. Y. Aminabadi, O. Ruwase, S. Yang, M. Zhang, D. Li, and Y. He, "ZeRO-Offload: Democratizing Billion-Scale Model Training," in *Annual Technical Conference (ATC)*. USENIX, Jul. 2021, pp. 551–564.

- [11] Y. Gao, Y. Liu, H. Zhang, Z. Li, Y. Zhu, H. Lin, and M. Yang, "Estimating GPU memory consumption of deep learning models," in *Joint Meeting on European Software Engineering Conference and Symposium on the Foundations of Software Engineering*. ACM, Nov. 2020, pp. 1342–1352.

[12] H. Albahar, S. Dongare, Y. Du, N. Zhao, A. K. Paul, and A. R. Butt,

- [12] H. Albahar, S. Dongare, Y. Du, N. Zhao, A. K. Paul, and A. R. Butt, "SchedTune: A Heterogeneity-Aware GPU Scheduler for Deep Learning," in *Symposium on Cluster, Cloud and Internet Computing (CCGrid)*. IEEE, May 2022, pp. 695–705.

- [13] H. Liu, S. Liu, C. Wen, and W. E. Wong, "TBEM: Testing-Based GPU-Memory Consumption Estimation for Deep Learning," *IEEE Access*, vol. 10, pp. 39 674–39 680, April 2022.

- [14] G. Yeung, D. Borowiec, R. Yang, A. Friday, R. Harper, and P. Garraghan, "Horus: Interference-Aware and Prediction-Based Scheduling in Deep Learning Systems," *IEEE Transactions on Parallel and Distributed Systems*, vol. 33, no. 1, pp. 88–100, Jan. 2022.

- [15] T. Kim, Y. Wang, V. Chaturvedi, L. Gupta, S. Kim, Y. Kwon, and S. Ha, "LLMem: Estimating GPU Memory Usage for Fine-Tuning Pre-Trained LLMs," in *International Joint Conference on Artificial Intelligence (IJCAI)*, Aug. 2024, pp. 6324–6332.

- [16] PyTorch, "CUDA semantics," Jul. 2024. [Online]. Available: https://pytorch.org/docs/stable/notes/cuda.html

- [17] \_\_\_\_, "CPP API," Oct. 2024. [Online]. Available: https://pytorch.org/cppdocs

- [18] M. J. Islam, G. Nguyen, R. Pan, and H. Rajan, "A comprehensive study on deep learning bug characteristics," in *Joint Meeting on European Software Engineering Conference and Symposium on the Foundations* of Software Engineering. ACM, Aug. 2019, pp. 510–520.

- [19] A. Paszke et al., "PyTorch: An Imperative Style, High-Performance Deep Learning Library," in Advances in Neural Information Processing Systems, vol. 32. Curran Associates, 2019.

- Y. Hasan and M. Chang, "A study of best-fit memory allocators," *Computer Languages, Systems & Structures*, vol. 31, no. 1, pp. 35–48, Apr. 2005.

PyTorch, "PyTorch Profiler," Aug. 2024. [Online]. Available:

- [21] PyTorch, "PyTorch Profiler," Aug. 2024. [Online]. Available https://pytorch.org/tutorials/recipes/profiler\_recipe.html

- [22] K. He, X. Zhang, S. Ren, and J. Sun, "Deep Residual Learning for Image Recognition," in *Conference on Computer Vision and Pattern Recognition* (CVPR). IEEE, Jun. 2016, pp. 770–778.

- [23] PyTorch, "Understanding CUDA Memory Usage," Sep. 2024. [Online]. Available: https://pytorch.org/docs/stable/torch\_cuda\_memory.html

- [24] —, "Datasets and DataLoaders," Oct. 2024. [Online]. Available: https://pytorch.org/tutorials/beginner/basics/data\_tutorial.html

- [25] D. P. Kingma and J. Ba, "Adam: A Method for Stochastic Optimization," in International Conference on Learning Representations, 2014.

- [26] W. Xiao, R. Bhardwaj, R. Ramjee, M. Sivathanu, N. Kwatra, Z. Han, P. Patel, X. Peng, H. Zhao, Q. Zhang, F. Yang, and L. Zhou, "Gandiva: Introspective cluster scheduling for deep learning," in *Symposium on Operating Systems Design and Implementation (OSDI)*. USENIX, Oct. 2018, pp. 595–610.

[27] Y. Peng, Y. Bao, Y. Chen, C. Wu, and C. Guo, "Optimus: An efficient

- [27] Y. Peng, Y. Bao, Y. Chen, C. Wu, and C. Guo, "Optimus: An efficient dynamic resource scheduler for deep learning clusters," in *EuroSys Conference*. ACM, Apr. 2018, pp. 1–14.

- [28] J. Gu, M. Chowdhury, K. G. Shin, Y. Zhu, M. Jeon, J. Qian, H. Liu, and C. Guo, "Tiresias: A GPU cluster manager for distributed deep learning," in *Symposium on Networked Systems Design and Implementation (NSDI)*. USENIX, Feb. 2019, pp. 485–500.

- [29] W. Gao, Q. Hu, Z. Ye, P. Sun, X. Wang, Y. Luo, T. Zhang, and Y. Wen, "Deep learning workload scheduling in GPU datacenters: Taxonomy, challenges and vision," *arXiv.org*, 2022, tex.litmapsid: 232009762.

- [30] S. Ruder, "An overview of gradient descent optimization algorithms," 2016.

- [31] K. Simonyan and A. Zisserman, "Very Deep Convolutional Networks for Large-Scale Image Recognition," in *International Conference on Learning Representations (ICLR)*. OpenReview, 2014.

- [32] M. Sandler, A. Howard, M. Zhu, A. Zhmoginov, and L.-C. Chen, "MobileNetV2: Inverted Residuals and Linear Bottlenecks," in *IEEE/CVF Conference on Computer Vision and Pattern Recognition*. IEEE, Jun. 2018, pp. 4510–4520.

- [33] A. Howard, M. Sandler, B. Chen, W. Wang, L.-C. Chen, M. Tan, G. Chu, V. Vasudevan, Y. Zhu, R. Pang, H. Adam, and Q. Le, "Searching for MobileNetV3," in *IEEE/CVF International Conference on Computer Vision (ICCV)*. IEEE, Oct. 2019, pp. 1314–1324.

- [34] M. Tan, B. Chen, R. Pang, V. Vasudevan, M. Sandler, A. Howard, and Q. V. Le, "MnasNet: Platform-Aware Neural Architecture Search for Mobile," in *IEEE/CVF Conference on Computer Vision and Pattern Recognition (CVPR)*. IEEE, Jun. 2019, pp. 2815–2823.

- [35] I. Radosavovic, R. P. Kosaraju, R. Girshick, K. He, and P. Dollar, "Designing Network Design Spaces," in *IEEE/CVF Conference on Computer Vision* and Pattern Recognition (CVPR). IEEE, Jun. 2020, pp. 10425–10433.

- [36] Z. Liu, H. Mao, C.-Y. Wu, C. Feichtenhofer, T. Darrell, and S. Xie, "A ConvNet for the 2020s," in *IEEE/CVF Conference on Computer Vision* and Pattern Recognition (CVPR). IEEE, 2022, pp. 11976–11986.

- [37] H. Scheffe, The Analysis of Variance. Wiley-Interscience, 1999.

- [38] NVIDIA Corporation, "NVML-NVIDIA Management Library," Apr. 2024. [Online]. Available: https://developer.nvidia.com/management-library-nvml

- [39] B. Chen, T. Medini, J. Farwell, S. Gobriel, C. Tai, and A. Shrivastava, "SLIDE : In Defense of Smart Algorithms over Hardware Acceleration for Large-Scale Deep Learning Systems," *arXiv*, 2019.

- [40] S. Daghaghi, N. Meisburger, M. Zhao, Y. Wu, S. Gobriel, C. Tai, and A. Shrivastava, "Accelerating SLIDE Deep Learning on Modern CPUs: Vectorization, Quantizations, Memory Optimizations, and More," arXiv, 2021.