# FlowKV: A Disaggregated Inference Framework with Low-Latency KV Cache Transfer and Load-Aware Scheduling

Weiqing Li\*, Guochao Jiang\*, Xiangyong Ding, Zhangcheng Tao, Chuzhan Hao, Chenfeng Xu, Yuewei Zhang, Hao Wang<sup>†</sup>

Alibaba Cloud Computing

{liweiqing.lwq, anyue.jgc}@alibaba-inc.com

cashenry@126.com

### **Abstract**

Disaggregated inference has become an essential framework that separates the prefill (P) and decode (D) stages in large language model inference to improve throughput. However, the KV cache transfer faces significant delays between prefill and decode nodes. The block-wise calling method and discontinuous KV cache memory allocation increase the number of calls to the transmission kernel. Additionally, existing frameworks often fix the roles of P and D nodes, leading to computational imbalances. In this paper, we propose FlowKV, a novel disaggregated inference framework, which reduces the average transmission latency of KV cache by 96%, from 0.944s to 0.053s, almost eliminating the transfer time relative to the total request latency by optimizing the KV cache transfer. FlowKV introduces the Load-Aware Scheduler for balanced request scheduling and flexible PD node allocation. This design maximizes hardware resource utilization, achieving peak system throughput across various scenarios, including normal, computational imbalance, and extreme overload conditions. Experimental results demonstrate that FlowKV significantly accelerates inference by 15.2%-48.9% on LongBench dataset compared to the baseline and supports applications with heterogeneous GPUs.

## 1 Introduction

Transformer-based (Vaswani et al., 2017) Large Language Models (LLMs), such as GPT-4 (OpenAI, 2023) and LLaMA-3 (Dubey et al., 2024), have become milestones in generative AI and provide new solutions for many industry scenarios. The vast potential of LLMs has reshaped many fields, including knowledge graphs (Ji et al., 2022), code generation (Jiang et al., 2024b), role-playing agents (Yuan et al., 2024), and information extraction (Xu et al., 2024; Jiang et al., 2024a; 2025). The rapid growth in industrial demand has created new requirements and challenges for the end-to-end inference service performance of LLMs.

LLM inference has two stages: the compute-bound prefill stage and the memory-bound decode stage. Recent integrated inference frameworks like vLLM (Kwon et al., 2023) and SGLang (Zheng et al., 2023) run both stages in the same instance, which improves inference performance. However, these methods ignore the distinct computing needs of each stage, leading to interference between them and reduced service throughput. Recent studies (Patel et al., 2024; Hu et al., 2024; Zhong et al., 2024; Qin et al., 2024) focus on disaggregated prefill and decode nodes to optimize them independently for specific tasks. This disaggregated inference framework can also scale horizontally and work with different types of computing hardware, which helps improve overall service throughput and reduce hardware costs.

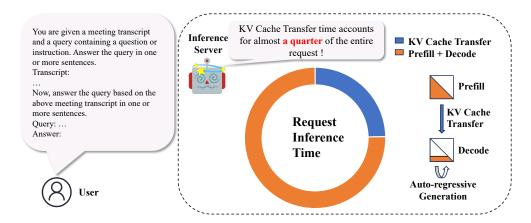

The disaggregated inference framework requires transmitting KV Cache between prefill nodes and decode nodes, an issue often overlooked in current research, as shown in Figure 1.

<sup>\*</sup>Equal contributions.

<sup>&</sup>lt;sup>†</sup>Corresponding author.

Figure 1: Time distribution of Prefill + Decode and KV Cache Transfer in a single request with NCCL-based transfer based original PagedAttention (Kwon et al., 2023). The request is sampled from the LongBench (Bai et al., 2024), with an input length of 13k and an output length of 100. In this case, the KV Cache Transfer time between the prefill node and the decode node in the disaggregated framework accounts for about a quarter of the entire inference latency.

Existing transmission schemes fall into two categories: RDMA-based transfer and NCCL-based transfer. Mooncake (Qin et al., 2024) uses an RDMA-based transfer solution that needs specific hardware. Its GPU VRAM exchange requires NVIDIA Mellanox NICs, and without them, we have to choose other solutions. Considering NCCL's good protocol compatibility (RoCE, IB, Socket), many studies have chosen to utilize NCCL. Splitwise (Patel et al., 2024) uses an NCCL-based solution that transfers data at the LLM layer level. While this approach overlaps communication and computation, its effectiveness is limited due to frequent NCCL transfers. vLLM-disaggregated (Kwon et al., 2023) uses NCCL-based buffer transfers, combining disaggregated KV Cache layer by layer into a continuous buffer before transmission. However, merging discrete tensors into complete ones causes extra memory usage and time delays, reducing overall throughput.

To address these challenges, we propose a framework that optimizes both the KV Cache structure and memory block allocator to minimize transfer time. While standard PagedAttention (Kwon et al., 2023) manages memory at block level and requires inter-node communication at the same level for KV Cache Transfer. Our KV Cache structure adjustment method reduces the number of NCCL communications, providing two benefits. First, fewer transmissions reduce the total KV Cache Transfer time with fewer communication kernels. Second, fewer communications reduce GPU computing task blocking time, which lowers overall request latency. In addition, we also propose a Load-Aware Scheduler designed to enhance the overall throughput of the inference service.

Our main contributions in this paper are summarized as follows:

- We analyze the communication patterns between prefill and decode nodes in the disaggregated inference framework. Based on our analysis, we propose modifications to the KV Cache structure and its allocator to reduce communication overhead. These optimizations effectively eliminate the KV Cache transfer time relative to the total request latency.

- We implement Load-Aware Scheduling between prefill and decode nodes, which significantly improves the overall throughput of our inference service.

- Through extensive experiments, we demonstrate the superior performance of our framework compared to existing open-source inference frameworks and validate its effectiveness across heterogeneous GPU environments.

#### 2 Related Work

**Inference Serving.** More and more inference serving systems are being proposed and updated to cope with the rapidly developing LLM application requirements. Orca (Yu et al., 2022) introduces continuous batching to improve the overall service throughput. vLLM (Kwon et al., 2023) uses paged attention to manage KV Cache memory, further alleviating the problem of GPU memory fragmentation. Sarathi (Agrawal et al., 2023) introduces chunked prefill to allow the service to perform prefill and decode requests simultaneously, optimizing the throughput of the overall inference service. TorchServe <sup>1</sup> and NVIDIA Triton <sup>2</sup> work on inference serving optimization for common transformer models. These inference serving frameworks generally process the prefill and decode tasks on the same node instance, and fail to consider the differences between the two-stage tasks compared to the disaggregated inference serving framework.

Prefill/Decode Disaggregated Inference. In light of the distinct task characteristics of LLM in the prefill and decode stages, several studies (Patel et al., 2024; Zhong et al., 2024; Hu et al., 2024; Qin et al., 2024) have explored Prefill/Decode Disaggregated Inference, achieving some improvements. All previous works separate prefill and decoding instances to enhance inference performance and propose a global scheduler for request distribution. Splitwise (Patel et al., 2024) maintains a mixed pool for expanding contracts as needed by the workload and uses a hierarchical two-level scheduling system for managing the pool and requests. MemServe (Hu et al., 2024) supports co-located P/D instances, in addition to separate prefill and decoding ones, with each instance having a memory pool for allocation, index management, and distributed transfer. Mooncake (Qin et al., 2024) features a KVCachecentric architecture that separates prefill and decoding clusters. However, these studies often overlook the latency of KV Cache transfer in single-request scenarios and thus fail to optimize this aspect.

## 3 Methodology

In this section, we first introduce the background of the disaggregated inference framework and then present the innovative optimizations of FlowKV framework proposed in this paper.

#### 3.1 Background: Prefill/Decode Disaggregated Inference

Formally, modern LLM inference framework employ autoregressive generation (Zhao et al., 2023), iteratively predicting the next token  $y_{t+1}$  based on the t input tokens  $x = \{x_1, x_2, \dots, x_t\}$ , until encountering the end-of-sequence (EOS) token.

The generation process consists of two distinct phases.

- **Prefill (P)**: Computing the initial token  $y_{t+1}$  and the associated KV cache of all t+1 tokens.

- **Decode (D)**: Iteratively generating subsequent tokens  $\{y_{t+2}, y_{t+3}, \cdots, y_{t+k}\}$  by processing only the newly generated token from the previous step while maintaining accumulated KV cache through incremental updates.

Most existing LLM inference systems (Kwon et al., 2023; Zheng et al., 2023) adopt a prefill-decode-colocated (PD-colocated) framework, where both phases are co-located on the same GPU devices despite their distinct computational characteristics. The Prefill/Decode disaggregated inference (PD-disaggregated) framework places the P nodes and D nodes on different devices, avoiding interference between the P and D phases.

Let  $\mathcal{P} = \{P_i\}_{i=1}^N$  and  $\mathcal{D} = \{D_j\}_{j=1}^M$  represent the clusters of prefill and decode nodes, respectively, where N is the number of P nodes and M is the number of D nodes. First, when

<sup>1</sup>https://pytorch.org/serve/

<sup>2</sup>https://developer.nvidia.com/triton-inference-server

the inference system receives a request R with the input token sequence  $x = \{x_1, x_2, \cdots, x_t\}$ , it selects the p-th target prefill node  $P_p$  and forwards request R to  $P_p$  for prefill computation to generate the first token  $y_{t+1}$  and KV Cache tensors  $\mathbf{K} = \{\mathbf{k}_1, \mathbf{k}_2, \cdots, \mathbf{k}_t, \mathbf{k}_{t+1}\}$  and  $\mathbf{V} = \{\mathbf{v}_1, \mathbf{v}_2, \cdots, \mathbf{v}_t, \mathbf{v}_{t+1}\}$ , where  $\mathbf{k}_i$  and  $\mathbf{v}_i$  are i-th token's KV Cache tensors. The process can be defined as follows:

$$y_{t+1}, \mathbf{K}, \mathbf{V} = P_p(R). \tag{1}$$

Second, after request R is processed, the inference system selects d-th decode node  $D_d$  and quickly transfers the KV Cache  $\mathbf{K}$  and  $\mathbf{V}$  from node  $P_p$  to node  $D_d$ .

Third, the inference system forwards request R to  $D_d$  to continue generating the next tokens  $\{y_{t+1}, y_{t+2}, \cdots, y_{t+k}\}$  iteratively. We define the request R forwarded to node  $D_d$  for decoding computation and sampling next token  $y_{t+i} (1 < i \le k)$  as follows:

$$y_{t+i}, \mathbf{k}_{t+i}, \mathbf{v}_{t+i} = D_d(\{x, y_{t+1}, \dots, y_{t+i-1}\}, \{\mathbf{k}_1, \dots, \mathbf{k}_{t+i-1}\}, \{\mathbf{v}_1, \dots, \mathbf{v}_{t+i-1}\}),$$

(2)

$$\mathbf{K} = \{\mathbf{k}_1, \mathbf{k}_2, \cdots, \mathbf{k}_{t+i}\},\tag{3}$$

$$\mathbf{V} = \{\mathbf{v}_1, \mathbf{v}_2, \cdots, \mathbf{v}_{t+i}\}. \tag{4}$$

Obviously, PD-disaggregated faces two challenges: 1. Performing a low-latency transfer of the KV cache between PD nodes, especially between heterogeneous nodes. 2. Maintaining the load balance between the P and D nodes.

#### 3.2 Overview of the Main Framework of FlowKV

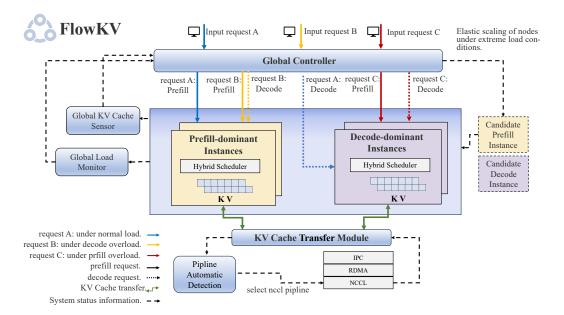

We propose the FlowKV framework, which effectively cuts down the cost and latency of KV Cache transfer. It introduces a Load-Aware Scheduler to keep all nodes running in a balanced state. FlowKV includes five main modules: Prefill nodes, Decode nodes, a global controller, hybrid schedulers, and a KV Cache transfer module, as shown in Figure 2.

FlowKV separates the dependencies between P nodes and D nodes, allowing them to run on any nodes regardless of number, ratio, or machine architecture. The global controller is FlowKV's central component, managing the scheduling of P/D processes and requests. It monitors load patterns and identifies global cache prefix matches to boost throughput and reduce KV Cache transfer latency. By creating optimal request scheduling schemes, the global controller ensures all nodes in the cluster work efficiently and supports elastic scaling of P and D nodes during overloads. The KV Cache transfer module, another key part of FlowKV, selects the best transfer pipeline based on hardware features. Unlike other architectures, FlowKV's P and D nodes perform hybrid computation when there's a computational imbalance. This capability is implemented by the hybrid scheduler within each P and D node, in collaboration with the global controller.

#### 3.3 A cost-effective low-latency KV Cache transfer solution

To handle different hardware setups, we've improved the KV Cache transfer between nodes, supporting various KV transfer methods like NCCL, Inter-Process Communication (IPC), and Remote Direct Memory Access (RDMA). In single-machine setups, IPC is the default method. In mixed deployments, NCCL is preferred because of its great performance and popularity for inter-node GPU communication.

While NCCL performs well, it only supports data transfers between contiguous memory addresses (Chen et al., 2025; Hu et al., 2024). This limitation becomes noticeable in disaggregated inference scenarios. Modern inference frameworks typically use PagedAttention (Kwon et al., 2023) to manage the KV Cache, improving memory use through logical-to-physical block mapping. However, fragmented physical blocks require NCCL to handle many small data chunks during cross-GPU transfers. This leads to a sharp increase in NCCL API calls and transmission latency. Additionally, frequent NCCL kernel launches may compete for SM resources with processes like GEMM, potentially causing more inference latency.

Figure 2: FlowKV framework. FlowKV enables high-speed transmission of KV Cache between P and D nodes through KV Cache transfer module. Furthermore, it employs a global controller to monitor the workload and KV cache status of P and D nodes in real-time. Under different load conditions (normal load, imbalanced load, extreme load), the system adopts load balancing strategies for request scheduling or performs elastic node scaling to ensure efficient resource utilization.

FlowKV introduces specific optimizations that cut down the latency of KV Cache transfer in disaggregated inference. By aiming to minimize how often the KV Cache is transfered, it first tweaks the KV Cache shape managed by PagedAttention. This change combines the separate tensor structures across all layer dimensions into a continuous tensor, reducing the number of NCCL API calls. The KV Cache shape transformation can be expressed as

$$K, V : (L, 2, B, H) \to (B, L, 2, H),$$

(5)

where B is the number of blocks, L represents the number of model layers, H represents the dimension of the remaining KV Cache vector. Thus, the number of NCCL API calls per KV block is reduced by a factor of  $L \times 2$ . Additionally, targeted optimizations are made for the PagedAttention kernel.

Second, FlowKV uses segment management techniques from operating systems to improve how traditional block allocators assign and release memory. It tries to allocate new requests within one or a few contiguous segments. It maintains continuous KV Cache blocks within these segments. FlowKV manages free memory blocks with segment-based minimum heaps. It chooses the right segments during allocation to minimize waste and merges adjacent free segments during deallocation to boost future allocation efficiency.

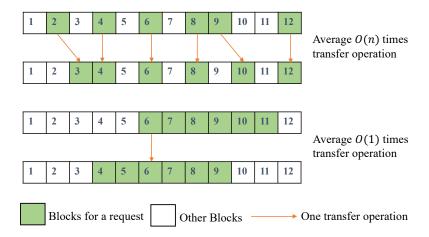

Finally, for requests that require KV Cache transfer, before triggering NCCL API calls, FlowKV performs *bidirectional segment alignment* on the KV Cache block ID lists. After alignment, the output results determine which block IDs can be merged for a single send-receive operation via NCCL, thereby minimizing the number of transfers, as illustrated in Figure 5 in the Appendix.

## 3.4 Load-Aware Scheduler for optimal compute power utilization

For PD-disaggregated inference systems, using a fixed ratio of P and D nodes isn't flexible. Under heavy loads and varying request patterns, this fixed ratio can easily overload one type of nodes, causing computational resource issues (Zhong et al., 2024). To address this, we propose a Load-Aware Scheduling scheme. It uses a global controller and local schedulers in

each P and D node to monitor each node's load status in real-time. Additionally, it balances the routing for prefill requests and decode requests through communication between the global controller and the local schedulers.

The global controller's main job is to create request scheduling plans based on each node's workload and the system's current load. It determines the best nodes to handle incoming requests. Local schedulers, or hybrid schedulers, manage both a prefill scheduler and a decode scheduler. Like vLLM's scheduler, each one has separate running, waiting, swapped, and pending queues, along with specific logic. They share a block manager with the hybrid scheduler. The hybrid scheduler manages the inference process by coordinating the prefill and decode schedulers. During each scheduling cycle, it can prioritize sub-schedulers based on the global controller's instructions. By default, prefill has priority, so all nodes focus on prefill requests when they are available.

To describe the current state of the inference system, we define three load scenarios: normal load, imbalanced load, and extreme load. Imbalanced load happens when either P or D nodes get more requests than they can handle. This causes one type of node to be GPU compute-bound while the other has low GPU use. Extreme scenarios include system overload and low load conditions. System overload occurs when both P and D nodes get more requests than they can handle. A low load scenario means there is minimal demand. Each load scenario needs a different request scheduling strategy. We outline the application of the Load-Aware Scheduling scheme in normal load, computational imbalance, and extreme scenarios in the Appendix B.1, and provide the pseudocode for Algorithm 1.

## 4 Experiments

In this section, we compare the performance of our approach under both single-node homogeneous scenarios and multi-node heterogeneous scenarios against PD-colocate inference framework and existing open-source disaggregated inference systems. Additionally, we conduct performance comparison experiments for different KV Cache transfer pipelines.

#### 4.1 Datasets and Models

- **Simulated Data**: We generated a batch of simulated data with predefined input and output lengths to compare the maximum throughput of the systems.

- Real-World Data: We selected the summarization task as a real-world benchmark to compare end-to-end response latency (E2E). The data is sampled from the summarization tasks in the LongBench (Bai et al., 2024) dataset, we select three subtasks: gov\_report, multi\_news, and qmsum.

For all scenarios, we simulate requests using a Poisson arrival process and control the request rate via requests per second (RPS).

We selected the LLaMA-3 (Dubey et al., 2024) series models (Meta-Llama-3.1-8B-Instruct <sup>3</sup>, Meta-Llama-3.1-70B-Instruct <sup>4</sup>) for testing, which are representative LLM series widely used in academia and industry.

**Baselines**. vLLM (Kwon et al., 2023) is a community-driven project contributed by both academia and industry. It uses PagedAttention to efficiently manage memory for attention keys and values combined with continuous batching to provide superior throughput performance. In addition to PD-colocated, vLLM currently also supports PD-disaggregated deployment. Other representative open-source PD-disaggregated inference systems: Mooncake (Qin et al., 2024), DistServe (Zhong et al., 2024).

• Homogeneous Performance Evaluation: This evaluation is run on an NVIDIA A100-SXM4-80GB server with 8 GPUs interconnected via NVLink links.

<sup>3</sup>https://huggingface.co/meta-llama/Llama-3.1-8B-Instruct

<sup>4</sup>https://huggingface.co/meta-llama/Llama-3.1-70B-Instruct

| Input/Output<br>tokens | RPS | DistServe<br>1P1D | Mooncake<br>1P1D | vLLM-<br>Disagg<br>1P1D | vLLM<br>PD-<br>colocated | FlowKV<br>1P1D |

|------------------------|-----|-------------------|------------------|-------------------------|--------------------------|----------------|

| 1K/256                 | 0.1 | 27.62             | 20.93            | 20.72                   | 20.93                    | 27.88          |

|                        | 0.2 | 54.78             | 41.87            | 41.84                   | 41.87                    | 55.52          |

|                        | 0.4 | 107.45            | 83.74            | 83.74                   | 83.74                    | 109.86         |

|                        | 0.6 | 158.17            | 126.93           | 125.12                  | 125.03                   | 163.45         |

|                        | 0.8 | 207.70            | 166.26           | 167.49                  | 165.75                   | 216.08         |

|                        | 1.0 | 254.04            | 206.38           | 208.00                  | 208.08                   | 267.61         |

|                        | 1.5 | 349.36            | 304.70           | 302.97                  | 304.98                   | 387.47         |

|                        | 2.0 | 404.55            | 397.18           | 394.05                  | 397.70                   | 507.36         |

| 5K/256                 | 0.1 | 26.54             | 21.08            | 21.08                   | 21.07                    | 27.86          |

|                        | 0.2 | 51.26             | 42.17            | 42.17                   | 42.17                    | 55.48          |

|                        | 0.4 | 86.99             | 83.00            | 83.48                   | 83.40                    | 109.91         |

|                        | 0.6 | 107.43            | 123.73           | 123.52                  | 124.11                   | 163.3          |

|                        | 0.8 | 109.11            | 165.41           | 162.28                  | 163.80                   | 215.35         |

|                        | 1.0 | 115.63            | 204.65           | 202.87                  | 203.04                   | 264.22         |

|                        | 1.5 | 114.00            | 291.05           | 287.40                  | 294.10                   | 382.34         |

|                        | 2.0 | 112.87            | 356.28           | 331.12                  | 378.97                   | 470.68         |

| 10K/256                | 0.1 | 20.92             | 20.52            | 20.52                   | 20.51                    | 27.85          |

|                        | 0.2 | 21.94             | 41.04            | 41.06                   | 41.05                    | 55.34          |

|                        | 0.4 | 21.93             | 81.89            | 81.83                   | 82.05                    | 109.44         |

|                        | 0.6 | 21.92             | 121.01           | 120.82                  | 121.25                   | 161.16         |

|                        | 0.8 | 21.94             | 155.78           | 154.03                  | 161.02                   | 208.61         |

|                        | 1.0 | 21.94             | 171.07           | 171.11                  | 194.24                   | 251.55         |

|                        | 1.5 | 21.94             | 63.71            | 184.61                  | 271.35                   | 281.93         |

|                        | 2.0 | 21.94             | Failure          | 185.47                  | 286.97                   | 285.14         |

Table 1: Throughput comparison based on Llama-3.1-8B-Instruct. We conducted evaluations using synthetic requests with varying input token counts of 1K, 5K, and 10K, while maintaining a fixed output token count of 256.

• Heterogeneous Performance Evaluation: This evaluation is run on two servers, L20 and H20, equipped with 4 GPUs with 48GB memory and 8 GPUs with 96GB memory, respectively. The two servers are connected via Elastic Network Interfaces (ENI), providing a basic network bandwidth allowing for low-latency KV Cache transfer.

#### 4.2 Homogeneous Deployment Scenario

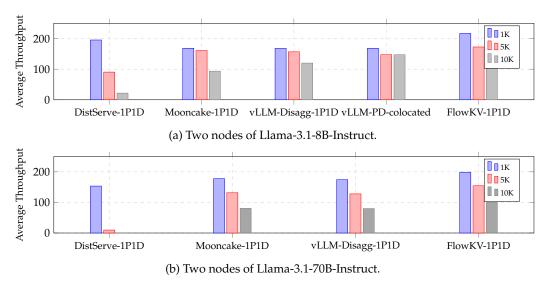

In this section, we evaluate the maximum throughput performance of FlowKV under a single-node deployment using simulated data. In this setup, the KV Cache transfer method automatically switches to IPC mode to optimize performance. The simulated dataset consists of 100 entries, with input tokens varying from 1K, 5K, to 10K, while the output tokens are fixed at 256. We gradually increase the RPS and benchmark against DistServe, Mooncake, and vLLM. Figure 3a and Table 1 illustrates the throughput performance of the Llama-3.1-8B-Instruct inference service powered by two GPUs. Compared to vLLM PD-colocated inference services, FlowKV significantly reduces mutual interference by disaggregating the P and D job processes. Additionally, this approach is enhanced by a Load-Aware Scheduling algorithm, which contributes to a 25% increase in average throughput for input tokens of 1K, 5K, and 10K. Compared to other disaggregated inference frameworks configured with a 1P1D setup, such as DistServe, Mooncake, and vLLM-Disagg, FlowKV improves throughput by 95%, 40%, and 35%, respectively.

Additionally, we conducted a performance evaluation using a large-scale parameter model for comparative analysis. Figure 3b and Table 2 illustrates the throughput performance of the Llama-3.1-70B-Instruct service deployed across eight A100 GPUs, configured as two nodes with intra-node tensor parallelism set to four. In comparison to DistServe, Mooncake, and vLLM-Disagg, FlowKV demonstrates substantial throughput enhancements, achieving improvements of 95%, 39%, and 35%, respectively.

| Input/Output<br>tokens | RPS | DistServe<br>1P1D | Mooncake<br>1P1D | vLLM-<br>Disagg<br>1P1D | FlowKV<br>1P1D |

|------------------------|-----|-------------------|------------------|-------------------------|----------------|

| 1K/256                 | 0.1 | 27.29             | 23.44            | 23.44                   | 27.67          |

|                        | 0.2 | 53.38             | 46.88            | 46.87                   | 54.69          |

|                        | 0.4 | 102.36            | 92.55            | 91.77                   | 106.74         |

|                        | 0.6 | 147.27            | 136.79           | 134.87                  | 156.28         |

|                        | 0.8 | 188.57            | 179.65           | 176.80                  | 203.51         |

|                        | 1.0 | 222.84            | 221.42           | 216.44                  | 248.03         |

|                        | 1.5 | 238.47            | 316.08           | 310.77                  | 351.10         |

|                        | 2.0 | 246.62            | 403.62           | 392.50                  | 442.12         |

| 5K/256                 | 0.1 | 9.68              | 23.57            | 23.56                   | 27.65          |

|                        | 0.2 | 9.69              | 47.12            | 46.91                   | 54.60          |

|                        | 0.4 | 9.69              | 92.58            | 91.59                   | 106.40         |

|                        | 0.6 | 9.69              | 134.74           | 133.69                  | 154.65         |

|                        | 0.8 | 9.69              | 172.68           | 167.79                  | 197.83         |

|                        | 1.0 | 9.69              | 182.81           | 178.95                  | 233.93         |

|                        | 1.5 | 9.69              | 195.32           | 188.00                  | 228.44         |

|                        | 2.0 | 9.69              | 202.72           | 191.83                  | 231.87         |

| 10K/256                | 0.1 | Failure           | 23.49            | 23.49                   | 27.62          |

|                        | 0.2 | Failure           | 46.67            | 46.62                   | 54.41          |

|                        | 0.4 | Failure           | 86.46            | 85.88                   | 103.47         |

|                        | 0.6 | Failure           | 97.10            | 96.14                   | 121.93         |

|                        | 0.8 | Failure           | 97.45            | 96.70                   | 122.62         |

|                        | 1.0 | Failure           | 97.69            | 96.93                   | 123.29         |

|                        | 1.5 | Failure           | 97.82            | 96.75                   | 123.45         |

|                        | 2.0 | Failure           | 97.75            | 96.79                   | 123.43         |

Table 2: Throughput comparison of Llama-3.1-70B-Instruct. DistServe encountered a failure when processing an input tokens of 10K.

Figure 3: Throughput performance using simulated data in homogeneous deployment scenario

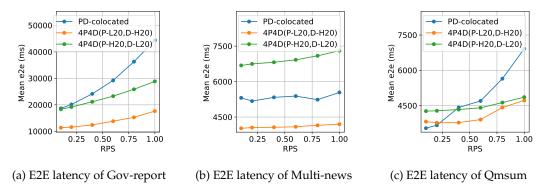

Figure 4: E2E performance in heterogeneous deployment scenario

#### 4.3 Heterogeneous Deployment Scenario

In this section, we conduct a comparative analysis of FlowKV and other baselines under heterogeneous deployment configurations, and evaluate E2E across practical application datasets. The key advantage of disaggregated heterogeneous inference lies in its capability to optimize service deployment by aligning GPU characteristics (e.g., memory bandwidth and capacity) with task-specific computational requirements. For summarization tasks demanding high decoding throughput, allocating decode operations to GPUs with superior memory resources (H20 nodes) achieves lower time-per-output-token (TPOT) and E2E.

Experimental results in Figure 4 demonstrate that the 4P4D (P-L20/D-H20) configuration outperforms 4P4D (P-H20/D-L20) with 34.67% faster average E2E on gov\_report, 40.1% on multi\_news, and 8.8% on qmsum. Notably, vLLM's co-located prefill and decode phases exhibit significant throughput degradation during extended prefill operations, failing to meet TPOT constraints. Our heterogeneous deployment strategy effectively resolves this limitation. Compared to vLLM PD-colocated inference services, the 4P4D (P-L20/D-H20) configuration achieves 48.9% faster E2E on gov\_report, 29.4% on multi\_news, and 15.2% on qmsum. Concurrent TPOT improvements reach 44.57%, 24.2%, and 15% , respectively.

#### 4.4 KV Cache transfer latency evaluation

In this section, we compare the KV Cache transfer latency based on simulated data for both single-server deployments (using a single L20 server) and multi-server heterogeneous deployments (using one L20 server and one H20 server) of Llama-3.1-8B-Instruct, with a deployment configuration of 1P1D. We also conduct a performance comparison with other disaggregated methods such as vLLM-Disagg and Mooncake. Additionally, we perform ablation experiments focused on transmission optimization for the NCCL pipeline, contrasting it with layer-wise transmission. The results are shown in the Table 3.

In single-server deployments, our NCCL pipeline reduces the average latency by 96.8% compared to vLLM-Disagg, achieving a speedup of 31.5×. When compared to the RDMA-based backend employed in Mooncake, our approach decreases the average latency by 98.2%, resulting in a speedup of 55.2×. In multi-server heterogeneous deployments, our NCCL pipeline reduces the average latency by 92% compared to vLLM-Disagg and by 96.3% compared to Mooncake, with corresponding speedups of 12.6× and 55.3×, respectively. Compared to the baseline layerwise-level KV Cache transfer, our method significantly reduces the number of NCCL kernel invocations per request, from 23,469 to just 1. In single-server deployments, the speedup is 24×, while in multi-server deployments, it is 15×.

## 5 Conclusion

We propose FlowKV, an innovative PD-disaggregated LLM inference framework that supports both homogeneous and heterogeneous deployment. FlowKV introduces multiple KV

cache transmission methods and achieves significant reductions in transmission latency when utilizing NCCL as the backend, demonstrating speedup ratios of 24× and 15× in single-node and multi-node configurations, respectively. Through Load-Aware Scheduler, FlowKV maximizes hardware utilization to enhance system throughput. Experimental results demonstrate a 25% improvement in throughput compared to baseline systems, with significant advantages of 95%, 40%, and 35% higher throughput over DistServe, Mooncake, and vLLM-Disagg, respectively. The framework exhibits scalable performance in heterogeneous GPU environments, delivering 15.2%-48.9% inference acceleration on gov report, multi news, and qmsum datasets compared to baseline.

## References

Amey Agrawal, Ashish Panwar, Jayashree Mohan, Nipun Kwatra, Bhargav S. Gulavani, and Ramachandran Ramjee. SARATHI: efficient LLM inference by piggybacking decodes with chunked prefills. *CoRR*, abs/2308.16369, 2023. doi: 10.48550/ARXIV.2308.16369. URL https://doi.org/10.48550/arXiv.2308.16369.

Yushi Bai, Xin Lv, Jiajie Zhang, Hongchang Lyu, Jiankai Tang, Zhidian Huang, Zhengxiao Du, Xiao Liu, Aohan Zeng, Lei Hou, Yuxiao Dong, Jie Tang, and Juanzi Li. Longbench: A bilingual, multitask benchmark for long context understanding. In Lun-Wei Ku, Andre Martins, and Vivek Srikumar (eds.), *Proceedings of the 62nd Annual Meeting of the Association for Computational Linguistics (Volume 1: Long Papers), ACL 2024, Bangkok, Thailand, August 11-16, 2024*, pp. 3119–3137. Association for Computational Linguistics, 2024. doi: 10.18653/V1/2024.ACL-LONG.172. URL https://doi.org/10.18653/v1/2024.acl-long.172.

Shiyang Chen, Rain Jiang, Dezhi Yu, Jinlai Xu, Mengyuan Chao, Fanlong Meng, Chenyu Jiang, Wei Xu, and Hang Liu. Kvdirect: Distributed disaggregated LLM inference. *CoRR*, abs/2501.14743, 2025. doi: 10.48550/ARXIV.2501.14743. URL https://doi.org/10.48550/arXiv.2501.14743.

Abhimanyu Dubey, Abhinav Jauhri, Abhinav Pandey, Abhishek Kadian, Ahmad Al-Dahle, Aiesha Letman, Akhil Mathur, Alan Schelten, Amy Yang, Angela Fan, Anirudh Goyal, Anthony Hartshorn, Aobo Yang, Archi Mitra, Archie Sravankumar, Artem Korenev, Arthur Hinsvark, Arun Rao, Aston Zhang, Aurélien Rodriguez, Austen Gregerson, Ava Spataru, Baptiste Rozière, Bethany Biron, Binh Tang, Bobbie Chern, Charlotte Caucheteux, Chaya Nayak, Chloe Bi, Chris Marra, Chris McConnell, Christian Keller, Christophe Touret, Chunyang Wu, Corinne Wong, Cristian Canton Ferrer, Cyrus Nikolaidis, Damien Allonsius, Daniel Song, Danielle Pintz, Danny Livshits, and et al. The llama 3 herd of models. *CoRR*, abs/2407.21783, 2024. doi: 10.48550/ARXIV.2407.21783. URL https://doi.org/10.48550/arXiv.2407.21783.

Cunchen Hu, Heyang Huang, Junhao Hu, Jiang Xu, Xusheng Chen, Tao Xie, Chenxi Wang, Sa Wang, Yungang Bao, Ninghui Sun, and Yizhou Shan. Memserve: Context caching for disaggregated LLM serving with elastic memory pool. *CoRR*, abs/2406.17565, 2024. doi: 10.48550/ARXIV.2406.17565. URL https://doi.org/10.48550/arXiv.2406.17565.

Shaoxiong Ji, Shirui Pan, Erik Cambria, Pekka Marttinen, and Philip S. Yu. A survey on knowledge graphs: Representation, acquisition, and applications. *IEEE Trans. Neural Networks Learn. Syst.*, 33(2):494–514, 2022. doi: 10.1109/TNNLS.2021.3070843. URL https://doi.org/10.1109/TNNLS.2021.3070843.

Guochao Jiang, Ziqin Luo, Yuchen Shi, Dixuan Wang, Jiaqing Liang, and Deqing Yang. Toner: Type-oriented named entity recognition with generative language model. In Nicoletta Calzolari, Min-Yen Kan, Véronique Hoste, Alessandro Lenci, Sakriani Sakti, and Nianwen Xue (eds.), Proceedings of the 2024 Joint International Conference on Computational Linguistics, Language Resources and Evaluation, LREC/COLING 2024, 20-25 May, 2024, Torino, Italy, pp. 16251–16262. ELRA and ICCL, 2024a. URL https://aclanthology.org/2024.lrec-main.1412.

Guochao Jiang, Ziqin Luo, Chengwei Hu, Zepeng Ding, and Deqing Yang. Mitigating out-of-entity errors in named entity recognition: A sentence-level strategy. In Owen

- Rambow, Leo Wanner, Marianna Apidianaki, Hend Al-Khalifa, Barbara Di Eugenio, and Steven Schockaert (eds.), *Proceedings of the 31st International Conference on Computational Linguistics*, *COLING* 2025, *Abu Dhabi*, *UAE*, *January* 19-24, 2025, pp. 7754–7765. Association for Computational Linguistics, 2025. URL https://aclanthology.org/2025.coling-main.519/.

- Juyong Jiang, Fan Wang, Jiasi Shen, Sungju Kim, and Sunghun Kim. A survey on large language models for code generation. *CoRR*, abs/2406.00515, 2024b. doi: 10.48550/ARXIV.2406.00515. URL https://doi.org/10.48550/arXiv.2406.00515.

- Woosuk Kwon, Zhuohan Li, Siyuan Zhuang, Ying Sheng, Lianmin Zheng, Cody Hao Yu, Joseph Gonzalez, Hao Zhang, and Ion Stoica. Efficient memory management for large language model serving with pagedattention. In Jason Flinn, Margo I. Seltzer, Peter Druschel, Antoine Kaufmann, and Jonathan Mace (eds.), *Proceedings of the 29th Symposium on Operating Systems Principles, SOSP 2023, Koblenz, Germany, October 23-26, 2023*, pp. 611–626. ACM, 2023. doi: 10.1145/3600006.3613165. URL https://doi.org/10.1145/3600006.3613165.

- OpenAI. GPT-4 technical report. *CoRR*, abs/2303.08774, 2023. doi: 10.48550/ARXIV.2303. 08774. URL https://doi.org/10.48550/arXiv.2303.08774.

- Pratyush Patel, Esha Choukse, Chaojie Zhang, Aashaka Shah, Íñigo Goiri, Saeed Maleki, and Ricardo Bianchini. Splitwise: Efficient generative LLM inference using phase splitting. In 51st ACM/IEEE Annual International Symposium on Computer Architecture, ISCA 2024, Buenos Aires, Argentina, June 29 July 3, 2024, pp. 118–132. IEEE, 2024. doi: 10.1109/ISCA59077.2024.00019. URL https://doi.org/10.1109/ISCA59077.2024.00019.

- Ruoyu Qin, Zheming Li, Weiran He, Mingxing Zhang, Yongwei Wu, Weimin Zheng, and Xinran Xu. Mooncake: A kvcache-centric disaggregated architecture for LLM serving. *CoRR*, abs/2407.00079, 2024. doi: 10.48550/ARXIV.2407.00079. URL https://doi.org/10.48550/arXiv.2407.00079.

- Ashish Vaswani, Noam Shazeer, Niki Parmar, Jakob Uszkoreit, Llion Jones, Aidan N. Gomez, Lukasz Kaiser, and Illia Polosukhin. Attention is all you need. In Isabelle Guyon, Ulrike von Luxburg, Samy Bengio, Hanna M. Wallach, Rob Fergus, S. V. N. Vishwanathan, and Roman Garnett (eds.), Advances in Neural Information Processing Systems 30: Annual Conference on Neural Information Processing Systems 2017, December 4-9, 2017, Long Beach, CA, USA, pp. 5998–6008, 2017. URL https://proceedings.neurips.cc/paper/2017/hash/3f5ee243547dee91fbd053c1c4a845aa-Abstract.html.

- Derong Xu, Wei Chen, Wenjun Peng, Chao Zhang, Tong Xu, Xiangyu Zhao, Xian Wu, Yefeng Zheng, Yang Wang, and Enhong Chen. Large language models for generative information extraction: a survey. *Frontiers Comput. Sci.*, 18(6):186357, 2024. doi: 10.1007/S11704-024-40555-Y. URL https://doi.org/10.1007/s11704-024-40555-y.

- Gyeong-In Yu, Joo Seong Jeong, Geon-Woo Kim, Soojeong Kim, and Byung-Gon Chun. Orca: A distributed serving system for transformer-based generative models. In Marcos K. Aguilera and Hakim Weatherspoon (eds.), 16th USENIX Symposium on Operating Systems Design and Implementation, OSDI 2022, Carlsbad, CA, USA, July 11-13, 2022, pp. 521–538. USENIX Association, 2022. URL https://www.usenix.org/conference/osdi22/presentation/yu.

- Xinfeng Yuan, Siyu Yuan, Yuhan Cui, Tianhe Lin, Xintao Wang, Rui Xu, Jiangjie Chen, and Deqing Yang. Evaluating character understanding of large language models via character profiling from fictional works. In Yaser Al-Onaizan, Mohit Bansal, and Yun-Nung Chen (eds.), *Proceedings of the 2024 Conference on Empirical Methods in Natural Language Processing*, EMNLP 2024, Miami, FL, USA, November 12-16, 2024, pp. 8015–8036. Association for Computational Linguistics, 2024. URL https://aclanthology.org/2024.emnlp-main.456.

- Wayne Xin Zhao, Kun Zhou, Junyi Li, Tianyi Tang, Xiaolei Wang, Yupeng Hou, Yingqian Min, Beichen Zhang, Junjie Zhang, Zican Dong, Yifan Du, Chen Yang, Yushuo Chen,

Zhipeng Chen, Jinhao Jiang, Ruiyang Ren, Yifan Li, Xinyu Tang, Zikang Liu, Peiyu Liu, Jian-Yun Nie, and Ji-Rong Wen. A survey of large language models. *CoRR*, abs/2303.18223, 2023. doi: 10.48550/ARXIV.2303.18223. URL https://doi.org/10.48550/arXiv.2303.18223.

Lianmin Zheng, Liangsheng Yin, Zhiqiang Xie, Jeff Huang, Chuyue Sun, Cody Hao Yu, Shiyi Cao, Christos Kozyrakis, Ion Stoica, Joseph E. Gonzalez, Clark W. Barrett, and Ying Sheng. Efficiently programming large language models using sglang. *CoRR*, abs/2312.07104, 2023. doi: 10.48550/ARXIV.2312.07104. URL https://doi.org/10.48550/arXiv.2312.07104.

Yinmin Zhong, Shengyu Liu, Junda Chen, Jianbo Hu, Yibo Zhu, Xuanzhe Liu, Xin Jin, and Hao Zhang. Distserve: Disaggregating prefill and decoding for goodput-optimized large language model serving. In Ada Gavrilovska and Douglas B. Terry (eds.), 18th USENIX Symposium on Operating Systems Design and Implementation, OSDI 2024, Santa Clara, CA, USA, July 10-12, 2024, pp. 193–210. USENIX Association, 2024. URL https://www.usenix.org/conference/osdi24/presentation/zhong-yinmin.

## A Supplementary Experimental Results and Figures

Figure 5: Comparison of the KV Cache transfer process in FlowKV with the pre-optimization approach. FlowKV aims to allocate the KV cache block IDs of both the sending and receiving instances within a contiguous memory segment as much as possible. Prior to the transfer operation, bidirectional segment alignment is performed to compare the block ID lists of both the sending and receiving instances, identifying N contiguous block IDs that are present on both sides. Since these N block IDs are memory-contiguous, they can be transferred in a single operation. The diagram illustrates an ideal scenario where the number of NCCL kernel calls in the KV Cache transfer operation is optimized from O(n) times to O(1).

| Setup         | Input/<br>Output | Mooncake | vLLM-<br>Disagg | FlowKV<br>Layerwise | FlowKV |

|---------------|------------------|----------|-----------------|---------------------|--------|

| Single        | 500/100          | 0.3010   | 0.1179          | 0.0678              | 0.0044 |

| Machine       | 1000/100         | 0.5416   | 0.2314          | 0.1309              | 0.0075 |

|               | 2000/100         | 1.0335   | 0.3435          | 0.2565              | 0.0126 |

|               | 4000/100         | 1.3473   | 0.6670          | 0.5338              | 0.0236 |

|               | 8000/100         | 2.0289   | 1.3382          | 1.1173              | 0.0447 |

|               | 10000/100        | Failure  | 1.7373          | 1.4121              | 0.0555 |

|               | 12000/100        | Failure  | 2.1894          | 1.7218              | 0.0681 |

| Multiple      | 500/100          | 0.3418   | 0.1197          | 0.1176              | 0.0080 |

| Heterogeneous | 1000/100         | 0.5820   | 0.1914          | 0.3262              | 0.0136 |

| Machines      | 2000/100         | 0.8180   | 0.3444          | 0.4324              | 0.0260 |

|               | 4000/100         | 1.4342   | 0.6681          | 0.8668              | 0.0519 |

|               | 8000/100         | 2.1250   | 1.3462          | 1.6711              | 0.0993 |

|               | 10000/100        | Failure  | 1.7425          | 2.0719              | 0.1500 |

|               | 12000/100        | Failure  | 2.1974          | 2.4965              | 0.1759 |

Table 3: Comparison of KV Cache transfer latency based on the Llama-3.1-8B-Instruct model with a deployment configuration of 1P1D. The unit in the figure is seconds.

## B Load-Aware Scheduling

#### B.1 Application of Load-Aware Scheduling Scheme in Different Scenarios

**Normal Load**. The global controller selects the optimal  $P_t$  node for prefill requests with the goal of minimizing Time-To-First-Token (TTFT), taking into account KV-cache prefix hits

and node loads. Subsequently,  $D_t$  node are chosen for subsequent KV-cache transmission and decoding, with the goal of minimizing transmission latency.

**Imbalanced Load**. Due to the inherent delay between simple request routing and node workload adjustments, under computational imbalance scenarios, the global scheduler directly instructs idle nodes' hybrid schedulers to switch inference roles for several scheduling cycles, alleviating computational resource bubbles due to uneven loads.

**Extreme Load**. The global controller assesses load scores, and if their duration exceeds a threshold, it determines the need to scale up by increasing the number of nodes for specific roles, or conversely, scale down. After scaling, dynamic restructuring of the cluster is necessary. This strategy aids in maintaining high system availability and cost efficiency.

### **B.2** Node Status Indicator Description

We employ several metrics to evaluate node load status, including the running queue lengths  $(L_r)$ , waiting queue lengths  $(L_w)$ , swapped queue lengths  $(L_{sw})$ , and sending queue lengths  $(L_{se})$  of prefill/decode requests, token budget  $(T_b)$ , KV-cache utilization  $(KV_u)$ , GPU utilization  $(G_u)$ , and GPU memory bandwidth utilization  $(MB_u)$ . The sending queue, a newly introduced component, is designed to manage requests that have completed the prefill phase and are now awaiting KV cache transmission to the decode node. Due to the bursty nature of GPU tasks (e.g., temporary high load followed by periods of idleness), instantaneous sampling can result in significant fluctuations. Therefore, we utilize a sliding-window approach to smooth out transient disruptions. After acquiring status indicators, we normalize all data to effectively assess each node's load status, and establish weight coefficients w for various metrics based on task type, and compute a comprehensive load score  $(C^p$  and  $C^d$ ) through weighted calculations. These weight coefficients are determined through several successful experiments. The judgment of the entire system scenario is then derived from the load status of each node and by comparing it with predefined thresholds  $\epsilon$ .

#### **B.3** Load-Aware Scheduling scheme

#### Algorithm 1 Load-Aware Scheduling Scheme

```

1: Input: Inference requests R, weight coefficients w, predefined thresholds \epsilon

2: Output: Scheduling strategy

3: while system is running do

4:

Update the status of each node

5:

for each node i do

S_i \leftarrow egin{bmatrix} L_v^{i,prefill}, & L_v^{i,prefill}, & L_s^{i,prefill}, & L_s^{i,prefill}, & L_s^{i,decode}, & L_w^{i,decode}, & L_w^{i,decode}, & L_s^{i,decode}, & L_w^{i}, & L_s^{i,decode}, & T_b^{i}, & KV_u^{i}, & G_u^{i}, & MB_u^{i} & \end{bmatrix}

6:

Calculate the comprehensive load score C_i^p and C_i^d for each node i

8:

for each node i do C_i^p = w_{r,p}L_r^{i,prefill} + w_{w,p}L_w^{i,prefill} + w_{sw,p}L_{sw}^{i,prefill} + w_{se,p}L_{se}^{i,prefill} + w_{t,p}T_b^i + w_{kv,p}KV_u^i + w_{g,p}G_u^i + w_{mb,p}MB_u^i

C_i^d = w_{r,d}L_r^{i,decode} + w_{w,d}L_w^{i,decode} + w_{sw,d}L_{sw}^{i,decode} + w_{se,d}L_{se}^{i,decode} + w_{t,d}T_b^i + w_{kv,d}KV_u^i + w_{g,d}G_u^i + w_{mb,d}MB_u^i

9:

10:

12:

Calculate the comprehensive load scores C^p and C^d:

13:

C^p = \frac{1}{N} \sum_i C_i^p for prefill node C^d = \frac{1}{M} \sum_i C_i^d for decode node

14:

15:

Determine the scenario based on C^p and C^d if |C^p| \le \epsilon_p^{low} and |C^d| \le \epsilon_d^{low} (normal load) then

16:

17:

18:

Schedule prefill request:

Among all options P_i in the set \mathcal{P}, select the option P_t that minimizes the time to

19:

first token (TTFT), subject to a cache prefix hit condition on P_i and given the state S_i

Forward R to P_t

20:

Schedule decode request:

21:

22:

Choose from options D_i in the set \mathcal{D}, the option D_t that minimizes the transmis-

sion latency from already selected prefill option \bar{P}_t

Forward R to D_t

23:

else if |C^p| \le \epsilon_p^{high} and |C^d| \le \epsilon_d^{high} (imbalanced load) then idleNodes \leftarrow \{i|C_i < \text{threshold}\}

24:

25:

Notify local scheduler of idleNodes to adjust the priorities of the hybrid scheduler.

26:

27:

Cycle scheduling until global controller sends terminate_signal

28:

29:

Increase/decrease number of instances/nodes

30:

Perform dynamic reconfiguration of the cluster

31:

end if

32: end while

```