# TokenSim: Enabling Hardware and Software Exploration for Large Language Model Inference Systems

1<sup>st</sup> Feiyang Wu *Beihang University* Beijing, China 21373411@buaa.edu.cn 2<sup>nd</sup> Zhuohang Bian *Beihang University* Beijing, China 22373017@buaa.edu.cn 3<sup>nd</sup> Guoyang Duan

Peking University

Beijing, China

2200011004@stu.pku.edu.cn

4<sup>rd</sup> Tianle Xu

Peking University

Beijing, China

2200011072@stu.pku.edu.cn

5<sup>th</sup> Junchi Wu Peking University Beijing, China 1281236805@qq.com

6<sup>th</sup> Teng Ma

Renmin University of China & Alibaba Group

Beijing, China

sima.mt@alibaba-inc.com

7<sup>th</sup> Yongqiang Yao Sensetime Shanghai, China soundbupt@gmail.com 8<sup>th</sup> Ruihao Gong

Sensetime

Beijing, China

gongruihao@sensetime.com

9<sup>th</sup> Youwei Zhuo Peking University Beijing, China youwei@pku.edu.cn

Abstract—The increasing demand for large language model (LLM) serving has necessitated significant advancements in the optimization and profiling of LLM inference systems. As these models become integral to a wide range of applications, the need for efficient and scalable serving solutions has grown exponentially. This work introduces TokenSim, a comprehensive hardware and software exploration system designed specifically for LLM inference. TokenSim is characterized by its support for extensible system optimizations including scheduling and memory management. We validate the results with systems running with real-world datasets, achieving an error rate of less than 1%. Furthermore, TokenSim facilitates various insightful explorations into the performance and optimization of LLM serving systems.

## I. INTRODUCTION

Large Language Models (LLMs) [1], such as ChatGPT [2] and Gemini [3], have demonstrated impressive capabilities in understanding and generating human-like content, thus revolutionizing applications in chatbots [2], [4] and programming assistants [5], [6]. As LLMs gain popularity, the growing computation and memory demand of LLM serving becomes increasingly challenging.

To address the demands, researchers have introduced a variety of hardware and software optimizations. On the hardware side, new accelerators emerge with various peak floating point performance and memory bandwidth. For example, near-data-processing accelerators like [7], [8] leverages novel memory technology and achieves higher bandwidth than conventional memory systems, which makes them favorable for memory-intensive operators. On the inference system side, the optimizations primarily focus on two key areas: request scheduling and memory management. Request scheduling optimizations aim to improve the utilization of the accelerator by batching requests of different lengths, while memory management optimizations tackle with memory footprint and memory access efficiency. For example, vLLM [9] adopts optimizations in both categories, which lead to orders of magnitude of latency reduction. Therefore, these system optimizations have become the norm in realworld LLM serving systems. The hardware and software innovations also open up new opportunities in cross-stack optimizations. For example, when managing a cluster of novel hardware accelerators, it is intuitive to implement heterogeneity-aware scheduling policies in the inference system.

Due to the diversity and complexity of existing optimization methods, it is important for LLM practitioners to understand and predict the performance and resource demand of LLM inference systems. Currently, several simulators [10], [11] support the performance modeling of different hardware. Unfortunately, they restrict the input

to single request or single batch, reporting only two numbers for a test case: latency and memory usage. These metrics are not enough for both the developers and users of LLM inference. In real-world LLM inference, a system typically handles hundreds to thousands of concurrent requests from different users. The user satisfaction is closely related with tail latency and it is important to obtain the distribution of the latency. As new requests enter and leave the system, memory usage also changes.

In this work, we address the lack of dynamic support by providing a highly modular and extensible simulator TokenSim. As shown in table I, TokenSim has two key features: (i) dynamic LLM request input support sampled from real datasets; (ii) user-defined scheduling and memory management at operator-level granularity. With the introduction of these new features, TokenSim can simulate QoS measures and generate detailed performance results, including the latency distribution and memory usage over time.

We present several case studies to facilitate hardware and software exploration. First, we demonstrate that existing simulators yield highly inaccurate performance metrics for dynamic LLM workloads due to their lack of batching support, as discussed in Section IV-A. Subsequently, we conduct experiments involving various software optimizations. These include limiting the GPU memory utilization ratio (Section IV-B), examining the worker ratio (Sections IV-C1), and identifying the optimal hardware type for decode workers in disaggregated settings (Section IV-C2). Leveraging TokenSim's memory management design, we also assess the performance implications of utilizing a memory pool for long conversations (Section IV-E). These experiments underscore the significance of system-level simulation. Finally, we investigate the impact of FLOPS, memory bandwidth, and memory capacity in a real LLM serving system (Section V), providing insights into the different hardware resource demands between prefill and decode workers.

#### II. BACKGROUND

# A. LLM Inference

Typically, large language models (LLMs) [1] are composed of several transformer [12] decoder blocks, each containing a self-attention and a multi-layer perceptron (MLP). During the generation process, the LLM samples and generates new tokens one by one, with each token depending on all preceding tokens. Due to this sequential dependency, the key and value vectors generated by preceding tokens in self-attention are often cached for generating subsequent tokens, referred to as the key-value (KV) cache [13].

TABLE I: Comparison of LLM Simulation Methods.

| Methods    | Modular | Scheduler | Mem Manager  | Portable | Dataset      |

|------------|---------|-----------|--------------|----------|--------------|

| Roofline   | X       | ×         | X            | <b>√</b> | X            |

| GenZ       | ×       | X         | ×            | X        | X            |

| LLMCompass | X       | X         | ×            | X        | X            |

| TokenSim   | ✓       | ✓         | $\checkmark$ | ✓        | $\checkmark$ |

Depending on the cauculation method, the inference process is often divided into two stages: In the **prefill stage**, each request runs only one iteration to generate the KV cache for the prompt part. This stage involves parallel computation of each token in the prompt through matrix multiplication, making it highly **compute-bound**. In the **decode stage**, the LLM utilizes the previously generated KV cache to autoregressively generate subsequent tokens over several iterations. This stage involves matrix-vector multiplication, calculating only one new token at a time, thus making it highly **memory-bound**.

## B. LLM Inference System Optimizations

Continuous batching [14] is a technique employed in the inference of LLMs to enhance throughput and efficiency. In traditional static batching, requests are accumulated and not processed until a batch is full, which often lead to delays. Continuous batching, on the other hand, allows for immediate processing of incoming requests by dynamically adjusting the batch size between iterations. This approach achieves high GPU utilization through fine-grained batch adjustment, allowing requests to be processed immediately upon arrival, thereby significantly improved request latency.

PagedAttention [9] is an advanced technique for managing KV cache during inference. It mitigates memory fragmentation caused by varying request and output lengths by partitioning GPU memory into blocks and mapping logical to physical blocks, similar to the operating system memory management. This approach enhances memory efficiency and significantly improves overall throughput.

Disaggregated serving [15], [16] is a recent optimization that focus on the distinct characteristics of prefill and decode stages. By disaggregating the stages across different devices, it allows for optimized resource allocation, thereby improving overall efficiency in LLM inference. Based on the disaggregated architectures, in order to reuse KV cache between multi-round conversations, CachedAttention [17] introduces a novel system integrating context caching based on disaggregated architecture. CachedAttention maintains a caching system that leverages efficient memory and storage mediums to save KV caches for all requests. MemServe [18] implements a similar system with a memory pool managing distributed KV cache through APIs, while enhancing cache reuse through a global prompt tree-based locality-aware policy. Both approaches improve the efficiency of serving multi-round conversations by optimizing cache management and reuse strategies.

# C. Simulating Frameworks

To efficiently and quickly conduct targeting tests, some studies [10] [11] have been proposed to provide simulations specifically for LLM inference tasks. **GenZ** [10] offers the simulation of single LLM inference iteration for different parallel methods and hardware parameters.**LLMCompass** [11] goes a step further by simulating single-layer computation of LLM inference based on different systolic arrays and buffer designs.

Recent advancements in the field have introduced support for sophisticated scheduling techniques, such as continuous batching, and advanced memory management strategies, like PagedAttention.

Vidur [19] is a large-scale simulation framework that supports advanced scheduling methods and memory management, following the approach of vLLM [9]. However, it relies on random forest regression models to estimate calculation runtime, which may introduce additional errors. Meanwhile, LLMServingSim [20] provides a hardware-software co-simulation infrastructure but suffers from significant performance limitations and lacks flexibility for customizing new models and hardware architectures.

Our TokenSim employs a detailed transformer-oriented simulation model to address these limitations, achieving higher accuracy while maintaining faster simulation speeds. Moreover, TokenSim supports novel techniques, such as simulating disaggregated prefill and decoding phases. [16] This approach enables comprehensive precision improvements without sacrificing efficiency.

## III. TOKENSIM DESIGN

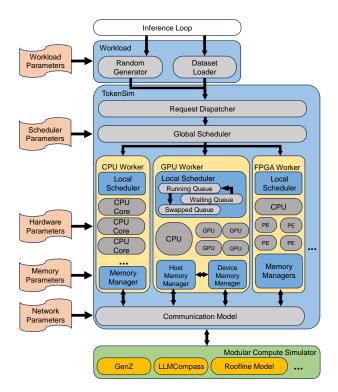

Fig. 1: TokenSim system overview.

In this section, we describe the internal implementation of Token-Sim and demonstrate how users can define their own scheduling and memory management policies in a modular and extensible manner.

TokenSim utilizes the SimPy [21] library to conduct simulations, leveraging its event-driven architecture to model complex systems efficiently. SimPy is a lightweight, discrete-event simulation framework that allows for the modeling of active components, such as workers and devices, working parallel with time tracked within an simulated environment. SimPy empowers TokenSim the ability to simulate processes in a highly efficient manner, supporting running even on personal computers without GPU.

Figure 1 shows the architecture of TokenSim. The system operates within an inference loop tracking simulated time across all workers. TokenSim generates workloads from datasets and parameters, with requests dispatched by a dispatcher to the global scheduler, which allocates them to workers based on user-defined settings.

```

global_scheduler

on_arrive: "re

transformer

num_layers: 32

name:

network: "Ethernet-100G

scatter: "RoundRobin

transmit: "RoundRobin

self_attn:

name: "Prefill"

on_finish: "submit()

quantity: 2

hardware: "A100'

intra_first: true

dim: [hid, 3*hid]

connection: "PCIe"

local_scheduler:

softmax

op: "Softmax"

run_decode: false

on_first_fin: "put_kv()"

policy: "Continuous'

out_gemm:

op: "GEMM"

before_sched: "ratio()

policy_params:

memory: "PagedAttn"

max_batched_tokens: 1000

dim: [hid, hid]

hook_after: "lo

quantity: 6

hardware: "A100'

# omitted for brevity

connection: "NVLink

block_size: 16

gpu_utilization: 0.8

run_prefill: false

on_st: "get_kv()"

layer_norm:

op: "LayerNorm"

```

- (a) Hardware config

- (b) Scheduler config

- (c) Model config

Fig. 2: One example of TokenSim configurations.

Each worker runs concurrently, managed by local schedulers employing various algorithms. These schedulers coordinate with memory managers that monitor device memory utilization. Once a batch is formed by scheduler for an iteration, relevant information is sent to a compute simulator, like GenZ, to determine iteration time. The architecture supports diverse compute simulators, enabling various hardware configurations and simulation methods. When interdevice data movement occurs, the communication model calculates transfer latency by connecting memory managers based on network parameters.

#### A. TokenSim Scheduler

Existing LLM inference systems employ advanced intra-worker (continous batching) and inter-worker (disaggregation) scheduling techniques. To support both current and future innovations, TokenSim features a **two-stage scheduler** with a global scheduler and local schedulers for each worker. The global scheduler manages incoming requests, assigning them to workers, while local schedulers decide between iterations whether requests should remain local or return to the global scheduler.

User-defined functions for both schedulers can be configured by modifying configuration file as shown in Figure ??. The scheduler function API provides all system information. For example, the global scheduler can access the number of current workers, their hardware type, and concurrent requests. It can also be stateful, so that users can actively store the number of requests already dispatched to a worker in a given time window, and uses the record book for future load-aware scheduling. For the local scheduler, the most important information needed in scheduling algorithm is the current task queue and memory utilization status. Fortunately, TokenSim is able to simulate memory changes in real time, as will be described in the next section.

To take full control of scheduling granularity, TokenSim introduces a **breakpoint** feature, enabling operator-level hooks in model configurations (Figure ??). Default breakpoints invoke the scheduler after each token generation. This setup simplifies implementing optimizations like disaggregation, which uses breakpoints for KV cache transfer with two lines of code, as shown in ??.

In TokenSim, breakpoints can be explicitly added at the end of the model configuration file and linked to: 1) a local scheduler that returns requests with new tokens to the global scheduler, and 2) a global scheduler that dispatches these requests to decode devices, as shown in Figure 3.

## B. TokenSim Memory Manager

Current techniques like PagedAttention have added significant complexity to memory management. To support these innovations, TokenSim implements memory managers for various worker types,

```

def schedule_local(worker: Worker, running_reqs, dispatch_reqs):

submit_global([r.id for running_reqs if len(r.tokens) == len(r.prompt) + 1])

return dispatch_reqs

def schedule_global(workers: list[Worker], new_reqs):

dispatch_results = {w.id: [] for w in workers}

for req in sum(w.get_submit() for w in workers, []):

target_id = random.choice(w.id for w in workers if w.run_decode)

dispatch_results[target_id].append(req)

for new_reqs:

target_id = random_choice(w.id for w in workers if w.run_prefil)

dispatch_results[target_id].append(req)

return dispatch_results

```

Fig. 3: User-defined scheduler example of global scheduler and local scheduler, defining a disaggregated architecture.

such as CPU, GPU, and FPGA, to monitor memory utilization at any granularity—by block, token, or byte—supporting user-defined scheduler behaviors.

Moreover, in a distributed environment, the memory of different workers are connected with network and inference systems tend to share them to create a large memory pool and transfer data from the memory of one node to another. For example, disaggregated architectures transfer KV cache between prefill and decode devices.

TokenSim uses a communication component to model the data transfer overhead. This model takes cache location (host or device), data size and memory bandwidth as arguments and returns the time to transfer the data to another devices.

This model is designed to support various types of memory transfer overlapping, leveraging SimPy's event-driven capabilities to facilitate both sequential and concurrent data loading and storage. By selecting appropriate data transfer sizes and overlap methods, simulations can be easily implemented.

For instance, in scenarios where data blocks are transferred from low-bandwidth to high-bandwidth storage, the default method initiates loading only after the receiver completes the previous task, executing each load and store operation sequentially. Furthermore, with more complex overlapping techniques, such as utilizing a preloading buffer, the communication model can achieve efficient data transfer by maintaining optimal buffer utilization. For an ideal transfer process that supports multiple data preloading, adjusting the model's buffer size to a larger value demonstrates the model's compatibility and simplicity.

#### C. Validation Studies

In this section, we validate the ouput of TokenSim with performance results generated from real hardware with vLLM v0.6.2.

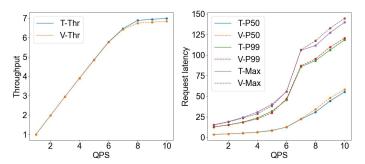

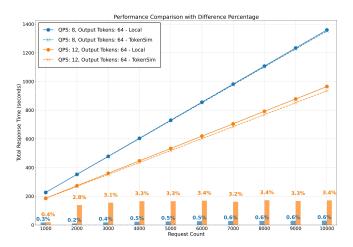

Fig. 4: vLLM throughput and latency validation. "V-" and "T-" stands for vLLM and TokenSim respectively. "Thr" denotes throughput.

To evaluate TokenSim's accuracy, we conducted experiments with the LLaMA2-7B model [22], [23] on an NVIDIA A100 GPU, using 2,000 requests from the ShareGPT dataset [24]. By varying request rates (queries per second, QPS), we compared throughput and latency

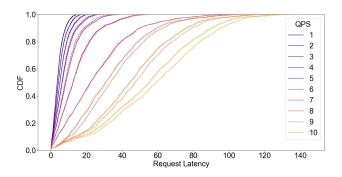

Fig. 5: vLLM latency CDF aligns with TokenSim at different QPS, dashed lines are vLLM and solid lines are TokenSim.

percentiles from TokenSim's simulations with vLLM's real-world results, as shown in Figure 4. The geometric mean error is 0.109% for throughput and 0.6%, 0.254%, and 0.337% for P50, P99, and maximum request latency, respectively.

To further validate simulation precision, we recorded request latencies and plotted the cumulative distribution function (CDF) of the latency distribution, as illustrated in Figure 5. The close alignment between TokenSim's simulations and actual hardware observations confirms a high degree of accuracy.

#### D. Comparison with State-of-the-Art Simulators

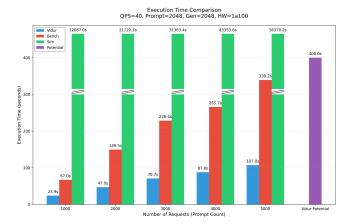

We conducted a comprehensive comparison of TokenSim against two state-of-the-art LLM inference simulators: Vidur [19] and LLM-ServingSim [20]. Our evaluation focused on two key metrics: simulation accuracy and runtime efficiency. Moreover, we test TokenSim on its ability to simulate disaggregated prefill and decoding phases.

1) Simulation Accuracy: To evaluate the simulation accuracy of TokenSim, we compared it with Vidur and LLMServingSim. The experimental setup is as follows: We conducted the experiments on an A100 GPU with 80 GB of memory. We first determined the optimal query-per-second (QPS) value by finding the point at which the LLM throughput reached 40 QPS, indicating the best performance state of the LLM. After obtaining this QPS value, we measured the total time elapsed from the submission of the first request to completion, varying the number of requests from 100 to 500.

Since the open-source version of LLMServingSim can only handle very short requests, we compared the results of all three simulators with the real-world scenario. We then compared TokenSim and Vidur with the real-world scenario using fixed token lengths ranging from 128 to 2048.

As shown in Table II, compared with the real results, TokenSim demonstrated higher accuracy than both Vidur and LLMServingSim, representing a significant improvement over the state-of-the-art level.

We attribute our high simulation accuracy to our fine-grained memory simulation. Through rigorous implementation and validation, we support block-granularity simulation, which provides a more detailed insight into the runtime status within Transformers. By adopting this approach, we avoid coarse-grained approximations in MLP simulations, thereby more accurately reflecting real-world runtime scenarios.

2) Runtime Efficiency: Regarding execution time, we compare our TokenSim with Vidur. LLMServingSim is impressively slow, even slower than the real-time behavior. As can be seen in Figure 6, although our TokenSim appears to have longer runtimes, Vidur requires a significant amount of time—about 400 seconds

TABLE II: Percentage difference in latency between real hardware results and simulations from different simulators. The bars represent the percentage error in latency for 10 output tokens across different request counts, ranging from 100 to 500.

| Request num   | 100   | 200   | 300   | 400    | 500    |

|---------------|-------|-------|-------|--------|--------|

| Local         | 2.756 | 5.246 | 7.819 | 10.371 | 12.981 |

| Vidur         | 2.371 | 4.698 | 7.246 | 9.935  | 12.122 |

| TokenSim      | 2.592 | 5.089 | 7.587 | 10.095 | 12.593 |

| LLMServingSim | 2.556 | 5.056 | 7.557 | 10.056 | 12.556 |

for pre-training before each run. Additionally, TokenSim supports fine-grained memory operation simulations, offering more detailed insights. LLMServingSim is set to handle only 10 tokens due to its limitation in simulating long prompts, and it exhibits notably slow performance.

While TokenSim may take slightly more time than Vidur, it avoids the pre-training procedure and is more lightweight. During the phase of verifying model runtime configurations, parameters may undergo substantial adjustments. The presence of numerous different configurations can render randomization ineffective. In terms of overall expected time, TokenSim still holds an advantage, with its lightweight operation allowing for more flexible adaptation.

Fig. 6: Comparison of execution time between TokenSim and Vidur. Note that Vidur requires significant pre-training time (approximately 400s) before each run, indicated by the shaded regions. Additionally, LLMServingSim is configured to handle only 10 tokens due to its inability to simulate long prompts, and it exhibits notably slow performance.

3) Disaggregated Prefill and Decoding Phases: We select Dist-Serve [16] as our real-world baseline. To the best of our knowledge, TokenSim is the first large language model simulator to support the disaggregation of prefill and decoding phases.

To validate this capability, we implement DistServe on two A100 GPUs. We measure the actual communication bandwidth between the GPUs and use this data to configure TokenSim for accurate simulation. We then compare TokenSim with DistServe using a set of requests ranging from 1000 to 10000, each with a fixed input token length of 64 tokens. We selected a QPS value of 8 to minimize the runtime variations caused by different memory scheduling strategies, thereby focusing more effectively on the simulation performance of Prefilling and Decoding separation itself.

As shown in Figure 7, TokenSim demonstrates high accuracy in simulating the disaggregated prefill and decoding phases. We

attribute the observed discrepancies to two primary sources: First, the transmission of KV-Cache over the bus is subject to unavoidable fluctuations, especially under a large volume of requests, which can accumulate and introduce certain errors. Second, DistServe employs SwiftTransformer as its underlying runtime framework, which we did not incorporate in our simulation. This difference is an inevitable source of error. Additionally, our experiments revealed that the error introduced by SwiftTransformer is more pronounced when the number of requests is relatively low.

Prefilling and Decoding separation technology is widely used in current inference deployments, offering significant performance improvements. The simulation of PD separation by TokenSim highlights its robust performance.

Fig. 7: Runtime comparison between DistServe and TokenSim. The experiment is conducted on 2 A100 GPUs, with each request comprising 64 input tokens and 64 output tokens, representing a common real-world setting. We test the actual communication bandwidth and use it for accurate simulation.

# IV. FRAMEWORK OPTIMIZATION ANALYSIS WITH TOKENSIM

In LLM inference, it is crucial to recognize that while frameworks like vLLM [9] offer recommended configurations, performance can vary significantly with different workloads and hardware environments. Consequently, optimization strategies such as scheduling methods, batch size adjustments, and the disaggregation of prefill and decode processes may not always enhance performance and could even degrade it under certain conditions.

This section investigates the impact of various optimization strategies on LLM inference, offering a thorough analysis of their interactions with different hardware configurations and workload characteristics. Through systematic evaluation, we aim to provide insights into achieving optimal performance across diverse computational environments. Our comprehensive experiments lead to six key findings, which are summarized below.

## A. Continuous Batching

Figure 8 shows an example of the execution when the inference servers takes as input four requests. In static batching, shorter requests have to wait for longer ones to finish, causing bubbles in the system. In contrast, continuous batching allows new requests to be added during batch processing. Thus GPU resources are not wasted in the bubbles. These differences lead to distinct performance characteristics of the two methods and highlight the necessity of

| R1    | R1    | R1    | R1    | R1    | R1    | END   |       |       | R5     |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------|

| R2    | R2    | R2    | R2    | END   |       |       |       |       | R6     |

| R3    | R3    | R3    | R3    | R3    | END   |       |       |       | R7     |

| R4    | END   | R8     |

| iter1 | iter2 | iter3 | iter4 | iter5 | iter6 | iter7 | iter8 | iter9 | iter10 |

| R1    | R1    | R1    | R1    | R1    | R1    | END   | R8    | R8    | R8     |

| R2    | R2    | R2    | R2    | END   | R6    | R6    | R6    | R6    | R6     |

| R3    | R3    | R3    | R3    | R3    | END   | R7    | R7    | R7    | R7     |

| R4    | END   | R10    |

|       |       | R5    | R5    | R5    | R5    | R5    | END   | R9    | R9     |

Fig. 8: Comparing iterations of static batching (above) and continuous batching (below). Yellow blocks denote the prefill stage and blue blocks denote the decode stage. White blocks are bubbles.

simulating continuous batching to accurately predict LLM inference system behavior.

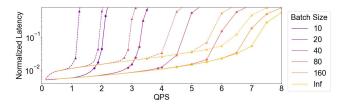

Figure 9 compares the system latency percentile with static and continuous batching. Using an A100 GPU for the LLaMA2-7B model, the experiment processed 50,000 random requests from the ShareGPT dataset. To demonstrate continuous batching's unique attributes, the maximum number of batched requests is restricted to match static batching. A batch size of "inf" indicates no limit, allowing the scheduler to maximize resource utilization. Performance is assessed using a normalized latency metric, as evaluated by the vLLM framework [9].

Fig. 9: Normalized latency graph for static batching and continuous batching with limited batch sizes. Dashed lines are static batching and solid lines are continuous batching. "Inf" stands for no batch size limit.

As shown in Figure 9, static and continuous batching exhibit distinct latency trends. As the request rate increases, continuous batching's latency rises at a slower and more consistent rate compared to static batching. This finding directly supports **Finding 1**, highlighting that continuous batching significantly reduces latency and improves scalability, especially under increasing load conditions.

**Finding 1:** Continuous batching significantly reduces latency and improves scalability compared to static batching, especially under increasing load conditions.

# B. Input Batching

Previous research [10] indicates that increasing batch size can improve throughput with minimal latency impact. This implies that maximizing GPU memory usage for KV cache is better for end-to-end performance. However, due to differences between static and continuous batching, our study shows that maximizing GPU utilization is not universally optimal.

When longer requests require more memory and no free blocks are available, LLM frameworks often preempt new requests. This involves moving running requests from device memory to host or remote memory. More importantly, it directly impacts the tail latency because preempted requests usually takes longer than average time

to finish. In conversational scenarios, token generation speed are expected to be fast and evenly distributed. If some tokens take longer, user experience may suffer even if average decode latency meets the Service Level Objective (SLO). When preemptions occur, requests may pause, yet average latency may still comply with the SLO. Therefore, we use the maximum Token Processing Over Time (mTPOT) SLO to highlight the importance of evenly distributed token generation: no interval between tokens should exceed the mTPOT SLO, or the request won't contribute to throughput.

To address this issue, inference frameworks tend to limit batch size by setting a maximum GPU memory utilization ratio for incoming requests, reserving memory for older requests and reducing preemptions. For example, vLLM uses a *gpu\_memory\_utilization* option for performance tunning.

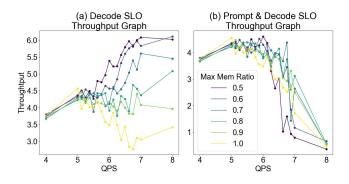

Figure 10 shows the throughput of serving requests from the ShareGPT dataset, considering only those that meet the Service Level Objectives (SLOs). We set the Time to First Token (TTFT) SLO to 15 seconds and the mTPOT SLO to 0.3 seconds. Figure 10(a) illustrates throughput with only mTPOT SLO, highlighting latency improvements in the decode stage. And figure 10(b) presents throughput considering both SLOs, demonstrating the effectiveness of this restriction in increasing throughput within SLOs. The results suggest that, under specific conditions, strategically limiting the influx of new requests while reserving memory for previously processed requests—rather than maximizing batch size—can significantly enhance the user experience by optimizing the management of future KV cache. This supports **Finding 2**, which states that limiting new requests and reserving memory for older requests can improve tail latency and user experience.

**Finding 2:** Limiting the influx of new requests and reserving memory for older requests can enhance user experience by reducing preemptions and improving tail latency, even if it means not maximizing batch size.

Fig. 10: Throughput graphs for restricting GPU memory utilization rate for new request to be scheduled. "Max Mem Ratio" denotes the GPU memory utilization rate, "Decode SLO Throughput" denotes throughput only considering mTPOT SLO, while "Prompt & Decode SLO Throughput" denotes throughput considering both TTFT and mTPOT SLO.

## C. Disaggregation Strategies

1) Device Type Ratio: Recent studies [15], [16] have introduced disaggregated architectures that separate prefill and decode stages

across independent GPUs. However, the impact of varying prefill to decode device ratios is underexplored. These ratios can significantly affect performance outcomes for workloads with specific characteristics. While some frameworks [16] offer dynamic methods to adjust these ratios, they can introduce performance trade-offs.

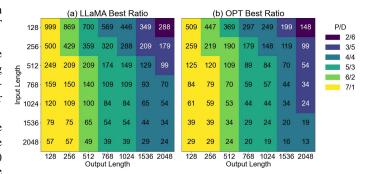

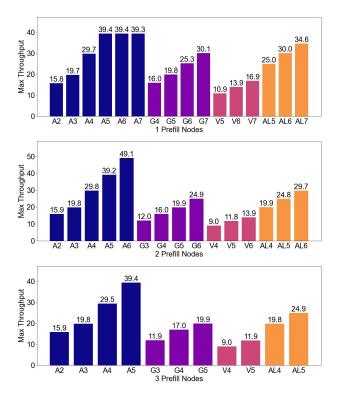

Fig. 11: Best disaggregation type ratio for an 8xA100 node running on different average input and output lengths for LLaMA2-7B and OPT-13B model. P/D denotes prefill and decode devices number. Numbers on the block denotes maximum throughput without violating SLO.

Figure 11 shows the optimal prefill to decode device ratio, depicted in different colors, on a node with 8× A100 GPUs across workloads with varying input and output sequence lengths. To maximize throughput without violating the serving SLO, increasing prefill nodes is crucial for longer output lengths, regardless of input length. However, as output length increases, shorter input lengths allow more prefill nodes to be used for decoding. This analysis supports **Finding 3**, which highlights that the optimal ratio of prefill to decode devices primarily depends on output lengths, with longer output lengths benefiting more from additional prefill devices.

**Finding 3:** The optimal ratio of prefill to decode devices in disaggregated architectures primarily depends on output lengths, with longer output lengths benefiting more from additional prefill devices.

2) Efficient Substitutes: Previous studies [10], [11] have shown that the decode stage of LLM inference is memory-bound, relying heavily on the GPU's memory capacity and bandwidth. In disaggregated architectures, prefill and decode stages can be allocated to different hardware components, optimizing based on each stage's characteristics. Since computational performance is not crucial for the decode stage, we tested various hardware configurations, including a low compute performance version of the original GPU, a cheaper GPU from a previous generation, and a Processing-In-Memory (PIM) chip known for its high memory capacity and bandwidth.

Figure 12 shows the throughput of a disaggregated architecture when different hardware devices replacing the A100 GPU in the decode stage. Due to the number of PCIe slots available on the server board, we only test configurations with 8 devices. We tested three types of hardware: the NVIDIA V100 as a cheaper GPU (about 1/4 the price of an A100) from the previous generation, the SK HYNIX GDDR6-Aim (G6-Aim) [7] as a high-performance PIM chip (about 1/2 the price of an A100), and an A100 with 1/4 compute performance.

As shown in Figure 12, if the budget allows for only 5 A100 GPUs, the optimal choice is to use 1 A100 as a prefill device and

Fig. 12: Disaggregation with Different Hardware: "V" denotes NVIDIA V100, "A" denotes NVIDIA A100, "G" denotes "SK HYNIX GDDR6-Aim", "AL" denotes A100 with 1/4 peak FLOPS. The number after the letter is the number of decode devices.

purchase 7 G6-Aim units, saving about half the cost of an A100 while achieving similar throughput. If 2 A100s are used as prefill devices, the maximum throughput is only 24.7, less than the previous 29.1. However, with a larger budget, using 2 A100s as prefill devices and other A100s as decode devices is preferable. With a smaller budget, such as purchasing only 4 A100s, using G6-Aim remains the best option, though the difference is not significant. The V100's performance is relatively poor, valuable only if the budget allows for exactly 3 or fewer A100s, but the performance difference is not substantial. The reduced compute performance version of the A100 GPU is suboptimal, indicating that the original A100's computational performance is not very excessive for the decode stage. In conclusion, PIM can be a cost-effective choice for budget-constrained scenarios but cannot replace the A100 for the decode stage due to the limitation on the total number of slots available within a node.

**Finding 4:** Processing-In-Memory (PIM) chips can be a cost-effective alternative for the decode stage in disaggregated architectures, especially when budget-constrained, although they cannot fully replace high-performance GPUs like A100 due to slot limitations.

# D. Disaggregation Memory Footpoint

To further investigate the memory requirements of the prefill and decode stages during inference, we conducted an analysis of the GPU memory usage patterns for the LLaMA2-7B model. In this experiment, we configured the input length to 128 tokens and the output length to 1024 tokens, using the optimal device allocation and query-per-second parameters identified in Figure 11. We launched a total of

10,000 requests within a fixed time window of [5,65] seconds. This time window was chosen because observing the memory footprint only requires analyzing a period of stable operation. Additionally, the prefill stage is significantly shorter in duration compared to the decode stage, which allows us to gather sufficient information within this time frame.

The memory footprint curves shown in Figure 13(a) reveal that the prefill stage exhibits significantly lower GPU memory usage compared to the decode stage during the PD separation process. This difference can be attributed to the distinct computational demands of these two stages. Prefill requires substantial initial memory allocation for KV cache computation but maintains lower memory usage thereafter, while decode sustains high memory demand due to its reliance on KV cache for autoregressive token generation.

Once the prefill stage is completed, the decode devices continue to operate under high memory load, while the prefill devices exhibit significantly lower GPU memory usage.

As highlighted in **Finding 5**, the prefill stage can be effectively managed with fewer resources, enabling more efficient GPU memory allocation and potentially enhancing system throughput. We propose that reducing the memory allocation for the prefill GPU may be a viable optimization strategy.

Following this proposal, we reduced the prefill GPU memory to half of its original capacity. Figure 13(b) shows reduce prefill GPU memory can achieve a better balance between resource utilization while the throughput remained almost the same. This finding allows for more efficient allocation of GPU memory and potentially improving overall system throughout.

Fig. 13: GPU Memory Footprint Heatmaps Over Time for Prefill and Decode Workers in a Disaggregated Architecture. The left heatmap shows the original memory allocation, while the right heatmap demonstrates the effect of reducing the prefill GPU memory to half.

**Finding 5:** The prefill stage exhibits lower memory usage compared to the decode stage. Reducing the memory allocation for the prefill GPU may be a viable optimization strategy.

# E. Memory Cache

Recent studies [17], [18] have introduced an innovative approach for serving multi-round conversations by storing the multi-round KV cache in dedicated storage for future use. However, the specific workloads and hardware configurations can vary significantly among users, making comprehensive testing under all conditions time-consuming and costly. By adding a few lines of configuration and code to TokenSim, we can effectively simulate this mechanism that uses a shared memory cache to manage KV cache from conversational contexts.

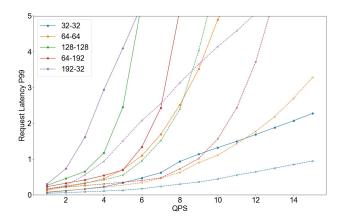

Figure 14 shows the P99 request latency across varying input and output sequence lengths, both with and without the memory cache from multi-round conversations. The conversation lengths are generated with a mean length following a Poisson distribution. To

Fig. 14: Request Latency P99 for memory cache enabled and disabled with different input and output lengths. Legends shown as "x-y" denotes input length is x and output length is y. Dashed lines indicates memory cache enabled and solid lines indicates disabled.

mimic a realistic chatbot scenario, half of the requests are single-round, while the other half involves two to seven rounds. The latency for retrieving KV cache from the memory cache is set at 800 nanoseconds per block, as referenced in [18].

The results reveal a trend similar to those in the original study while providing additional insights. As the request rate increases, using a memory cache significantly reduces latency, especially at average output lengths of 64, effectively doubling the request rate for the same P99 latency. This supports **Finding 6**, which states that memory caching optimizations are most effective for short output lengths in multi-round conversations, significantly reducing latency for outputs around 64 tokens, but offer diminishing returns for very short outputs, such as those with lengths less than or equal to 32. Overall, our observation is that memory cache optimizations are most effective for short output scenarios, but always offers advantages over the original version.

**Finding 6:** Memory caching optimizations are most effective for short output lengths in multi-round conversations, significantly reducing latency for outputs around 64 tokens, but offer diminishing returns for very short outputs (e.g.,  $\leq 32$  tokens).

### V. PLATFORM CHARACTERISTICS ANALYSIS WITH TOKENSIM

In this section, we analyze various hardware properties using the TokenSim framework. Our focus is on the following key properties:

- Computing Performance: This property reflects the ability to execute floating-point calculations.

- Memory Bandwidth: This indicates the data transfer speed to and from GPU memory, affecting how quickly data can be moved between the GPU and its memory.

- Memory Capacity: This determines the amount of data that can be stored in GPU memory, impacting the ability to handle large models and contain more KV cache.

In our experiments, we varied these properties both independently and in combination to evaluate their impact on performance. While some of our findings align with those reported by existing simulators [10], TokenSim have yielded different conclusions when system optimizations are taken into consdieration. Due to space constraints,

we present one of these findings in disaggregated settings, with plans for further exploration.

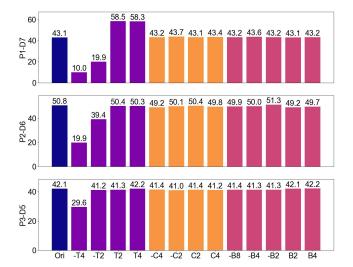

Fig. 15: Throughput for 1, 2, and 3 prefill devices ("P1-D7" denotes 1 prefill device with 7 decode device) with varying hardware parameters: "Ori" denotes original A100; "T" indicates compute performance; "C" and "B" represent capacity and bandwidth, respectively. "C2" doubles capacity while "-C2" halves it.

Figure 15 evaluates different parameters for the prefill GPU within a disaggregated architecture, processing 50,000 requests from the ShareGPT dataset at varying request rates. The figure illustrates the maximum throughput achievable without violating the SLOs. The results show that memory capacity ranging from 1/4 to 4 times that of the A100 and bandwidth from 1/8 to 4 times have minimal impact on performance, indicating the low bandwidth and capacity requirement of the prefill stage. 1/8 capacity is untested because it's lower than the model parameter size in fp16. In contrast, computational performance significantly influences throughput, but once the cumulative computational performance reaches  $2 \times 312$ , it hits the decoding capability limit, beyond which further increases do not enhance throughput. This supports Finding 7, which highlights that the prefill stage benefits more from increased computational performance rather than memory capacity or bandwidth, indicating that the A100 GPU's memory capacity and bandwidth are excessive for prefill tasks.

**Finding 7:** In disaggregated settings, the prefill stage benefits more from increased computational performance rather than memory capacity or bandwidth, indicating that the A100 GPU's memory capacity and bandwidth are excessive for prefill tasks.

# VI. CONCLUSION

This work introduces TokenSim, a highly extensible framework designed to simulate modern LLM serving systems. TokenSim is designed to work with various hardware setups and system optimizations. Its modular design, along with its support for a wide range of scheduling and memory management techniques, establishes TokenSim as a valuable tool for optimizing LLM inference systems. It shows high accuracy, with an error rate of less than 1% when simulating real-world datasets, further attests to its efficacy.

Through the use of TokenSim, we conduct an analysis of current system optimizations, including continuous batching, disaggregated architecture, and memory caching. Furthermore, we explore various hardware configurations, yielding new insights beyond existing work on disaggregated architectures.

#### REFERENCES

- [1] T. B. Brown, B. Mann, N. Ryder, M. Subbiah, J. Kaplan, P. Dhariwal, A. Neelakantan, P. Shyam, G. Sastry, A. Askell, S. Agarwal, A. Herbert-Voss, G. Krueger, T. Henighan, R. Child, A. Ramesh, D. M. Ziegler, J. Wu, C. Winter, C. Hesse, M. Chen, E. Sigler, M. Litwin, S. Gray, B. Chess, J. Clark, C. Berner, S. McCandlish, A. Radford, I. Sutskever, and D. Amodei, "Language models are few-shot learners," 2020. [Online]. Available: https://arxiv.org/abs/2005.14165

- [2] OpenAI, "Chatgpt: Language model," https://www.openai.com/chatgpt, 2023

- [3] Google, "Gemini chat to supercharge your ideas," https://gemini. google.com/, 2023.

- [4] \_\_\_\_, "Google bard," https://bard.google.com/, 2023.

- [5] GitHub, "Github copilot," https://github.com/features/copilot, 2022.

- [6] M. Chen, J. Tworek, H. Jun, Q. Yuan, H. P. de Oliveira Pinto, J. Kaplan, H. Edwards, Y. Burda, N. Joseph, G. Brockman, A. Ray, R. Puri, G. Krueger, M. Petrov, H. Khlaaf, G. Sastry, P. Mishkin, B. Chan, S. Gray, N. Ryder, M. Pavlov, A. Power, L. Kaiser, M. Bavarian, C. Winter, P. Tillet, F. P. Such, D. Cummings, M. Plappert, F. Chantzis, E. Barnes, A. Herbert-Voss, W. H. Guss, A. Nichol, A. Paino, N. Tezak, J. Tang, I. Babuschkin, S. Balaji, S. Jain, W. Saunders, C. Hesse, A. N. Carr, J. Leike, J. Achiam, V. Misra, E. Morikawa, A. Radford, M. Knight, M. Brundage, M. Murati, K. Mayer, P. Welinder, B. McGrew, D. Amodei, S. McCandlish, I. Sutskever, and W. Zaremba, "Evaluating large language models trained on code," 2021. [Online]. Available: https://arxiv.org/abs/2107.03374

- [7] Y. Kwon, K. Vladimir, N. Kim, W. Shin, J. Won, M. Lee, H. Joo, H. Choi, G. Kim, B. An, J. Kim, J. Lee, I. Kim, J. Park, C. Park, Y. Song, B. Yang, H. Lee, S. Kim, D. Kwon, S. Lee, K. Kim, S. Oh, J. Park, G. Hong, D. Ka, K. Hwang, J. Park, K. Kang, J. Kim, J. Jeon, M. Lee, M. Shin, M. Shin, J. Cha, C. Jung, K. Chang, C. Jeong, E. Lim, I. Park, J. Chun, and S. Hynix, "System architecture and software stack for gddr6-aim," in 2022 IEEE Hot Chips 34 Symposium (HCS), 2022, pp. 1–25.

- [8] UPMEM, "Upmem: Processing-in-memory (pim) solutions," https:// www.upmem.com/.

- [9] W. Kwon, Z. Li, S. Zhuang, Y. Sheng, L. Zheng, C. H. Yu, J. Gonzalez, H. Zhang, and I. Stoica, "Efficient memory management for large language model serving with pagedattention," in *Proceedings of the* 29th Symposium on Operating Systems Principles, ser. SOSP '23. New York, NY, USA: Association for Computing Machinery, 2023, p. 611–626. [Online]. Available: https://doi.org/10.1145/3600006.3613165

- [10] A. Bambhaniya, R. Raj, G. Jeong, S. Kundu, S. Srinivasan, M. Elavazhagan, M. Kumar, and T. Krishna, "Demystifying platform requirements for diverse llm inference use cases," 2024. [Online]. Available: https://arxiv.org/abs/2406.01698

- [11] H. Zhang, A. Ning, R. Prabhakar, and D. Wentzlaff, "A hardware evaluation framework for large language model inference," 2023. [Online]. Available: https://arxiv.org/abs/2312.03134

- [12] A. Vaswani, N. Shazeer, N. Parmar, J. Uszkoreit, L. Jones, A. N. Gomez, L. Kaiser, and I. Polosukhin, "Attention is all you need," in *Proceedings* of the 31st International Conference on Neural Information Processing Systems, ser. NIPS'17. Red Hook, NY, USA: Curran Associates Inc., 2017, p. 6000–6010.

- [13] R. Pope, S. Douglas, A. Chowdhery, J. Devlin, J. Bradbury, A. Levskaya, J. Heek, K. Xiao, S. Agrawal, and J. Dean, "Efficiently scaling transformer inference," 2022. [Online]. Available: https://arxiv.org/abs/2211.05102

- [14] G.-I. Yu, J. S. Jeong, G.-W. Kim, S. Kim, and B.-G. Chun, "Orca: A distributed serving system for Transformer-Based generative models," in 16th USENIX Symposium on Operating Systems Design and Implementation (OSDI 22). Carlsbad, CA: USENIX Association, Jul. 2022, pp. 521–538. [Online]. Available: https://www.usenix.org/ conference/osdi22/presentation/yu

- [15] P. Patel, E. Choukse, C. Zhang, A. Shah, Íñigo Goiri, S. Maleki, and R. Bianchini, "Splitwise: Efficient generative Ilm inference using phase splitting," 2024. [Online]. Available: https://arxiv.org/abs/2311.18677

- [16] Y. Zhong, S. Liu, J. Chen, J. Hu, Y. Zhu, X. Liu, X. Jin, and H. Zhang, "Distserve: Disaggregating prefill and decoding for goodputoptimized large language model serving," 2024. [Online]. Available: https://arxiv.org/abs/2401.09670

- [17] B. Gao, Z. He, P. Sharma, Q. Kang, D. Jevdjic, J. Deng, X. Yang, Z. Yu, and P. Zuo, "Cost-Efficient large language model serving for multi-turn conversations with CachedAttention," in 2024 USENIX Annual Technical Conference (USENIX ATC 24). Santa Clara, CA: USENIX Association, Jul. 2024, pp. 111–126. [Online]. Available: https://www.usenix.org/conference/atc24/presentation/gao-bin-cost

- [18] C. Hu, H. Huang, J. Hu, J. Xu, X. Chen, T. Xie, C. Wang, S. Wang, Y. Bao, N. Sun, and Y. Shan, "Memserve: Context caching for disaggregated llm serving with elastic memory pool," 2024. [Online]. Available: https://arxiv.org/abs/2406.17565

- [19] A. Agrawal, N. Kedia, J. Mohan, A. Panwar, N. Kwatra, B. Gulavani, R. Ramjee, and A. Tumanov, "Vidur: A large-scale simulation framework for llm inference," in *Proceedings of Machine Learning and Systems*, P. Gibbons, G. Pekhimenko, and C. D. Sa, Eds., vol. 6, 2024, pp. 351–366

- [20] J. Cho, M. Kim, H. Choi, G. Heo, and J. Park, "Llmservingsim: A hw/sw co-simulation infrastructure for llm inference serving at scale," in 2024 IEEE International Symposium on Workload Characterization (IISWC), 2024, pp. 15–29.

- [21] K. G. Müller, T. Vignaux, O. Lünsdorf, and S. Scherfke, "Simpy: Discrete event simulation for python," https://simpy.readthedocs.io/, 2002, version 4.1.1, released November 12, 2023.

- [22] H. Touvron, T. Lavril, G. Izacard, X. Martinet, M.-A. Lachaux, T. Lacroix, B. Rozière, N. Goyal, E. Hambro, F. Azhar, A. Rodriguez, A. Joulin, E. Grave, and G. Lample, "Llama: Open and efficient foundation language models," 2023. [Online]. Available: https://arxiv.org/abs/2302.13971

- [23] H. Touvron, L. Martin, K. Stone, P. Albert, A. Almahairi, Y. Babaei, N. Bashlykov, S. Batra, P. Bhargava, S. Bhosale, D. Bikel, L. Blecher, C. C. Ferrer, M. Chen, G. Cucurull, D. Esiobu, J. Fernandes, J. Fu, W. Fu, B. Fuller, C. Gao, V. Goswami, N. Goyal, A. Hartshorn, S. Hosseini, R. Hou, H. Inan, M. Kardas, V. Kerkez, M. Khabsa, I. Kloumann, A. Korenev, P. S. Koura, M.-A. Lachaux, T. Lavril, J. Lee, D. Liskovich, Y. Lu, Y. Mao, X. Martinet, T. Mihaylov, P. Mishra, I. Molybog, Y. Nie, A. Poulton, J. Reizenstein, R. Rungta, K. Saladi, A. Schelten, R. Silva, E. M. Smith, R. Subramanian, X. E. Tan, B. Tang, R. Taylor, A. Williams, J. X. Kuan, P. Xu, Z. Yan, I. Zarov, Y. Zhang, A. Fan, M. Kambadur, S. Narang, A. Rodriguez, R. Stojnic, S. Edunov, and T. Scialom, "Llama 2: Open foundation and fine-tuned chat models," 2023. [Online]. Available: https://arxiv.org/abs/2307.09288

- [24] ShareGPT Team, "Sharegpt," https://www.sharegpt.com/, 2023.