# **Reciprocating Locks**

Dave Dice 回

dave.dice@oracle.com Oracle Labs USA

# Abstract

We present **Reciprocating Locks**, a novel mutual exclusion locking algorithm, targeting cache-coherent shared memory (CC), that enjoys a number of desirable properties. The doorway arrival phase and the Release operation both run in constant-time. Waiting threads use local spinning and only a single *waiting element* is required per thread, regardless of the number of locks a thread might hold at a given time. While our lock does not provide strict FIFO admission, it bounds bypass and has strong anti-starvation properties. The lock is compact, space efficient, and has been intentionally designed to be readily usable in real-world general purpose computing environments such as the linux kernel, pthreads, or C++. We show the lock exhibits high throughput under contention and low latency in the uncontended case. The performance of Reciprocating Locks is competitive with and often better than the best state-of-the-art scalable spin locks.

**CCS Concepts:** • Software and its engineering  $\rightarrow$  Multithreading; Mutual exclusion; Concurrency control; Process synchronization.

*Keywords:* Synchronization; Locks; Mutual Exclusion; Mutex; Scalability; Cache-coherent Shared Memory

# 1 Introduction

Locks often have a crucial impact on the performance of parallel software, hence they remain in the focus of intensive research with a steady stream of algorithms proposed over the last several decades.

# 2 The Reciprocating Lock Algorithm

Briefly, under contention, Reciprocating Locks partitions the set of waiting threads into two disjoints lists, which we call the *arrival* and *entry* segments. Threads arriving to acquire the lock will push (prepend) themselves onto a stack, using an atomic exchange operation, forming the *arrival*

PPoPP'25, , © 2025 ACM. https://doi.org/10.1145/3710848.3710862 Alex Kogan 💿

alex.kogan@oracle.com Oracle Labs USA

*segment*. When the owner releases the lock, it first tries to pass ownership to any threads found in the *entry segment*. Otherwise, if the entry segment is found empty, the thread then uses a atomic exchange to detach the entire current arrival segment (setting it empty), which then becomes the next entry segment, and then passes ownership to the first element of the entry segment.

In Reciprocating Locks, a lock instance consists of an *ar-rival* word. We deem the lock held if the arrival word is non-zero. Specifically, a value of 0 (nullptr) encodes the *unlocked* state, 1 encodes the state of *simple locked* – locked with an empty arrival segment – and other values encode being locked, where the remainder of the arrival word points to a stack of threads that have recently arrived at the lock and are waiting for admission, forming the arrival segment.

Threads arriving to acquire the lock use an atomic swap (exchange) operator to install the address of a thread-private waiting element into the arrival word. If the return value from the atomic exchange was nullptr then the arriving thread managed to acquire the lock without contention and can immediately enter the critical section. Otherwise, our thread has encountered contention and must wait. By virtue of the atomic exchange, the thread has managed to push its waiting element onto the arrival segment. The non-nullptr value returned from the atomic exchange identifies the next thread in the stack. Similar to the HemLock[20] and CLH[13, 33] lock algorithms, a thread knows only the identity of its immediate neighbor in the arrival segment, and unlike MCS, no explicit linked list of waiting threads is formed or required <sup>1</sup>. That is, the arrival stack is implicit with no next pointer fields in the waiting elements. Our thread then proceeds to local spinning on a flag field within its waiting element. This flag will eventually be set during normal ownership succession by some thread running in the Release operation, passing ownership to our waiting thread. Our thread, still executing in Acquire and now the owner, arranges to convey the address of the next thread in the entry segment, which was obtained from the atomic exchange, to the subsequent corresponding Release operation. The thread identified by that address will subsequently serve as the successor to our current thread. Our thread finally enters the critical section.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

<sup>&</sup>lt;sup>1</sup>Regarding terminology, say thread *A* arrives and pushes itself onto the stack and then *B* follows. In terms of arrival, *B* is *A*'s *predecessor*. But in terms of subsequent admission order, in Reciprocating Locks, *B* is *A*'s *successor*. There is no such situational distinction between arrival and admission for FIFO

In the corresponding Release operator, if a successor was passed from the corresponding Acquire operator, we simply enable that thread to enter the critical section by setting the flag in its waiting element. Otherwise, we attempt to use an atomic compare\_and\_exchange (CAS) operation to swing the arrival word from *simple locked* state, encoded as 1, back to *unlocked*, encoded as nullptr. If the CAS was successful then no waiting threads exist and the lock reverts to *unlocked* state. If the CAS failed, however, additional newly arrived threads must be present on the arrival segment. In that case we employ an atomic exchange to detach the entire arrival segment, leaving the arrival word in *simple locked* state, encoded as 1. We then pass lock ownership to the first thread in the detached segment by setting the flag in its waiting element.

Crucially, under contention, threads arrive and join the arrival segment. While the entry segment remains populated, ownership is passed through the entry segment elements in turn. When the current entry segment becomes empty, the Release operator detaches the arrival segment, (via an atomic exchange) which then becomes the next entry segment. Threads migrate, in groups, from the arrival segment to the entry segment. The arrival segment consists of those newly arrived threads currently pushed onto the stack anchored at the arrival word while entry segment reflects a set of threads that have already been detached from the arrival stack.

The Release operator consults the entry segment first – via the successor reference passed from Acquire to Release – and passes ownership to the successor if possible. The sequence of successor references passed from Acquire to Release constitutes the entry segment. But if the entry segment is empty – the passed successor argument is nullptr – Release then attempts to replenish the entry segment by detaching the arrival segment, and transferring ownership to the first element. In the event the arrival segment is found empty, the lock reverts to *unlocked* state.

The arrival segment is implemented by means of a concurrent *pop-stack*[8], where the key primitives are *push* and *detach-all*, which makes our technique immune to the *A-B-A* pathology [42]. By convention, in Reciprocating Locks, only the current lock holder is allowed to detach the arrival segment.

The waiting element is similar to the CLH or MCS "queue node". In our implementation, we opt to place a thread's wait element in thread-local storage (TLS). As a thread can wait on at most one lock at any given time, such a singleton suffices, and tightly bounds memory usage.

Given that we form a stack for arriving threads, admission order is LIFO within a segment, but remains FIFO between segments. As such, if thread T1 pushes itself onto the arrival segment in Acquire, and then waits, and T2 arrives and pushes itself after T1, then a given thread T2 can bypass or overtake T1 at most once before T1 is next granted ownership, providing *thread-specific bounded bypass* and thus avoiding indefinite starvation. Alternatively, we could say Reciprocating Locks provides classic *K*-bounded bypass (worst case) where *K* reflects the cardinality of the population of threads that might compete for the lock, yielding *population bounded bypass*.

### 3 Implementation Details

```

1 struct WaitingElement {

2

std::atomic<int> Gate {0} ;

std::atomic<WaitingElement *> Terminus {nullptr} ;

3

4 } ;

5

// Encoding for Lock.Arrivals :

6 // 0:0 = Unlocked

// 0:1 = Locked with empty arrival list : SIMPLELOCKED

7

// T:0 = Locked with populated arrival list where T is the

8

9

most recently arrived thread on the arrival stack

10 //

11 // Use Lock.Succ to pass identity of successor on entry segment

12 // from Acquire to corresponding Release.

13 // Succ is accessed only by the owner so protected by the lock

14 // itself and not required to be atomic<>

15 struct Lock {

std::atomic <WaitingElement *> Arrivals {nullptr} ;

16

17

WaitingElement * Succ = nullptr ;

18 } ;

19 static auto const SIMPLELOCKED = (WaitingElement *) uintptr_t(1) ;

void Acquire (Lock * L) {

20

21

static thread_local WaitingElement E {} ;

22

E.Terminus.store (nullptr , std::memory_order_release) ;

23

E.Gate.store (0

, std::memory_order_release) ;

24

auto tail = L→Arrivals.exchange (&E) ;

25

26

assert (tail \neq &E);

27

if (tail == nullptr) {

28

fast-path uncontended acquire -- We now hold the lock

29

// Trv to replace &E with SIMPLELOCKED.

assert (L \rightarrow Succ == nullptr) :

30

31

auto R = L→Arrivals.exchange (SIMPLELOCKED) ;

32

assert (R ≠ nullptr) ;

if (R == &E) return;

33

34

35

// Other threads arrived and pushed onto L \rightarrow Arrivals in

// the Exchange-Exchange window, above.

36

37

// Our &E is now buried at distal end of arrival stack

38

// The exchange() above snapped off a new entry segment,

39

// which is anchored at "R"

40

R \rightarrow Terminus.store (&E, std::memory_order_release) ;

L \rightarrow Succ = R:

41

return ;

42

43

}

44

// Coerce SIMPLELOCKED to nullptr

45

46

// succ will be our successor when we subsequently release

auto succ = (WaitingElement *) (uintptr_t(tail) & ~1) ;

47

48

assert (succ \neq &E);

49

slow path : contention -- waiting phase

50

51

while (E.Gate.load() == 0) Pause() ;

52

// Determine if succession has reached the end of the entry list

53

// segment by checking for marker address.

// E.Terminus == succ implies E is logical terminal WaitingElement.

54

55

assert (L→Succ == nullptr) ;

56

auto eos = E.Terminus.load() ; // end-of-segment address

57

58

assert (eos ≠ &E)

59

if (succ == eos) return ;

60

// Propagate end-of-segment value through the detached entry list

61

62

// pass successor reference to corresponding Release()

63

assert (succ ≠ nullptr && succ→Terminus == nullptr);

64

\texttt{succ} \rightarrow \texttt{Terminus.store} (eos, <code>std::memory_order_release)</code> ;

65

L \rightarrow Succ = succ ;

66

```

```

67

void Release (Lock * L) {

assert (L→Arrivals.load() ≠ nullptr) ;

68

69

// Case : entry list populated -- appoint successor from entry list

70

auto succ = L→Succ ;

71

if (succ ≠ nullptr) {

L→Succ = nullptr

72

// reset

73

74

succ→Gate.store (1, std::memory_order_release) ;

75

return ;

76

77

// Case : entry list and arrivals are both empty

78

// try fast-path uncontended unloc

79

auto v = L→Arrivals.cas (SIMPLELOCKED, nullptr) ;

80

if (v == SIMPLELOCKED) return ;

81

assert (v ≠ nullptr) ;

82

83

84

// Case : entry list is empty and arrivals is populated

// New threads have arrived and pushed themselves onto the

85

arrival stack

86

87

// We now detach that segment, shifting those arrivals to

// become the next entry segmen

88

auto w = L\rightarrowArrivals.exchange (SIMPLELOCKED) ;

89

assert (w ≠ nullptr && w ≠ SIMPLELOCKED)

90

w→Gate.store (1, std::memory_order_release) ;

91

92

```

Listing 1. Reciprocating Lock Algorithm

In Listing-1 we show an implementation of Reciprocating Locks in modern C++. To further explain the operation of Reciprocating Locks we next annotate key scenarios, showing Reciprocating Locks in action.

Our implementation uses conservatively over-fenced C++ std::atomic loads and stores for the sake clarity and brevity of explication, even though weaker memory order constraints would suffice and potentially yield better performance. We also assume the existence of a "polite" Pause() operator for busy-waiting, and a strong cas operator that returns the previous value, which can be trivially implemented via std::atomic<>::compare\_exchange\_strong with default std::memory\_order\_seq\_cst memory ordering. For encoding the arrival word, we assume that low-order bit of wait element addresses are 0. We further assume the existence of a wait-free atomic exchange operator. Specifically, the implementation thereof should not be via loops that employ optimistic compare-and-swap or load-locked(LL) and store--conditional(SC) primitives. In particular we assume that C++ atomic<> exchange and compare\_and\_exchange primitives are implemented in a wait-free fashion, as is the case on AMD or Intel x86 processors or ARM processors that support the LSE instruction subset.

▶ Uncontended Simple uncontended Acquire and Release : ● Thread T1 arrives at Line-20 to acquire lock *L*. *L*'s arrival word is currently nullptr, indicating that *L* is in *unlocked* state. ● At Line-22 and -23, T1 initializes its thread-specific waiting element, *E*. T1 then swaps the address of *E* into *L*1's arrival word in Line-25. The atomic exchange returns nullptr, so control enters the "if" block at Line-28. ● At Line-28, T1, recognizing there was no contention, tries to replace the address of *E* in the arrival word with the *simple locked* encoding of 1. As no other threads have arrived, the exchange replaces *E* with 1. ● Control returns at Line-33 and the thread can enter and execute the critical section. Acquire returns with  $L \rightarrow$ Succ remaining set to nullptr indicating that the entry list is empty and no successor exists. **③** *T*1 invokes Release at Line-67, with  $L \rightarrow$ Succ still set to nullptr. (We can think of Acquire passing the identity of the entry segment successor, if any, to Release via the  $L \rightarrow$ Succ field. Release checks and resets  $L \rightarrow$ Succ). **④** Control reaches Line-80, where *T*1 uses an atomic CAS to try to restore *L*'s arrival field from 1 to 0, *unlocked*. As no new threads have arrived, the CAS is successful, and *T*1 returns from Release at Line-81.

An uncontended Acquire requires two atomic exchange operations, at Line-25 and Line-31, increasing the theoretical RMR complexity [4, 7]. In practice, however, as the lock is uncontended, the underlying cache line tends to remain in local *modified* state in T1's cache, assuming normal cache coherent shared memory, so the 2nd exchange incurs very little additional cost. Later, we show a variation, with slightly more complex encodings, that avoids this *double swap* arrival. We also observe that the double swap manifests only absent contention, where the arriving thread found the lock in *unlocked* state. Under sustained contention, we avoid the double swap.

► Onset of contention In this scenario we show how to recover from a race in Acquire where a thread pushes its wait element onto the stack but, because of other arriving threads, is not able to exchange the arrival word back to 1, and its element becomes "submerged" on the arrival stack. We tolerate this situation by conveying the address of that submerged element through the segment, during succession, allowing us to treat the buried element as the effective endof-segment (equivalent to nullptr) and otherwise ignore it. We convey that address through the wait element Terminus field, which is normally nullptr but will be non-nullptr in the case where the race manifested and an element became submerged. In this case we say we have a zombie terminal element. During succession a thread checks the address of the successor to determine if matches the submerged terminal element.

• Lock *L* is in *unlocked* state and thread *T*1 invokes Acquire on *L* at Line-20. • *T*1 executes the atomic exchange at Line-25 to install the address of its wait element *E*, which we will designate *E*1, into *L*'s arrival word, the exchange returns 0, so *T*1 now holds the lock. • Thread *T*2 now arrives in Acquire and exchanges the address of its wait element, *E*2 into the lock's arrival word, at Line-25. • Thread *T*3 also arrives in Acquire and pushes the address of its wait element, *E*3, onto the arrival stack. • At Line-31, *T*1 attempts to replace the address of its *E*1 with 1, the *simple locked* encoding. The exchange, however, returns *E*3 instead of *E*1, as *T*2 and *T*3 raced *T*1 in the exchange-exchange window (Lines 25 through 31). *T*1 is unable to return at Line-33. At this point, *T*1's wait element *E*1 is "buried" or "submerged" in the arrival stack, residing at the distal end, and is not easily removed from the stack. The arrival word is 1. E3's successor is E2, E2's successor is E1, and E1 has no successor, forming an entry segment that consists of  $E3 \rightarrow E2 \rightarrow E1$ . Note that *T*1 is the owner, but its own E1 also resides on the entry segment stack. 6 To recover, *T*1 installs the address of its own *E*1 into its successor *E3*'s Terminus field at Line-40, which is otherwise set to nullptr by virtue of Line-22. T1 records the address E3 (in variable R) at Line-41, to ultimately be used as T1's successor when T1 subsequently calls Release.

T1 enters and executes the critical section. (8) T2 and T3, resuming at Line-27, observe that the lock was held and must thus wait, at Line-51. **9** *T*1 invokes Release on *L*. The address *E*3 is passed through the L $\rightarrow$ Succ field. 10 *T*1 at Line-74 sets the Gate flag in E3, passing ownership to T3. 1 returns from Release at Line-75. 12 T3 is now the owner and departs its waiting loop at Line-51, and fetches its Terminus field from E3 at Line-57, observing the address E1. T3's local successor variable (succ) refers to E2, so the equality check at Line-59 is not true. **13** *T*3, at Line-64, passes the address *E*1, which represents the logical end-of-segment, into E2's Terminus field. 1 T3, at Line-65, stores E2, which is passed to the corresponding Release. 15 T3, returns and executes the critical section. **16** T3 invokes Release, and observes E2 in L $\rightarrow$ Succ. T 3 at Line-74, sets E2's Gate field, passing ownership to T2. 18 T3 returns from Release at Line-75. 19 T2 at Line-51 observes that its Gate field was set, indicating that is now the owner of *L*. 20 *T*2's local succ variable refers to *E*1. *T*2 fetches from its own E2 Terminus field, observing E1. T2, at Line-59, recognizes, via the address-based check, that it has reached the end of the arrival segment, marked by E1, and returns. 21 T2 returns from Acquire at Line-59 and enters the critical section. 22 T2 invokes Release, and observes that  $L \rightarrow$  Succ is equal to nullptr, indicating the entry segment is empty. 23 T2 at Line-80, attempts to CAS the arrival work from 1 to 0. The CAS succeeds and L is restored to unlocked state and T2 returns at Line-81. We note that if new threads had arrived and pushed onto the arrival segment, the CAS would fail, and the Release operator would detach the arrival stack at Line-89, shifting those arrivals to become the next entry segment, and then pass ownership to the most recently arrived element of the entry segment at Line-91.

In practice we find the arrival race between Lines 25 and 31 (the two swaps) to be rare, likely as the window of vulnerability is short, and because it takes time for the coherent interconnect to re-arbitrate the cache line between processors. Also, the race can only occur at the *onset* of contention, when the first arriving thread found the lock not held and then other threads arrived in quick succession. In the event of the race, at Line-40, we pass the address of *E* through the Terminus field. We are using *E*'s address for addressed-based comparisons (Line-59) as a distinguished marker or sentinel to indicate the logical end-of-segment. *E* itself, however, will

not be subsequently accessed by succession within the segment. We note that elements associated with a given thread can appear on at most one segment at any time, but, when an address is used as an end-of-segment marker, it is possible that it appears on both the arrival segment and entry segment.

We observe that the Terminus field could also reside in the lock body instead of in the waiting elements. While viable, that approach increases the size of the lock body, and increases induced coherence traffic. Instead, we borrow a technique from Compact NUMA-Aware Locks (CNA) [17] and avoid such shared central fields by propagating information – in this case the address of the terminal element of the segment – through the chain of waiting elements.

► Sustained contention ① Lock *L* is initially in *unlocked* state. Thread T1 arrives in Acquire at Line-20. @ T1's exchange operation at Line-25 installs the address of T1's wait element, E1, into L's arrival word. As the exchange returned nullptr, T1 has acquired the lock. T1 then, via the exchange at Line-31, replaces *E*1 with 1 and returns at Line-33. **3** *T*1 enters and executes the critical section. **4** While *T*1 holds L, thread T2 arrives E2 pushes onto the arrival stack. The exchange operation at Line-25 returns 1 into T2's local tail variable. As tail is non-0, T2 must wait and control passes through Line-47, which coerces the value 1 to nullptr, as there are no successors in the arrival segment. We interpret 1 (simple locked) as effectively equivalent to nullptr for the purposes of forming the arrival segment. T2 waits on *E*2 at Line-51. **6** With *T*1 still holding *L*, *T*3 also arrives and uses the atomic exchange to push its element E3 onto the arrival stack. The exchange returns E2 and Line-47 leaves E2 unchanged. T3's succ variable points to E2. The arrival stack consists of E3 followed by E2. The arrival word points to E3 and T3's succ variable points to E2, while E2's succ variable is nullptr, indicating that E2 is the final element on the arrival segment. The entry segment is empty. T3 waits on E3 at Line-51. 6 Similarly, T4 arrives and pushes E4 onto the arrival stack and then waits. **7** T eventually calls Release. As  $L \rightarrow$  Succ is nullptr, indicating an empty entry segment, T1 then attempts the CAS, at Line-80, which fails. T1 then executes exchange(1) to detach the arrival segment at Line-89. The exchange operator returns E4. The arrival segment is now empty and the entry segment consists of E4 then E3 then E2. T1 passes ownership to T4 at Line-91. **③** *T*4 departs its waiting phase at Line-51. The Terminus value is nullptr and does not equal succ, which is *E*3, so control passes through Line-64, which performs a redundant but benign store of 0 over 0. T4 sets E3 as its successor at Line-65, returns, and then enters the critical section. The arrival segment is currently empty and the entry segment consists of just *E*3 and *E*2. while *T*3 holds *L*, *T*5 and then T6 arrive to acquire L, pushing E5 and then E6, respectively, onto the arrival stack. The arrival segment consists of E6

then E5 and the detached entry segment is just E3 and E2. 10 T4 calls Release. As E3 is the successor, and we grant ownership to T3 at Line-74. 11 T3 departs its wait phase at Line-51 and marks E2 as its successor at Line-65. 12 T3 enters and executes the critical section. 13 T3 calls Release, observing E2 as its successor and grants ownership to T2 at Line-74. M T2 departs its wait phase at line-51. We have reached the end of the entry segment. That is, the entry segment is exhausted. As  $L \rightarrow Succ$  is already known to be nullptr, we just return at Line-59. 15 T2 enters and executes the critical section. 16 T2 invokes Release observing  $L \rightarrow$  Succ==nullptr. As the entry segment is now empty and there is no immediate successor, we bypass the block at Lines 73-77 and then attempt the CAS at Line-80, which fails, as the arrival segment is populated. T2 then detaches the arrival segment of E6 then E5 at Line-89, leaving the arrival word set to 1, and passes ownership to T6 at Line-91. 17 T6 exits its waiting loop at Line-51, marks E5 as its successor and returns. B T6 enters and executes the critical section. 19 T6 invokes Release observing L $\rightarrow$ Succ==E5. We clear  $L \rightarrow$  Succ and we grant ownership to *T*5 at Line-74. 20 *T*5 exits its waiting loop at Line-51 and returns with L→Succ still set to nullptr, indicating there is no successor in the entry segment. 21 *T*5 enters and executes the critical section. 22 T5 calls Release observing L $\rightarrow$ Succ==nullptr. Both the entry segment and arrival segment are empty. The CAS at Line-80 succeeds, and *L* is restored to *unlocked* state.

One possible disadvantage to Reciprocating Locks is that we might be required to access the central shared lock body more than, say, under MCS. MCS updates the lock's head pointer as threads arrive and use exchange to join the queue of waiting threads. But if contention is steady-state and sustained, all hand-over of ownership in the Release operations can be accomplished directly thread-to-thread without needing to access the lock body. In Reciprocating Locks, however, we need to periodically consult the arrival stack to replenish the entry segment, potentially increasing RMR (remote memory reference) complexity and generating additional coherence traffic. Interestingly, as more threads contend, Reciprocating Locks needs to detach the arrival segment less often, somewhat mitigating the concern.

# 4 Additional Requirements

We target lock algorithms that are suitable for environments such as the Linux kernel, as a replacement for the user-level pthreads\_mutex primitive, or for use in runtime environments such as the Java Virtual Machine (JVM), which is written in C++. As such, we identify additional de-facto requirements for general purpose lock algorithms.

**Safe Against Prompt Lock Destruction** Various lock algorithms perform stores in the Release operation that potentially release ownership, but then perform additional

accesses to fields in the lock body to ensure succession and progress. This can result in a class of unsafe use-after-free memory reference errors [11, 36]. A detailed description of such an error can be found in [20]. All algorithms for use in the linux kernel or in the pthreads environment are expected to be prompt lock destruction safe.

**Support for Large Numbers of Extant Threads** The algorithms must support the simultaneous participation of an arbitrary number of threads, where threads are created and destroyed dynamically, and the peak number of extant threads is not known in advance.

**Support for Large Numbers of Extant Locks** Similarly, the algorithm needs to support large numbers of lock instances, which can be created and destroyed dynamically. Recent work [30] shows the Linux kernel has more than 6000 statically initialized lock instances. Again, the number of locks is not know in advance, as drivers load, and unload, for instance, or as data structures dynamically resize.

**Plural Locking** A given thread is expected to be able to lock and hold a large number of locks simultaneously. In the Linux kernel, for instance, situations arise when 40 or more distinct locks are held by a single thread at a given time, as evidenced by the MAX\_LOCK\_DEPTH tunable, which is used by the kernel's "lockdep" facility to track the set of locks held in an explicit per-thread list for the purposes of detecting potential deadlock. Furthermore, locks must be able to be released in non-LIFO imbalanced order as it is fairly common to acquire a lock in one routine, return, and then release the lock in the caller.

**Space Efficient** We expect the lock algorithm to be frugal and parsimonious with regard to space usage. Critically, any algorithms that require per-lock and per-thread storage – with *Threads* \* *Locks* space consumption – such as Anderson's Array-Based Queue Lock [6], are not suitable.

FIFO as a non-goal We also note that many real-world lock implementations, such as the current implementation of Java's "synchronized" in the HotSpot Java Virtual Machine, the java.util.Concurrent.ReentrantLock, and the default pthread\_mutex on Linux, are non-FIFO, and in fact permit unbounded bypass and indefinite starvation. Relatedly, Compact NUMA-Aware Locks (CNA) [17] intentionally imposes non-FIFO admission order to improve throughput on NUMA platforms, trading aggregate throughput against strict FIFO ordering. In fact, strict FIFO locking is an antipattern for common practical lock designs, as it suffers from reduced throughput compared to more relaxed admission schedules, and has shortcomings when used with waiting techniques that deschedule threads, or when involuntary preemption is in play [16, 19]. Forgoing strict FIFO admission schedules allows more opportunism that in some circumstances may translate into improved throughput.

Given these particular constraints, we exclude a number of algorithms from consideration. Dvir's algorithms [23], Rhee's algorithm [39], Lee's HL1 and HL2 [28, 29], and Javanati's "Ideal Queued Spinlock" [26] [27] algorithms, when simplified for use in cache-coherent (CC) environments, all have extremely simple and elegant paths and low RMR complexity, suggesting they would be competitive and good candidates, but they do not readily tolerate multiple locks being held simultaneously. The above tend to use so-called "nodetoggling" and "node-switching" techniques - also called "two-face" by Lee – that, while they work well when a thread holds at most one lock, are awkward for general purpose use. Our specific concerns are space blow-up due to the need to maintain toggle element pairs and a "face" index for pairs of locks and threads, in addition to the requirement that we re-associate that metadata with the lock instance at releasetime. Some of Dvir and Lee's algorithms are also not safe against prompt lock destruction.

# 5 Related Work

While mutual exclusion remains an active research topic [1-3, 13, 15-18, 22-27, 35, 38, 40?] we focus on locks closely related to our design.

Simple test-and-set or polite test-and-test-and-set [40] locks are compact and exhibit excellent latency for uncontended operations, but fail to scale and may allow unfairness and even indefinite starvation. Ticket Locks are compact and FIFO, and also have excellent latency for uncontended operations, but they also fail to scale because of global spinning, although some variations attempt to overcome this obstacle, at the cost of increased space [18, 37]. For instance, Anderson's array-based queueing lock [5, 6] is based on Ticket Locks but provides local spinning. It employs a waiting array for each lock instance, sized to ensure there is at least one array element for each potentially waiting thread, yielding a potentially large footprint. The maximum number of participating threads must be known in advance when initializing the lock. TWA[18] is a variation on ticket locks that reduces the incidence of global spinning.

Queue-based locks such as MCS or CLH are FIFO and provide local spinning and are thus more scalable. MCS is used in the linux kernel for the low-level "qspinlock" construct [10, 12, 31]. Modern extensions of MCS edit the queue order to make the lock *NUMA-Aware*[17]. MCS readily allows editing and re-ordering of the queue of waiting threads, [15, 17, 34] whereas editing the chain is more difficult under CLH, HemLock and Reciprocating Locks, where there are no explicit linked lists.

CLH is extremely simple, has excellent RMR complexity, and requires just an single atomic exchange operation in the Acquire operation and no atomic read-modify-write instructions in Release. Unfortunately the waiting elements migrate between threads, which may be inimical to performance in NUMA environments. CLH locks also require explicit constructors and destructors, which may be inconvenient <sup>2</sup> Our specific implementation uses a variation on Scott's [40] Figure 4.14, which converts the CLH lock to be *context free*[44], adhering to a simple programming interface that passes just the address of the lock, albeit at the cost of adding an extra field to the lock body to convey the address of the head waiting element to Release.

The K42 [32, 40] variation of MCS can recover the queue element before returning from Acquire whereas classic MCS recovers the queue element in Release. That is, under K42, a queue element is needed only while waiting but not while the lock is held, and as such, queue elements can always be allocated on stack, if desired. While appealing, the paths are much more complex and touch more cache lines than the classic version, impacting performance. In addition, neither the doorway nor the Release path operate in constant time.

HemLock combines aspects of both CLH and MCS to form a lock that has very simple waiting node lifecycle constraints, is context free but still scales well. HemLock does not provide constant remote memory reference (RMR) complexity [23]. Similar to MCS, HemLock lacks a completely constant-time unlock operation, whereas the unlock operator for CLH and Tickets is constant-time. Unlike MCS, HemLock requires active synchronous back-and-forth communication in the unlock path between the outgoing thread and its successor to protect the lifecycle of the waiting element. We note, however, that HemLock remains constant-time in the Release operator to the point where ownership is conveyed to the successor. HemLock uses address-based transfer of ownership, writing the address of the lock instead of a boolean, differentiating it from MCS and CLH. Reciprocating Locks, like HemLock, requires just a singleton per-thread waiting element allocated in thread-local storage.

For both HemLock and Reciprocating Locks, the amount of memory required for locking is T \* W + L \* B where T is the number of extant threads, W is the size of the waiting element in thread-local storage, L is the number of currently extant locks, and B is the size of the lock body.

We opted to exclude NUMA-aware locks such as Cohort Locks [21, 22] and Compact NUMA-Aware Locks (CNA) [17] from consideration. We excluded Fissile Locks and GCR[16]

<sup>&</sup>lt;sup>2</sup>Many lock implementations require just trival constructors to set the lock fields to 0 or some constant, and trivial destructors, which do nothing. The Linux kernel spinlock\_t/qspinlock\_t interface provides a constructor, but does not even expose a destructor. Similarly, C++ std: :mutex is allowed to be *trivially destructable*, meaning storage occupied by trivially destructible objects may be reused without calling the destructor. Under both GCC g++ version 13 and Clang++ Version 18, is\_trivially\_destructible reports True for std::mutex, and as such, destructors do not run. This situation could be rectified by recompiling, but we would also need to recompile all libraries transitively depended on by the application, included those deployed in shared libraries in binary-only form on the system.

|                                   | Lock Algorithm |       |         |        |       |               |

|-----------------------------------|----------------|-------|---------|--------|-------|---------------|

| Property                          | MCS            | CLH   | HemLock | Ticket | TWA   | Reciprocating |

| Spinning                          | Local          | Local | Semi    | Global | Semi  | Local         |

| Constant-time Release             | No             |       | No      |        |       |               |

| Context-free                      | No             | No    |         |        |       | No            |

| FIFO                              |                |       |         |        |       | No            |

| Complexity – Acquire              | 29             | 19    | 22      | 12     | 57    | 42            |

| Complexity – Release              | 17             | 4     | 21      | 5      | 11    | 20            |

| On-Stack                          | No             | No    | No      | N/A    | N/A   |               |

| Nodes Circulate                   |                | Yes   |         | N/A    | N/A   |               |

| Explicit CTOR/DTOR Required       |                | Yes   |         |        |       |               |

| Maximum Remote Misses per episode | 3              | 4     | 4       | Т      | T * 2 | 2             |

| Invalidations per episode         | 6              | 5     | 5       | 8.5(T) | 10(T) | 4             |

Table 1. Comparison of lock algorithm properties

as they have lax time-based anti-starvation mechanism. Fissile, specifically, depends on the owner of the *inner lock* to make progress to monitor for starvation. We also excluded MCSH[25] which is a recent variation of MCS that uses onstack allocation of queue nodes and hence supports a standard locking interface. Like MCS, the lock is not innately context free, and additional information needs to be passed from Acquire to Release via extra fields in the lock body. In our experiments, the performance of MCSH is typically lower than MCS proper, concurring with the results in the original paper. Broadly, we also restrict our comparison to locks that use *direct succession* and hand off ownership directly from the owner to a specific successor.

In Table-1 we compare the attributes of various local algorithms. Note that all the locks provide a constant-time doorway phase. For readability, the table contains only noteworthy or problematic attributes.

Local Spinning: reflects whether the lock utilizes local, global or semi-local[20] spinning. Constant-time Unlock: indicates if the lock Release operation is bounded. Hem-Lock is lock-free up point where the lock is either released or transferred to a successor, but the Release operator, for reasons of memory safety, then waits for the successor to acknowledge transfer of ownership before the memory underlying the queue element can be potentially reused. Specifically, in HemLock an uncontended Release operation is constant-time and a contended Release is constant-time up to and including the point where ownership is conveyed to the successor. FIFO: does the lock provide strict FCFS admission. Context-free: indicates additional information does not need to be transferred from the lock operator to the corresponding Release operation. Complexity - Acquire and Complexity - Release : we measured the size of the Acquire and Release methods in units of platform independent LLVM intermediate representation (IR) instructions, as

emitted by clang++-18, which serves as a simple measure for path complexity. We note that much of the complexity found in TWA manifests through the use of the hash function which maps lock address and ticket value pairs to slots in the waiting array. On-Stack: indicates the queue elements, if any, may be allocated on-stack. This also implies the nodes do not migrate and have a tenure constrained to the duration of the locking episode. Nodes Circulate: queue elements migrate between threads. This often implies the need for an explicit queue element lifecycle management system and precludes convenient on-stack allocation of queue elements. Migration may also be unfriendly to performance in NUMA environments. Explicit CTOR/DTOR Required: indicates the lock requires non-trivial constructors or destructors. CLH, for instance, requires destructors to run to release the wait elements referenced in the lock, to avoid memory leaks. Maximum Remote Misses per episode: is the worst-case maximum number of misses to remote memory incurred, under simple sustained contention, by a matching Acquire-Release pair. Misses to remote memory may be more expensive than local misses on various platforms, such as modern Intel systems that use the UPI coherence fabric [14], where miss requests are first adjudicated by the *home node* of the cache line. Algorithms where nodes circulate appear more vulnerable to accumulating such remote misses. We note that under more complex contention scenarios, such as *multi-waiting*[?], HemLock devolves to unbounded RMR complexity. Invalidations per episode: is the number coherence misses, under sustained contention, induced by an Acquire-Release episode in a given thread. Using the ARMv8 system, we modifed the MutexBench microbenchmark to have a degenerate critical section that advanced only a local random number generator and to pass any context from Acquire to Release via thread-local storage, in order to reduce mutation of shared memory. Absent

coherence misses, an Acquire-Release episode, including the critical section, manages to remain completely resident in the private L1 data cache. As such, any misses are coherence misses. This technique yields a useful empirical metric on how much coherence traffic various lock algorithms generate. We used the ARM 12d\_cache\_inval hardware performance counter, which tallies L2 cache invalidation events, as simple proxy for coherence traffic - latency and bandwith. We report the number of 12d\_cache\_inval events per episode. As can be seen, Reciprocating Locks is parsimonious and incurs just 4 invalidations per episode, while CLH requires 5. Ticket locks require T (10 in our case) invalidations per episode, where T is the number of participating threads, given the global spinning. The number of misses incurred by CLH, MCS, HemLock and Reciprocating Locks is constant and not a function of the number of threads. These empiricallyderived results align closely with a static analysis of the code and the expected number of coherence misses in the Acquire and Release paths. We also observed in passing, while examining data from hardware performance counters, that CLH and MCS suffered from more stalls (both event counts and duration) from misses than did Reciprocating locks. CLH in particular executes a dependent load in the critical path in the arrival doorway on the address returned from the atomic exchange. The address to be loaded from is not known until after the exchange returns, denying the processor the ability to speculate or execute out-of-order.

#### **Empirical Performance Results** 6

All data was collected on a system having 2 sockets, each populated with an Intel Xeon E5-2699 v3 CPU running at 2.30GHz. Each socket has 18 cores, and each core is 2-way hyperthreaded, yielding 72 logical CPUs in total. The system was running Ubuntu 20.04 with a stock Linux version 5.4 kernel, and all software was compiled using the provided GCC version 9.3 toolchain at optimization level "-O3". 64bit C or C++ code was used for all experiments. Factoryprovided system defaults were used in all cases, and Turbo mode [43] was left enabled. In all cases default free-range unbound threads were used, with no pinning of threads to processors.

We implemented all user-mode locks within LD\_PRELOAD interposition libraries that expose the standard POSIX pthread\_ mutex\_t programming interface using the framework from [22]. This allows us to change lock implementations by varying the LD\_PRELOAD environment variable and without modifying the application code that uses locks. The C++ std::mutex construct happens to map directly to pthread\_mutex texBench on an ARMv8 (aarch64) system, showing that primitives, so interposition works for both C and C++ code. All lock busy-wait loops used the Intel PAUSE instruction. To reduce false sharing, all waiting elements were aligned

and sequestered at 128-byte boundaries, and, for the "MutexBench" benchmarks, below, the lock instances where similarly sequestered.

#### 6.1 MutexBench benchmark

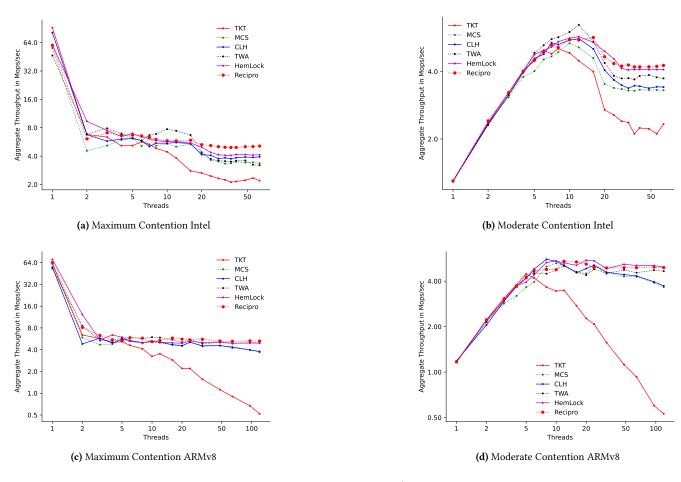

The MutexBench benchmark spawns *T* concurrent threads. Each thread loops as follows: acquire a central lock L; execute a critical section; release L; execute a non-critical section. At the end of a 10 second measurement interval the benchmark reports the total number of aggregate iterations completed by all the threads. We report the median of 7 independent runs in Figure-1a where the critical section advances a shared global std::mt19937 Mersenne Twister pseudo-random number generator (PRNG) one step, and the non-critical section is empty, subjecting the lock to extreme contention. (At just one thread, this configuration also constitutes a useful benchmark for uncontended latency). The X-axis reflects the number of concurrently executing threads contending for the lock, and the Y-axis reports aggregate throughput. For clarity and to convey the maximum amount of information to allow a comparison of the algorithms, the Y-axis is offset to the minimum score and the X-axis is logarithmic.

We ran the benchmark under the following lock algorithms: MCS is classic MCS. To avoid memory allocation during the measurement interval, the MCS implementation uses a thread-local stack of free queue elements. CLH is CLH based on Scott's CLH variant with a standard interface Figure-4.14 of [40]; For the MCS and CLH locks, our implementation stores the current head of the queue - the owner - in a field adjacent to the tail, so the lock body size was 2 words. CLH presents something of a challenge when used under the pthread\_mutex interface First, pthreads allows the programmer to use trivial initializers - setting the mutex body to all 0 and avoid calling pthread\_mutex\_init. To compensate, we modified pthread\_mutex\_lock to populate such an uninitialized lock with the CLH "dummy node" lazily, on-demand, on the first lock operation. In pthread\_mutex\_destroy we free the node, if populated, but many applications also do not call pthread\_mutex\_destroy, which constitutes a memory leak. As such, to allow CLH to be included, we avoided applications that create and then abandon large numbers of locks in a dynamic fashion. Ticket is a classic Ticket Lock; Hem-Lock is the HemLock algorithm, with the CTR (coherence traffic reduction) optimization.

The Ticket Lock has a size of 2 words, while HemLock requires a lock body of just 1 word. MCS and CLH additionally require one queue element for each lock held or waited upon.

In Figure-1c and Figure-1d, we show the results of Muthe relative performance of the various algorithms remains portable over disparate architectures. The ARMv8 system was an Ampere Altra Max NeoVerse-N1 with 128 processors

Figure 1. MutexBench

on a single socket and was running Ubuntu 24.04. We compiled all code using the -mno-outline-atomics -march=armv8. 2**nathlse**r generator. The non-critical section generates, using flags in order to allow direct use modern atomic exchange, CAS and fetch-and-add instructions instead of the legacy LL-SC (load-linked store-conditional) forms thereof. Each thread has a private std::mt19937 pseudo-random the private PRNG, a uniform random number in the range (0 - 250) and then advances its private PRNG that many steps. (We take care to make sure this operation can not be

In Figure-1a we make the following observations regarding operation at maximal contention with an empty critical section:

- At 1 thread the benchmark measures the latency of uncontended Acquire and Release operations. Ticket Locks are the fastest, followed closely by HemLock, Reciprocating Locks, CLH and MCS.

- As we increase the number of threads, Ticket Locks initially do well but then fade, exhibiting a precipitous drop in performance. TWA is the clear leader in the "middle" area of the graph, between 4 and 16 threads.

- Broadly, at higher thread counts, HemLock performs slightly better than or the same as CLH or MCS, while Reciprocating Locks provides the best throughput.

In Figure-1b we pass arguments to MutexBench that configure it to implement a delay in the non-critical section. Each thread has a private std::mt19937 pseudo-random mathlser generator. The non-critical section generates, using the private PRNG, a uniform random number in the range [0 - 250) and then advances its private PRNG that many steps. (We take care to make sure this operation can not be optimized away by consuming the PRNG value at the end of the thread's run). As above, the critical section advances the shared PRNG one step. As can be seen, we enjoy positive scalability up to about 5 threads. At higher thread counts, Reciprocating Locks manages to exhibit the least reduction in scalability.

#### 6.2 std::atomic

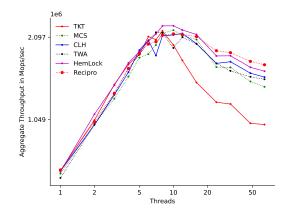

In Figure-2, our C++ atomic exchange benchmark defines a simple structure type SimpleTuple that contains 5 32-bit integers. Each thread declares a local SimpleTuple instance, and we also declare a shared global std::atomic<SimpleTuple> A {}. The C++ compiler and runtime implement std::atomic for such objects by hashing the address of the instance into an array of mutexes, and acquiring those as needed to implement the desired atomic action. Each thread loops for

Figure 2. C++ std::atomic<struct> exchange()

Figure 3. C++ std::atomic<struct> compare\_exchange\_strong()

10 seconds, using std::atomic<SimpleTuple>::exchange to swap its local copy with the shared global, and we then report aggregate throughput rate, in terms of completed exchange operations, at the end of the measurement interval. The figure depicts the median score of 7 runs and the overall ranking of the locks is similar to that observed under MutexBench.

Figure-3 is similar, but instead of std::atomic:exchange, we use std::atomic:load to fetch the shared global, make a local copy, increment the 1st of the five constituent integer fields in that copy, and then call std::atomic:compare\_ exchange\_strong (CAS) in an inner loop to try replace the global copy with the updated local version. The load operator acquires and releases all necessary covering locks, as does the compare\_exchange\_strong operator. If the CAS fails, we update our fresh local copy (returned from CAS) and retry. At the end of the 10 second measurement interval we report total number of successful CAS operations. The graph reports the median score of 7 runs. For both benchmarks, the relative ranks of the various lock algorithms remains similar to what was observed with MutexBench.

Figure 4. LevelDB : readrandom

#### 6.3 LevelDB

In Figure-4 we used the "readrandom" benchmark in LevelDB version 1.20 database <sup>3</sup> varying the number of threads and reporting throughput from the median of 5 runs of 50 seconds each. Each thread loops, generating random keys and then tries to read the associated value from the database. We first populated a database <sup>4</sup> and then collected data <sup>5</sup>. We made a slight modification to the db\_bench benchmarking harness to allow runs with a fixed duration that reported aggregate throughput. LevelDB uses coarse-grained locking, protecting the database with a single central mutex: DBImpl::Mutex. Profiling indicates contention on that lock via leveldb::DBImpl::Get().

# 7 Palindromic Admission Schedules

Reciprocating Locks may allow a *palindromic* admission schedule which, under the right circumstances, can persist for long periods.

### 7.1 Example Scenario

Table-2 illustrates the phenomena with a simple scenario. Threads  $A \ B \ C \ D$  and E all complete for a given lock L. Initially, at time 1, A is the owner, executing in the critical section, the entry segment is empty and the arrival segment consists of B then C then D then  $E \ (B + C + D + E)$ . The non-critical section is empty, so when a thread releases the lock, it immediately recirculates and tries to reacquire. A completes the critical section and invokes Release, which, as the entry segment is empty, reverts to and detaches the arrival segment of B + C + D + E and moves those threads enmasse to entry segment, and then passes ownership to the head of the entry segment, B. A recirculates, calls Acquire again, and emplaces itself on the arrival segment, reflecting

<sup>&</sup>lt;sup>3</sup>leveldb.org

<sup>&</sup>lt;sup>4</sup>db\_bench --threads=1 --benchmarks=fillseq --db=/tmp/db/

<sup>&</sup>lt;sup>5</sup>db bench –-threads=*threads* –-benchmarks=readrandom

<sup>--</sup>use existing db=1 --db=/tmp/db/ --duration=50

the state at time 2. Next, B releases the lock, and passes ownership to C. B then calls Acquire and prepends itself to the arrival segment stack, which now contains B + A, as shown at time 3. C releases the lock and conveys ownership to the head of the entry segment, D. C then recirculates and pushes itself onto the arrival segment, which now holds C + B + Aat time 4. D releases L, cedes ownership to the head of the entry segment, E and then recirculates, adding itself to the arrival segment, now containing D + C + B + A, at time 5. E calls Release and, as the entry segment is empty, E detaches the arrival segment of D + C + B + A, shifting those threads into the arrival segment, and then enables D. E recirculates and joins the arrival segment, leaving the configuration as seen at time 6. D releases the lock and passes ownership to *C* and *D* then joins the arrival segment, as shown at time 7. *C* releases *L* and conveys ownership to *B*, and then prepends itself to the arrival segment, leaving the state as shown at time 8. B releases L, enables A, and then joins the arrival segment, leaving the state as shown at time 9. The states at times 1 and 9 are identical, so the admission schedule repeats with a period length of 8 steps.

### 7.2 Long-term Admission Unfairness

While there is no long-term starvation, within the admission cycle ABCDEDCB we see that A and E are admitted just once while the others thread are admitted twice, which can manifest as long-term relative unfairness between the participating threads. While not a perfect palindrome, we say such a schedule is *palindromic* and note that the worst case admission fairness that might manifest is 2X.

| Time | Owner | Entry Segment | Arrival Segment |

|------|-------|---------------|-----------------|

| 1    | А     | -             | B+C+D+E         |

| 2    | В     | C+D+E         | А               |

| 3    | С     | D+E           | B+A             |

| 4    | D     | E             | C+B+A           |

| 5    | E     | -             | D+C+B+A         |

| 6    | D     | C+B+A         | E               |

| 7    | С     | B+A           | D+E             |

| 8    | В     | А             | C+D+E           |

| 9    | А     | -             | B+C+D+E         |

Table 2. Example of palindromic admission schedule

### 7.3 Throughput Benefits

We assume a simple system model where all threads circulating over a lock access the same shared last-level cache (LLC). While threads are waiting, their residency in the LLC undergoes exponential decay because of the actions of the other threads executing in the critical section or their respective non-critical sections. We consider a true repeating palindrome admission schedule, ABCDE - EDCBA, as compared to the FIFO schedule of ABCDE - ABCDE. Applying a simplistic decay model, when a thread ceases waiting and takes ownership of the lock, it incurs a "cache reload transient"[41] where it suffers a burst of cache misses as it reprovisions the LLC with its own previously displaced private data. The residual residency fraction can be approximated as  $Residual(T) = exp(-T * \lambda)$  where *T* is the sojourn or waiting time – the number of quanta since the thread last ran – and  $\lambda$  parameterizes the decay rate. As *Residual* is a convex function, we can employ Jensen's inequality [9] as follows. Taking thread *B* as a specific example, its waiting times under the FIFO schedule is always 4 time units and under the palindrome schedule the waiting time alternate 2-6-2-6 etc. The average waiting time is the same under both schedules, but the average residual LLC residency when the thread resumes is the same or better under the palindrome schedule as  $Residual(2) + Residual(6) \ge Residual(4) + Residual(4)$ . In fact, each and every thread will have the same or better residual fraction under the palindrome schedule than under FIFO.

Intuitively, as the decay process is exponential in nature, the retained residency benefits accrued by the relatively short gap outweigh the decay penalty of the subsequent longer gap found in the palindrome schedule.

The overall aggregate miss rate for the palindrome schedule, as computed over all the threads, will be less than that in the round-robin FIFO schedule, yielding better overall throughput. (Higher residency fractions implies reduced miss rates and better performance). Specifically, The palindrome schedule enjoys better overall aggregate LLC miss rates and throughput than a simple repeating round-robin FIFO schedule of ABCDE - ABCDE. And in fact the FIFO schedule is pessimal for aggregate miss rate if we require equal fairness as measured over two back-to-back cycles.

We call out an analogy in simple sequential single-threaded code where an application needs to iterate over all elements of an array or linked list. A naive approach is to simply access the elements in ascending order until reaching the end, and then repeat, yielding a robin-robin order. Taking residual cache residency in account, however it is better to alternate ascending then descending orders – akin to a classic *elevator seek* or *boustrophedonic* order – which yields a palindrome access pattern. Such cache-friendly alternating direction optimizations are well known and appear in various sorting algorithms [45, 46]. Yuan et al. [47] use the term "sawtooth" for the palindrome schedule. In our case, the "elements" are threads contending for a lock.

### 7.4 Mitigation

If desired, we can mitigate the unfairness from the effects above in a number of ways. A simple and expedient approach is to stochastically disrupt or perturb the repeating cycle, which reestablishes statistical long-term fairness. A viable technique is for incoming owners, having just acquired the lock, to run a thread-local Bernoulli trial, and based on the outcome, occasionally defer and immediately cede ownership to the next element in the entry segment, and propagate a reference to its wait element through the entry segment, where it will percolate to the tail, and eventually PPoPP'25,,

be re-granted ownership. This modification does not abrogate or otherwise violate our bypass guarantees or imperil anti-starvation as the reordering is strictly intra-segment.

More generally, if we just pick random elements, without replacement, from the entry segment for succession, we still retain the desirable population bounded anti-starvation property, statistically avoid long-term admission unfairness and cache residency fairness, and continue to enjoy aggregate miss rates (and throughput) that on average are the same or better than classic FIFO.

# 8 Avoiding the double-swap

```

struct Element {

std::atomic <int> Gate {0};

2

3 } ;

4 struct Lock {

5

std::atomic <Element *> Arv {nullptr};

std::atomic <Element *> Terminus {nullptr} ;

Element * Succ

= nullptr ;

8 } ;

9 static Element * const LOCKEDEMPTY = (Element *) uintptr_t(1) ;

10 void Acquire (Lock * L) {

11

static thread_local Element E {} ;

E.Gate = 0 ;

12

returns previous tail

13

14

auto tail = L\rightarrowarv.exchange (&E) ;

15

assert (tail \neq &E)

if (tail == nullptr) {

16

17

// Uncontended acquire -- fast-path return

18

L→Succ

= nullptr ;

19

L \rightarrow Terminus = \&E;

20

return ;

21

}

22

// Contention -- slow-path -- need to wait

23

24

auto succ = (Element *) (uintptr_t(tail) & ~1) ;

25

while (E.Gate ≠ 0) Pause()

26

assert (L→Arv.load() ≠ nullptr) ;

27

28

auto eos = L\rightarrowTerminus.load() :

assert (eos ≠ nullptr && eos ≠ &E) ;

29

30

if (tail == eos) {

Detected logical end-of-segment : annul succ

31

32

L→Terminus = LOCKEDEMPTY ;

33

succ = nullptr ;

34

3

35

L \rightarrow Succ = succ ;

36

}

37

void Release (Lock * L) {

assert (L→Arv.load() ≠ nullptr) ;

38

39

// case : normal succession within entry segment

auto succ = L \rightarrow Succ :

40

if (succ ≠ nullptr) { succ→Gate = 1 ; return ; }

41

42

// case : try uncontended fast-path

43

auto eos = L→Terminus.load() ;

44

assert (eos ≠ nullptr) ;

auto v = L→Arv.cas (eos, nullptr) ;

45

46

if (v == eos) return ;

47

48

// case : detach arrival segment which becomes next

49

// entry segment

50

auto w = L→Arv.exchange(LOCKEDEMPTY) ;

51

assert (w ≠ nullptr && w ≠ LOCKEDEMPTY && w ≠ eos) ;

52

53

w \rightarrow Gate = 1:

54

}

```

Listing 2. Double-Swap Avoidance

Listing-2 illustrates one way to avoid the *double-swap* scenario. We shift the Terminus field into the lock body and, during succession in the entry segment, check to see if the successor is the logical end-of-segment, and if, annul the successor and clear the Terminus field.

# 9 Conclusion

Reciprocating Locks is the first lock algorithm to have a fully constant-time doorway phase and a constant-time Release but which is still practical and fulfills the criteria for general purpose locking <sup>6</sup>.

In the future, we plan on exploring the "coherence traffic reduction" optimization (CTR), from HemLock, with Reciprocating Locks. Related, using the Intel CLDEMOTE or instructions or non-temporal stores to covey ownership may also act to reduce coherence traffic. Finally, we are working on techniques to impose long-term statistical admission fairnesss by means of randomizing or perturbing the order of the entry segment in order to break repeating palindromic admission schedules.

# Acknowledgments

We thank Peter Buhr at the University of Waterloo for access to their ARMv8 system.

# References

- Ole Agesen, David Detlefs, Alex Garthwaite, Ross Knippel, Y. S. Ramakrishna, and Derek White. An efficient meta-lock for implementing ubiquitous synchronization. *SIGPLAN Notices OOPSLA 1999*, 1999. doi:10.1145/320385.320402.

- [2] Vitaly Aksenov, Dan Alistarh, and Petr Kuznetsov. Performance prediction for coarse-grained locking. *CoRR*, abs/1904.11323, 2019. URL: http://arxiv.org/abs/1904.11323, arXiv:1904.11323.

- [3] Vitaly Aksenov, Daniil Bolotov, and Petr Kuznetsov. Peformance prediction for coarse-grained locking: MCS case. *CoRR*, abs/2110.05545, 2021. URL: https://arxiv.org/abs/2110.05545, arXiv:2110.05545.

- [4] James H. Anderson and Yong-Jik Kim. An improved lower bound for the time complexity of mutual exclusion. *Distrib. Comput.*, 2002. doi:10.1007/s00446-002-0084-2.

<sup>&</sup>lt;sup>6</sup>The name *Reciprocating Locks* arises from the following analogy with a piston-based compressor or reciprocating pump. The pump's cylinder has distinct intake and exhaust ports and the piston is initially positioned at the bottom of the cylinder. Threads intending to acquire the lock - say, A, B and C where A was the first to arrive and C last - arrive at the intake port and wait there. On the intake cycle, the piston pulls those threads from the intake port into the cylinder body. On the subsequent exhaust cycle, the piston expels the threads through the exhaust port. Passing through the exhaust port is analogous to passing through the lock's critical section. Like packets of air or gas, the threads are expelled from the cylinder through the exhaust port in an order reversed from that in which they originally arrived : C then B then A. The entry segment corresponds to the current cylinder contents and the arrival segment reflects threads that reside in the intake manifold, before entering the cylinder. The non-critical section is where threads circulate back from the exhaust to the intake. The intake phase is analogous to detaching the current arrival segment and shifting those threads into the entry segment.

- [5] J.H. Anderson, Y.J. Kim, and T. Herman. Shared-memory mutual exclusion: major research trends since 1986. *Distributed Computing*, 2003. URL: https://doi.org/10.1007/s00446-003-0088-6.

- [6] T. E. Anderson. The performance of spin lock alternatives for sharedmoney multiprocessors. *IEEE Transactions on Parallel and Distributed Systems*, 1990. doi:10.1109/71.80120.

- [7] Hagit Attiya, Danny Hendler, and Philipp Woelfel. Tight rmr lower bounds for mutual exclusion and other problems. In *Proceedings of the Fortieth Annual ACM Symposium on Theory of Computing*, STOC '08, 2008. doi:10.1145/1374376.1374410.

- [8] D. Avis and M. Newborn. On pop-stacks in series. Utilitas Math. 19, pages 129–140, 1981.

- [9] Stephen Boyd and Lieven Vandenberghe. Convex optimization. Cambridge university press, 2004.

- [10] Jonathan Corbet. MCS locks and qspinlocks. https://lwn.net/Articles/ 590243, March 11, 2014. Accessed: 2018-09-12.

- [11] Jonathan Corbet. A surprise with mutexes and reference counts. https: //lwn.net/Articles/575460, December 4, 2013.

- [12] Jonathan Corbet. Mcs locks and qspinlocks, 2014. URL: https://lwn. net/Articles/590243/.

- [13] Travis Craig. Building fifo and priority-queueing spin locks from atomic swap, 1993.

- [14] Intel Corporation David Mulnix. Intel® xeon® processor scalable family technical overview, 2017. Updated 2022. URL: https://www.intel.com/content/www/us/en/developer/articles/ technical/xeon-processor-scalable-family-technical-overview.html.

- [15] Dave Dice. Malthusian locks. In Proceedings of the Twelfth European Conference on Computer Systems, EuroSys '17, 2017. URL: http://doi. acm.org/10.1145/3064176.3064203.

- [16] Dave Dice and Alex Kogan. Avoiding scalability collapse by restricting concurrency. In Euro-Par 2019: Parallel Processing - 25th International Conference on Parallel and Distributed Computing, Göttingen, Germany, August 26-30, 2019, Proceedings, Lecture Notes in Computer Science. Springer, 2019. doi:10.1007/978-3-030-29400-7\\_26.

- [17] Dave Dice and Alex Kogan. Compact numa-aware locks. In Proceedings of the Fourteenth EuroSys Conference 2019, EuroSys '19. Association for Computing Machinery, 2019. doi:10.1145/3302424.3303984.

- [18] Dave Dice and Alex Kogan. TWA ticket locks augmented with a waiting array. In Euro-Par 2019: Parallel Processing - 25th International Conference on Parallel and Distributed Computing, Göttingen, Germany, August 26-30, 2019, Proceedings. Springer, 2019. doi:10.1007/978-3-030-29400-7\\_24.

- [19] Dave Dice and Alex Kogan. Fissile locks. In *Networked Systems (NETYS 2020)*, 2021. URL: https://doi.org/10.1007/978-3-030-67087-0\_13.

- [20] David Dice and Alex Kogan. Hemlock : Compact and scalable mutual exclusion. In Proceedings of the 33rd ACM Symposium on Parallelism in Algorithms and Architectures, SPAA, 2021. URL: https://doi.org/10. 1145/3409964.3461805.

- [21] David Dice, Virendra J. Marathe, and Nir Shavit. Lock cohorting: A general technique for designing numa locks. In *Proceedings of the* 17th ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming, PPoPP '12. Association for Computing Machinery, 2012. doi:10.1145/2145816.2145848.

- [22] David Dice, Virendra J. Marathe, and Nir Shavit. Lock cohorting: A general technique for designing numa locks. ACM Trans. Parallel Comput., 2015. URL: http://doi.acm.org/10.1145/2686884, doi: 10.1145/2686884.

- [23] Rotem Dvir and Gadi Taubenfeld. Mutual Exclusion Algorithms with Constant RMR Complexity and Wait-Free Exit Code. In James Aspnes, Alysson Bessani, Pascal Felber, and João Leitão, editors, 21st International Conference on Principles of Distributed Systems (OPODIS 2017), Leibniz International Proceedings in Informatics (LIPIcs), Dagstuhl, Germany, 2018. Schloss Dagstuhl-Leibniz-Zentrum fuer Informatik. URL: http://drops.dagstuhl.de/opus/volltexte/2018/

8652, doi:10.4230/LIPIcs.0PODIS.2017.17.

- [24] Stijn Eyerman and Lieven Eeckhout. Modeling critical sections in amdahl's law and its implications for multicore design. In *Proceedings* of the 37th Annual International Symposium on Computer Architecture, ISCA '10. ACM, 2010. URL: http://doi.acm.org/10.1145/1815961. 1816011, doi:10.1145/1815961.1816011.

- [25] Wim H. Hesselink and Peter A. Buhr. Mcsh, a lock with the standard interface. ACM Trans. Parallel Comput., 2023. URL: https://doi.org/10. 1145/3584696.

- [26] Prasad Jayanti, Siddhartha Jayanti, and Sucharita Jayanti. Towards an ideal queue lock. In *Proceedings of the 21st International Conference on Distributed Computing and Networking*, ICDCN 2020. Association for Computing Machinery, 2020. URL: https://doi.org/10.1145/3369740. 3369784.

- [27] Siddhartha Visveswara Jayanti. Simple, fast, scalable, and reliable multiprocessor algorithms. Massachusetts Institute of Technology, 2023. URL: https://dspace.mit.edu/handle/1721.1/150219.

- [28] Hyonho Lee. Local-spin mutual exclusion algorithms on the dsm model using fetch&store objects. Masters Thesis, University of Toronto. URL: http://www.cs.toronto.edu/pub/hlee/thesis.ps.

- [29] Hyonho Lee. Transformations of mutual exclusion algorithms from the cache-coherent model to the distributed shared memory model. In 25th IEEE International Conference on Distributed Computing Systems (ICDCS'05), 2005. doi:10.1109/ICDCS.2005.83.

- [30] Alexander Lochmann, Horst Schirmeier, Hendrik Borghorst, and Olaf Spinczyk. Lockdoc: Trace-based analysis of locking in the linux kernel. In *Proceedings of the Fourteenth EuroSys Conference 2019*, EuroSys '19. Association for Computing Machinery, 2019. doi:10.1145/3302424. 3303948.

- [31] Waiman Long. qspinlock: Introducing a 4-byte queue spinlock implementation. https://lwn.net/Articles/561775, July 31, 2013, 2013. Accessed: 2018-09-19.

- [32] O. Krieger B. Rosenburg M. Auslander, D. Edelsohn and R. Wisniewski. Enhancement to the mcs lock for increased functionality and improved programmability – u.s. patent application number 20030200457, 2003. URL: https://patents.google.com/patent/US20030200457.

- [33] P. Magnusson, A. Landin, and E. Hagersten. Queue locks on cache coherent multiprocessors. In *Proceedings of 8th International Parallel Processing Symposium*, 1994. doi:10.1109/IPPS.1994.288305.

- [34] Evangelos P. Markatos and Thomas J. LeBlanc. Multiprocessor synchronization primitives with priorities. 8th IEEE Workshop on Real-Time Operating Systems and Software. IEEE, 1991.

- [35] John M. Mellor-Crummey and Michael L. Scott. Scalable reader-writer synchronization for shared-memory multiprocessors. In *Proceedings* of the Third ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming, PPOPP '91. ACM, 1991. URL: http://doi.acm. org/10.1145/109625.109637.

- [36] Atsushi Nemoto. Bug 13690 pthread\_mutex\_unlock potentially cause invalid access. https://sourceware.org/bugzilla/show\_bug.cgi? id=13690, February 14, 2012.

- [37] Pedro Ramalhete. Ticket lock array of waiting nodes (awn), 2015. URL: http://concurrencyfreaks.blogspot.com/2015/01/ticket-lockarray-of-waiting-nodes-awn.html.

- [38] Pedro Ramalhete and Andreia Correia. Tidex: A mutual exclusion lock. In Proceedings of the 21st ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming, PPoPP '16, 2016. URL: http: //doi.acm.org/10.1145/2851141.2851171.

- [39] I. Rhee. Optimizing a fifo, scalable spin lock using consistent memory. In 17th IEEE Real-Time Systems Symposium, 1996. doi:10.1109/REAL. 1996.563705.

- [40] Michael L. Scott and Trevor Brown. Shared-Memory Synchronization, Second Edition. Springer, 2024. doi:10.1007/978-3-031-38684-8.

- [41] Harold S. Stone and Dominique Thibaut. Footprints in the cache. SIGMETRICS Perform. Eval. Rev., 1986. doi:10.1145/317531.317533.

PPoPP'25,,

- [42] R.K. Treiber, 1986.

- [43] U. Verner, A. Mendelson, and A. Schuster. Extending amdahl's law for multicores with turbo boost. *IEEE Computer Architecture Letters*, 2017. URL: https://doi.org/10.1109/LCA.2015.2512982.

- [44] Tianzheng Wang, Milind Chabbi, and Hideaki Kimura. Be my guest: Mcs lock now welcomes guests. SIGPLAN PPoPP, 2016. doi:10.1145/ 3016078.2851160.

- [45] Wikipedia. Cocktail shaker sort, 2018. URL: https://en.wikipedia.org/ wiki/Cocktail\_shaker\_sort.

- [46] Wikipedia. Gnome sort, 2018. URL: https://en.wikipedia.org/wiki/ Gnome\_sort.

- [47] Liang Yuan, Chen Ding, Wesley Smith, Peter Denning, and Yunquan Zhang. A relational theory of locality. *TACO – ACM Trans. Archit. Code Optim.*, 2019. doi:10.1145/3341109.