## arXiv:2412.01183v4 [quant-ph] 20 Dec 2024

## Neural Network-Based Frequency Optimization for Superconducting Quantum Chips

Bin-Han Lu<sup>1,2</sup>, Qing-Song Li<sup>1,2</sup>, Peng Wang<sup>1,2</sup>, Zhao-Yun Chen<sup>\*3</sup>, Yu-Chun Wu<sup>1,2,3</sup>, and Guo-Ping Guo<sup>1,2,3,4</sup>

<sup>1</sup> Key Laboratory of Quantum Information Chinese Academy of Sciences, School of Physics,

University of Science and Technology of China, Hefei, Anhui, 230026, P. R. China

<sup>2</sup> CAS Center For Excellence in Quantum Information and Quantum Physics,

University of Science and Technology of China, Hefei, Anhui, 230026, P. R. China

<sup>3</sup> Institute of Artificial Intelligence, Hefei Comprehensive National Science Center, Hefei, Anhui, 230026, P. R. China and

<sup>4</sup> Origin Quantum Co., Ltd. (Hefei)."

Optimizing the frequency configuration of qubits and quantum gates in superconducting quantum chips presents a complex NP-complete optimization challenge. This process is critical for enabling practical control while minimizing decoherence and suppressing significant crosstalk. In this paper, we propose a neural network-based frequency configuration approach. A trained neural network model estimates frequency configuration errors, and an intermediate optimization strategy identifies optimal configurations within localized windows of the chip. The effectiveness of our method is validated through randomized benchmarking and cross-entropy benchmarking. Furthermore, we found that for variational quantum eigensolvers, optimizing the frequency configurations for a crosstalk-aware hardware-efficient ansatz leads to improved energy calculations.

To achieve fault-tolerant quantum computing [1–4], superconducting quantum processors must scale beyond the limitations of noisy intermediate-scale quantum (NISQ) chips [5]. However, this progression faces two significant challenges: unreliable hardware manufacturing and imperfections in control systems, which contribute to various errors. Decoherence errors, including qubit relaxation and dephasing, are one major issue [6]. Another critical problem is crosstalk errors, which occur when excessive residual coupling between qubits causes parallel operations to interfere with each other [7–9]. Additionally, microwave pulses intended for single-qubit gates have unwanted effects on neighboring qubits, leading to microwave crosstalk errors [10]. Addressing these challenges is essential for enabling scalable fault-tolerant quantum computing.

The frequency-tunable architecture enables two-qubit gates by bringing neighboring qubits directly into resonance [11–13], resulting in shorter gate execution times than fixed-frequency qubits. However, errors in this architecture are susceptible to the frequency configuration. Different configurations lead to variations in qubit dephasing and relaxation times. Notably, when qubit frequencies align with Two-Level System (TLS) defects [14] or flux-sensitive points [15], decoherence times are significantly reduced. Furthermore, crosstalk arises when qubit frequencies unintentionally come into resonance [16]. As a result, optimizing qubit frequency configurations is critical to mitigating errors in frequency-tunable architectures [17–19].

Addressing frequency configuration requires developing a model that maps the frequency of each quantum gate to its associated error values. This model must account for decoherence noise at different qubit frequencies and identify whether qubit frequencies lie within closely resonant regions. Understanding how various errors interact and collectively impact qubits adds to the complexity. Building upon this model, solving an optimization problem becomes necessary to determine a set of frequency configurations that minimize errors for each quantum gate. However, as the number of qubits increases, the scale of the problem grows exponentially, making it a highly constrained and computationally intensive challenge.

Existing research tackles these challenges using compensation pulses to mitigate XY control signal crosstalk [20] and two-tone flux modulation to suppress decoherence [21]. However, these methods inevitably increase the complexity of the control system. Given the strong dependence of errors on frequency, a more direct approach involves identifying frequency configurations that circumvent hardware imperfections, thereby simplifying hardware control.

While some frequency configuration strategies lack a thorough investigation of the underlying physical systems [22, 23], Google's frequency configuration scheme [24] offers a more advanced solution by incorporating a deeper understanding of the physical principles. This approach employs an error model that linearly combines all sources of error, demonstrating a more comprehensive grasp of the system. Nonetheless, it has certain limitations. First, the impact of different error sources on qubits may not be accurately captured by linear combinations. Second, error sources such as gate distortion, microwave crosstalk, and other unknown global errors remain challenging to model precisely [18], which limits the generalization and scalability of this method. In [25], Ai et al. proposed using a multilayer perceptron to predict gate errors and a graph neural network for frequency optimization. After training, the multilayer perceptron is used to predict errors on other chips. However, due to fabrication inconsistencies, the error sources of each quantum chip vary, and the trained neural network may lack generalizability. In [26, 27], Morvan et al. and Zhang et al. formulated the frequency configuration problem as an integer programming problem with linear constraints. However, the physical mechanisms of qubit noise cannot be adequately captured by a simple set of linear constraints. Moreover,

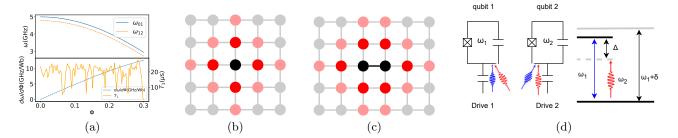

FIG. 1. (a) The frequency spectrum of tunable qubits, along with the variations in  $T_1$  and  $\frac{d\omega}{d\phi}$ , as the external control magnetic flux changes. (b-c) Coupling diagrams of quantum chips, where the dots represent qubits and the lines denote couplers. The black qubits (gate qubits) are shown to have stray coupling with all the red qubits. (d) Illustration of microwave crosstalk, where the drive applied to the target qubit  $q_1$  induces crosstalk with  $q_2$ . When the drive is not resonant with  $q_2$ , it causes a shift in the energy levels of  $q_2$ , and this effect becomes more pronounced as the frequencies of  $q_1$  and  $q_2$  approach resonance.

in addition to the mutual interactions between qubits, each qubit also exhibits its own complex noise mechanisms.

In this paper, we propose a neural network-based frequency configuration scheme to address these challenges. Unlike methods that rely on linear combinations of errors, neural networks can effectively learn and model the nonlinear interactions among error mechanisms. Additionally, as model-free tools, neural networks adapt to complex and dynamic environments, enabling them to better capture difficult-to-quantify error sources such as microwave crosstalk and gate distortions. Moreover, our approach eliminates the need to collect calibration data, such as decoherence times, for building the error model, significantly simplifying the data collection process.

In our frequency allocation process, we begin by randomly initializing a frequency configuration and using the neural network to predict gate errors across the chip. The window with the highest average error is identified and optimized locally. This iterative process is repeated until the overall average gate errors are minimized. In contrast, Google's scheme starts without predefined frequencies, progressively configuring windows adjacent to the previous step until all gates are assigned. However, their approach does not allow modifications to previously set frequencies, potentially leading to higher overall errors. Our method, by enabling iterative revisions to prior configurations, achieves lower global average errors and greater optimization flexibility.

Finally, after completing the configuration, we conducted single-qubit randomized benchmarking (RB) [28] and two-qubit cross-entropy benchmarking (XEB) [29] on the chip. The results significantly reduced gate errors, confirming that our frequency configuration effectively identifies and selects low-error-rate frequencies. Furthermore, we developed optimized frequency configurations for crosstalk-aware hardware-efficient ansatz (HEA) [30– 32] in variational quantum eigensolvers (VQE) [33–35]. Experimental results show that, under the same HEA, optimized frequency configurations achieve lower energy values compared to random configurations, highlighting the importance of frequency configurations in minimizing errors and enhancing computation fidelity.

Error Mechanisms On a quantum chip, the frequencies of single-qubit and two-qubit gates directly impact the final computational results. The first type of error is relaxation error  $(T_1 \text{ error})$  [6]. As the qubit frequency shifts, its  $T_1$  relaxation time also changes. The  $T_1$  relaxation time sharply decreases at certain Two-Level System (TLS) defect points [14], causing the qubit to easily transition from the higher energy state to the lower energy state. The second type is dephasing error  $(T_2 \text{ error})$  [15]. In a tunable-frequency architecture, a qubit's dephasing time  $T_2$  depends on the first derivative of the frequency to the magnetic flux, given by  $\frac{1}{T_2} \propto \frac{d\omega}{d\phi}$  (see Fig. 1(a)). Therefore, frequency settings should be chosen such that both  $T_1$  and  $T_2$  are sufficiently long to minimize errors (see Fig. 1(a)). The third type of error occurs during twoqubit gate execution when the qubit frequency shifts from the idle frequency  $\omega_{\text{off}}$  to the interaction frequency  $\omega_{\text{on}}$ . An excessive shift  $|\omega_{\text{off}} - \omega_{\text{on}}|$  can cause gate distortion errors. The fourth type is stray coupling crosstalk [18]. As shown in Fig. 1(b-c), if the gate-qubit frequency approaches resonance with neighboring or next-neighboring qubits, unintended coupling occurs, which can reduce gate fidelity. Finally, microwave crosstalk (see Fig. 1(d)) arises when a drive signal intended for qubit  $q_i$  influences a nearby qubit  $q_i$ . If  $q_i$  and  $q_j$  are near resonance,  $q_j$  is significantly affected. Unlike stray coupling, microwave crosstalk has a broader reach and can impact even nonneighboring qubits.

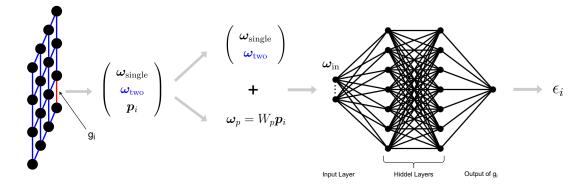

Neural Network Error Estimator We use a neural network to predict gate error under a given frequency configuration [36, 37]. The network (see Fig. 2) consists of a position embedding layer [38], an input layer, hidden layers, and an output layer. Overall, it is a multilayer perceptron [39, 40].

The network uses the frequencies of all single-qubit and two-qubit gates as inputs and predicts the errors for a specific single-qubit or two-qubit gate under a given configuration. Based on the previously discussed error mechanisms, the error of a single-qubit gate is influenced by its own frequency, the frequencies of its neighboring and next-neighboring qubits, as well as the frequencies

FIG. 2. Given a chip and a set of frequency configuration ( $\omega_{\text{single}}, \omega_{\text{two}}$ ). The input vector is defined as ( $\omega_{\text{single}}, \omega_{\text{two}}, p_i$ ). The vector  $p_i$  undergoes a linear transformation  $W_p$ , transforming it into a dense vector  $\omega_p$  incorporating positional information. This transformed vector is then added to ( $\omega_{\text{single}}, \omega_{\text{two}}$ ), resulting in a combined vector  $\omega_{\text{in}}$  that contains both configuration and positional information.  $\omega_{\text{in}}$  is then fed into a multilayer perceptron, and the final output  $\epsilon_i$  is the predicted error of  $g_i$  under configuration ( $\omega_{\text{single}}, \omega_{\text{two}}$ ).

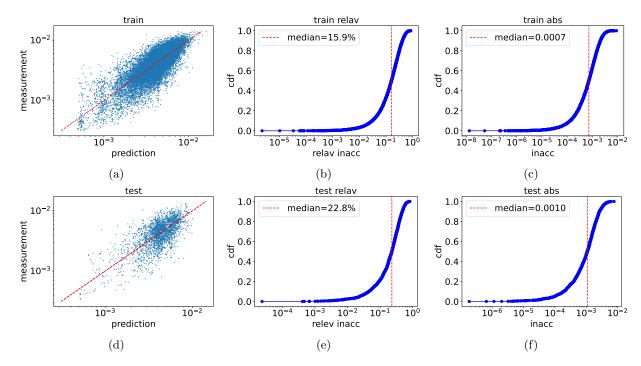

FIG. 3. (a) Scatter plot of the training set, showing the measured error data (vertical axis) and the corresponding predicted error data (horizontal axis) for each gate under a given configuration. Ideally, all points should cluster around the red line, where |prediction – measure| = 0. Similarly, (d) presents the scatter plot for the test set, where points in both the training and test sets are distributed around the red line after training. (b) Cumulative frequency distribution plot of relative errors, |prediction – measure|/measure, in the training set, with a median of 15.9%. (e) Cumulative distribution plot of relative errors in the test set, with a median of  $7 \times 10^{-4}$ . (f) Cumulative distribution plot of absolute errors in the test set, with a median of  $1 \times 10^{-3}$ .

of qubits inducing microwave crosstalk. For a two-qubit gate, its error is affected by the idle and interaction frequencies of the gate qubits, the frequencies of neighboring spectator qubits, and the frequencies of qubits causing microwave crosstalk with the gate qubits. To determine which qubit frequencies affect the target quantum gate, the neural network analyzes the input data and dynamically refines the connections between its neurons to optimize the learning process. As a result, the input vector must comprehensively include the single-qubit and twoqubit frequencies of all qubits on the chip.

$$\boldsymbol{\omega}_{\rm in} = (\boldsymbol{\omega}_{\rm single}, \boldsymbol{\omega}_{\rm two}). \tag{1}$$

Here,  $\omega_{\text{single}}$  and  $\omega_{\text{two}}$  represent the frequencies of singlequbit and two-qubit gates, respectively. For preprocess-

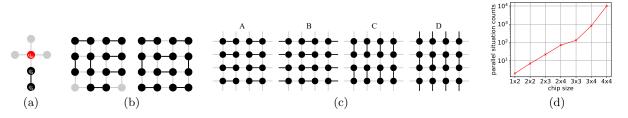

FIG. 4. (a) Qubits  $q_i$  and  $q_j$  perform a two-qubit gate, with  $q_n$  as the spectator. In a periodic grid,  $q_n$  can either execute a twoqubit gate with one of its three neighboring qubits (represented by gray dots) or a single-qubit gate, resulting in four possible frequency configurations. Considering all four scenarios introduces excessive constraints, expanding the exclusion zones. (b) The black edges and nodes represent the qubits and couplers involved in quantum gates within a specific time slice. Four example configurations are shown. (c) The coupler activation pattern determines which qubits can execute two-qubit gates simultaneously. (d) The number of parallel two-qubit gate scenarios increases with the scale of the  $M \times N$  chip.

ing the input data, let  $\omega_{\min}$  and  $\omega_{\max}$  denote the minimum and maximum frequencies across all single-qubit and two-qubit gates. Normalize the input data by mapping the frequency range to the interval (0, 1).

To enable the neural network to predict the error for a specific quantum gate, the input vector must include information about the gate's position on the chip. This is achieved using position embedding [38]. For clarity of explanation, we consider an example chip with an  $M \times N$ qubit array and 2MN - M - N couplers, resulting in an input vector of dimension 3MN - M - N. For position embedding, we define a one-hot sparse vector  $p_i$  with the same dimension as the number of gates (3MN - M - N)in this example). To predict the error  $\epsilon_i$  for the *i*-th gate,  $p_i$  is set such that  $(p_i)_j = \delta_{ij}$ .  $p_i$  is transformed via a trainable linear layer  $W_p$ , yielding a dense vector  $\boldsymbol{\omega}_p = W_p \boldsymbol{p}_i$  with dimensions matching the input vector  $\omega_{\mathrm{in}}$ . The final input to the neural network is constructed by combining  $\omega_p$  and  $\omega_{in}$  through addition:  $\omega = \omega_{in} + \omega_p$ . This combined vector encodes both the frequency configuration and positional information, enabling the network to output the error  $\epsilon_i$  for the target gate. The trainable position embedding layer is effective for this network as it processes fixed-dimension inputs without requiring extrapolation.

Fig. 3(a-c) shows the training results. In Fig. 3(a), the scatter plot of predicted errors versus measured errors is shown, with ideal data points aligning closely along the diagonal. Fig. 3(b) and Fig. 3(c) present cumulative frequency distribution plots of the relative and absolute errors between the predicted and measured values. Fig. 3(d-f) illustrates the test results. As seen in Fig. 3(e) and Fig. 3(f), the median relative error and absolute error in the test set are 22.8% and  $1 \times 10^{-3}$ , respectively. These values closely match those in the training set and fall within the same order of magnitude as the results from Google's model. Notably, our test set includes only 500 configurations, significantly fewer than Google's 6500 configurations.

**Frequency Configuration Strategy** In a periodic grid structure (see Fig. 4(a)), when qubits  $q_i$  and  $q_j$  execute a two-qubit gate, their neighboring qubit  $q_n$  may

engage in a two-qubit gate with up to three other qubits or a single-qubit gate, requiring up to four distinct frequency settings. Ideally, an optimized frequency configuration should avoid any crosstalk between parallel quantum gates. However, for an  $M \times N$  chip (see Fig. 4(b)). the number of couplers is 2MN - M - N, with each two-qubit gate on a coupler having two possible states: executed or not executed. Consequently, the number of potential parallel two-qubit gate scenarios can reach  $O(2^{MN})$  [41, 42] (see Fig. 4(d)). The crosstalk between qubits varies with each unique parallel gate scenario, and considering all possible scenarios results in an overwhelming number of frequency constraints. Given the exponential number of parallel scenarios, performing frequency configuration for all of them is infeasible. Thus, we focus on one two-qubit gate grouping pattern (see Fig. 4(c)), dividing the two-qubit gates into four groups. Gates within each group can operate in parallel, but groups cannot execute in parallel with one another. This approach covers all possible two-qubit gates on the chip.

Using a trained neural network, we can estimate the error rates of all quantum gates based on their frequency configurations. Building on this, we propose an optimization scheme designed to identify the configuration that minimizes the error predicted by the neural network.

Each quantum gate operates at a designated frequency, and for an  $M \times N$  chip, the number of frequency variables is 3MN - M - N. The control system allows for a frequency precision of  $\delta f$ , so each frequency can vary within the range  $F = \{f_{\min} + k\delta f | k \in \mathbb{N}, k \leq (f_{\max} - f_{\min})/\delta f\}$ . This makes the problem scale exponentially as  $O(|F|^{3MN})$ , limiting us to incrementally optimize the frequency configuration within a local window S on the chip.

Starting with a random configuration, we calculate the error for all quantum gates under this initial setup. Then, using a maximum optimization window size S, we iterate through all possible windows. For each window, we calculate the average gate error by summing the errors of all gates within the window and then optimize the frequencies of the two-qubit and single-qubit gates in the window with the highest average error. This iterative pro-

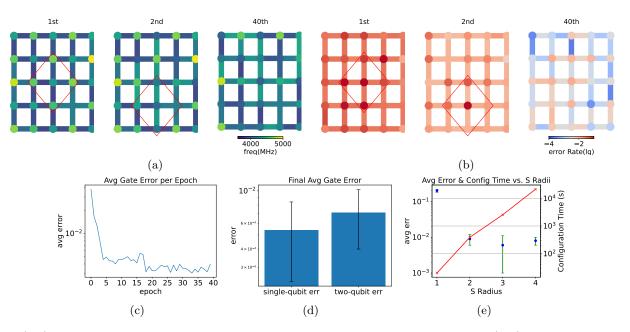

FIG. 5. (a-b) From left to right, the frequencies and errors are shown for the 1st, 2nd, and 40th(last) iterations, respectively. In each instance, the region S with the highest average error is selected (indicated by a red diamond). (c) The overall average error decreases progressively with the number of iterations. (d) The average errors of single-qubit and two-qubit gates are displayed. (e) The average gate error decreases as the radius of S increases.

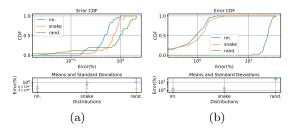

FIG. 6. (a) The orange lines show the CDF of single-qubit gate errors after neural network-based optimization, the red line represents Google's optimization, and the green line corresponds to a random configuration. The average errors are 0.49%, 0.78%, and 1.02%, respectively. (b) For two-qubit gates, the orange lines show the CDF after neural network-based optimization, the red line represents Google's baseline, and the green line corresponds to a random configuration. The average errors are 1.31%, 1.45%, and 23.3%, respectively.

cess continues until a configuration with minimal global average gate errors is achieved.

Fig. 5 illustrates the iterative optimization process for frequency configuration. Fig. 5(a) shows the frequency configurations at the 1st, 2nd, and final (40th) iterations. In Fig. 5(b), the predicted errors for each configuration are displayed. For each configuration, we calculate the average error of all quantum gates within each window S of radius 2. The window S with the highest average error is outlined in red and targeted for local optimization in the next iteration.

As seen in Fig. 5(c-d), the average gate error across the chip gradually converges to below  $10^{-2}$ . Finally, by

adjusting the radius of S, we observe that larger S values result in lower converged average errors. However, as Sincreases, the optimization process approaches global optimization, leading to a significant rise in computational complexity (see Fig. 5(d)). Selecting an optimal S allows the gate error to converge to a low level within a feasible computation time.

Fig. 6 shows the cumulative distribution function (CDF) of error probabilities measured after applying frequency configuration optimization. Single-qubit gates were evaluated using RB, while two-qubit gates were tested with XEB. Baselines include Google's optimizerbased frequency allocation framework and a parallel experiment using random configurations. From Fig. 6, our approach reduces average errors by 37.1% and 52.0% in the RB experiment, and by 9.7% and 94.4% in the XEB experiment, compared to Google's method and random configuration, respectively, highlighting significant twoqubit gate optimization.

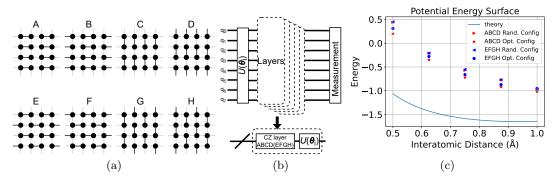

**Frequency configuration for HEA** The HEA is the most commonly used ansatz in VQE. The structure of this ansatz consists of a layer of single-qubit gates followed by a layer of entangling unitary operations  $U_{ENT}$  that entangle all of the qubits in the circuit Fig. 7(b). Typically, these  $U_{ENT}$  are composed of CNOT gates. Each time, a maximum set of parallelizable two-qubit gates is selected.

Therefore, we need to consider the frequency configuration when designing the HEA. For each layer of parallel CNOT gates, the maximum allowable parallel set permitted by the configuration must be selected.

FIG. 7. (a) Two sets of the largest parallelizable CZ gate patterns. Multiple CZ gates within any single ABCD (or EFGH) pattern can execute in parallel, while gates from different patterns cannot execute simultaneously. (b) In the HEA circuit, each layer comprises trainable CZ and single-qubit gates arranged in the ABCD(EFGH) patterns, coupling all qubits together. (c) The ground-state potential energy surface of the  $H_4$  molecule was calculated using VQE circuits with the ABCD and EFGH ansatz patterns.

We optimized the frequency configuration of two-qubit gates based on the patterns ABCD or EFGH. The HEA ansatz follows a cyclic, multi-layer sequence:  $A(E) \rightarrow U(\boldsymbol{\theta}_i) \rightarrow B(F) \rightarrow U(\boldsymbol{\theta}_i) \rightarrow C(G) \rightarrow U(\boldsymbol{\theta}_i) \rightarrow D(H)$ , where  $U(\boldsymbol{\theta}_i)$  represents the parameterized single-qubit gate layer.

To verify the effectiveness of the frequency configuration optimization, we optimized the frequencies for two different patterns and compared the results with random frequency configurations. We also assessed the difference in the minimum energy of the ground-state potential energy surface (PES) from the theoretical line after frequency optimization. From Fig. 7(c), we conclude that, under the same ansatz, the potential energy surface for the random frequency configuration is higher than that of the optimized frequency configuration. This demonstrates that the HEA designed with frequency-optimized configuration allows the quantum chip to operate at an optimal frequency, mitigating the impact of crosstalk on algorithm fidelity.

**Conclusion** In this work, we developed a comprehensive strategy to optimize quantum gate frequencies on a multi-qubit chip, addressing a critical challenge in enhancing quantum computing performance. Combining neural network-guided prediction, frequency configuration, and rigorous benchmarking effectively reduced gate errors and minimized crosstalk in quantum circuits.

Our frequency configuration method, optimized for a specific two-qubit activation pattern, enables parallelizable two-qubit gates to execute with significantly lower error rates compared to unoptimized configurations. Experimental validation through Randomized Benchmarking (RB) and Cross-Entropy Benchmarking (XEB) demonstrated that our optimized configurations achieve the lowest error rates, validating the effectiveness of our approach. In testing with the Variational Quantum Eigensolver (VQE), circuits using the optimized pattern produced more accurate ground-state energy calculations for the  $H_4$  molecular system. Notably, circuits with non-optimized configurations exhibited higher error rates, underscoring the importance of carefully designed frequency allocations.

Our findings highlight the potential of targeted frequency configuration and error minimization strategies in quantum computing, demonstrating how these methods can enable reliable performance improvements while managing computational complexity. Future research could extend this approach to larger quantum systems and explore dynamic frequency adjustments for real-time applications, further advancing the fidelity and scalability of quantum algorithms.

Acknowledgements This work was supported by the National Key Research and Development Program of China (Grant No. 2023YFB4502500).

- D. Horsman, A. G. Fowler, S. Devitt, and R. Van Meter, Surface code quantum computing by lattice surgery, New Journal of Physics 14, 123011 (2012).

- [2] C. Chamberland, G. Zhu, T. J. Yoder, J. B. Hertzberg, and A. W. Cross, Topological and subsystem codes on low-degree graphs with flag qubits, Physical Review X 10, 011022 (2020).

- [3] T. Jochym-O'Connor and R. Laflamme, Using concatenated quantum codes for universal fault-tolerant quantum gates, Physical review letters 112, 010505 (2014).

- [4] A. Paetznick and B. W. Reichardt, Universal faulttolerant quantum computation with only transversal gates;? format?; and error correction, Physical review letters 111, 090505 (2013).

- [5] S. Boixo, S. V. Isakov, V. N. Smelyanskiy, R. Babbush, N. Ding, Z. Jiang, M. J. Bremner, J. M. Martinis, and H. Neven, Characterizing quantum supremacy in nearterm devices, Nature Physics 14, 595 (2018).

- [6] G. Ithier, E. Collin, P. Joyez, P. Meeson, D. Vion, D. Esteve, F. Chiarello, A. Shnirman, Y. Makhlin, J. Schriefl,

*et al.*, Decoherence in a superconducting quantum bit circuit, Physical Review B—Condensed Matter and Materials Physics **72**, 134519 (2005).

- [7] P. Zhao, K. Linghu, Z. Li, P. Xu, R. Wang, G. Xue, Y. Jin, and H. Yu, Quantum crosstalk analysis for simultaneous gate operations on superconducting qubits, PRX quantum 3, 020301 (2022).

- [8] S. Krinner, S. Lazar, A. Remm, C. K. Andersen, N. Lacroix, G. J. Norris, C. Hellings, M. Gabureac, C. Eichler, and A. Wallraff, Benchmarking coherent errors in controlled-phase gates due to spectator qubits, Physical Review Applied 14, 024042 (2020).

- [9] S. Seo, J. Seong, and J. Bae, Mitigation of crosstalk errors in a quantum measurement and its applications, arXiv preprint arXiv:2112.10651 (2021).

- [10] P. Zhao, Y. Zhang, X. Li, J. Han, H. Xu, G. Xue, Y. Jin, and H. Yu, Spurious microwave crosstalk in floating superconducting circuits, arXiv preprint arXiv:2206.03710 (2022).

- [11] F. Yan, P. Krantz, Y. Sung, M. Kjaergaard, D. L. Campbell, T. P. Orlando, S. Gustavsson, and W. D. Oliver, Tunable coupling scheme for implementing high-fidelity two-qubit gates, Physical Review Applied **10**, 054062 (2018).

- [12] Y. Xu, J. Chu, J. Yuan, J. Qiu, Y. Zhou, L. Zhang, X. Tan, Y. Yu, S. Liu, J. Li, *et al.*, High-fidelity, highscalability two-qubit gate scheme for superconducting qubits, Physical review letters **125**, 240503 (2020).

- [13] Y. Sung, L. Ding, J. Braumüller, A. Vepsäläinen, B. Kannan, M. Kjaergaard, A. Greene, G. O. Samach, C. Mc-Nally, D. Kim, *et al.*, Realization of high-fidelity cz and zz-free iswap gates with a tunable coupler, Physical Review X **11**, 021058 (2021).

- [14] L. Tian, Cavity cooling of a mechanical resonator in the presence of a two-level-system defect, Physical Review B—Condensed Matter and Materials Physics 84, 035417 (2011).

- [15] P. Krantz, M. Kjaergaard, F. Yan, T. P. Orlando, S. Gustavsson, and W. D. Oliver, A quantum engineer's guide to superconducting qubits, Applied physics reviews 6 (2019).

- [16] B. han Lu, P. Wang, Z. yun Chen, H. yu Liu, T. ping Sun, P. Duan, Y. chun Wu, and G. ping Guo, Camel: Physically inspired crosstalk-aware mapping and gate scheduling for frequency-tunable quantum chips (2024), arXiv:2311.18160 [quant-ph].

- [17] M. Brink, J. M. Chow, J. Hertzberg, E. Magesan, and S. Rosenblatt, Device challenges for near term superconducting quantum processors: frequency collisions, in 2018 IEEE International Electron Devices Meeting (IEDM) (IEEE, 2018) pp. 6–1.

- [18] P. Klimov, J. Kelly, K. Satzinger, Z. Chen, H. Neven, and J. Martinis, Optimizing quantum gate frequencies for google's quantum processors, Bulletin of the American Physical Society 65 (2020).

- [19] P. V. Klimov, J. Kelly, J. M. Martinis, and H. Neven, The snake optimizer for learning quantum processor control parameters, arXiv preprint arXiv:2006.04594 (2020).

- [20] S. Krinner, N. Lacroix, A. Remm, A. Di Paolo, E. Genois, C. Leroux, C. Hellings, S. Lazar, F. Swiadek, J. Herrmann, *et al.*, Realizing repeated quantum error correction in a distance-three surface code, Nature **605**, 669 (2022).

- [21] J. A. Valery, S. Chowdhury, G. Jones, and N. Didier, Dy-

namical sweet spot engineering via two-tone flux modulation of superconducting qubits, PRX Quantum **3**, 020337 (2022).

- [22] R. Versluis, S. Poletto, N. Khammassi, B. Tarasinski, N. Haider, D. J. Michalak, A. Bruno, K. Bertels, and L. DiCarlo, Scalable quantum circuit and control for a superconducting surface code, Physical Review Applied 8, 034021 (2017).

- [23] Y. Ding, P. Gokhale, S. F. Lin, R. Rines, T. P. Propson, and F. T. Chong, Systematic crosstalk mitigation for superconducting qubits via frequency-aware compilation, 2020 53rd Annual IEEE/ACM International Symposium on Microarchitecture (MICRO), 201 (2020).

- [24] P. V. Klimov, A. Bengtsson, C. Quintana, A. Bourassa, S. Hong, A. Dunsworth, K. J. Satzinger, W. P. Livingston, V. Sivak, M. Y. Niu, *et al.*, Optimizing quantum gates towards the scale of logical qubits, Nature Communications **15**, 2442 (2024).

- [25] H. Ai and Y.-x. Liu, Graph Neural Networks-based Parameter Design towards Large-Scale Superconducting Quantum Circuits for Crosstalk Mitigation, arxiv (2024), arXiv:2411.16354 [quant-ph].

- [26] A. Morvan, L. Chen, J. M. Larson, D. I. Santiago, and I. Siddiqi, Optimizing frequency allocation for fixedfrequency superconducting quantum processors, Physical Review Research 4, 023079 (2022).

- [27] Z. Zhang, P. Gokhale, and J. M. Larson, Efficient frequency allocation for superconducting quantum processors using improved optimization techniques, arXiv preprint arXiv:2410.20283 (2024).

- [28] E. Knill, D. Leibfried, R. Reichle, J. Britton, R. B. Blakestad, J. D. Jost, C. Langer, R. Ozeri, S. Seidelin, and D. J. Wineland, Randomized benchmarking of quantum gates, Physical Review A—Atomic, Molecular, and Optical Physics 77, 012307 (2008).

- [29] F. Arute, K. Arya, R. Babbush, D. Bacon, J. C. Bardin, R. Barends, R. Biswas, S. Boixo, F. G. Brandao, D. A. Buell, *et al.*, Quantum supremacy using a programmable superconducting processor, Nature **574**, 505 (2019).

- [30] A. Kandala, A. Mezzacapo, K. Temme, M. Takita, M. Brink, J. M. Chow, and J. M. Gambetta, Hardwareefficient variational quantum eigensolver for small molecules and quantum magnets, nature 549, 242 (2017).

- [31] L. Leone, S. F. Oliviero, L. Cincio, and M. Cerezo, On the practical usefulness of the hardware efficient ansatz, arXiv preprint arXiv:2211.01477 (2022).

- [32] X. Wang, B. Qi, Y. Wang, and D. Dong, Eha: Entanglement-variational hardware-efficient ansatz for eigensolvers, arXiv preprint arXiv:2311.01120 (2023).

- [33] Y. Du, Y. Qian, and D. Tao, Accelerating variational quantum algorithms with multiple quantum processors, arXiv preprint arXiv:2106.12819 (2021).

- [34] D. Wang, O. Higgott, and S. Brierley, Accelerated variational quantum eigensolver, Physical review letters 122, 140504 (2019).

- [35] A. Peruzzo, J. McClean, P. Shadbolt, M.-H. Yung, X.-Q. Zhou, P. J. Love, A. Aspuru-Guzik, and J. L. O'brien, A variational eigenvalue solver on a photonic quantum processor, Nature communications 5, 4213 (2014).

- [36] Y.-c. Wu and J.-w. Feng, Development and application of artificial neural network, Wireless Personal Communications 102, 1645 (2018).

- [37] A. Dongare, R. Kharde, A. D. Kachare, *et al.*, Introduction to artificial neural network, International Journal of

Engineering and Innovative Technology (IJEIT) **2**, 189 (2012).

- [38] Z. Huang, D. Liang, P. Xu, and B. Xiang, Improve transformer models with better relative position embeddings, arXiv preprint arXiv:2009.13658 (2020).

- [39] M.-C. Popescu, V. E. Balas, L. Perescu-Popescu, and N. Mastorakis, Multilayer perceptron and neural networks, WSEAS Transactions on Circuits and Systems 8, 579 (2009).

- [40] M. W. Gardner and S. Dorling, Artificial neural networks

(the multilayer perceptron)—a review of applications in the atmospheric sciences, Atmospheric environment **32**, 2627 (1998).

- [41] W. Samotij, Counting independent sets in graphs, European journal of combinatorics 48, 5 (2015).

- [42] M.-J. Jou and G. J. Chang, The number of maximum independent sets in graphs, Taiwanese Journal of Mathematics 4, 685 (2000).