# Hardware Implementation of Projection-Aggregation Decoders for Reed-Muller Codes

Marzieh Hashemipour-Nazari, Andrea Nardi-Dei, Kees Goossens, and Alexios Balatsoukas-Stimming

Electronic Systems, Eindhoven University of Technology, The Netherlands

arXiv:2408.10850v1 [cs.AR] 20 Aug 2024

*Abstract*—This paper presents the hardware implementation of two variants of projection-aggregation-based decoding of Reed-Muller (RM) codes, namely unique projection aggregation (UPA) and collapsed projection aggregation (CPA). Our study focuses on introducing hardware architectures for both UPA and CPA. Through thorough analysis and experimentation, we observe that the hardware implementation of UPA exhibits superior resource usage and reduced energy consumption compared to CPA for the vanilla IPA decoder. This finding underscores a critical insight: software optimizations, in isolation, may not necessarily translate into hardware cost effectiveness.

*Index Terms*—Projection-aggregation-based decoding, Reed-Muller codes, hardware implementation.

## I. INTRODUCTION

T HE demand for ultra-reliable low-latency communications (URLLC) in future communication systems, particularly for machine-type communications (MTC) and IoT scenarios, necessitates the development of efficient error-correction coding schemes capable of handling short packets [1]–[3]. Traditional codes like low-density parity check (LDPC) and turbo codes can face challenges in maintaining high reliability for short packets due to their design complexities and inherent limitations [4], [5]. Polar codes [6] offer a promising solution for short blocks through successive cancellation list (SCL) decoding [7]. However, optimizing their performance for short block lengths necessitates adjustments such as using a large list size, which increases decoding complexity, and the integration of cyclic redundancy check (CRC) codes, which decreases the effective information rates, especially for low-rate codes.

Reed-Muller (RM) codes, initially introduced by Reed [8] and Muller [9], have regained attention due to the practical limitations of polar codes, particularly for short block lengths [10], [11]. Unlike polar codes, which aim to minimize error probability under successive cancellation (SC) decoding [12], [13], RM codes are designed to optimize performance under maximum likelihood (ML) decoding by maximizing the minimum distance between codewords. Consequently, RM codes exhibit superior performance under ML decoding compared to polar codes. Recent research has also highlighted capacity-achieving capability of RM codes for binary erasure channels (BEC) [14], binary symmetric channels (BSC) [15], and general binary-input memoryless symmetric (BMS) channels [16].

Several decoding algorithms have been developed to efficiently decode RM codes [17]–[22]. Moreover, due to the structural similarities between RM codes and polar codes, improved decoding algorithms initially designed for polar codes, such as fast successive cancellation (FSC) and fast successive cancellation list (FSCL) decoding, can be adapted to RM codes [23], [24]. Recently, recursive projection-aggregation (RPA), a near-maximum likelihood (ML) decoding technique, has demonstrated significant potential to improve error-correction performance for short block-length RM codes [25]. The RPA decoding method first breaks down the received codeword into shorter RM codewords using codeword projections. Subsequently, it recursively decodes these projected codewords until reaching first-order codewords, which are efficiently decoded using the fast Hadamard transform (FHT) [26]. Finally, it aggregates the shorter decoded codeword.

The computational complexity of RPA decoding depends on the number of projections required to generate first-order codewords, which is influenced by the order of the RM code r and its block length n. The complexity of RPA decoding scales as  $n^r$ , making it generally impractical for RM codes with r > 2. Furthermore, the recursive nature of RPA poses challenges for hardware implementation. Consequently, various approaches have been proposed to address these issues.

The work of [27] introduces a method to reduce complexity by incorporating an early stopping condition. However, this approach necessitates additional hardware to verify the early stopping condition. The work of [28] proposes K-sparse RPA (K-SRPA), employing multiple pruned RPA decoders instead of one full RPA decoder and utilizing a CRC code to select the best output among the outputs of k decoders. As explained previously, integrating a CRC into the codeword decreases the information rate, and the presence of multiple decoders increases hardware cost. The work of [29] suggests reducing the complexity of [28] by incorporating run-time preprocessing computations on the received vector to select the optimal projections for pruned RPA, thus reducing the number of projections compared to K-SRPA. However, from a hardware implementation perspective, this method would require extensive run-time preprocessing components, increasing latency and hardware resources while also disrupting the inherent parallelism of the RPA decoder. The research conducted in [30] introduces collapsed projection aggregation (CPA), merging r-1 levels of projections into one level, resulting in fewer first-order codewords compared to RPA decoding. The work of [31] combines the concepts of [27] and [28] and presents a multi-factor pruned RPA (MFP-RPA), which achieves good performance while reducing complexity. However, its unstructured pruning method poses challenges for hardware implementation. Subsequently, based on observations in MFP-RPA, [32] proposes a systematic pruning approach

called recursive unique projection-aggregation (RUPA). RUPA prevents the generation of duplicate projections in RPA, resulting in exactly the same algorithmic complexity as CPA. In addition, pruned CPA (PCPA) [33] and optimized PCPA [34] proposed methods to reduce CPA complexity. However, similar to [29], these methods require run-time preprocessing to select the best group of projections based on the received vector.

In addition to the considerable computational complexity of the RPA algorithm, its recursive nature poses significant challenges for hardware implementation. To address this, [35] introduces the iterative projection aggregation (IPA) algorithm, converting the recursive structure of the RPA decoder into an iterative one. Recently, in [36], a soft-input flexible pipelined architecture for the IPA algorithm has been proposed. Postsynthesis results in [36] indicate that using the proposed IPA architecture, RM codes outperform polar codes under a state-of-the-art SCL decoder [37] with identical block length, information rate, and error-correction performance. However, implementing the IPA decoder for RM codes with r > 2remains challenging due to either high resource usage or high latency in parallel or sequential configurations, respectively. To extend the applicability of IPA to a broader range of RM codes, algorithmic complexity-reduction methods are needed.

*Contributions & Outline:* In this work, we first highlight the challenge posed by the unique projection selection method [36] for hardware implementation and then address it by formulating and solving an integer linear problem (ILP) for projection selection. We then propose a flexible hardware architecture tailored to the iterative unique projection aggregation (IUPA) decoder, leveraging the ILP solution to minimize resource usage. Additionally, we introduce a semi-flexible pipelined architecture for CPA decoding [30], facilitating a comprehensive analysis and comparison of the IUPA, CPA, and IPA architectures. Our results are a reminder that focusing solely on improving the algorithmic complexity might not always result in better hardware. For instance, although CPA decoding has lower asymptotic computational complexity than IPA, it may still require more hardware resources in certain configurations.

The remainder of this paper is organized as follows. In Section II, we provide an overview of RM codes and the decoding algorithms associated with them, including RPA, IPA, CPA, and IUPA. We then highlight the challenges of implementing the IUPA algorithm in hardware and propose solutions in Section III, while in Section IV we introduce a flexible hardware architecture tailored to IUPA. Following this, we present the hardware architecture for CPA decoding in Section V. In Section VI, we present comprehensive simulation and synthesis results, offering a thorough comparison of IPA, IUPA, and CPA decoders. Finally, Section VII concludes the paper and summarizes our findings.

#### II. BACKGROUND

*Notation:* Throughout this paper, vectors are represented in boldface. Matrices are denoted by bold uppercase non-italic letters. The notation y(i) refers to the *i*-th element of the vector y. Additionally,  $D_{ij}$  denotes the element on row *i* and column *j* of the matrix **D**.  $D_{i\star}$  and  $D_{j\star}$  indicate the *i*-th row and

the *j*-th column in matrix **D**, respectively. Furthermore, the symbol  $\oplus$  signifies summation over the binary field  $\mathbb{F}_2$ . Finally,  $\binom{m}{s}_2$  is the 2-binomial coefficient and is given by:

$$\binom{m}{s}_{2} = \prod_{i=0}^{s-1} \frac{1 - 2^{m-i}}{1 - 2^{i+1}}.$$

(1)

# A. Reed-Muller codes

Reed-Muller (RM) codes denoted as RM(m,r) are linear block codes, where r denotes the code rate and m determines the block length with  $n = 2^m$ . They encode a k-bit binary vector  $\boldsymbol{u}$  into an n-bit codeword  $\boldsymbol{c} = \boldsymbol{u}\mathbf{G}_{(m,r)}$ , where  $k = \sum_{i=0}^{r} {m \choose i}$  and  $\mathbf{G}_{(m,r)}$  is the generator matrix of the RM(m,r)code. The matrix  $\mathbf{G}_{(m,r)}$  can be constructed recursively as [38]:

$$\mathbf{G}_{(m,r)} = \begin{bmatrix} \mathbf{G}_{(m-1,r)} & \mathbf{G}_{(m-1,r)} \\ \mathbf{0} & \mathbf{G}_{(m-1,r-1)} \end{bmatrix}, \quad \mathbf{G}_{(1,1)} = \begin{bmatrix} 1 & 1 \\ 0 & 1 \end{bmatrix}.$$

(2)

Moreover, each codeword  $c = (c(z), z \in \mathbb{E}) \in \text{RM}(m, r)$ represents a binary incidence vector of a monomial F with a degree at most r, evaluated across all elements  $z_i$ , where  $i \in 0, 1, \ldots, 2^m - 1$ , of  $\mathbb{E} := \mathbb{F}_2^m$ .

# B. RPA decoding

The work of [25] demonstrates that projecting  $c \in \text{RM}(m, r)$ onto the cosets of a one-dimensional subspace  $\mathbb{B}$  of  $\mathbb{E}$  generates the codeword  $c_{/\mathbb{B}} \in \text{RM}(m-1, r-1)$ . The projection of conto the cosets of  $\mathbb{B}$  is defined as follows:

$$c_{/\mathbb{B}} = \operatorname{Proj}(c, \mathbb{B}) := (c_{/\mathbb{B}}(T) := \bigoplus_{z \in T} c(z), T \in \mathbb{E}/\mathbb{B}), (3)$$

where  $\mathbb{E}/\mathbb{B}$  is a quotient space comprising  $2^{m-1}$  cosets  $T$  of

where  $\mathbb{E}/\mathbb{B}$  is a quotient space comprising  $2^{m-1}$  cosets T of  $\mathbb{B}$ . The construction of  $\mathbb{E}/\mathbb{B}$  is detailed in [25]. RPA decoding leverages this characteristic of RM codes and has three main steps: projection, recursive decoding, and aggregation.

1) Projection: Let L denote the vector of log-likelihood ratios (LLRs) corresponding to the output of a transmitted codeword  $c \in \text{RM}(m, r)$ . RPA decoding computes the projected vector  $L_{/\mathbb{B}}$  for each one-dimensional subspace  $\mathbb{B}$  of  $\mathbb{E} := \mathbb{F}_2^m$ . This projection can be computed using the hardware-friendly min-sum (MS) approximation [27]:

$$\boldsymbol{L}_{/\mathbb{B}} \approx \left( c_{/\mathbb{B}}([T]) := \min_{z \in T} \left\{ |L(z)| \right\} \prod_{z \in T} \operatorname{sign}\left(L\left(z\right)\right), T \in \mathbb{E}/\mathbb{B} \right).$$

(4)

Since each one-dimensional subspace of  $\mathbb{E}$  is comprised of 0 and a non-zero element, there exist  $2^m - 1$  such subspaces in total, leading to  $2^m - 1$  projected vectors.

2) Recursive decoding: RPA calls itself recursively until r = 1, i.e., until first-order codewords are obtained. Subsequently, it employs an efficient fast Hadamard transform (FHT) decoder [39] to decode the generated first-order RM codes.

3) Aggregation: After the projection and recursive decoding steps,  $2^m - 1$  LLR vectors  $\hat{L}_{/\mathbb{B}}$  are obtained. RPA aggregates these codewords with the input vector L as:

$$\hat{L}(z) = \frac{1}{2^m - 1} \sum_{i=1}^{2^m - 1} \left( 1 - 2\hat{c}_{/\mathbb{B}_i}([z \oplus \mathbb{B}_i]) \right) L(z \oplus i), \quad (5)$$

where  $\hat{L}(z)$  denotes the *z*-th coordinate of  $\hat{L} = (\hat{L}(z), z \in \mathbb{E})$ , and  $[z \oplus \mathbb{B}_i]$  is the index of the coset  $\mathbb{B}_i$  that includes coordinate

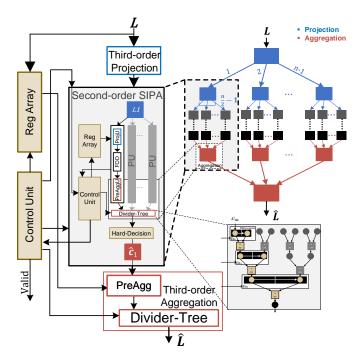

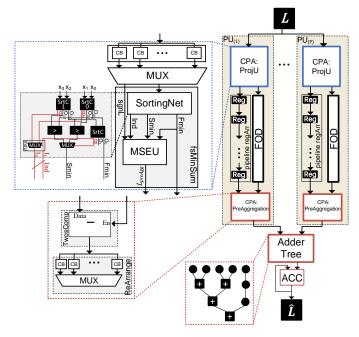

Fig. 1: Third-order IPA decoder for one iteration [36].

z. Additionally,  $\hat{c}_{/\mathbb{B}_i}$  represents the result of recursive decoding of the projected vector on subspace  $\mathbb{B}_i$ . Then, L is replaced by  $\hat{L}$  and additional RPA iterations are performed until  $\hat{L}$  is equal to L or a maximum number of iterations is reached. Finally, RPA decoding takes element-wise hard decisions on  $\hat{L}$  to determine the binary decoded codeword  $\hat{c}$ .

The number of first-order codewords generated in the innermost level of recursion is a proxy for the computational complexity of the RPA algorithm and scales exponentially with r [25]. From an implementation perspective, this makes the RPA algorithm impractical for r > 2.

# C. IPA decoding and implementation

The simulation results in [35] show that the majority of projected codewords are corrected after the initial iteration within each recursion level. Moreover, the work of [36] demonstrates that internal iterations disrupt the intrinsic parallelism of the RPA decoding method, leading to difficulties in hardware implementation. Therefore, the iterative projection aggregation (IPA) decoding method eliminates internal iterations, keeping only the iterations at the outer level. Based on this approach, both hard-decision and soft-decision IPA decoders were proposed and implemented in [35] and [36], respectively.

Fig. 1 illustrates the block diagram of the (soft-input) IPA decoder for third-order RM codes that we proposed in [36]. Specifically, the architecture proposed in [36] employs a foundational decoder for second-order codes, which is comprised of p processing units (PUs), each containing a projection unit (*ProjU*), a first-order decoder (*FOD*), and a preaggregation unit (*PreAggU*). The second-order IPA decoder can be configured from fully sequential with p = 1 PU to fully parallel with  $p = 2^m - 1$  PUs. The *ProjU* component for the *i*-th PU encompasses  $\frac{2^m}{p}$  distinct permutations based

on corresponding subspaces  $\mathbb{B}_j, j \in \{i, \ldots, i \times \frac{2^m}{p} - 1\}$ , for the received vector  $L \in \mathrm{RM}(m, 2)$ . Additionally, it includes  $2^m - 1$  two-input *MinSum* components, implementing the MS update rule of (4) on each pair of permuted coordinates of L. The *FOD* component is a hardware implementation of the FHT-based first-order decoder.

The aggregation step based on (5) requires all decoded results of the first-order codewords for all  $2^m - 1$  projections to compute an average for each coordinate of  $\hat{L}$ . Due to this dependency, it cannot be implemented directly in parallel. Hence, [36] divided it into two steps: pre-aggregation and averaging. In the pre-aggregation step,  $L_{agg}^i$  for the decoded projected vector  $\hat{c}_{/\mathbb{B}_{*}}$  is calculated as:

$$L^{i}_{\operatorname{agg}}(z) := \left(1 - 2\hat{c}_{/\mathbb{B}_{i}}([z \oplus \mathbb{B}_{i}])\right) L(z \oplus i).$$

(6)

The *PreAggU* component includes two crossbars for selecting the proper indices for  $\hat{c}_{/\mathbb{B}_i}$  and L. Moreover, since  $(1 - 2\hat{c}_{/\mathbb{B}_i}([z \oplus \mathbb{B}_i]))$  is either 1 or -1 the product in (6) can be performed with a two's complement circuit for  $L(z \oplus i)$  with  $\hat{c}_{/\mathbb{B}_i}([z \oplus \mathbb{B}_i])$  as its enable port. To finalize the aggregation process and compute the average of all estimated vectors  $L^i_{agg}, i \in \{1, \ldots, n-1\}$ , a divider tree composed of m twoinput adders and shift registers is employed. Further details on the divider tree are provided in [36, Section III-B].

Post-synthesis analysis of IPA has shown that it outperforms a state-of-the-art SCL decoder [37] for polar codes of identical block-length and information rate, achieving comparable error-correction performance for selected short codes. However, its high number of projections either requires large hardware for RM codes with r > 2 in low-latency configurations or has high latency in low-resource setups.

# D. CPA decoding

Collapsed projection aggregation (CPA) [30] decoding directly projects the received vector of LLRs  $\boldsymbol{L}$  onto (r-1)-dimensional subspaces of  $\mathbb{E}$  instead of r-1 levels of one-dimensional projections. In CPA decoding, the projection rule is similar to (4). However, each coset T in CPA contains  $2^{r-1}$  elements, unlike the IPA algorithm where each coset contains only two elements. Since, there exist  $\binom{m}{r-1}_2$  different (r-1)-dimensional subspaces for  $\mathbb{E}$ , CPA decoding yields  $\binom{m}{r-1}_2$  distinct first-order codewords instead of  $\prod_{i=0}^{r-2} \binom{m-i}{1}_2$  in the IPA decoding. After decoding the obtained first-order codewords using an FHT-based decoder, CPA constructs the vector  $\hat{\boldsymbol{L}} = (\hat{L}(z), z \in \mathbb{E})$  according to:

$$\hat{L}(z) = \frac{1}{n_p} \sum_{i=1}^{n_P} -1^{\hat{c}_{/\mathbb{B}_i}([T])} \left( \min_{z_j \in T-z} \{ |L(z_j)| \} \prod_{z_j \in T-z} \operatorname{sign}\left(L\left(z_j\right)\right) \right), \tag{7}$$

where  $n_P = {\binom{m}{r-1}}_2$ . Finally, CPA iterates until either reaching a maximum number of iterations  $N_{\text{max}}$  or achieving convergence of the output vector  $\hat{L}$  to the input vector L.

The complexity of CPA is significantly reduced for RM codes with r > 2 compared to IPA. This reduction can be quantified using the ratio of the number of first-order codewords generated in CPA ( $N_{\text{CPA}}$ ) to that in IPA ( $N_{\text{IPA}}$ ):

$$\frac{N_{\text{CPA}}}{N_{\text{IPA}}} = \frac{\binom{m}{r-1}_2}{\prod_{i=0}^{r-2} \binom{m-i}{1}_2} = \prod_{i=0}^{r-2} \frac{1}{2^{i+1}-1}.$$

(8)

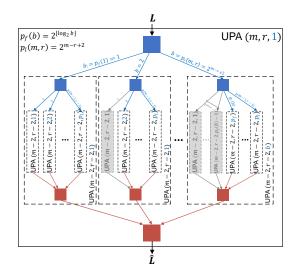

Fig. 2: Block diagram of two unfolded levels of unique projection aggregation method for RM(m, r) [32].

However, the projection and aggregation rules in CPA are more complex than IPA since they involve  $2^{r-1}$  inputs.

# E. IUPA decoding

The work of [32] reveals that a considerable number of first-order codewords generated after r-1 levels of projections in RPA or IPA algorithms are duplicates. Specifically, within the inner level of projections of both RPA and IPA algorithms, only  $\binom{m}{r-1}_2$  unique projected vectors exist. These unique projected vectors are identical to those generated in the CPA algorithm. By following the RPA projection methodology with r-1 levels on one-dimensional subspaces,  $N_{\text{IPA}}$  subspaces with r-1 dimensions are constructed, of which  $\binom{m}{r-1}_2$  are distinct. Therefore, the unique projection selection method of [32] proposes a method of projection in r-1 levels on one-dimensional subspaces such that there are no duplicate first-order codewords at the innermost level of projection.

The decoding method based on this projection selection is referred to as recursive/iterative unique projection aggregation (RUPA/IUPA). The difference between the recursive and iterative versions of this decoding method lies in the iteration on the levels of recursion in RUPA. As mentioned in Section II-C, internal iterations add complexity to hardware implementation without considerable enhancements in error correction performance [35]. Therefore, considering the hardware implementation goal of this work, we focus on IUPA.

Fig. 2 illustrates a single iteration of IUPA decoding. The grayed-out branches indicate the redundant projections found in IPA decoding but disregarded in IUPA decoding. As depicted in Fig. 2, the unique projection selection process introduces a new parameter, denoted as b, indicating the index of the projection branch. The initial and final projections within each UPA block are labeled as  $b_f$  and  $b_l$  respectively, and are defined as:

$$b_f = 2^{\lfloor \log_2 b \rfloor},$$

$b_l = 2^{m-r+2} - 1.$

(9)

IUPA for  $\operatorname{RM}(m, r)$  starts with b = 1 initially and generates  $L^i, i \in 1, \ldots, 2^{\lfloor \log_2 b \rfloor}$ , vectors potentially belonging to  $\operatorname{RM}(m-1, r-1)$  code. Consequently, IUPA runs on each  $L^i$  with a parameter  $b_i = i$ . The number of projections for decoding each  $L^i$  is a function of  $b_i$ , m, and r, and is defined as  $b_l - b_f + 1$  according to (9). Therefore, the projection and aggregation rules in IUPA are as simple as in IPA and, at the same time, the number of generated first-order codewords in IUPA is identical to that of CPA.

### **III. IUPA: PROJECTION ALLOCATION**

IPA decoding avoids duplicate first-order codewords for second-order RM codes, making IUPA decoding identical to IPA. For higher-order codes, applying the unique selection method to our IPA architecture [36] is a promising way to reduce resource usage and energy consumption. However, implementing the unique selection method in hardware is not straightforward. In this section, we explain the challenges associated with using the unique selection projection method in hardware for RM(m, 3) codes and we then propose a solution.

#### A. IUPA hardware challenges

Unique projection selection significantly reduces the hardware requirements of the IPA decoder by a factor of  $\prod_{i=0}^{r-2} \frac{1}{2^{i+1}-1}$  for a fully-parallel implementation. However, a fully-parallel decoder requires substantial hardware resources and has a high energy consumption, making it impractical [36], so partially-parallel decoders are typically used in practice.

As elaborated in Section II-C, in a partially-parallel implementation of the IPA decoder for RM(m,3) codes, a base second-order decoder with p PUs is defined. This decoder is then reused to decode all the second-order projected vectors, as they all need to project onto the same  $2^{m-1}-1$  one-dimensional subspaces. The projection and aggregation circuits within each PU of the second-order decoder provide  $\frac{2^{m-1}}{n}$  distinct permutations of their input vector. However, in IUPA decoding for RM(m, 3), different second-order codewords require different numbers of projections based on different one-dimensional subspaces. This non-uniform distribution of projections is not ideal for hardware implementation. Implementing a secondorder decoder providing all possible projections is inefficient in terms of hardware, as only the first projected second-order vector requires all  $2^{m-1} - 1$  projections, while following vectors require only a subset of projections. Moreover, as each projection is required at least once, we cannot eliminate a subset of projections from the second-order decoder. The challenge now lies in distributing the projections in a way that maximizes reuse of the second-order decoder.

#### B. Projection allocation method for RM(m, 3) codes

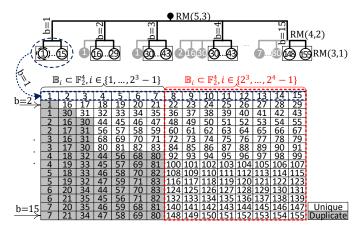

Fig. 3 illustrates the unfolded projection levels for an example third-order RM code with m = 5 in a tree-like structure, which we call *redundancy tree*. Since only the first  $2^{m-1}-1$  branches (i.e., projections) on the initial level contribute to unique first-order codewords at the innermost level [32], the latter  $2^{m-1}$  branches are eliminated from the redundancy tree shown in

Fig. 3: Redundancy tree and matrix  $\mathbf{R}$  for RM(5,3).

Fig. 3. The first-order vectors are represented as leaves on the tree and are numbered from 1 to  $\binom{m}{r-1}_2$ . Duplicate vectors share identical numbers. A matrix **R** with size  $(2^{m-r+2} - 1) \times (2^{m-r+2} - 1)$  is built from the redundancy tree as shown in Fig. 3. Each innermost level branch, corresponding to a second-order vector, is illustrated as a row in **R**. Moreover, the *i*-th column in **R** represents the one-dimensional projection of the second-order codewords onto  $\mathbb{B}_i = \{0, i\}$ . The right half of **R** always contains unique numbers (white), while the left half contains both unique and duplicate numbers (gray), representing duplicate first-order codewords generated during IPA decoding.

As discussed earlier, the unique projection selection method in IUPA decoding prevents the generation of duplicate projected first-order codewords. In a partially-parallel implementation of the IUPA decoder with G second-order decoders, each second-order decoder can perform different sets of secondorder projections (i.e., columns in  $\mathbf{R}$ ). The primary goal is to minimize the hardware required for the IUPA decoder while maintaining a given latency. To achieve this, we first need to identify all unique numbers (i.e., first-order codewords) generated by the second-order decoders used in the IUPA decoder. We do this by grouping the rows of  $\mathbf{R}$  such that each group contains unique numbers, both within the group and across other groups, while maximizing the overlap in their column indices. Consequently, rows within a group that share similar columns will utilize the same second-order decoder, reducing hardware requirements. Moreover, if one PU in each second-order decoder can perform one second-order projection in one clock cycle, we will require  $\begin{bmatrix} \frac{\#\text{selected columns}}{2} \end{bmatrix}$  PUs for each group to finish its assigned second-order projections in  $\lambda$ clock cycles. Hence, in a partially-parallel implementation with G second-order decoders, achieving a high degree of column overlap within each group can significantly reduce hardware costs for a given latency. The aforementioned problem can be formulated as an integer linear program (ILP) with the objective of minimizing the total number of PUs required for G second-order decoders to achieve a fixed latency  $\lambda$ .

# C. ILP formulation

We use a  $(2^{m-1}-1) \times (2^{m-1}-2)$  matrix **D** constructed from the left half of **R**. The right half of **R**, which has  $2^{m-2}$  columns (i.e., second-order projections), is excluded from **D** as it contains only unique first-order vectors. These unique firstorder vectors require  $\lceil \frac{2^{m-2}}{\lambda} \rceil$  dedicated PUs in each secondorder decoder to be processed within  $\lambda$  cycles, so they do not need to be involved in the ILP formulation. In **D**, each number appears three times for RM(m, 3) codes. Hence, for any element  $D_{jk}$  in **D**, there exist  $D_{j'k'}$  and  $D_{j''k''}$  such that  $D_{jk} = D_{j'k'} = D_{j''k''}$ , where  $(j, k) \neq (j', k') \neq (j'', k'')$ .

Along with **D**, we provide two parameters as inputs to the ILP problem: the target latency  $\lambda$  and the number of groups G. Limiting G to a power of two is advantageous because it prevents uneven distribution of rows among the groups, which can complicate the control unit and lead to inefficient resource usage as smaller groups would be idle part of the time. By making G a power of two, each group contains  $\frac{2^{m-1}}{G}$  equally distributed rows, except for one group, which has  $\frac{2^{(m-1)}}{G} - 1$  rows. Similarly, limiting the latency of each decoder to  $\lambda = 2^l, l \in \mathbb{N}$  simplifies the hardware design as  $\frac{2^{m-2}}{\lambda}$  PUs are needed for processing the second-order projections excluded from matrix **D** (i.e., right-half of matrix **R**).

The objective for the ILP problem is to minimize the total number of PUs required to process the unique numbers in matrix **D** among G groups of rows with latency  $\lambda$ . To define the ILP constraints, we first introduce the following variables:

- $x_{ijk}$ : A binary variable in  $\{0,1\}$  for which  $x_{ijk} = 1$  if and only if the *i*-th group processes  $D_{jk}$ .

- $c_{ik}$ : A continuous<sup>1</sup> variable in [0, 1] for which  $c_{ik} = 1$  if the *i*-th group processes the *k*-th column  $\mathbf{D}_{\star k}$ .

- r<sub>ij</sub>: A continuous<sup>1</sup> variable in [0, 1] for which r<sub>ij</sub> = 1 if the *i*-th group selects the *j*-th row D<sub>j★</sub> to process.

- *p<sub>i</sub>*: An integer variable in ℕ indicating the number of PUs allocated for the *i*-th group.

In addition, let  $\mathcal{G} = \{1, \ldots, G\}$  denote the set of second-order decoders, and  $\mathcal{R} = \{1, \ldots, 2^{m-1}-1\}$  and  $\mathcal{C} = \{1, \ldots, 2^{m-2}-1\}$  represent the sets of rows and columns in the input matrix **D**, respectively. Now, we can formulate the projection allocation problem as follows:

n

$$\lim \sum_{i \in \mathcal{G}} p_i \tag{10}$$

s.t.

$$\lambda \ge \max_{i} \left( \frac{\sum_{k \in \mathcal{C}} c_{ik}}{p_{i}} \right), \forall i \in \mathcal{G}$$

(11)

$$\forall j, j', j'' \in \mathcal{R}, \forall k, k', k'' \in \mathcal{C},$$

$$(12)$$

$$c_{ik} \ge x_{ijk}, \ \forall i \in \mathcal{G}, \forall j \in \mathcal{R}, \forall k \in \mathcal{C},$$

(13)

$$r_{ij} \ge x_{ijk}, \ \forall i \in \mathcal{G}, \forall j \in \mathcal{R}, \forall k \in \mathcal{C},$$

(14)

$$\sum_{i \in \mathcal{G}} r_{ij} = 1, \ \forall j \in \mathcal{R}, \tag{15}$$

<sup>1</sup>We choose continuous variables because they are computationally cheaper and faster to solve using an ILP solver. All values  $c_{ik} < 1$  and  $r_{ik} < 1$  are rounded down to zero.

Fig. 4: Third-order IUPA decoder for one iteration.

$$\sum_{j \in \mathcal{R}} r_{ij} = \left\lceil \frac{|\mathcal{R}|}{|\mathcal{G}|} \right\rceil, \ \forall i \in \mathcal{G} \land i > 0,$$

(16)

$$\sum_{j \in \mathcal{R}} r_{ij} = \left\lceil \frac{|\mathcal{R}|}{|\mathcal{G}|} \right\rceil - 1, \ \forall i \in \mathcal{G} \land i = 0.$$

(17)

Each group *i* can perform  $p_i$  second-order projections (i.e., columns) per clock cycle. Constraint (11) ensures that every group completes its assigned projections whithin  $\lambda$  cycles. Constraint (12) ensures that only one out of three copies of each first-order codeword is selected among all groups since  $x_{ijk}, x_{ij'k'}$ , and  $x_{ij''k''}$  are binary variables. Constraint (13) guarantees that if  $x_{ijk} = 1$ , group *i* must include column  $\mathbf{D}_{\star k}$ . Likewise, if group *i* selects  $D_{jk}$  (i.e.,  $x_{ijk} = 1$ ), row  $\mathbf{D}_{j\star}$  should be assigned to group *i*. To avoid redundant second-order decoders, constraint (15) specifies that each row can only belong to one group. Constraints (16) and (17) ensure an even distribution of rows across groups, as previously discussed.

### IV. IUPA: HARDWARE ARCHITECTURE

In this section, we present a hardware architecture of the soft-input IUPA decoder for third-order RM codes. Fig. 4 illustrates the block diagram for the proposed soft-input IUPA decoder, which is designed based on the solution of the ILP in Section III-C. This decoder consists of G parallel units, each having three primary hardware components: for *third-order projection, second-order decoding*, and *third-order pre-aggregation*. A divider tree is also implemented to determine the final output for the aggregation step. Additionally, a register array and a control unit manage the data path and control

signals, respectively. The proposed architecture decodes the input vector L using a partially-parallel approach to adapt to the available resources and desired latency.

#### A. Third-order projection

The third-order projection component for the *i*-th group contains crossbars for  $2^{m-1}/G$  different permutations of the input vector  $\boldsymbol{L}$  based on the subspaces  $\mathbb{B}_j$  selected by the ILP (i.e.,  $r_{ij} = 1, \forall j \in \mathcal{R}$ ). A multiplexer controlled by the control unit selects one permutation at each clock cycle. The output of the multiplexer, which is the permuted input vector of LLRs is directed to the *MinSum* component. The *MinSum* component includes  $2^{m-1}$  two-input circuits to perform (4) on every pair of coordinates of the permuted LLR vector. Therefore, at each clock cycle, one projected vector of the received vector  $\boldsymbol{L}$  onto the one-dimensional subspace  $\mathbb{B}_j$ ,  $r_{ij} = 1$  is generated.

## B. Second-order decoder

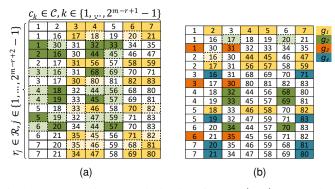

A partially-parallel second-order decoder is implemented for each group  $g_i$  to decode the second-order projected vector generated by the third-order projection component. This decoder consists of  $p_i$  PUs to handle selected secondorder projections for the *i*-th group of rows (i.e., the selected columns  $c_{ik} = 1, \forall k \in C$ ). The ILP output may not always provide a perfect solution. For instance, Fig. 5a illustrates an output of the ILP for an RM(5,3) code with G = 2and  $\lambda = 2$ . In this example, group  $q_1$ , illustrated in yellow, covers columns  $\{3, 4, 6, 7\}$  and rows  $\{1, 2, 5, 7, 10, 13, 14, 15\}$ . Although all columns  $\{3, 4, 6, 7\}$  are selected in rows  $\{1, 5, 15\}$ , the other rows assigned to this group do not select all the columns. In such cases, the second-order decoder processes all selected columns for all the second-order vectors dedicated to it. This may lead to the presence of some duplicate first-order codewords, such as codeword 18, and the other duplicate codewords highlighted in light colors with dashed lines. Nevertheless, this potential overlap simplifies the control unit and is small in practice. Notably, reducing the number of rows that are grouped together decreases the number of duplicate codewords. Consequently, a higher number of secondorder decoders (i.e., a higher G) results in fewer duplicate codewords. For instance, in Fig. 5b, where G = 4 and  $\lambda = 2$ , only 3 duplicate second-order codewords are required compared to 25 in the previous case.

The implementation of each PU in the proposed decoder is similar to [36]. Within each PU, there exists a second-order projection unit (*ProjU*), one FOD, and a second-order preaggregation unit (*PreAggU*). Based on the ILP output, each group  $g_i$  performs second-order projections denoted by  $\mathbb{B}_k$  according to the columns selected (i.e.,  $c_{ik} = 1$ ) for that group. Therefore, each PU dedicated to  $g_i$  must accommodate projection circuits for  $\lambda$  different second-order projections, such that  $\left[\frac{\sum_{k \in C} c_{i,k}}{\lambda}\right] = p_i$ . Consequently, the second-order projection for the projected vector  $L_i$ , generating  $\lambda$  first-order codewords in  $\lambda$  clock cycles due to the pipe-lined implementation. Subsequently, the generated first-order codewords are decoded

Fig. 5: Output of ILP optimization for RM(5,3) code with different G. (a) G = 2 and (b) G = 4.

using the FOD, as in [36]. Following this, the second-order preaggregation unit prepares the output of the FOD to compute the average LLR over all second-order vectors processed by group  $g_i$  as defined in (5). Moreover, in order to achieve the desired latency  $\lambda$ , each group  $g_i$  is also equipped with  $\frac{2^{m-2}}{\lambda}$  extra PUs (highlighted in red in Fig. 4) only for the second-order projections corresponding to  $\mathbb{B}_i$  where  $i \in \{2^{m-2}, \ldots, 2^{m-1}\}$ . These projections always result in unique first-order codewords, as illustrated in the right half of the matrix **R** in Fig. 3.

The non-pruned IPA decoder always uses  $2^m - 1$  inputs to compute the average, so [36] used a divider tree for this purpose. However, when the number of inputs is not a power of two, an alternative method is required for averaging. The objective in the aggregation step (5) is to compute the average as the new estimation for the LLR values of the decoded vector for the subsequent iteration. In the IUPA framework, there are no additional iterations for internal levels. Thus, the goal of the aggregation step for second-order codewords is to determine the sign of the average to finalize decoding at this level and derive the binary decoded vector as the output. Consequently, the average can be replaced by a simple summation since they have the same sign. To this end, the output of the PUs for the initial segment of group  $q_i$ , which processes the projections selected from the ILP output, are inserted into a full-precision adder tree as depicted in Fig. 4.

However, the output of the PUs for the second segment of group  $g_i$  (highighted in red) is directed to a divider tree initially to compute the average of  $2^{m-2-l}$  decoded codewords. The divider tree is selected due to its low hardware requirement compared to a full-precision adder tree. To ensure that the output of the divider tree has the same numerical impact on the final average of this group as the output of the adder tree, we need to multiply it by  $2^{m-2-l}$ . This is achieved by appending m-2-l zero bits to the right of the output of divider tree. To derive the final output for each second-order decoder, we must accumulate the results from the first and second segments using the adder tree depicted in Fig. 4. Finally, a hard-decision is made based on the output of the adder for the *i*-th group to estimate the binary codeword  $\hat{c}_i$  for the next level.

# C. Third-order pre-aggregation

The third-order pre-aggregation unit follows the design of the second-order pre-aggregation unit [36]. Similar to the projection unit, the crossbars described in Section II-C are designed to perform appropriate permutations based on the subspaces  $\mathbb{B}_j$  chosen for group  $g_i$  from the ILP result (i.e.,  $r_{ij} = 1$ ).

# D. Divider tree

In IUPA decoding for third-order RM codes, there are always  $2^{m-2} - 1$  third-order pre-aggregated vectors. In our proposed IUPA decoder, we introduce an extra dummy allzero vector generated from running the second-order decoder for the additional row added to the output of the ILP for the group with  $2^{m-1-\log_2(G)} - 1$  rows. Consequently, there are  $2^{m-1}$  pre-aggregated vectors to average, which we can average with the divider tree used in the IPA decoder, shown in Fig. 1. Considering that we require at least two groups for the third-order IUPA decoder, more than one input is available at every clock cycle for the divider. Additionally, based on the constraints defined in Section III-C for the number of groups, the divider tree receives a power-of-two number of inputs at each clock cycle. Therefore, we can replace the shift registers depicted in Fig. 1 with standard registers for the first  $\log_2(G)$ levels of the divider tree. Thus, we have  $2^{\log_2(G)-l}$  two-input standard registers at first  $\log_2(G)$  levels. These registers are activated with the valid output of the pre-aggregation unit. We maintain the sequential part of the divider tree operating with shift registers for the last  $m - \log_2(G)$  levels of the dividing. The shift register placed in the first level of the sequential part, which is the  $(m - \log_2(G))$ -th level, is activated with the valid signal of the *pre-aggregation* unit delayed by  $\log_2(G)$  clock cycles. The activation signals for the remaining shift registers are generated by the control unit.

## E. Register array

In Fig. 4, each second-order decoder has a register array responsible for storing the LLR values of the second-order codewords entering that decoder. This array is crucial for the pre-aggregation step which requires the LLRs of second-order codewords as shown in (5). In a pipelined structure, registers are necessary to preserve this vector across stages for each PU. To minimize area, all PUs within a group share a register array with read and write operations managed by a central control unit. As a result, the requirement for transporting this vector across pipeline stages is eliminated, and this saves multiple registers. The depth of this array is:

$$D_{\text{RA2nd}} = \left| \frac{l_{\text{agg2nd}}}{\lambda} \right| + 1, \tag{18}$$

where  $l_{agg2nd}$  is the number of pipeline stages from generating a new second-order vector until the pre-aggregation unit in the PU. Similarly, a register array is essential for the third-order level due to the same requirement. The depth of this array is:

$$D_{\text{RA3rd}} = \left\lceil \frac{l_{\text{agg3rd}}}{\lambda \times n/2 \times G} \right\rceil + 1,$$

(19)

where  $l_{agg3rd}$  is the length of pipeline stages from the insertion of a new vector until it reaches the third-order pre-aggregation

Fig. 6: Block diagram of CPA decoder for one iteration.

unit. For most configurations,  $D_{RA3rd} = 2$ , as the denominator of the fraction in (19) exceeds its nominator.

### F. Throughput and latency

In the proposed third-order IUPA decoder configured with the output of the ILP model with input parameters G and  $\lambda$ , a new codeword with a block length of n can be inserted every  $\frac{n \times \lambda}{2G}$  clock cycles. Therefore, the throughput is:

$$\text{Throughput}_{\text{Mbps}} = \frac{2G \times \text{Frequency}}{\lambda}, \quad (20)$$

where the frequency is given in MHz. The latency of our decoder in clock cycles is given by:

$$t(m,3) = t_{\text{proj}} + t_{\text{group}} + t_{\text{preAgg}} + \left\lceil \frac{(2^{m-1}-1)\lambda}{G} \right\rceil + m, \quad (21)$$

where  $t_{\text{proj}} = 1$  and  $t_{\text{preAgg}} = 1$  are the latencies of the projection and pre-aggregation unit, respectively.  $t_{\text{group}}$  is the latency of the group or the second-order decoder:

$$t_{\text{group}} = (t_{\text{proj}} + t_{\text{FOD}} + t_{\text{preAgg}}) + \lambda + 1, \quad (22)$$

where  $t_{\text{FOD}}$  is the latency of first-order decoder and equals 3 or 4, depending on the block-length of the target RM code [36].

#### V. CPA: HARDWARE ARCHITECTURE

If we consider the number of first-order decodings as a proxy for the computational complexity of IUPA decoding, the complexity of CPA decoding is identical to IUPA decoding. However, the question about which decoder is more efficient in terms of hardware implementation was left open by [32]. To this end, in this section, we propose an efficient CPA decoding hardware architecture in order to compare CPA and IUPA.

# A. Architecture

As discussed in Section II-D, the CPA decoder projects the received LLR vector L onto (r-1)-dimensional subspaces to construct first-order codewords. Therefore, it involves a single projection level, a first-order decoding step, and subsequent aggregation. Fig. 6 illustrates our proposed CPA decoder. The architecture follows the design of IUPA and IPA decoders, including p PUs, each with a projection unit, FOD, and a pre-aggregation unit. Similar to the IPA and IUPA decoders, we impose a constraint on the number of PUs, limiting p to be a divisor of  $\binom{m}{r-1}_2$  to simplify the control unit.

1) PU: Similar to the IUPA decoder, the projection unit in each PU of the CPA decoder consists of modules for reordering the coordinates of the input LLR vector and calculating the MS operation. The reordering module uses  $\frac{\binom{m}{r-1}_2}{p}$  crossbars to rearrange the coordinates of the input vector L. This step groups the coordinates according to their corresponding (r-1)-dimensional subspaces, with each group containing  $2^{r-1}$  coordinates. As shown in Fig. 6, the MS operation is implemented in the *fsMinSum* component. This module carries out the MS calculation described in (4), determining the minimum absolute value along with its index, the sign, as well as the second minimum absolute value. To perform the sorting process, we use the SortingNet sub-component, which is based on a pruned sorting network called tree structure (TS) proposed in [40]. This component finds the first and second minimum, denoted by  $f_{\min}$  and  $s_{\min}$ , respectively, among the absolute value of the inputs of the fsMinSum component as well as the index of the first absolute minimum, denoted by I.

The first minimum found by the *SortingNet* component is sent to the FOD component, while the second minimum goes to the MS extension unit *MSEU* to prepare the input for the pre-aggregation step. To estimate the coordinate  $\hat{L}(z)$  during the aggregation step as described in (7), we perform an MS operation on the vector L, considering the coordinates indexed by the elements of the coset T, except for the one indexed by z. This is similar to the projection step in (3), but excluding the coordinate indexed by z. The MS operation in (7) can be broken into two parts:

$$\min_{z_j \in T-z} \{ |L(z_j)| \} = \begin{cases} |f_{\min}|, & \text{if } I \neq z, \\ |s_{\min}|, & \text{if } I = z \end{cases}.$$

(23)

$$\prod_{z_j \in T-z} \operatorname{sign}\left(L\left(z_j\right)\right) = \left(\prod_{z_j \in T} \operatorname{sign}\left(L\left(z_j\right)\right)\right) \oplus \operatorname{sign}\left(L\left(z\right)\right) \quad (24)$$

A multiplexer selects between  $f_{\min}$  and  $s_{\min}$ , using I as the selector to implement (23). Additionally, equation (24) can be implemented with an XOR gate with two inputs, the sign output from *fsMinSum* component and the binary vector  $L_{sgn}$ , containing the sign bits from the coordinates of the input LLR vector L. Considering the above, we can rewrite (7) as:

$$\hat{L}(z) = \frac{1}{n_p} \sum_{i=1}^{n_P} -1^{\hat{c}_{/\mathbb{B}_i}([T])} \boldsymbol{L}_{\text{preAgg}}(z),$$

(25)

where  $L_{\text{preAgg}}$  is a vector of LLRs, for which the absolute values are calculated based on (23), and the signs are determined based on (24). We need to keep  $L_{\text{preAgg}}$  for the pre-aggregation unit

during the pipeline stages of FOD, which typically requires 3 to 4 clock cycles depending on the code blocklength. As a result, the pipeline register array consisting of three or four registers, where the output of each register serves as the input for the subsequent register as depicted in Fig. 6.

To implement the aggregation step, we follow the design principles of the IPA and IUPA decoders, which break this step into two sub-steps. In the first sub-step, the value inside the summation in (25) is calculated. This is done by using the decoded binary vector  $\hat{c}_{/\mathbb{B}_i}$ , which is the output of the FOD, along with the  $L_{\text{preAgg}}$  vector in the pre-aggregation unit. As explained in Section II-C, the term  $-1^{\hat{c}_{/\mathbb{B}_i}([T])}L_{\text{preAgg}}(z)$  can be implemented with a component calculating the two's complement of its input. The input to this unit is the  $L_{\text{preAgg}}$  vector, with the enable port controlled by  $\hat{c}_{/\mathbb{B}_i}$ . This functionality is managed by the *TwosCom* subunit of the pre-aggregation unit. Additionally, because the coordinates in  $L_{\text{preAgg}}$  are reordered in the projection unit, we need to restore them to their original order using the *ReArrange* unit.

2) Average: To finalize the aggregation step, we take the average of  $\binom{m}{r-1}_2$  estimations, which requires division. However, since the final decoded output is determined by the sign of the average, we can simply add up all estimated vectors instead. Since there are p PUs, we can insert p inputs into the adder at each clock cycle. This structure allows us to perform the additions using an adder tree, as depicted in Fig. 6. The output of the adder tree feeds into an accumulator, calculating the final summation every  $\binom{m}{r-1}_2/p$  clock cycles. Both the adder tree and the accumulator can be implemented with either full-precision or saturated adders with configurable precision.<sup>2</sup>

Fig. 6 illustrates the hardware for one iteration of CPA decoding. To implement additional iterations, this architecture can be replicated as needed, with the output of each iteration being the input to the next iteration. It is essential to maintain a limited bit-width for the input of each subsequent iteration. If each LLR is represented by Q bits, then the output from the accumulator at the end of each iteration is saturated to fit within these Q bits for the next iteration.

#### B. Throughput and latency

In our CPA decoder with p PUs, a new codeword of length n can be inserted into the pipeline every  $\frac{\binom{m}{r-1}_2}{p}$  clock cycles. Hence, the throughput of the CPA decoder is:

Throughput<sub>Mbps</sub> =

$$\frac{p \times \text{Frequency}}{\binom{m}{r-1}_2} \times n,$$

(26)

where the frequency is given in MHz. Furthermore, the latency of one iteration of the CPA decoder can be expressed as:

$$t_{\text{CPA}} = 1 + t_{\text{proj}} + t_{\text{FOD}} + t_{\text{preAgg}} + t_{\text{Add}} + \frac{\binom{m}{(r-1)_2}}{p}.$$

(27)

Similar to IUPA,  $t_{\text{proj}} = t_{\text{preAgg}} = 1$ , and  $t_{\text{FOD}}$  is 3 or 4 clock cycles, depending on the code block length.  $t_{\text{Add}}$  represents the latency of the parallel adder tree for p inputs and  $\log_2 p$  stages, and its value is 1 or 2, depending on p.

<sup>2</sup>This choice is discussed further in Section VI-A4.

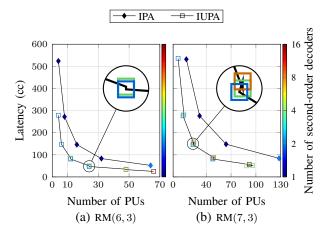

Fig. 7: Latency-resource usage trade-offs for IPA and ILP-aided IUPA decoding for (a) RM(6,3) and (b) RM(7,3)

#### VI. SIMULATION AND IMPLEMENTATION RESULTS

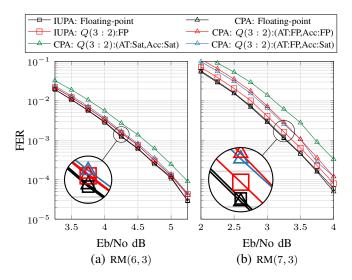

In this section, we present the simulation results for the frame error rate (FER) of the proposed IUPA and CPA decoders, followed by the synthesis results.

## A. Simulation results

In this section, we present the results of the ILP described in Section III-C for various parameters. We analyze different number of groups and delays to provide a detailed trade-off between latency and resource usage. Additionally, we compare the simulation results of the ILP-aided IUPA decoder with the IPA and CPA decoding methods. We also explore different numbers of iterations and quantization bit-widths to find an efficient configuration for the hardware implementation.

1) Latency-resource usage trade-offs: Fig. 7 illustrates the relationship between the per-iteration latency and the resource usage (measured using the number of PUs) for the IPA and ILP-aided IUPA decoder applied to RM(6, 3) and RM(7, 3) codes. For IUPA, each color indicates the number of second-order decoders (i.e., group G). To solve the ILP for the IUPA decoder, we use a cluster with 64 CPU cores at a clock speed of 2.6 GHz and a total memory of 512 GB, using Gurobipy (v10.0.2) as the ILP solver. The execution of the solver was set to stop if the solver did not find a new feasible solution with improved number of PUs within six hours.

The results show that the number of PUs required for the IUPA decoder for third-order RM codes is nearly one-third of that needed for the IPA decoder at similar latencies, which aligns with our initial expectations discussed in Section II-E. Based on (8), one-third of first-order codewords are generated in IUPA decoding for RM(m,3) codes compared to IPA. As shown in Fig. 7, we observe a similar gain with our proposed hardware-friendly approach for even distribution of the unique projections. Some points on the Pareto front for the IUPA decoder overlap, indicating identical latencies and number of PUs, but a different number of groups. It is essential to consider both the number of PUs and the number of second-order decoders in hardware implementations since both impact resource usage. As discussed further in

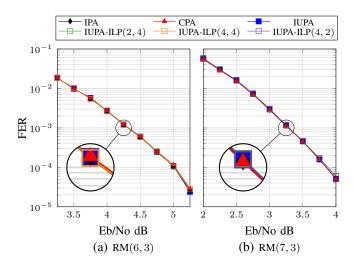

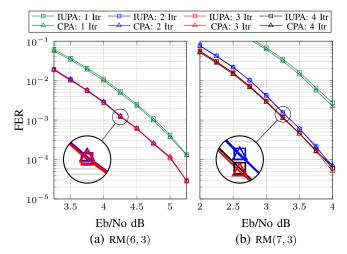

Fig. 8: Comparison of different flavours of IPA, IUPA, and CPA for Reed-Muller codes over AWGN channel.

Section VI-B, configurations with fewer groups are smaller than those with more groups, even when the number of PUs is the same. This is because each group requires a separate second-order decoder, along with its control unit and register arrays. Moreover, achieving extremely low latency requires high parallelism, leading to a higher number of groups. Therefore, simply decreasing the input parameter  $\lambda$  in the ILP formulation is insufficient for achieving very low latency, since the total latency measured in number of clock cycles is also influenced by the number of groups.

2) IUPA vs. CPA vs. IPA: Fig. 8 shows the FER for the floating-point IPA, CPA, and IUPA decoders for RM(6,3) and RM(7,3) codes. For all decoders, the maximum number of iterations  $N_{\text{max}}$  is set to  $\lceil \frac{m}{2} \rceil$  [25]. As shown for both codes, CPA and IUPA decoding exhibit the same error-correcting performance, which is comparable to the IPA decoding without pruning. Additionally, the ILP-aided IUPA with different values for  $(\lambda, G)$ , which result in varying numbers of duplicate first-order codewords as explained in Section IV-B, has the same FER as the standard IUPA with only unique first-order codewords. This result is expected because the duplicate first-order codewords do not add new information and thus neither improve nor degrade the performance.

3) Number of iterations: Since the number of iterations  $N_{\text{max}}$  for hardware implementation directly impacts resource requirements in our architecture, we explored reducing the number of iterations below  $\lceil \frac{m}{2} \rceil$  for the CPA and IUPA decoders. As shown in Fig. 8,  $N_{\text{max}} = 1$  results in poor performance. However, for the RM(6,3) code, the performance with  $N_{\text{max}} = 2$  is equivalent to that with  $N_{\text{max}} = 3$ , indicating that two iterations are sufficient. For the RM(7,3) code,  $N_{\text{max}} = 2$  results in a minor degradation of 0.05 dB in error-correcting performance compared to three and four iterations. Given that in our architecture the resource usage scales linearly with the number of iterations, having three iterations instead of two would increase hardware usage by approximately 50%, which is not justified by the marginal performance gain. Therefore, we also decided to proceed with

Fig. 9: Comparison of different numbers of iterations for the IUPA and CPA algorithm.

Fig. 10: FER comparison between floating-point and different fixed-point implementations of IUPA and CPA decoders.

two iterations for the IUPA and CPA decoders for RM(7,3).

4) Quantization bit-width: As the final simulation step before hardware implementation, we need to determine the quantization bit width and the precision required for adders in the CPA decoder. Similar to the IUPA decoder [36], we use 5-bit quantization for channel LLRs, with 3-bit integer and 2-bit fractional parts (represented as Q(3:2)) for IUPA and CPA decoders. Fig. 10 shows the performance of the IUPA decoder with 5-bit LLRs as inputs and full-precision (FP) internal additions wherever needed. Additionally, it shows the performance of the CPA decoder with Q(3:2) input LLRs and full precision for both the adder tree (AT) and accumulator (Acc). However, for CPA with p PUs, having fullprecision adders with  $q + \log_2(p)$  bits for the adder tree and  $q + \log_2\left(\binom{m}{r-1}_2\right)$  bits for the accumulator is costly. Therefore, the adder tree and accumulator defined in Section V-A2 should be implemented to saturate to a certain value with a limited number of bits in case of overflow, instead of using full

precision. The simplest option is to saturate both the adder tree and the accumulator to q bits. However, this approach does not provide good error-correcting performance, as shown in Fig. 10. After several simulations with different quantization levels for the CPA adders, we observed that using a full-precision adder tree with  $q + \log_2(p)$  bits of quantization for p inputs and a saturating (Sat) accumulator yields a FER close to that of the full-precision CPA. We examined different values of p (i.e., different numbers of PUs), all showing similar performance. The plots for both RM(6, 3) and RM(7, 3) codes in Fig. 10 use p = 7, with an 8-bit full-precision adder tree and a saturating accumulator that saturates to  $\pm 2^7$  in case of overflow.

#### B. ASIC synthesis results

In this section, we present synthesis results for our proposed soft-input IUPA and CPA decoders, and we compare them to the IPA decoder [36]. We synthesized the decoders using Cadence Genus with an STM 28nm FD-SOI technology, operating in the slow-slow corner at 25°C. We also conducted gate-level (GL) simulations by generating a standard delay file (SDF) from synthesis to achieve precise power measurements. This SDF was used for GL simulations in Cadence Xcelium. Moreover, we included the switching activity file obtained from the GL simulation in our analysis for power estimation. All decoders have been implemented for 5-bit input LLRs, i.e., Q(3:2), and two decoding iterations. For the CPA decoder with p PUs, the adder tree is implemented with full precision using 5 + $\log_2(p)$  bits and the accumulator with saturation to  $\pm 2^{4+\log_2(p)}$ . Additionally, the output of the first iteration is saturated to  $\pm 2^4$ for the second iteration of the CPA decoder.

Table I and Table II show the synthesis results for RM(6,3)and RM(7,3) codes, respectively. We provide synthesis results for different numbers of PUs (with various  $\lambda$  and G) of the IUPA decoder to show the trade-off between area and power consumption, latency, and throughput. Table I demonstrates that the area usage varies for the IUPA decoder when the number of groups differs, despite similar latency, throughput, and the same number of PUs. More specifically, with 12 PUs for the IUPA decoder for the RM(6,3) code, we have two configurations for  $(\lambda, G)$ : (2, 4) and (4, 8). The ILP optimization for both ended up with 12 PUs, and they have similar throughput and latency after implementation. However, the area usage for the one with G = 4 is 34% higher than the one with G = 2. As explained earlier, each second-order decoder requires its own control unit and register array, so a higher value for G, or a higher number of second-order decoders, results in higher resource usage. Therefore, when multiple configurations share the same location in the latency Pareto chart depicted in Fig. 7, one should always choose the one with fewer groups.

Additionally, compared to the IPA decoder, approximately one-third of the PUs are needed in the IUPA for a comparable throughput and latency as shown in Table I and Table II. However, the number of second-order decoders also affects the resource usage. Therefore, the resource usage reduction in the IUPA with a higher number of second-order decoders is limited to a maximum of 54% compared to the IPA with similar latency and throughput for both RM(6, 3) and RM(7, 3)

TABLE I

Synthesis results for our proposed IUPA and CPA decoders compared to SIPA for RM(6, 3) code.

| $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                          | IPA [36]                   |                            |                               |                                                  | RM(6, 3)<br>IU                                                               | PA                                                                          | CPA                        |                              |                            |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|-------------------------------|--------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------|------------------------------|----------------------------|

|                                                                                                                                | 16<br>1<br>-               | 32<br>1<br>-               | 64<br>2<br>-                  | $ \begin{array}{c} 6 \\ 2 \\ (2,8) \end{array} $ | $     \begin{array}{c}       12 \\       2 \\       (2, 4)     \end{array} $ | $     \begin{array}{c}       12 \\       4 \\       (4,8)     \end{array} $ | $24 \\ 2 \\ (2, 2)$        | 7<br>-<br>-                  | 21<br>-<br>-               |

| Clock Rate (MHz)<br>Latency (cc)<br>Latency (µs)<br>Throughput (Mbps)                                                          | 714<br>294<br>0.411<br>357 | 714<br>168<br>0.235<br>714 | $714 \\ 106 \\ 0.148 \\ 1428$ | 714<br>294<br>0.411<br>357                       | $714 \\ 164 \\ 0.229 \\ 714$                                                 | 714<br>170<br>0.238<br>714                                                  | 714<br>98<br>0.137<br>1428 | $500 \\ 202 \\ 0.404 \\ 344$ | 500<br>78<br>0.156<br>1032 |

| $\begin{array}{l} \textbf{Area} \ \left( mm^2 \right) \\ \textbf{Area} \ \textbf{Eff.} \ \left( Gbps/mm^2 \right) \end{array}$ | $0.38 \\ 0.94$             | $0.61 \\ 1.17$             | $1.21 \\ 1.18$                | $0.25 \\ 1.43$                                   | $0.32 \\ 2.16$                                                               | $0.43 \\ 1.66$                                                              | $0.47 \\ 3.03$             | $0.51 \\ 0.67$               | $1.21 \\ 0.85$             |

| Power (mW)<br>Energy (pJ/b)                                                                                                    | 317<br>888                 | 505<br>707                 |                               | $175 \\ 490$                                     | $256 \\ 358$                                                                 | $316 \\ 442$                                                                | 422<br>295                 | $355 \\ 1031$                | 828<br>802                 |

TABLE IISynthesis results for our proposed IUPA and CPA decoders<br/>compared to SIPA for RM(7,3) code.

| Code                    | RM(7,3)  |       |       |         |        |        |       |       |

|-------------------------|----------|-------|-------|---------|--------|--------|-------|-------|

| Decoder                 | IPA [36] |       |       | ,       | IUPA   | CPA    |       |       |

| PU                      | 16       | 32    | 64    | 6       | 12     | 24     | 7     | 21    |

| Second-Order Decoder    | 1        | 1     | 1     | 2       | 2      | 2      | -     | -     |

| $(G, \lambda)$          | -        | -     | -     | (2, 16) | (2, 8) | (2, 4) | -     | -     |

| Clock Rate (MHz)        | 625      | 625   | 625   | 625     | 625    | 625    | 465   | 465   |

| Latency (cc)            | 1060     | 556   | 304   | 1072    | 552    | 292    | 778   | 272   |

| Latency (µs)            | 1.696    | 0.890 | 0.486 | 1.715   | 0.883  | 0.467  | 1.672 | 0.585 |

| Throughput (Mbps)       | 157      | 314   | 628   | 156     | 312    | 625    | 156   | 469   |

| Area (mm <sup>2</sup> ) | 0.84     | 1.48  | 2.60  | 0.62    | 0.79   | 1.18   | 1.23  | 2.72  |

| Area Èff. $(Gbps/mm^2)$ | 0.19     | 0.21  | 0.24  | 0.25    | 0.39   | 0.53   | 0.13  | 0.17  |

| Power (mW)              | 676      | 1302  | 2221  | 377     | 562    | 906    | 641   | 1700  |

| Energy (pJ/b)           | 4305     | 4146  | 3536  | 2417    | 1801   | 1445   | 4109  | 3624  |

codes. However, for the configuration with the same number of second-order decoders (e.g., IUPA for RM(6,3) with 24 PUs and  $(G, \lambda) = (2, 2)$  and IPA with 64 PUs), the reduction in resource usage, which is approximately 62%, aligns with the reduction in the number of PUs.

Moreover, we synthesized the CPA decoder with 7 and 21 PUs for both RM(6,3) and RM(7,3) codes to achieve similar throughput and latency with the IPA and IUPA decoders, enabling a fair comparison. The CPA decoding for thirdorder RM codes projects the received vector directly into firstorder vectors using a 2-dimensional subspace. Consequently, the projection and the pre-aggregation units in the CPA are significantly larger than those in the IPA and IUPA decoders, as detailed in Section V-A1. Following the design principle for IUPA and IPA decoder, we allocate one clock cycle for the projection unit. Due to its larger size compared to its counterpart in the IUPA and IPA decoders, the critical path is longer and the frequency is lower. Allocating more clock cycles would necessitate additional registers in our pipelined architecture, leading to increased resource usage. Therefore, it is a trade-off between resource usage and frequency. Due to the substantial number of registers required, we opted to allocate a single clock cycle for the projection unit.

The synthesis results for both RM(6,3) and RM(7,3) codes demonstrate that while the CPA exhibits up to a 66% decrease in the number of PUs compared to the IPA for similar latency, it does not result in a substantial reduction in area. This is due to the fact that each PU in the CPA is significantly larger than in the IPA. Furthermore, the IPA decoder shows better overall area and energy efficiency than the CPA decoder. Specifically, the synthesis results for both RM(6,3) and RM(7,3) reveal that the IPA with 64 PUs outperforms the CPA with 21 PUs in terms of latency, area, and energy efficiency.

## VII. CONCLUSION

In this work, we addressed the challenges associated with applying the unique projection selection method to the hardware implementation of the IPA decoder and proposed a solution based on an ILP formulation. Our ILP-based solution demonstrated a significant reduction in the number of PUs compared to the traditional IPA decoder. We also introduced a pipelined and flexible architecture for the soft-input IUPA decoder, allowing for various configurations that balance area, power consumption, latency, and throughput. Synthesis results demonstrated that the IUPA decoder outperforms the IPA decoder in terms of resource usage, showing a potential reduction of up to 60% for certain configurations. This flexible architecture can also provide a robust foundation for further pruning and optimization of the IPA decoder. Additionally, we implemented the soft-input CPA decoder, which has the same algorithmic complexity as the IUPA decoder to compare hardware usage. Synthesis results illustrate that CPA decoder is about twice as large as IUPA and 1.3 times larger than IPA for similar latency and throughput. Our findings are a reminder that algorithmic optimizations do not always translate to more efficient hardware.

#### REFERENCES

- S. Miao et al., "Trends in channel coding for 6G," Proceedings of the IEEE, pp. 1–23, 2024.

- [2] G. Durisi, T. Koch, and P. Popovski, "Toward massive, ultrareliable, and low-latency wireless communication with short packets," *Proceedings of the IEEE*, pp. 1711–1726, Sep 2016.

- [3] N. H. Mahmood *et al.*, "White paper on critical and massive machine type communication towards 6G," *arXiv* 2004.14146, 2020.

- [4] R. Gallager, "Low density parity check codes," *Cambridge*, vol. 1, pp. 1–73, 1963.

- [5] C. Berrou and A. Glavieux, "Near optimum error correcting coding and decoding: Turbo-codes," *IEEE Transactions on communications*, vol. 44, no. 10, pp. 1261–1271, 1996.

- [6] E. Arikan, "Channel polarization: A method for constructing capacityachieving codes for symmetric binary-input memoryless channels," *IEEE Transactions on Information Theory*, vol. 55, no. 7, pp. 3051–3073, jul 2009.

- [7] I. Tal and A. Vardy, "List decoding of polar codes," *IEEE Transactions on Information Theory*, vol. 61, no. 5, pp. 2213–2226, 2015.

- [8] I. Reed, "A class of multiple-error-correcting codes and the decoding scheme," *Transactions of the IRE Professional Group on Information Theory*, vol. 4, no. 4, pp. 38–49, Sep 1954.

- [9] D. E. Muller, "Application of boolean algebra to switching circuit design and to error detection," *Transactions of the IRE Professional Group on Electronic Computers*, vol. EC-3, no. 3, pp. 6–12, Sep 1954.

- [10] E. Arikan, "A performance comparison of polar codes and Reed-Muller codes," *IEEE Communications Letters*, vol. 12, no. 6, pp. 447–449, 2008.

- [11] E. Arikan, "A survey of Reed-Muller codes from polar coding perspective," in *IEEE Information Theory Workshop on Information Theory (ITW)*, 2010, pp. 1–5.

- [12] I. Tal and A. Vardy, "How to construct polar codes," *IEEE Transactions on Information Theory*, vol. 59, no. 10, pp. 6562–6582, 2013.

- [13] P. Trifonov, "Efficient design and decoding of polar codes," *IEEE Transactions on Communications*, vol. 60, no. 11, pp. 3221–3227, 2012.

- [14] S. Kudekar *et al.*, "Reed–Muller codes achieve capacity on erasure channels," *IEEE Transactions on Information Theory*, vol. 63, no. 7, pp. 4298–4316, Jul. 2017.

- [15] E. Abbe, A. Shpilka, and A. Wigderson, "Reed–Muller codes for random erasures and errors," in *Annual ACM Symposium on Theory of Computing*, Jun 2015.

- [16] G. Reeves and H. D. Pfister, "Reed–Muller codes on bms channels achieve vanishing bit-error probability for all rates below capacity," *IEEE Transactions on Information Theory*, vol. 70, no. 2, pp. 920–949, 2024.

- [17] V. M. Sidel'nikov and A. S. Pershakov, "Decoding of Reed–Muller codes with a large number of errors," *Problemy Peredachi Informatsii*, vol. 28, pp. 80–94, 1992.

- [18] B. Sakkour, "Decoding of second order Reed–Muller codes with a large number of errors," in *IEEE Information Theory Workshop*, Aug 2005.

- [19] I. Dumer, "Recursive decoding and its performance for low-rate Reed–Muller codes," *IEEE Transactions on Information Theory*, vol. 50, no. 5, pp. 811–823, May 2004.

- [20] I. Dumer and K. Shabunov, "Soft-decision decoding of Reed–Muller codes: Recursive lists," *IEEE Transactions on Information Theory*, vol. 52, no. 3, pp. 1260–1266, Mar 2006.

- [21] E. Santi, C. Hager, and H. D. Pfister, "Decoding Reed-Muller codes using minimum-weight parity checks," in *IEEE International Symposium* on Information Theory (ISIT), 2018, pp. 1296–1300.

- [22] K. Ivanov and R. Urbanke, "Permutation-based decoding of Reed-Muller codes in binary erasure channel," in 2019 IEEE International Symposium on Information Theory (ISIT), 2019, pp. 21–25.

- [23] S. A. Hashemi, N. Doan, M. Mondelli, and W. J. Gross, "Decoding Reed–Muller and polar codes by successive factor graph permutations," in *IEEE International Symposium on Turbo Codes and Iterative Information Processing (ISTC)*, Dec 2018.

- [24] M. H. Ardakani, M. Hanif, M. Ardakani, and C. Tellambura, "Fast successive-cancellation-based decoders of polar codes," *IEEE Transactions on Communications*, vol. 67, no. 7, pp. 4562–4574, 2019.

- [25] M. Ye and E. Abbe, "Recursive projection-aggregation decoding of Reed–Muller codes," *IEEE Transactions on Information Theory*, vol. 66, no. 8, pp. 4948–4965, Aug 2020.

- [26] Y. Be'ery and J. Snyders, "Optimal soft decision block decoders based on fast Hadamard transform," *IEEE Transactions on Information Theory*, vol. 32, no. 3, pp. 355–364, May 1986.

- [27] J. Li, S. M. Abbas, T. Tonnellier, and W. J. Gross, "Reduced complexity RPA decoder for Reed–Muller codes," in *IEEE International Symposium* on Topics in Coding, Sep 2021.

- [28] D. Fathollahi, N. Farsad, S. A. Hashemi, and M. Mondelli, "Sparse multi-decoder recursive projection aggregation for Reed-Muller codes," in *IEEE International Symposium on Information Theory*, Jul. 2021.

- [29] J. Voigt, H. Jaekel, and L. Schmalen, "Semi-deterministic subspace selection for sparse recursive projection-aggregation decoding of Reed-Muller codes," in *International ITG Workshop on Smart Antennas and Conference on Systems, Communications, and Coding (WSA & SCC)*, 2023, pp. 1–6.

- [30] M. Lian, C. Hager, and H. D. Pfister, "Decoding Reed–Muller codes using redundant code constraints," in *IEEE International Symposium on Information Theory (ISIT)*, Jun. 2020.

- [31] M. Hashemipour-Nazari, K. Goossens, and A. Balatsoukas-Stimming, "Multi-factor pruning for recursive projection-aggregation decoding of RM codes," in *IEEE Workshop on Signal Processing Systems (SiPS)*, Nov. 2022.

- [32] M. Hashemipour-Nazari, R. Debets, K. Goossens, and A. Balatsoukas-Stimming, "Recursive/iterative unique projection-aggregation decoding of Reed-Muller Codes," in *IEEE International Conference on Acoustics*, *Speech and Signal Processing (ICASSP)*, 2023, pp. 1–5.

- [33] Q. Huang and B. Zhang, "Pruned collapsed projection-aggregation decoding of Reed-Muller codes," arXiv:2105.11878, May 2021.

- [34] J. Li and W. J. Gross, "Optimization and simplification of PCPA decoder for Reed-Muller codes," *IEEE Communications Letters*, vol. 26, no. 6, pp. 1206–1210, Jun. 2022.

- [35] M. Hashemipour-Nazari, K. Goossens, and A. Balatsoukas-Stimming, "Hardware implementation of iterative projection-aggregation decoding of Reed–Muller codes," in *IEEE International Conference on Acoustics*, Speech and Signal Processing (ICASSP), Jun. 2021.

- [36] M. Hashemipour-Nazari, Y. Ren, K. Goossens, and A. Balatsoukas-Stimming, "Pipelined architecture for soft-decision iterative projection aggregation decoding for rm codes," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 70, no. 12, pp. 5468–5481, 2023.

- [37] Y. Ren et al., "A sequence repetition node-based successive cancellation list decoder for 5G polar codes: Algorithm and implementation," *IEEE Transactions on Signal Processing*, vol. 70, pp. 5592–5607, Oct. 2022.

- [38] M. Plotkin, "Binary codes with specified minimum distance," IRE Transactions on Information Theory, vol. 6, no. 4, pp. 445–450, 1960.

- [39] R. Green, "A serial orthogonal decoder," Jet Propulsion Laboratory (JPL) Space Programs Summary, vol. 37, pp. 247–253, 1966.

- [40] C. Wey, M. Shieh, and S. Lin, "Algorithms of finding the first two minimum values and their hardware implementation," *IEEE Transactions* on Circuits and Systems I, vol. 55, no. 11, pp. 3430–3437, 2008.