# Integration of Quantum Accelerators into HPC: Toward a Unified Quantum Platform

Amr Elsharkawy

Chair of Computer Architecture and Parallel Systems Technical University of Munich Munich, Germany amr.elsharkawy@in.tum.de Xiaorang Guo

Chair of Computer Architecture and Parallel Systems Technical University of Munich Munich, Germany xiaorang.guo@tum.de

Martin Schulz Chair of Computer Architecture and Parallel Systems Technical University of Munich Munich, Germany schulzm@in.tum.de

Abstract—To harness the power of quantum computing (OC) in the near future, tight and efficient integration of QC with high performance computing (HPC) infrastructure (both on the software (SW) and the hardware (HW) level) is crucial. This paper addresses the development of a unified quantum platform (UQP) and how it is being integrated into the HPC ecosystem. It builds on the concepts of hybrid high performance computing - quantum computing (HPCQC) workflows and a unified HPCQC toolchain, introduced in our previous work and makes the next needed step: it unifies the low-level interface between the existing classical HPC systems and the emerging quantum hardware technologies, including but not limited to machines based on superconducting qubits, neutral atoms or trapped ions. The UQP consists of three core components: a runtime library, an instruction set architecture (ISA) and a quantum control processor (OCP) micro-architecture. In particular, this work contributes a unified HPCQC runtime library that bridges the gap between programming systems built on quantum intermediate representation (QIR) standard with a novel, unified hybrid ISA. It then introduces the initial extension of an ISA and QCP micro-architecture to be platform and technology agnostic and enables it as an efficient execution platform. The UQP has been verified to ensure correctness. Further, our performance analysis shows that the execution time and memory requirements of the runtime library scale superlinearly with number of qubits, which is critical to support scalability efforts in QC hardware.

*Index Terms*—Quantum Computing, High Performance Computing, HPCQC Integration, Quantum Control Processor, Instruction Set Architecture, Unified Quantum Platform.

## I. MOTIVATION

The quantum computing (QC) paradigm offers the opportunity to tackle involved scientific problems, such as quantum chemistry simulations [1] and cryptography [2], which have been considered intractable in the classical computing sense. The research community has recently realized that tangible quantum advantage is not going to be achieved in a vacuum, but requires integrating quantum accelerators into the currently available high performance computing (HPC) systems and workflows [3]. As a consequence, novel hybrid classicalquantum systems are emerging to push the boundaries of both fields by attempting to tackle the question of "what is the optimal way of integrating quantum and classical computations on the software and the hardware level"?

One of the core approaches to achieve quantum advantage during the noisy intermediate-scale quantum (NISQ) era is via hybrid variational quantum-classical algorithms, which utilize both classical and quantum computing resources. These algorithms involve a substantial amount of communication between quantum and classical processors. In case of slow communication and high latency connection, such interaction will add a huge overhead that would eat away any advantage we gain from quantum acceleration. It, therefore, requires an efficient abstraction layer that unifies the interaction between classical and quantum machines and supports a seamless integration process. In our previous workshop paper [4], we introduce the concept of a unified hybrid HPCQC toolchain that can dampen the overhead of communication between both sides, in order to maximize the benefit of the hybrid compute resources. In this work, we take this initial idea and provide new contributions that enable the low-level integration and interfacing with the quantum accelerator and how it is realized with currently available software tools and hardware components.

To enable low-level integration, considerable efforts are currently underway to develop quantum control processors (QCPs) as close as possible to quantum processing units (QPUs) [5]–[8]. While these specialized controllers promise to deliver fast and timing-precise control to mitigate the impact of short decoherence times, the absence of unified quantum instruction set architecture (QISA) support means each currently existing quantum control processor (QCP) is limited to serving a single physical technology. Expanding this to multiple technologies is, therefore, critical, yet challenging to achieve.

To address these challenges, we propose a unified quantum platform (UQP) that abstracts away the complexities of

© 20xx IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

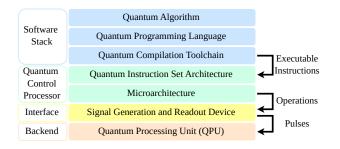

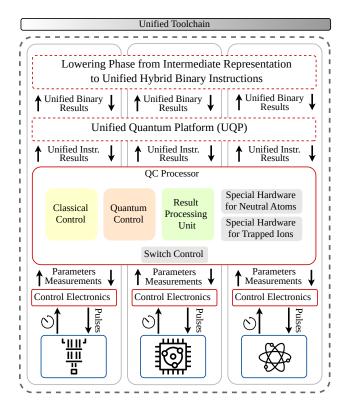

Fig. 1. Abstract representation of a full-stack quantum computer.

integrating multiple quantum modalities with classical HPC system. The UQP considers both software and hardware perspectives. Overall, the main contribution of this work is as follows:

- On the software level, the UQP introduces a runtime library that maps a quantum intermediate representation (QIR) representation of the quantum kernel to the novel unified binary instructions understood by the QCP. Moreover, the novel instruction set architecture (ISA) is capable of accommodating all instructions exposed by the various quantum hardware to the software side.

- At the backend interface of the UQP, we upgrade the QCP based on our previous work *HiSEP-Q* [5], by generalizing the architecture to also support neutral atom quantum computers. The upgraded version implements the quantum and classical control logic needed for not only initiating execution for distinct quantum hardware technologies but also post-processing the measurement results.

- Our experimental evaluations illustrate that the execution time and memory utilization of the runtime library scales super-linearly with the number of qubits. This feature guarantees the applicability of our work in large-scale quantum systems, existing and future.

The remainder of the paper is structured as follows. In Section II, we introduce the core concepts of high performance computing - quantum computing (HPCQC) integration and workflow, as well as available quantum hardware (HW) technologies and their interface to the software stack. In Section III we highlight the relevant ongoing research and the shortcomings of the currently available workflows. In Section IV we present our proposal for the HPCQC workflow of a UQP and in Section V we validate the workflow and analyze its performance properties. Finally, the work concludes with Section VI.

#### II. BACKGROUND

HPCQC is a comprehensive undertaking that must span many layers, starting from the hybrid algorithmic description, all the way to the interface between classical and quantum HWs, see Figure 1. In this section, we describe the concepts needed for HPCQC integration from different perspectives.

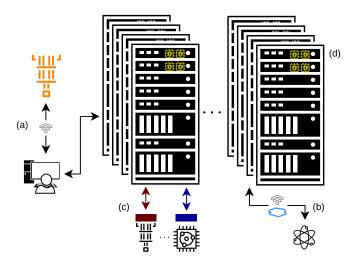

Fig. 2. HPCQC Integration Scenarios. (a) Loose Integration – Standalone, (b) Loose Integration – Co-located, (c) Tight Integration – Co-located and (d) Tight Integration – On-node.

#### A. User View on HPCQC Integration

While QC offers distinct benefits over classical computing in particular contexts, its utility is constrained by the presently available qubit count in quantum HWs and the absence of effective methods for storing, manipulating, and retrieving classical data within quantum frameworks. Consequently, the prevalent approach to leveraging QC is to deploy a quantum processing unit (QPU) as a supplementary, sophisticated accelerator that can be used for specific computational tasks [3].

1) SW-Level View on HPCQC Integration: HPCQC integration, from the software (SW) perspective, entails the design and development of programming models, execution schedulers, runtime systems, and networking approaches that not only take into consideration the core features of quantum computation, e.g., stochastic behavior and real-time feedback control, but also integrate well with existing and emerging classical computing approaches [9], [10]. The ultimate goal of the SW tools built to realize all these functionalities, is to allow for efficient and seamless integration that does not eat away the expected quantum HW advantage by overheads.

2) HW-Level View on HPCQC Integration: HPCQC integration, from the HW perspective, focuses on the physical arrangement of quantum HW and HPC infrastructure. Specifically, it considers the architecture of HPC and quantum HW elements and their interconnections [11]. In our previous work [9], [12], we have identified four integration scenarios that could co-exist as well as the technical challenges they introduce, see Figure 2. The different scenarios represent the progress of the emerging field of HPCQC integration, starting from standalone QPUs to on-node integration, which comes with the highest technical challenges.

In the NISQ era, HW vendors are investigating different technologies (e.g., superconducting materials, atoms & ions) to build a quantum HW. Each of these has unique characteristics and imposes different constraints. This fact not only

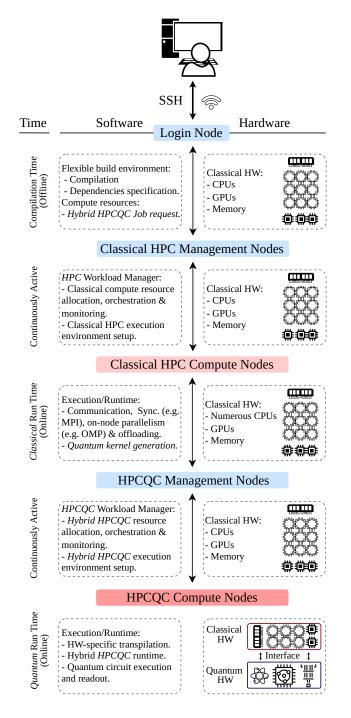

Fig. 3. Abstract HPCQC workflow. The figure shows five components: login node, HPC management node, HPC compute node, HPCQC management node and HPCQC compute node.

complicates the task of supercomputing centers that work on integrating quantum devices with their HPC systems, but also raises the bar very high for researchers who work on developing software tools that interface with such HWs.

## B. The HPCQC Workflow

Figure 3 shows an abstract representation of a hybrid HPCQC workflow. The workflow describes a sequence of steps

to perform a computation on a hybrid HPCQC system. The description highlights the location and the time of the tasks being executed. The diagram is broadly divided into three main components: first are the login and management nodes, second are the classical compute resources, and third are the hybrid HPCQC compute resources and the quantum hardware. HPC systems usually feature an external access point, often known as a login node. This node offers a versatile building environment, equipped with a package manager, enabling users to establish their necessary dependencies and choose their desired compiler or interpreter. The compiled executables and the specified resources are encapsulated within a job request, which is submitted to a workload manager. This marks the end of the *compilation time*.

During *classical run time*, the program execution starts simultaneously on the allocated classical compute nodes, where communication and synchronization occur according to the user's specifications within the program with the help of HPC libraries and frameworks, such as Message Passing Interface (MPI) and OpenMP [13], [14]. During this time, it is typical that all information (e.g., run time parameters) needed for quantum circuit generation is available. Hence, on the classical HPC nodes, quantum kernels are generated, and offloaded to the HPCQC resource manager, which then allocates the suitable resources and initiates execution which marks the start of *quantum run time*.

The details of how quantum and classical resources interplay within HPCQC compute resources during *quantum run time* is an open research question. This is because it is highly dependent on the involved classical systems, quantum systems, available level of interfacing, and how much control is exposed to the programmer (i.e., which execution model is adopted? [9]). In the process, though, the quantum circuit is optimized according to the allocated quantum hardware and offloaded to the QPU to get executed. Upon completion, the system provides the user with the job outcomes, including both classical and quantum results.

#### C. Quantum Intermediate Representation Specification (QIR)

QIR [15] is a specification that defines an intermediate representation for quantum programs, designed to bridge the gap between high-level quantum programming languages and lower-level quantum execution targets, such as quantum hardware or simulators. QIR is built upon the well-established LLVM IR, leveraging its robust, platform-agnostic framework to enable the optimization and execution of quantum programs. The goal of QIR is to provide a common interface that facilitates interoperability between different quantum programming languages and diverse quantum processing units (QPUs).

The QIR specification is actively developed and maintained by the QIR Alliance, a collaboration of industry, academia, and independent professionals. The specification is still evolving, with ongoing efforts to expand its capabilities, improve its efficiency, and enhance its compatibility with a wide range of quantum hardware and classical integration scenarios. The open-source nature of the project encourages contributions from the *HPCQC* community, fostering innovation and the adoption of best practices in software development.

# D. Quantum Hardware and Control

To achieve the full potential of quantum advantages, SW-Level and HW-Level should be seamlessly integrated, which also contributes to the fully programmable quantum computer shown in Figure 1. Although the high-level programming language can be compiled into hardware-specific instructions, direct control from the SW level to the HW level restricts the efficiency and scalability of the quantum computers [16]. Therefore, QCPs [5], [17] are proposed to act as an interface between the software and hardware layers. QCPs compile the executable binary instructions generated by compilers into a sequence of pulses to control the qubits. Positioned close to QPUs, this kind of unit is able to provide precise nanosecond timing control and features fast mid-circuit measurement support.

# III. RELATED WORK AND RESEARCH GAPS

It is evident that existing literature predominantly concentrates on the development of hybrid programming models and the seamless integration of quantum software stacks within conventional HPC environments. On the one hand, the authors of [18]-[21] have proposed language extension (i.e. C++ and Python) to integrate quantum and classical computations. Moreover, they have proposed a system-level software infrastructure that supports such extensions. These studies explore frameworks that allow quantum and classical computing resources to collaboratively address computational tasks, leveraging the strengths of each to enhance overall performance and efficiency. These efforts correspond to the software stack components of Figure 1. On the other side, data centers that host classical and quantum resources are investigating the optimal approach to build a unified software stack that supports the emerging programming models. For instance, the Leibniz Supercomputing Centre (LRZ) has proposed a vision on how the two paradigms may come together efficiently [3], [22]. Moreover, there have been other efforts investigating hybrid HPCQC hardware architectures [11] and middleware setup [23].

Despite these advancements, a noticeable gap in the research landscape is not only the *uniformity* of binary instructions across different quantum modalities, but also the software infrastructure needed to map higher-level representations to such unified binary representation. Current discussions largely bypass the challenges of creating a standardized set of binary instructions that would ensure *compatibility* and *interoperability* among varied quantum computing platforms. Such standardization would allow quantum applications, once compiled, to be executed across different quantum systems without the need for recompilation or modification, addressing a crucial bottleneck in the widespread adoption of quantum accelerators in HPC settings.

Additionally, there also exists a gap in the development of novel quantum control processors capable of handling the aforementioned standardized binary streams and providing cross-technology control, see Figure 1. To date, most existing quantum controllers [6], [8], [24]–[26] are all designed for a single physical modality. To the best of our knowledge, OpenQL [27], as proposed by Khammassi et al., stands as the sole example of an architecture capable of controlling both superconducting and semiconducting qubits. However, this design relies on the eQASM instruction set [6], which is topology-dependent and lacks scalability. Consequently, the utilization of OpenQL is limited in scenarios where qubit connectivity is unconstrained, such as in neutral atom quantum computers. Therefore, addressing these gaps could significantly streamline the deployment of quantum solutions, fostering a more integrated and versatile HPCQC landscape.

## IV. INTRODUCING A UNIFIED QUANTUM PLATFORM

The concept of a unified quantum platform is an emerging HPCQC system that consists of various building blocks including various SW tools and HW components. In the following, we highlight our focus, which is the interfacing layer between the hybrid SW toolchain and the quantum processing units. First, we describe our novel unified runtime library implementation. Then, we discuss the extension of a single technology approach and introduce a generalized ISA and QCP micro-architecture as a step toward supporting more backend modalities.

## A. Unified HPCQC Runtime Environment

In the NISQ era, no specific technology has proved itself as the superior approach to building quantum hardware. Hence, supercomputer centers are poised to have to host various QPUs based on different technologies.

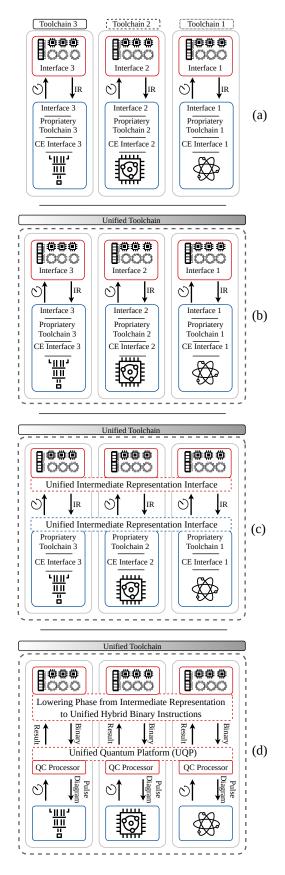

Looking at the evolution Figure 4 shows the integration development of distinct quantum accelerators into currently available HPC systems and workflows. (a) At the early stage of the emerging HPCQC field, each backend requires a standalone toolchain to map the algorithmic representation to a unique low-level representation that is understandable by the machine, (b) then, the concept of a unified toolchain has emerged, yet, it still requires providing different interfacing approaches that suit the available hardware, (c) then various efforts, including the one within the LRZ, push toward a unified intermediate representation interface where all backends accept the same languages, such as QASM and QIR, but still leave us with distinct technology stacks towards the hardware. To really provide a cross-technology platform, in this work, we propose to go to the final step, (d), which pushes the unified interface as low as the ISA level. For this, we exploit two main building blocks, developed or adopted in this work for our HPCOC approach:

1) Block 1: Unified Intermediate Representation: We first must realize a truly cross-platform intermediate representation. For this, we adopt the QIR specification as an established, platform- and vendor-neutral approach. QIR does not enforce a precise syntax; it is the responsibility of quantum hardware builders and software developers to adopt the syntax that

Fig. 4. The expected progress of cross-technology execution within an HPCQC system.

they see fit for their platform. As an initial step, we have adopted the *base profile* that only includes quantum operations and limited classical instructions. In future work, we will incorporate new instructions as they emerge from both sides of the hardware builders and the software developers.

2) Block 2: Unified Runtime Library: Building on QIR, we design and implement a unified runtime library that maps the OIR base profile representation to the novel unified ISA supported by the proposed quantum control processor, which is described below. The library is written in  $C \setminus C++$ . The runtime takes care of implementing the binary instruction corresponding to the QIR representation along with the required memory management for allocating quantum and classical registers. At the moment we only support sequential execution of the 32bit binary instructions. The library implementation addresses the time management requirements for instruction scheduling. Moreover, the runtime library is responsible for initializing the execution environment which differs according to the targeted quantum hardware. Yet, across all hardware modalities, the execution environment initialization retrieves information such as the size of both quantum and classical registers from the attributes of the QIR representation. On a different note, additional information, such as the number of shots and the specific hardware target, is provided to the runtime via the workload manager as part of the job submission call. As both the input (i.e., represented by the QIR specification) and the output (i.e., represented by the novel ISA) evolve, the runtime implementation is going to continuously be updated to support the latest setup.

### B. SW-HW Interface

The binary file generated by the runtime system, including both classic control and quantum instructions, is offloaded to the quantum control processor via a shared memory segment. The quantum control processor has an on-board ARM CPU that takes care of making the binary available to the on-board controllers, which are then used to execute the quantum circuit. While this interface is simple, it is both effective and efficient, allowing quick and easy transfer of quantum code to hardware execution.

## C. Novel Quantum Control Processor

While the runtime system, with its intermediate representation and its execution platform, can hide the already discussed differences between physical modalities – from superconducting qubits to neutral atoms and ion traps – the actual technology stack on the backend must also support this heterogeneity. However, even though the physical technologies of the platforms are different, the control theories over them have much in common. This provides us with the needed leverage to create a technology-agnostic backend architecture, which we propose in our novel system architecture for a unified control unit, illustrated in Figure 5. When selecting a physical platform to execute the algorithm, the unified toolchain compiles highlevel instructions into executable unified binary instructions. Meanwhile, the switch also selects the target modality. After

Fig. 5. System architecture of the proposed cross-technology quantum control processor.

loading the waveform configuration files for each platform, the generated executable binary sequence will then be processed on the QCP to generate the pulses (through control electronics) to control the qubits, specialized for the particular modality as defined by a respective pulse library. The pulse library itself is defined by the backend developer and, with that, ensures the needed flexibility while hiding the differences in the userfacing interface. Further, to improve efficiency, the architecture can be enhanced with specific accelerators, e.g., for handling of atoms or swap optimizations in ions, that can be used on demand. This concept of heterogeneous accelerators is well known from the development of modern multi-media and mobile processors and has been shown to be highly performing and energy efficient.

To implement this HW-Level integration, we again build on two main building blocks: a novel cross-technology control processor and a new instruction set that supports arbitrary, pulse-based technology platforms.

1) Quantum Instruction Set: A QISA functions as an interface between the compilation toolchain and the control microarchitecture. Its specifications have a significant impact on both the performance and scalability of QCPs, as well as the efficiency of high-level algorithm mapping. Given the current development state of HPCQC, where quantum computers serve as specialized accelerators alongside classical HPC systems, it becomes essential to design QISA in a way that is compatible with classical ISAs. Furthermore, to effectively

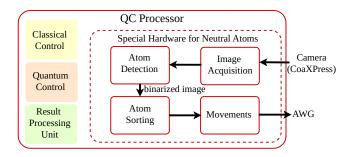

Fig. 6. Architecture of the QCP activated for neutral atom quantum computer. AWG represents an arbitrary waveform generator.

manage classical control flows, such as conditional jumps and feedback management, QISA needs to be hybrid in nature. This implies that classical and quantum instructions need to seamlessly integrate with each other.

In order to achieve this goal, we build on a QISA for superconducting systems [5], which features a hybrid instruction format and an efficient and scalable control for that modality To achieve a unified control scheme, we extend the support in this QISA beyond superconducting qubits alone. We do this by adding instructions needed on other platforms, as well as their needed support functionality, like the introduction of swap gates. In our current work, we demonstrate this by supporting both superconducting and neutral atom-based systems in a single platform and QISA.

While the fundamentals of qubit addressing and gate control remain unified, with only waveform parameters differing across platforms, we have enriched the instruction set to incorporate actions specific to neutral-atom systems. This enrichment mainly involves introducing instructions for atom preparation, such as image acquisition, atom detection, and atom resorting, which facilitate the seamless integration of neutral-atom quantum computing into the unified QISA framework. Moreover, to streamline compiler efforts and maintain consistency across platforms, these initialization instructions are strategically placed at the beginning when configuring the neutral-atom quantum computer as the target platform. Table I provides an illustration of the extended instructions, while the original QISA specification can be found in the original Hisep-Q processor [5].

TABLE I

Extended Instructions for Neutral-Atom Quantum Computer

| Function       | Description                                             |

|----------------|---------------------------------------------------------|

| Image Fetch    | Start to fetch the atom image into the memory.          |

| Atom Detection | Start to detect the atom positions and occupancy        |

| Atom Sorting   | Start to sort (rearrange) atoms to a defect-free target |

| Atom Moving    | Start to send control signals                           |

2) *Microarchitecture:* Along with the changes we have made on the QISA, we also enhance the microarchitecture accordingly. Figure 5 demonstrates the unified microarchitecture targeting cross-technology support, by adding technology technology-specific accelerator block; a corresponding functional block will be activated when a physical platform is selected, a technique readily used in the mobile and multimedia chip world in which one processor offers a variety of small custom blocks for specific target functions. Figure 6 exemplifies the microarchitecture in managing a neutral atom quantum computer. While the three core blocks overseeing classical and quantum control, along with processing intermediate results, remain consistent, a specialized hardware configuration is introduced in this scenario. Corresponding to our extended instructions, the fluorescence image, captured by an electron-multiplying charge-coupled device (EMCCD) camera, is acquired within the 'Image Acquisition' stage [28]. Subsequently, an atom detection unit, typically employing deconvolution algorithms, detects the presence of atoms. Following this, an atom-resorting algorithm is engaged to devise a strategy for arranging the atoms into a defect-free atom array. Finally, this strategy is translated into a sequence of commands instructing arbitrary waveform generators (AWGs) to manipulate the qubits efficiently. By activating and deactivating specialized hardware, our quantum controller can be switched between different platforms effectively while maintaining the same basic unified components.

#### V. EXPERIMENT AND EVALUATION

To show the correctness and the efficiency of the presented approach, we evaluate our unified system with using a hybrid workflow. First, we conduct a performance analysis to show that our implementation does not add significant run time overhead. We then validate the correctness of the generated binary instructions step-by-step to guarantee the correspondence to the high-level algorithmic description.

## A. Performance Analysis

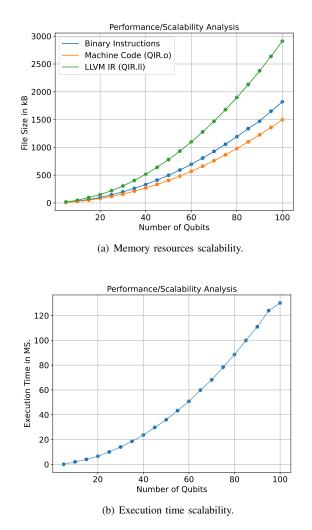

In the experiment, we utilize the Munich Quantum Toolkit (MQT) Bench [29], which is a benchmarking software and design automation tool for quantum computing. The analysis has been conducted on a local machine that runs Linux as the operating system with a 13th Gen Intel(R) Core(TM) i9-13900HX CPU. The study scales the number of qubits from five to one hundred, which is the maximum number of qubits that can be addressed by the current version of the 32-bit QISA. The result sample in Figure 7 is for the Amplitude Estimation algorithm represented in the native gate set of IBM quantum hardware. Each data point is the average of a thousand executions. Figure 7(a) shows that the memory requirement of our implementation scales super-linearly with the size of the input circuit. Hence, there is no exponential increase in memory resources despite of introducing the memory and time management instructions on the binary level representation. Moreover, Figure 7(b) illustrates that the execution time of the runtime library also scales super-linearly with the size of quantum code. The super-linear scaling of memory and execution time facilitates predictable resource planning and allocation. This predictability is crucial for scaling quantum applications as it allows developers and system architects to estimate the computational and memory requirements based

Fig. 7. Performance analysis of the runtime library - Alpha version.

on the number of qubits involved easily. Such performance means that – as quantum computers grow in terms of qubit count – the software infrastructure can expand to accommodate this growth without facing exponential increases in resource demands. This scalability is essential for the practical implementation of larger and more complex quantum algorithms. This provides the basis for future work that includes more run time analysis and optimization.

#### B. Workflow Verification

The work presented adds the missing building block in existing HPCQC workflows, as the one being built by LRZ, as it bridges the gap between the QIR representation of the quantum kernel and the novel ISA supported by the unified quantum platform. This mapping enables researchers, for the first time, to target the UQP using the high-level representation of quantum circuits without the need for writing binary instructions manually. Moreover, our implementation lays the groundwork for a more comprehensive, more intricate UQP which abstracts away the complexity of interfacing with different quantum hardware modalities. This research, from

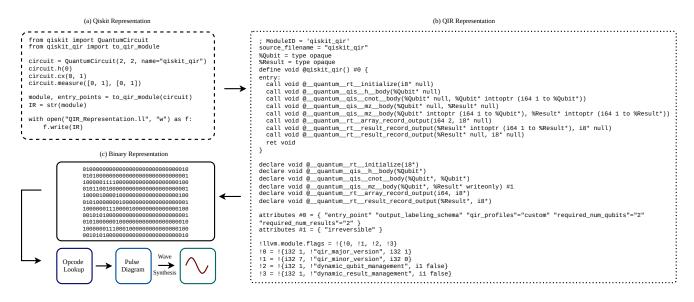

Fig. 8. Workflow verification.

the software perspective, introduces the concept of binary portability across different quantum machines as long as requirements such as qubit connectivity are satisfied. Hence, there is no need to re-compile to generate a new binary to target different quantum processing units.

Figure 8 shows the workflow verification of the proposed setup. The high-level quantum circuit representation is mapped to a quantum intermediate representation. Figure 8(a) illustrates a simple quantum circuit that prepares the famous bell state using Qiskit as a development environment. The mapping from Qiskit representation to QIR representation is done via a software tool written by Microsoft developers called "giskit\_gir". The corresponding QIR implementation is seen in Figure 8(b), where each quantum or classical instruction is represented by an external function call to the backend runtime library. The runtime library is responsible for the specifics of implementing such instruction to fit the supported hardware. Moreover, additional metadata is included in the QIR representation, such as the attributes. Then, upon compilation and execution of the QIR code, the corresponding binary instructions are generated and offloaded to the unified quantum platform as seen in Figure 8(c). Finally, the control logic implemented on the QCPs generates the parameters required for the wave synthesis which is then passed to the control electronics for the actual quantum operation execution on the quantum register.

Table II shows the direct correspondence between the highlevel representation of the simple Bell state quantum circuit and the binary instructions being executed on the quantum control processor. For the sake of clarity, this example intentionally avoids any intermediate optimization passes that would change the structure of the quantum circuit. This correspondence table is indicative of a well-defined ISA for quantum computing. It reflects the design choices made for the quantum processor's ISA, such as operation types, operand specifications, and memory access patterns. Moreover, The table suggests a systematic approach to extending the binary instruction set to include new quantum operations as the field of quantum algorithms grows.

By providing a low-level view of the binary instructions, developers and researchers gain an in-depth understanding of how their quantum algorithms are executed on the hardware. This level of transparency ensures that the quantum operations are carried out precisely as intended, without the abstractions or optimizations that vendor-supplied runtimes might perform unknowingly to the users. It empowers users to make informed decisions regarding their quantum code, facilitating fine-tuned optimizations and adjustments based on the detailed feedback from the execution layer.

#### VI. CONCLUSION

This work introduced the implementation of an abstraction layer needed to realize a unified quantum platform. Such implementation is positioned right at the interface of the software stack and quantum processing units. Hence, the implementation touches on both levels of software and hardware. On the software side, we have developed a novel unified runtime library that maps QIR representation to an extended, unified hybrid ISA. On the hardware side, we show how a quantum control processor can be extended to include the logic to support multiple technologies and we demonstrate this by adding the required control logic for a quantum hardware based on neutral atoms technology in addition to the existing superconducting support. The performance analysis and workflow verification highlight the scalability capabilities of this approach and ensure the correctness of the implementation. To the best of our knowledge, this research is the first to successfully introduce the idea of a unified and open quantum platform and to implement it within a tight HPCQC integration setup.

| Qiskit Representation           | Binary Instruction Representation      |

|---------------------------------|----------------------------------------|

| N/A                             | 01000000000000000000000000000000000000 |

| circuit.h(0)                    | 01010000000000000000000000000000000000 |

|                                 | 10000011110000000000000000000000000000 |

| circuit.cx(0, 1)                | 01011001000000000000000000000000000000 |

|                                 | 10000100001000000000000000000000000000 |

| circuit.measure([0, 1], [0, 1]) | 01010000000100000000000000000000000000 |

|                                 | 10000001110000100000000000000000000000 |

|                                 | 00101010000000000000000000000000000000 |

|                                 | 01010000001000000000000000000000000000 |

|                                 | 10000001110001000000000000000000000000 |

|                                 | 00101010000000000000000000000000000000 |

TABLE II BINARY INSTRUCTION VERIFICATION

#### ACKNOWLEDGMENT

The research is part of the Munich Quantum Valley (MQV), which is supported by the Bavarian state government with funds from the Hightech Agenda Bayern. Moreover, this work is supported by BMW Group.

#### REFERENCES

- C. S. Wang, J. C. Curtis, B. J. Lester, Y. Zhang, Y. Y. Gao, J. Freeze, V. S. Batista, P. H. Vaccaro, I. L. Chuang, L. Frunzio, L. Jiang, S. M. Girvin, and R. J. Schoelkopf, "Efficient multiphoton sampling of molecular vibronic spectra on a superconducting bosonic processor," *Phys. Rev. X*, vol. 10, p. 021060, 06 2020. [Online]. Available: https://link.aps.org/doi/10.1103/PhysRevX.10.021060

- [2] J. Yin, Y.-H. Li, S.-K. Liao, M. Yang, Y. Cao, L. Zhang, J.-G. Ren, W.-Q. Cai, W.-Y. Liu, S.-L. Li *et al.*, "Entanglementbased secure quantum cryptography over 1,120 kilometres," *Nature*, vol. 582, no. 7813, pp. 501–505, 2020. [Online]. Available: https://doi.org/10.1038/s41586-020-2401-y

- [3] M. Ruefenacht, B. G. Taketani, P. Lähteenmäki, V. Bergholm, D. Kranzlmüller, L. Schulz, and M. Schulz, "Bringing quantum acceleration to supercomputers," 2022. [Online]. Available: https://www.quantum.lrz.de/fileadmin/QIC/Downloads/IQM\_ HPC-QC-Integration-Whitepaper.pdf

- [4] P. Seitz, A. Elsharkawy, X.-T. M. To, and M. Schulz, "Toward a unified hybrid hpcqc toolchain," in 2023 IEEE International Conference on Quantum Computing and Engineering (QCE), vol. 02, 2023, pp. 96–102. [Online]. Available: https://ieeexplore.ieee.org/document/10313648

- [5] X. Guo, K. Qin, and M. Schulz, "Hisep-q: A highly scalable and efficient quantum control processor for superconducting qubits," in 2023 IEEE 41st International Conference on Computer Design (ICCD), 2023, pp. 86–93. [Online]. Available: https://doi.org/10.1109/ ICCD58817.2023.00023

- [6] X. Fu, L. Riesebos, A. Rol, J. van Straten, H. van Someren, N. Khammassi, I. Ashraf, R. Vermeulen, V. Newsum, K. Loh, J. de Sterke, W. Vlothuizen, R. Schouten, C. Almudever, L. DiCarlo, and K. Bertels, "eqasm: An executable quantum instruction set architecture," in 2019 IEEE International Symposium on High Performance Computer Architecture (HPCA). Washington, DC, USA: IEEE, 2019, pp. 224– 237. [Online]. Available: https://doi.org/10.1109/HPCA.2019.00040

- [7] M. Zhang, L. Xie, Z. Zhang, Q. Yu, G. Xi, H. Zhang, F. Liu, Y. Zheng, Y. Zheng, and S. Zhang, "Exploiting different levels of parallelism in the quantum control microarchitecture for superconducting qubits," in *MICRO-54: 54th Annual IEEE/ACM International Symposium on Microarchitecture*, 2021, pp. 898–911. [Online]. Available: https: //doi.org/10.1145/3466752.3480116

- [8] L. Stefanazzi, K. Treptow, N. Wilcer, C. Stoughton, C. Bradford, S. Uemura, S. Zorzetti, S. Montella, G. Cancelo, S. Sussman *et al.*, "The qick (quantum instrumentation control kit): Readout and control for qubits and detectors," *Review of Scientific Instruments*, vol. 93, no. 4, 2022. [Online]. Available: https://doi.org/10.1063/5.0076249

- [9] A. Elsharkawy, X.-T. M. To, P. Seitz, Y. Chen, Y. Stade, M. Geiger, Q. Huang, X. Guo, M. Arslan Ansari, C. B. Mendl, D. Kranzlmüller, and M. Schulz, "Integration of Quantum Accelerators with High Performance Computing – A Review of Quantum Programming Tools," *arXiv e-prints*, 2023. [Online]. Available: https://doi.org/10.48550/arXiv.2309.06167

- [10] T. S. Humble and K. A. Britt, "Software systems for high-performance quantum computing," in 2016 IEEE High Performance Extreme Computing Conference (HPEC), 2016, pp. 1–8. [Online]. Available: https://ieeexplore.ieee.org/abstract/document/7761628

- [11] T. S. Humble, A. McCaskey, D. I. Lyakh, M. Gowrishankar, A. Frisch, and T. Monz, "Quantum computers for high-performance computing," *IEEE Micro*, vol. 41, no. 5, p. 15–23, sep 2021. [Online]. Available: https://doi.org/10.1109/MM.2021.3099140

- [12] A. Elsharkawy, X.-T. M. To, P. Seitz, Y. Chen, Y. Stade, M. Geiger, Q. Huang, X. Guo, M. A. Ansari, M. Ruefenacht, L. Schulz, S. Karlsson, C. B. Mendl, D. Kranzlmüller, and M. Schulz, "Challenges in HPCQC integration," in 2023 IEEE International Conference on Quantum Computing and Engineering (QCE), vol. 02, 2023, pp. 405–406. [Online]. Available: https://ieeexplore.ieee.org/document/10313875

- [13] L. Dagum and R. Menon, "Openmp: an industry standard api for sharedmemory programming," *IEEE Computational Science and Engineering*, vol. 5, no. 1, pp. 46–55, 1998.

- [14] Message Passing Interface Forum, MPI: A Message-Passing Interface Standard Version 4.0, Message Passing Interface Forum, 2021. [Online]. Available: https://www.mpi-forum.org/docs/mpi-4.0/mpi40-report.pdf

- [15] (2021) Quantum intermediate representation specification. QIR Alliance.[Online]. Available: https://github.com/qir-alliance/qir-spec/tree/spec\_update

- [16] X. Fu, M. A. Rol, C. C. Bultink, J. Van Someren, N. Khammassi, I. Ashraf, R. Vermeulen, J. De Sterke, W. Vlothuizen, R. Schouten et al., "An experimental microarchitecture for a superconducting quantum processor," in *Proceedings of the 50th Annual IEEE/ACM International Symposium on Microarchitecture*, 2017, pp. 813–825. [Online]. Available: https://doi.org/10.1145/3123939.3123952

- [17] X. Guo and M. Schulz, "A scalable and cross-technology quantum control processor," in 2023 33rd International Conference on Field-Programmable Logic and Applications (FPL), 2023, pp. 353–354. [Online]. Available: https://doi.org/10.1109/FPL60245.2023.00063

- [18] T. M. Mintz, A. J. Mccaskey, E. F. Dumitrescu, S. V. Moore, S. Powers, and P. Lougovski, "Qcor: A language extension specification for the heterogeneous quantum-classical model of computation," ACM Journal on Emerging Technologies in Computing Systems (JETC), vol. 16, no. 2, pp. 1–17, 2020. [Online]. Available: https://doi.org/10.1145/3380964

- [19] A. Mccaskey, T. Nguyen, A. Santana, D. Claudino, T. Kharazi, and H. Finkel, "Extending c++ for heterogeneous quantum-classical computing," ACM Transactions on Quantum Computing, vol. 2, no. 2, pp. 1–36, jul 2021. [Online]. Available: https://doi.org/10.1145/3462670

- [20] T. Nguyen and A. J. McCaskey, "Extending python for quantumclassical computing via quantum just-in-time compilation," ACM Transactions on Quantum Computing, vol. 3, no. 4, jul 2022. [Online]. Available: https://doi.org/10.1145/3544496

- [21] A. J. McCaskey, D. I. Lyakh, E. F. Dumitrescu, S. S. Powers, and T. S. Humble, "XACC: a system-level software infrastructure for heterogeneous quantum-classical computing," *Quantum Science*

and Technology, vol. 5, p. 024002, 2020. [Online]. Available: https://doi.org/10.1088/2058-9565/ab6bf6

- [22] M. Schulz, M. Ruefenacht, D. Kranzlmüller, and L. B. Schulz, "Accelerating hpc with quantum computing: It is a software challenge too," *Computing in Science & Engineering*, vol. 24, no. 4, pp. 60–64, 2022. [Online]. Available: https://doi.org/10.1109/MCSE.2022.3221845

- [23] N. Saurabh, S. Jha, and A. Luckow, "A conceptual architecture for a quantum-hpc middleware," in 2023 IEEE International Conference on Quantum Software (QSW). IEEE Computer Society, 2023, pp. 116–127. [Online]. Available: https://doi.ieeecomputersociety.org/10. 1109/QSW59989.2023.00023

- [24] G. Huang, Y. Xu, N. Fruitwala, A. D. Rajagopala, K. Nowrouzi, R. K. Naik, D. Santiago, and I. Siddiqi, "Qubic 2.0: A flexible advanced full stack quantum bit control system," in 2023 IEEE International Conference on Quantum Computing and Engineering (QCE). Los Alamitos, CA, USA: IEEE Computer Society, sep 2023, pp. 248–249. [Online]. Available: https://doi.ieeecomputersociety.org/ 10.1109/QCE57702.2023.10227

- [25] Y. Xu, G. Huang, J. Balewski, R. Naik, A. Morvan, B. Mitchell, K. Nowrouzi, D. I. Santiago, and I. Siddiqi, "Qubic: An open-source fpga-based control and measurement system for superconducting quantum information processors," *IEEE Transactions on Quantum Engineering*, vol. 2, pp. 1–11, 2021. [Online]. Available: https: //doi.org/10.1109/TQE.2021.3116540

- [26] M. Mathews, X. Yin, A. Baumgärtner, T. Esslinger, and A. Akin, "A control and testing framework for a digital micromirror device in neutral atom quantum computing and simulation platforms," in 2022 IEEE International Conference on Quantum Computing and Engineering (QCE), 2022, pp. 724–726. [Online]. Available: https://doi.org/10.1109/QCE53715.2022.00098

- [27] N. Khammassi, I. Ashraf, J. V. Someren, R. Nane, A. M. Krol, M. A. Rol, L. Lao, K. Bertels, and C. G. Almudever, "Openql: A portable quantum programming framework for quantum accelerators," *J. Emerg. Technol. Comput. Syst.*, vol. 18, no. 1, dec 2021. [Online]. Available: https://doi.org/10.1145/3474222

- [28] J. Winklmann, D. Tsevas, and M. Schulz, "Realistic neutral atom image simulation," in 2023 IEEE International Conference on Quantum Computing and Engineering (QCE), vol. 01, 2023, pp. 1349–1359. [Online]. Available: https://doi.org/10.1109/QCE57702.2023.00153

- [29] N. Quetschlich, L. Burgholzer, and R. Wille, "Mqt bench: Benchmarking software and design automation tools for quantum computing," *Quantum*, vol. 7, p. 1062, Jul. 2023. [Online]. Available: http: //dx.doi.org/10.22331/q-2023-07-20-1062