# Highly Versatile FPGA-Implemented Cyber Coherent Ising Machine

Toru Aonishi<sup>\*‡</sup>, Tatsuya Nagasawa<sup>†</sup>, Toshiyuki Koizumi<sup>†</sup>, Mastiyage Don Sudeera Hasaranga Gunathilaka<sup>‡</sup>, Kazushi Mimura<sup>§</sup>, Masato Okada<sup>\*</sup>, Satoshi Kako<sup>¶</sup>, Yoshihisa Yamamoto<sup>¶</sup>

\*Graduate School of Frontier Sciences, The University of Tokyo 5-1-5 Kashiwanoha, Kashiwa-shi, Chiba 277-8561, JAPAN

<sup>†</sup>D-CLUE Technologies Co.,Ltd. 4F KAKiYA Building, 2-7-17 Shin-Yokohama, Kohoku-ku, Yokohama, Kanagawa 222-0033, JAPAN

<sup>‡</sup>School of Computing, Tokyo Institute of Technology 4259-J2-38 Nagatsuda, Midori-ku, Yokohama, Kanagawa 226-8502, Japan

<sup>§</sup>Graduate School of Information Sciences, Hiroshima City University 3-4-1 Ohtsukahigashi, Asaminami-ku, Hiroshima 731-3194 Japan

<sup>¶</sup>Physics and Informatics Laboratories, NTT Research Inc. 940 Stewart Dr, Sunnyvale, CA, 94085, USA

Abstract—In recent years, quantum Ising machines have drawn a lot of attention, but due to physical implementation constraints, it has been difficult to achieve dense coupling, such as full coupling with sufficient spins to handle practical large-scale applications. Consequently, classically computable equations have been derived from quantum master equations for these quantum Ising machines. Parallel implementations of these algorithms using field-programmable gate arrays (FPGAs) have been used to rapidly find solutions to these problems on a scale that is difficult to achieve in physical systems. We have developed an FPGA implemented cyber coherent Ising machine (cyber CIM) that is much more versatile than previous implementations using FPGAs. Our architecture is versatile since it can be applied to the open-loop CIM, which was proposed when CIM research began, to the closed-loop CIM, which has been used recently, as well as to Jacobi successive over-relaxation method. By modifying the sequence control code for the calculation control module, other algorithms such as Simulated Bifurcation (SB) can also be implemented. Earlier research on large-scale FPGA implementations of SB and CIM used binary or ternary discrete values for connections, whereas the cyber CIM used singleprecision floating-point format (FP32) values. Also, the cyber CIM utilized Zeeman terms that were represented as FP32, which were not present in other large-scale FPGA systems. Our implementation with continuous interaction realizes N = 4096 on a single FPGA, comparable to the single-FPGA implementation of SB with binary interactions, with N = 4096. The cyber CIM enables applications such as code division multiple access multi-user detector and L0-norm regularization-based compressed sensing which were not possible with earlier FPGA systems, while enabling superior calculation speeds, more than ten times faster than a GPU implementation. The calculation speed can be further improved by increasing parallelism, such as through clustering.

# I. INTRODUCTION

Combinatorial optimization problems involve finding a solution for a combination of discrete parameters that maximizes (or minimizes) a particular evaluation index within given conditions. The combination that meets all constraints does not exist for most real-world problems. Under such conditions, as the size of the problem increases, it becomes more difficult to find an optimal combination. According to computational complexity theory, such problems are NP-hard [1], and require computing time that scales exponentially with the problem size. Combinatorial optimization problems include various real-world problems such as resource allocation [2], scheduling [3], portfolio optimization [4], traffic flow optimization [5], drug discovery [6], [7], and machine learning [8], [9], [10], [11]. Because of the importance of these problems, there has been a strong demand for high-speed solution searches for combinatorial optimization problems, and thus a series of heuristics have been proposed to solve these problems [12], [13], [14].

Ising models are composed of microscopic elements called Ising spins, which can take either of two states: up or down. This model can form complex macroscopic states such as glass states in which ferromagnetic and antiferromagnetic interactions (force the spins to align in the same and opposite directions respectively) coexist. Many combinatorial optimization problems, such as quadratic unconstrained binary optimization (QUBO), can be mapped to the task of finding the ground state of an Ising Hamiltonian. Consequently, to perform high-speed solution searches for the combinatorial optimization problems described above, Ising machines, which are dedicated hardware for rapidly searching for the ground state of Ising Hamiltonians, have been actively researched in recent years. In particular, quantum Ising machines have garnered increasing interest due to their possession of quantum attributes that could offer potential solutions to the challenges inherent in large-scale combinatorial optimization problems.

Several quantum Ising machines have been proposed. This includes D-Wave systems[15], [16], which utilize superconducting quantum interferometers [17], [18], [19] to execute quantum annealing for adiabatic quantum computation[20], [21]. There is also a quantum bifurcation machine that has been proposed to execute non-dissipative quantum adiabatic optimization [22], [23], [24]. Its implementation can be realized through either two-photon-driven Kerr parametric oscil-

lators [25] or superconducting quantum circuits [26]. Moreover, Coherent Ising Machines (CIMs) represent a dissipative optical-parametric-oscillation (OPO) network leveraging the minimum gain principle for solving optimization problems [27], [28], [29], [30], [31], [32], [33], [34]. In physically implemented systems based on superconducting or nonlinear quantum optical phenomena, the attainment of a large number of spins and dense interconnections presents considerable technical hurdles. This limitation primarily stems from the difficulty in physical wiring among a large number of spins. Consequently, there have been efforts to derive classically computable mathematical formulas from theoretical models of quantum Ising machines, often articulated in quantum master equations, Schrödinger equations, and related frameworks. Then use them to solve combinatorial optimization problems. By deploying these algorithms in parallel on graphics processing units (GPUs) [35], [36], [37] and field-programmable gate arrays (FPGAs), it has become feasible to expeditiously solve problems necessitating extensive system sizes and dense interconnections. These are challenges that would be cumbersome to address in a physical system. This paper focuses on parallel computing architectures on FPGAs, which can also be implemented with application-specific integrated circuits (ASICs). Simulated Bifurcation (SB) has been proposed as a classically computable model for quantum bifurcation machines [35], [38]. SB has been implemented on a single FPGA [35], [39], [40] and on a large-scale multi-node FPGA cluster [40], [41]. N = 4096 is implemented in a single FPGA [39], [40], and N = 32,768 is implemented in an 8-node FPGA cluster [41]. It is claimed that the FPGA-implemented SB is more efficient at solving Max-cut than the physical CIM system for N = 2000 [35], [40]. In addition, attempts have been made to apply the FPGA-implemented SB to portfolio problems [42], [43], [44].

In contrast, a stochastic differential equation (SDE) describing the amplitudes of optical-parametric-oscillation (OPO) pulses, derived from the quantum master equation using either the Wigner representation or the Positive-*P* representation, serves as a computationally tractable model for Coherent Ising Machines (CIM).[45], [46], [47], [48], [49]. In the CIM literature, a model integrating feedback kinetics to enable chaotic amplitude control (CAC) is called a closed-loop model [50], [51], [52], [53], [54], [55], while a model lacking such kinetics is denoted as an openloop model [50]. The closed-loop model has been realized on an FPGA [56]. Despite its calculation speed being inferior to that of FPGA-implemented SB, it has been shown to yield a higher success rate in solution finding. Furthermore, it has demonstrated a small slope in solution search time with respect to the system size on a logarithmic scale [56].

The classically computable models have been implemented on FPGAs as described above. However, as the system size N increases, the logic capacity and internal memory capacity becomes insufficient to implement such models in parallel on FPGA. Due to this capacity problem and problems with the models themselves as described below, for larger system sizes than  $N \ge 1024$ , their functions are restricted as follows [35], [39], [40], [41], [56].

1) Connections are low-bit discrete values, and not continu-

ous real values.

- 2) The Zeeman terms are not configurable.

- 3) Handling of either QUBO or Ising Hamiltonian optimization.

- 4) The implemented algorithm cannot be changed.

(1) The most expensive process in the calculation of the models is the multiplication of the  $N \times N$  coupling matrix with the N-dimensional spin-state vector. With both CIM and SB, when the system size is large, binary or ternary value connections are used to reduce the consumption of memory and logic resources and to improve their calculation speeds [35], [39], [40], [41], [56]. Continuous real-valued connections are needed to handle real-world problems. (2) The Zeeman terms play a crucial role in most optimization problems pertinent to signal processing applications, including compressed sensing [36], [37], code division multiple access (CDMA) multi-user detectors [57], multi-input multi-output (MIMO) systems [58], [59], [60] and other problems such as portfolio optimization [42], [43], [44]. Given that the spin variables in the aforementioned models adopt continuous values (without adhering strictly to +1 or -1), there arises a discrepancy between the magnitudes of the Zeeman term and the interaction term, leading to a degradation in their performance [57]. Therefore, it is necessary to devise ways to handle the Zeeman term. In CIM, where solutions to this problem have recently been proposed [51], [55], [36], [37], [61], the Zeeman term is not yet implemented in an FPGA system. In SB [38], the diagonal elements of the interactions i.e. selfinteractions are used as Zeeman terms. Since the interaction is binary as described in (1), the Zeeman term can only be configured with binary values [42]. (3) With the models using continuous valued spin variables, to handle the QUBO problem with Zeeman terms, it is necessary to configure a suitable local field that is different from the Ising optimization [36], [37]. There is no single architecture capable of performing both of these. (4) The models update frequently. Depending on the problem, the appropriate model can also differ. Currently, every time the model changes, the architecture needs to be redesigned. The flexibility of being able to change the model on FPGA is required.

In this research, we have developed a highly versatile FPGAimplemented cyber-CIM to overcome the issues described above. Our developed architecture is highly versatile, allowing three different algorithms, open-loop CIM [47], [49], [36] and closed-loop CIM [54], [55] for combinatorial optimization problems and Jacobi Successive Over-Relaxation (SOR) for quadratic optimization problems to be executed on the same modules. By rewriting the sequence control code in the calculation control module, other algorithms can also be executed, and in principle SB could also be executed. The coupling matrix, Zeeman terms and OPO amplitudes are all represented using single-precision floating-point format (FP32), so local field and time evolution (TE) calculations are operated with FP32. The system sizes realized on a single FPGA are N = 1024, N = 2048and N = 4096, which are comparable to N = 4096 of SB implemented on a single FPGA[39], [40]. Our system has 1/4 degree of parallelism of the single-FPGA SB implementation, so it requires approximately four-times the number of cycles for

one step including the local field and TE calculations [39], [40]. As benchmarks to evaluate the FPGA system we developed, we used a CDMA multi-user detector, which is an example of optimization of Ising Hamiltonian including Zeeman terms [57], and L0-norm based regularization compressed sensing (L0RBCS), which is an example of optimization of QUBO Hamiltonian including Zeeman terms [36], [37], [61]. Our architecture realizes an alternative optimization for L0RBCS by alternating repeatedly between open-loop CIM or closed-loop CIM, and Jacobi SOR, [36], [37], [61]. These problems cannot be executed on the earlier FPGA systems described above. Here, we assess the performance of the FPGA system we've developed by comparing the computed results and execution times for these problems against those obtained using GPUs.

#### **II. IMPLEMENTED ALGORITHMS**

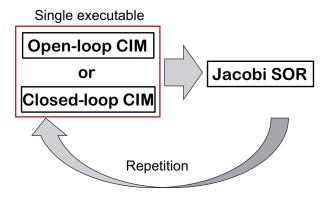

We implemented the following three algorithms on the same FPGA architecture: open-loop CIM with Zeeman terms that does not perform amplitude control [47], [49], [36], closed-loop CIM with Zeeman terms that performs chaotic amplitude control [54], [55], [61], and Jacobi SOR that solves simultaneous equations. As shown in Fig. 1, the architecture we have proposed can alternate repeatedly between open-loop CIM or closed-loop CIM, and Jacobi SOR, realizing an alternative optimization for L0RBCS [36], [37], [61]. It can also execute only open-loop CIM or closed-loop CIM, so it can be applied to various combinatorial optimization problems. We give an overview of each algorithm we implemented below.

#### A. Supported Hamiltonians

The algorithms we implemented support the following Ising Hamiltonian.

$$\mathcal{H} = -\frac{1}{2} \sum_{ij}^{N} J_{ij} \sigma_i \sigma_j - \sum_{i}^{N} g_i \sigma_i.$$

(1)

$\sigma_i$  is the *i*-th Ising spin taking either +1 or -1,  $J_{ij}$  is the coupling strength between the *i*-th spin and *j*-th spin, and  $g_i$  is the external field, which is called the Zeeman term.

The algorithms also support the following QUBO Hamiltonian.

$$\mathscr{H} = -\frac{1}{2} \sum_{ij}^{N} J_{ij} r_i r_j q_i q_j - \sum_{i}^{N} g_i r_i q_i + \lambda \sum_{i}^{N} q_i$$

(2)

$q_i$  is the *i*-th binary Potts spin taking either 0 or 1,  $J_{ij}$  is the coupling strength between the *i*-th spin and the *j*-th spin, and  $g_i$  is the Zeeman term.  $\lambda$  is an external field corresponding to a threshold, common to each spin.  $r_i$  is a real-value entry of the fixed auxiliary variable vector  $r \in \Re^N$ , which is configured according to the problem being solved. For most combinatorial optimization problems, it is required to set  $r_i = 1$  ( $i = 1, \dots, N$ ). In contrast, if q is fixed, the Hamiltonian in Eq. 2 with respect to r becomes a quadratic function for r.

Both the open-loop CIM and closed-loop CIM described below perform the optimization of the above Ising Hamiltonian and QUBO Hamiltonian. The Jacobi SOR described below performs the quadratic optimization of the Hamiltonian in Eq. 2 with respect to r under fixed q.

Fig. 1. Relationship among the implemented algorithms. L0-RBCS is realized by alternative execution between open-loop CIM or closed-loop CIM, and Jacobi SOR algorithms. It is also possible to execute only open-loop CIM or closed-loop CIM for various combinatorial optimization problems.

#### B. Open-Loop CIM

CIM is an Ising machine composed of a network of optical parametric oscillators (OPOs). Here time-multiplexed OPO pulses propagate along a cavity created by a long-distance optical fiber ring. The phase and amplitude of each OPO pulse are measured, and the mutual coupling among OPO pulses is computed using an FPGA. The injection field, representing the mutual coupling, is then fed back to each OPO pulse. This is an architecture of a measurement feedback-type CIM [29], [30].

By expanding the density operator of the whole OPO network with the Wigner function, applying Ito's rule to the resulting Fokker-Planck equation, and ignoring measurement noise in the measurement feedback, we obtain the following equation [45], [46], [47], [49].

$$\frac{dc_i}{dt} = (-1 + p - a_i)c_i + KI_i + g_s \sqrt{a_i + 0.5}W_{1i},

\frac{ds_i}{dt} = (-1 - p - a_i)s_i + g_s \sqrt{a_i + 0.5}W_{2i},

a_i = c_i^2 + s_i^2, \quad i = 1, \cdots, N,$$

(3)

where  $c_i$  and  $s_i$  are the in-phase and quadrature-phase amplitudes of the *i*-th OPO pulse, which are normalized by the saturation parameter,  $g_s$ .  $I_i$  is the injection field corresponding to the mutual coupling. This term only has an in-phase component, because the injection field is only injected into the in-phase component of the target OPO pulse in physical CIM. K is the gain coefficient of the injection field. p is the normalized pump rate. p = 1 corresponds to the oscillation threshold of a solitary OPO without the mutual coupling. If p is above the oscillation threshold ( $p \leq 1$ ), each of the OPO pulses is either in the 0-phase state or  $\pi$ -phase state. The 0-phase of an OPO pulse is assigned to an Ising-spin up-state, while the  $\pi$ -phase is assigned to the down-state.  $g_s$  is the saturation parameter which determines the nonlinear increase (abrupt jump) of the photon number at the OPO threshold. The last terms of the upper and lower equations express the vacuum fluctuations injected from external reservoirs and the pump fluctuations coupled to the OPO system via gain saturation.  $W_{1i}(t)$  and  $W_{2i}(t)$  are independent real Gaussian noise processes satisfying  $\langle W_{ki}(t) \rangle = 0$  and  $\langle W_{ki}(t)W_{lj}(t') \rangle = \delta_{kl}\delta_{ij}\delta(t-t')$ .

To be able to apply this to both the Ising Hamiltonian (Eq. 1) and the QUBO Hamiltonian (Eq. 2), we give the injection field  $I_i$  as follows.

$$I_i = F_{\chi}(h_i) - \eta \tag{4}$$

$$h_i = \begin{cases} \sum_{j=1(\neq i)}^N J_{ij}c_j + g_i \text{ (Ising)} \\ \sum_{j=1(\neq i)}^N J_{ij}r_jH(c_j) + g_i \text{ (QUBO)} \end{cases}, \quad (5)$$

where  $h_i$  is called the local field in statistical mechanics, and  $g_i$  is the Zeeman term introduced in Eqs. 1 and 2. The injection field  $I_i$  is calculated based on the local field  $h_i$ . The upper definition of  $h_i$  where the pulse amplitude takes its original continuous value is for the Ising Hamiltonian (Eq. 1), and the lower definition of  $h_i$  where the pulse amplitude is binarized as 0 or 1 by the Heaviside step function H is for the QUBO Hamiltonian (Eq. 2) [36], [37].  $r_i$  is a real-value entry of the fixed auxiliary variable vector  $r \in \Re^N$  defined in Eq. 2.  $\eta$  denotes a threshold value, which, in the context of LORBCS, is associated with  $\lambda$  in Eq. 2 via  $\eta = \sqrt{2\lambda}$  [36]. In most other combinatorial optimization problems, it is required to set  $\eta = 0$  and  $r_i = 1$  ( $i = 1, \dots, N$ ).  $F_{\chi}$  is the function defined as follows.

$$F_{\chi}(h) = \begin{cases} h & (\chi = \text{identity}) \\ |h| & (\chi = \text{absolute}) \end{cases}$$

For LORBCS, the absolute value function ( $\chi$  = absolute) is required. The reason that the absolute value function is required is discussed in our previous paper [36]. In most other combinatorial optimization problems, it is required to use the identity function ( $\chi$  = identity).

Here, we solve the open-loop CIM stochastic differential equation using the Euler-Maruyama method. This numerical algorithm is shown in Algorithm 1.

Algorithm 1 Open-loop CIM

**Require:** J matrix:  $J \in \mathfrak{R}^{N \times N}$ , Zeeman term:  $g \in \mathfrak{R}^N$ , Pump rate sequence:  $p \in \Re^{N_{step}}$ , Threshold:  $\eta \in \Re$ , Saturation parameter:  $g_s \in \mathfrak{R}$ , Gain: K, Index for  $F_{\chi}(h) = |h|$  or h:  $\chi$ , Auxiliary variable for QUBO:  $r \in \Re^N$ . 1:  $c \leftarrow 0, s \leftarrow 0$ . 2:  $\mu \leftarrow r, \sigma \leftarrow 0$  (if QUBO) or  $\mu \leftarrow 0, \sigma \leftarrow 1$  (if Ising). 3: for l = 1 to  $N_{step}$  do // Matrix-Vector Multiplication (MM) 4: **for** *i* = 1 to *N* **do** 5:  $h_i \leftarrow \sum_{j=1(\neq i)}^N J_{ij}\sigma_j\mu_j + g_i.$ 6: end for 7: // Time Evolution (TE) 8: for i = 1 to N do 9:

$$\begin{split} & W_{i1} \leftarrow N(0,1), \quad W_{i2} \leftarrow N(0,1) \\ & a_i \leftarrow c_i^2 + s_i^2, \quad b_i \leftarrow \sqrt{1/2 + a_i} \\ & c_i \leftarrow c_i + \Delta t \left( (-1 + p_l + a_i) \, c_i + K \left( F_{\chi} \left( h_i \right) - \eta \right) \right) + \end{split}$$

10: 11: 12:  $\sqrt{\Delta t} g_s b_i W_{i1}$  $s_i \leftarrow s_i + \Delta t (-1 - p_l + a_i) s_i + \sqrt{\Delta t} g_s b_i W_{i2}$ 13:  $\mu_i \leftarrow c_i$  (if Ising) or  $\sigma_i \leftarrow H(c_i)$  (if QUBO) 14: end for 15: 16: end for

#### C. Closed-Loop CIM

By integrating feedback kinetics for amplitude homogenous control with a SDE, derived from the quantum master equation for the entire OPO network using either the Wigner or Positive-P approximation, the closed-loop CIM model is derived. Especially, the effectiveness of CAC feedback, which produces chaotic trajectories of OPO amplitudes, is attracting attention [50], [51], [52], [53], [54], [55], [61]. In the zero quantum noise limit, a simple deterministic differential equation called the mean-field model is obtained [55]. Due to the parametric oscillation, in-phase amplitude components are amplified, while quadrature-phase amplitude components are anti-amplified, so the in-phase amplitude components becomes dominant in the SDEs for CIMs. Therefore, the mean field model of the closeloop CIM is described by the equation for  $c_i$  in Eq. 3 in the limit of  $g_s \rightarrow 0$  and the CAC feedback kinetic equation [53], [54], [55], [61]:

$$\frac{dc_i}{dt} = (-1 + p - a_i)c_i + Ke_iI_i,$$

$$\frac{de_i}{dt} = \beta(\tau - a_i)e_i,$$

$$a_i = c_i^2, \quad i = 1, \cdots, N,$$

(6)

where  $c_i$  is the in-phase amplitude of the *i*-th OPO pulse,  $I_i$  is the injection field, *K* is the gain coefficient of the injection field, and *p* is the pump rate.  $e_i$  is the feedback error to keep the pulse amplitudes homogeneous.  $\tau$  is the target value for the squared amplitude  $a_i$ , and  $\beta$  is the rate of exponential growth or decline for  $e_i$ . It has been reported that forcefully trying to equalize the amplitudes of the system to a target amplitude may result in a chaotic behavior in the system which may result in escaping from local minima in the energy landscape [50], [51], [52], [53], [54], [55].

To enable this model to be applied to both Ising Hamiltonians (Eq. 1) and QUBO Hamiltonians, (Eq. 2), the injection field  $I_i$  is given as follows.

$$I_i = r_i h_i - \lambda \tag{7}$$

$$h_i = \begin{cases} \sum_{j=1(\neq i)}^N J_{ij}c_j + g_i \text{ (Ising)} \\ \sum_{j=1(\neq i)}^N J_{ij}r_jH(c_j) + g_i \text{ (QUBO)} \end{cases} . \tag{8}$$

Here,  $h_i$  is called the local field in statistical mechanics, and  $g_i$  is the Zeeman term introduced in Eqs. 1 and 2.  $r_i$  is a real-value entry of the fixed auxiliary variable vector  $r \in \Re^N$  defined in Eq. 2. For closed-loop CIM,  $F_{\chi}$  is not introduced, and the injection field  $I_i$  is defined as the product of  $h_i$  with  $r_i$  [37], [61]. The upper definition of  $h_i$  where the pulse amplitude takes its original continuous value is for the Ising Hamiltonian (Eq. 1), and the lower definition of  $h_i$  where the pulse amplitude is binarized as 0 or 1 by the Heaviside step function H is for the QUBO Hamiltonian (Eq. 2) [61].  $\lambda$  is a threshold, corresponding to  $\lambda$  in Eq. 2. For LORBCS,  $\lambda$  is related to  $\eta$  in Eq. 5 by  $\eta = \sqrt{2\lambda}$  [36]. In most other combinatorial optimization problems, it is required to set  $\lambda = 0$  and  $r_i = 1$  ( $i = 1, \dots, N$ ).

Here, we solve the differential equation for the closed-loop CIM using the Euler method. The numerical algorithm used to solve the differential equation is shown in Algorithm 2. Initial values shown in Algorithm 2 were set according to our previous research [55], [61].

# Algorithm 2 Closed-loop CIM

**Require:** J matrix:  $J \in \mathfrak{R}^{N \times N}$ , Zeeman terms:  $g \in \mathfrak{R}^N$ , Pump rate sequence:  $p \in \Re^{N_{step}}$ , Gain: K, Threshold:  $\lambda \in \Re$ , Target amplitude:  $\tau \in \mathfrak{R}$ , Feedback coefficient:  $\beta \in \mathfrak{R}$ , Auxiliary variable for QUBO:  $r \in \mathfrak{R}^N$ . 1: *c* ← *i.i.d.N*(0, 0.02), *e* ← 1. 2:  $\mu \leftarrow r, \sigma \leftarrow 0$  (if QUBO) or  $r \leftarrow 1, \mu \leftarrow 0, \sigma \leftarrow 1$  (if Ising). 3: for l = 1 to  $N_{step}$  do 4: // Matrix-Vector Multiplication (MM) for i = 1 to N do 5:  $h_i \leftarrow \sum_{j=1(\neq i)}^N J_{ij}\sigma_j\mu_j + g_i.$ 6: end for 7: // Time Evolution (TE) 8: **for** *i* = 1 to *N* **do** 9:  $a_i \leftarrow c_i^2$ . 10:  $c_i \leftarrow c_i + \Delta t \left( (-1 + p_l + a_i) c_i + K e_i \left( r_i h_i - \lambda \right) \right).$ 11: 12:  $e_i \leftarrow e_i + \Delta t \beta (\tau - a_i) e_i.$  $\mu_i \leftarrow c_i$  (if Ising) or  $\sigma_i \leftarrow H(c_i)$  (if QUBO). 13: 14: end for 15: end for

# D. Jacobi SOR

The Hamiltonian in Eq. 2 with respect to r if q is fixed becomes a quadratic function for r. The optimal solution of the Hamiltonian with respect to r is the same as a solution of the following simultaneous equations.

$$\begin{bmatrix} J_{11} & J_{12} & \cdots & J_{1N} \\ J_{21} & J_{22} & \cdots & J_{2N} \\ \vdots & \vdots & \ddots & \vdots \\ J_{N1} & J_{N2} & \cdots & J_{NN} \end{bmatrix} \begin{bmatrix} q_1 r_1 \\ q_2 r_2 \\ \vdots \\ q_N r_N \end{bmatrix} + \begin{bmatrix} g_1 \\ g_2 \\ \vdots \\ g_N \end{bmatrix} = 0$$

(9)

We seek to obtain  $r = [r_1 \cdots r_N]^T$  that satisfies the simultaneous equations.  $q_i$  is the *i*-the entry in  $q \in \{0, 1\}^N$  which are given externally. More detail is given in the description of LORBCS below.

Jacobi Successive Over-Relaxation (Jacobi SOR), which is an extension of the Jacobi method by introducing a relaxation factor, is used to find the solution. The recursive update equation for solving the above simultaneous equation is as follows.

$$r_i \leftarrow (1 - \Delta t)r_i + \frac{\Delta t}{J_{ii}} \left( g_i + \sum_{j(\neq i)} J_{ij} q_j r_j \right)$$

(10)

Adjusting  $\Delta t$  improves the numerical stability and the speed of convergence. The numerical algorithm of the Jacobi SOR is shown in Algorithm 3. In the algorithm, it is required to set  $d_i = 1/J_{ii}$ .

# E. CDMA multiuser detector

We briefly explain the CDMA multiuser detector applied to FPGA implemented cyber CIM. To formulate the CDMA

# Algorithm 3 Jacobi Successive Over-Relaxation (SOR)

**Require:** J matrix:  $J \in \mathfrak{R}^{N \times N}$ , Zeeman terms:  $g \in \mathfrak{R}^N$ , Inverse of J diagonal elements:  $d \in \mathfrak{R}^N$ , Auxiliary variable:  $q \in \{0, 1\}^N$ . 1:  $\sigma \leftarrow q, r \leftarrow 0, \mu \leftarrow 0$ .

- 2: for l = 1 to  $N_{step}$  do

- // Matrix-Vector Multiplication (MM) 3:

- 4: **for** *i* = 1 to *N* **do**

- $h_i \leftarrow \sum_{j=1(\neq i)}^N J_{ij}\sigma_j\mu_j + g_i.$ 5: end for

- 6:

- 7: // Time Evolution (TE) for *i* = 1 to *N* do

- 8: 9:

- $r_i \leftarrow r_i + \Delta t (-r_i + d_i h_i).$

- 10:  $\mu_i \leftarrow r_i$ .

- end for 11:

- 12: end for

multiuser detector, we introduce a model of multiple access, wherein N users transmit information bits concurrently over a single communication channel [62], [63], [57].

$$\begin{bmatrix} y^{1} \\ \vdots \\ y^{M} \end{bmatrix} = \frac{1}{\sqrt{M}} \begin{bmatrix} \xi_{1}^{1} & \xi_{2}^{1} & \cdots & \xi_{N}^{1} \\ \vdots & \vdots & \ddots & \vdots \\ \xi_{1}^{M} & \xi_{2}^{M} & \cdots & \xi_{N}^{M} \end{bmatrix} \begin{bmatrix} \sigma_{1} \\ \sigma_{2} \\ \vdots \\ \sigma_{N} \end{bmatrix} + \begin{bmatrix} n^{1} \\ \vdots \\ n^{M} \end{bmatrix}.$$

(11)

Here,  $y = [y^1, \dots, y^M]^T \in \mathfrak{R}^M$  is the *M*-bit received sequence.  $\sigma = [\sigma_1, \cdots, \sigma_N] \in \{+1, -1\}^N$  is the information bits sent from N users.  $\xi_i = [\xi_i^1, \cdots, \xi_i^M] \in \{+1, -1\}^M$ is the *i*-th user's spreading code with M chips.  $\Xi$  =  $1/\sqrt{M}[(\xi_1)^T, \cdots, (\xi_N)^T]^T \in \mathfrak{R}^{M \times N}$  is the  $M \times N$  spreading code matrix.  $n = [n^1, \cdots, n^M]^T \in \mathfrak{R}^M$  is the additive Gaussian noise satisfying  $\langle n^{\mu} \rangle = 0$  and  $\langle n^{\mu} n^{\nu} \rangle = \zeta^2 \delta_{\mu\nu}$ .

This model represents the following process. The information bits  $\sigma_1$  to  $\sigma_N$  for each of N users are sought to be transmitted over a single communication channel. Before transmitting, the spreading code  $\xi_i$  with M chips is assigned to each user, and multiplied with the information bit  $\sigma_i$  for each user to perform the spreading encoding. The encoded sequences from all users are summed up, resulting in an M-bit sequence transmitted through a single Gaussian communication channel. The received *M*-bit sequence denoted *y*, is then obtained. Here, as an indicator to measure the difficulty of the problem, the spreading rate  $\alpha$ , defined as  $\alpha = M/N$ , is introduced.

The objective of this problem is to simultaneously retrieve all user bits  $\sigma$  from the received sequence y under the condition that the spreading code matrix  $\Xi$  is known.  $\sigma$  is retrieved by solving the following optimization problem.

$$\hat{\sigma} = \arg\min_{\sigma \in \{+1,-1\}^N} \left( \frac{1}{2} \|y - \Xi \sigma\|_2^2 \right).$$

(12)

Here,  $\hat{\sigma}$  is the inferred value of the information bits for all users. From Eq. 12, we can determine the Hamiltonian for the CDMA multi-user detector:

$$\mathcal{H} = -\frac{1}{2} \sum_{i,j=1}^{N} J_{ij} \sigma_i \sigma_j - \sum_{i=1}^{N} g_i \sigma_i, \qquad (13)$$

$$J_{ij} = -\frac{1}{M} \sum_{\mu=1}^{M} \xi_i^{\mu} \xi_j^{\mu}, \quad g_i = \frac{1}{\sqrt{M}} \sum_{\mu=1}^{M} \xi_i^{\mu} y^{\mu}.$$

(14)

This Hamiltonian is the same as the Ising Hamiltonian in Eq. 1.

#### F. LORBCS

We briefly describe LORBCS applied to FPGA implemented cyber CIM. To formulate LORBCS, we introduce the following observation process model [36].

$$\begin{bmatrix} y^{1} \\ \vdots \\ y^{M} \end{bmatrix} = \begin{bmatrix} A_{1}^{1} & A_{2}^{1} & \cdots & A_{N}^{1} \\ \vdots & \vdots & \ddots & \vdots \\ A_{1}^{M} & A_{2}^{M} & \cdots & A_{N}^{M} \end{bmatrix} \begin{bmatrix} x_{1} \\ x_{2} \\ \vdots \\ x_{N} \end{bmatrix} + \begin{bmatrix} n^{1} \\ \vdots \\ n^{M} \end{bmatrix}.$$

(15)

Here,  $y = [y^1, \dots, y^M]^T \in \mathfrak{R}^M$  is the *M*-dimensional observed signal,  $x = [x_1, \dots, x_N] \in \mathbb{R}^N$  is the *N*-dimensional observed source signal, and  $A = [A_i^{\mu}] \in \mathbb{R}^{M \times N}$  is the  $M \times N$ observation matrix.  $n = [n^1, \dots, n^M]^T \in \mathbb{R}^M$  is the *M*dimensional Gaussian observation noise satisfying  $\langle n^{\mu} \rangle = 0$ and  $\langle n^{\mu}n^{\nu}\rangle = \zeta^2 \delta_{\mu\nu}$ .

Because the dimension M of the observed signal y is less than the dimension N of the original signal x, as a prerequisite for compressed sensing, the simultaneous equations in Eq. 15 are indeterminate even if the observation noise n is zero. The objective of compressed sensing is to recover the higher-dimensional source signal x from the lower-dimensional observed signal y. Under the sparse condition for the source signal x that the number of non-zero elements in x is less than the dimension M of the observed signal y, it is possible to recover x from y if the position of the non-zero elements in x can be identified. Here, we introduce the compression rate  $\alpha = M/N$ , which is the ratio between the dimension M of y and the dimension N of x, and also the sparseness, a, which is the ratio of the number of non-zero elements in x and the dimension N of x.

We reconstruct the sparse source signal x by solving the following optimization problem, which incorporates L0-norm regularization.

$$x = \underset{x \in \mathbb{R}^{N}}{\arg\min} \left( \frac{1}{2} \|y - Ax\|_{2}^{2} + \sum_{k} \frac{\gamma_{k}}{2} \|\Gamma_{k}x\|_{2}^{2} + \lambda \|x\|_{0} \right).$$

(16)

Here,  $\sum_k \frac{\gamma_k}{2} \|\Gamma_k x\|_2^2$  is the L2-norm regularization term to improve the estimation accuracy [64].  $\Gamma_k$  is a linear operator matrix, e.g., discrete-differential matrix to detect changing points. The LORBCS formulation in Eq. 16 can be reformulated into a two-fold optimization problem [65], [66]:

$$\begin{aligned} (\hat{r}, \hat{q}) &= \arg\min_{q \in \{0,1\}^N} \arg\min_{r \in \mathbb{R}^N} \left( \frac{1}{2} \| y - A(q \circ r) \|_2^2 \\ &+ \sum_k \frac{\gamma_k}{2} \| \Gamma_k (q \circ r) \|_2^2 + \lambda \| q \|_0 \right). \end{aligned}$$

(17)

11

6

Here,  $\hat{r}$  is the estimated value of the N-dimensional source signal and each element  $r_i$  in r represents the real-number value of the *i*-th element in the source signal.  $\hat{q}$  is the estimated value of a support vector, which represents the places of the non-zero elements in the N-dimensional source signal. The entry  $q_i$  in q takes either 0 or 1 to indicate whether the *i*-th element in the source signal is zero or non-zero. The symbol o denotes the Hadamard (element-wise) product. From the elementwise representation of Eq. 17, the Hamiltonian of LORBCS can be written as

$$\mathcal{H} = -\frac{1}{2} \sum_{i,j=1}^{N} J_{ij} r_i r_j q_i q_j - \sum_{i=1}^{N} g_i r_i q_i + \lambda \sum_{i=1}^{N} q_i, \quad (18)$$

$$J = -A^T A + \sum_k \gamma_k \Gamma_k^T \Gamma_k, \quad g = A^T y. \quad (19)$$

This Hamiltonian is the same as the QUBO Hamiltonian in Eq. 2. Therefore as described in the above sections, Algorithm 1 (openloop CIM) and Algorithm 2 (closed-loop CIM) for QUBO can optimize the Hamiltonian of LORBCS with respect to q under the condition that r is fixed, whereas Algorithm 3 (Jacobi SOR) can optimize the Hamiltonian of LORBCS with respect to r under the condition that q is fixed.

As shown in Fig. 1, the architecture we have proposed alternate repeatedly between open-loop CIM or closed-loop CIM, and Jacobi SOR to perform alternative optimization of the Hamiltonian in Eq. 18 [36], [37], [61]. Details of the alternative optimization are shown in Algorithm 4. As mentioned above,  $\lambda$ in Eq. 18 is related to  $\eta$  in Eq. 5 by  $\eta = \sqrt{2\lambda}$  [36].  $\lambda$  is set to satisfy this relationship.

Algorithm 4 Alternating minimization of LORBCS as a QUBO problem. The schedules of the pump rate and threshold are given in Section 2.7

- **Require:** J matrix:  $J = -A^T A + \sum_k \gamma_k \Gamma_k^T \Gamma_k$ , Zeeman terms:  $g = A^T y$ , Initial value:  $r_{init}$ , Pump rate sequence:  $p \in$  $\mathfrak{R}^{N_{step}}$ , Threshold sequence:  $H \in \mathfrak{R}^{N_{outer}}$

- **Ensure:** N-dimensional support vector: q, N-dimensional signal vector: r

- 1:  $r = r_{init}$ .

- 2: for n=1 to Nouter do

- $\eta \leftarrow H_n$  (if open-loop) or  $\lambda \leftarrow H_n^2/2$  (if closed-loop). 3:

- Minimize  $\mathcal{H}$  with respect to  $\sigma$  by QUBO-open-loop CIM 4: (Algorithm 1) or QUBO-closed-loop CIM (Algorithm 2).

- Minimize  $\mathcal{H}$  with respect to r by Jacobi SOR (Algorithm 5: <mark>3</mark>). A for

7: return  $\sigma$  and r

### G. Parameter configuration

Parameter settings for the experiments comparing FPGA and GPU implementations are described below. Parameter values for each algorithm on each experiment are summarized in Table I. These values were determined based on our previous research results [57], [36], [37], [61]. The schedules of the pump rate The schedule of the pump rate p for open-loop CIM (Algorithm 1) was set as follows.

$$p(t) = p_{max} \left(\frac{t}{N_{step}\Delta t}\right)^2,$$

where t is the time in Eq. 3, normalized to the photon lifetime.  $N_{step}$  and  $\Delta t$  are the number of loop repetitions and time interval for the TE calculation in Algorithm 1, and  $N_{step}\Delta t$  corresponds to the end time of TE.  $p_{max}$  is the maximum value of the pump rate. These parameter settings are shown in Table I.

The schedule of the pump rate p for closed-loop CIM (Algorithm 2) was given by the following.

$$p(t) = p_{tr} - dp + \frac{2dp}{1 + \exp(-(t-4)/2)}.$$

Here, t is the time in Eq. 6, normalized to the photon lifetime, and  $p_{tr}$  is the baseline of the pump rate, and dp is the variation range of the pump rate. These parameter settings are shown in Table I.

The schedule of the threshold  $\eta$  in the alternating optimization for LORBCS (Algorithm 4) is given by the following function for both open-loop CIM and closed-loop CIM.

$$\eta(n) = \max\left(\eta_{init} \frac{n-1}{N_{outer} - 1}, \eta_{end}\right),\,$$

where *n* is the loop step for alternating optimization (a natural number), and  $N_{outer}$  is the number of loop repetitions.  $\eta_{init}$  is the initial value for the threshold, and  $\eta_{end}$  is the final value for the threshold. The settings for these parameters for each experiment are shown in Table I.

#### III. EXPERIMENTAL ENVIRONMENT

We evaluate the computation accuracy and running time of Algorithms 1 to 4 on the following FPGA and GPU systems.

For the GPU implementation, we used an NVIDIA Quadro RTX 8000 (4608 CUDA cores, 48 GB GDDR6 memory, 16.3 TFLOP 32-bit floating-point operations). We used a machine with an AMD RIZEN9 4950X CPU and 128GB of memory, connected to the GPU by 16 PCI Express 3.0 interfaces. The OS was Ubuntu 22.04.3. Algorithms 1 to 4 were programmed in CUDA. The CUDA programs were compiled using the mexcuda compile command in MATLAB, and linked to shared libraries called MEX functions that can be called from MATLAB. In MATLAB, we performed pre-processing such as generating the *J* matrix and the Zeeman term. These were passed to the MEX functions to perform calculation on the GPU, and the results were returned to MATLAB through the MEX functions, for graphing and other post processing.

For the FPGA implementation, we used Xilinx ALVEO U250s (INT8 TOPs (peak) 33.3, 1,728K look-up tables (LUTs), 54MB internal SRAM, 38Tb/s total internal SRAM bandwidth). We used a machine with an AMD RIZEN9 3950X CPU and 64GB of memory, which was connected to the FPGA by 16 PCI Express 3.0 interfaces. The OS was Ubuntu 22.04.3. We developed an application programming interface (API) to control the FPGA. This API was used to program Algorithms 1

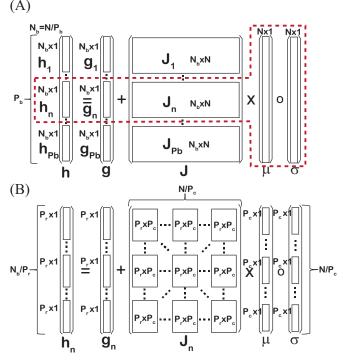

Fig. 2. Indexes  $P_b$ ,  $P_r$ , and  $P_c$ , showing the parallelization format used for matrix-vector multiplication in the local field calculation. (A) Block parallelization index  $P_b$  of local field calculation. The local field calculation is partitioned into  $P_b$  blocks, and the process in (B) is applied to each block in parallel. (B) Matrix-vector multiplication parallelization indices  $P_r$  and  $P_c$  of block-partitioned local field calculation. In a parallel MAC operation, a  $P_r \times P_c$ matrix and  $P_c$ -dimensional vector are multiplied. By repeating this  $N/P_c$ times,  $P_r$  entries of local field have been calculated. This local calculations repeated  $N_b/P_r$  times to have completely calculated all entries of local field.  $N_b = N/P_b$ .

to 4 in the C programming language. These coded C programs were compiled and linked into MEX functions and static libraries of the FPGA control APIs. As with the GPU case, we performed preprocessing in MATLAB as described above, passed the data to MEX functions to be processed by the FPGA, and the results from the FPGA were passed back to MATLAB through the MEX functions for graphing and other post processing.

#### IV. FPGA ARCHITECTURE

#### A. Parallelization scheme and index definitions

In this section, we redefine the indices  $P_b$ ,  $P_r$  and  $P_c$ , introduced to explain the parallelization scheme in Toshiba's FPGA implementation of SB (FPGA-SB) [39], [40].

Fig. 2 shows the parallelization scheme for matrix-vector multiplication in the local field calculation that is assumed for these indices. This schematic diagram shows the parallelization into  $P_b$  blocks (Fig. 2 (A)) and the  $P_r \times P_c$  parallel multiply-accumulate (MAC) operations in each of  $P_b$  blocks (Fig. 2 (B)). The local field calculation is firstly partitioned into  $P_b$  blocks as shown in Fig. 2 (A). The local field h, Zeeman term g and coupling matrix J are allocated for the  $P_b$  blocks to get  $\mathbf{h_n}$ ,

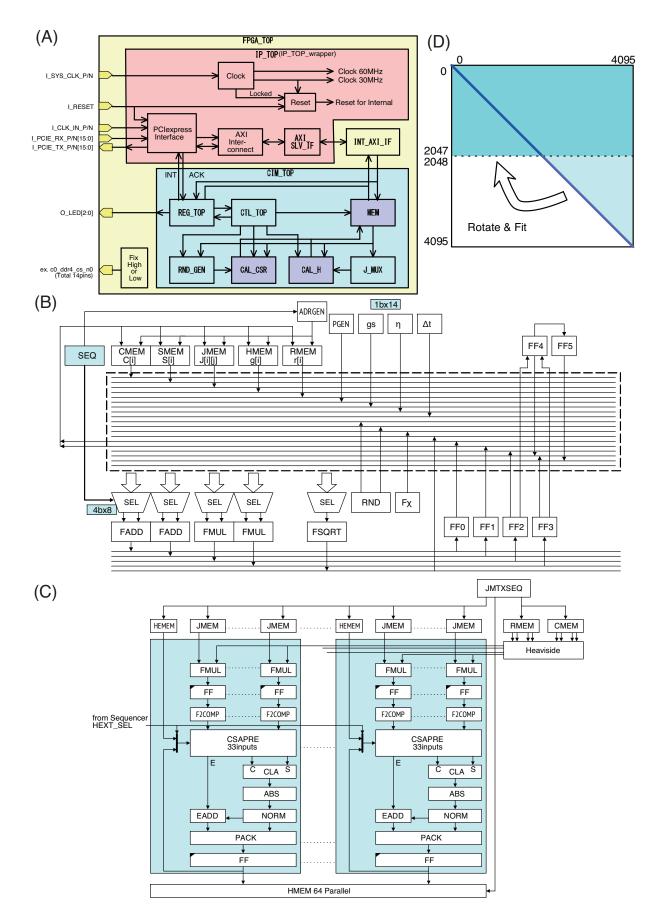

Fig. 3. FPGA architecture. (A) Block diagram showing the relationships between individual FPGA modules. An overview of each module is given in Table II. (B) CAL\_CSR functional diagram. (C) CAL\_H functional diagram. (D) Storage scheme for matrix J.

| Fig. #      | Open-loop CIM (Alg. 1)                                | Closed-loop CIM (Alg. 2)                        | Jacobi SOR (Alg. 3) | Alternating mini. (Alg. 4)                 |

|-------------|-------------------------------------------------------|-------------------------------------------------|---------------------|--------------------------------------------|

| Figs. 6 & 7 | $\Delta t = 0.1, p_{max} = 2, \chi = \text{identity}$ | $\Delta t = 0.02,  p_{tr} = 1,  dp = 0.6$       | -                   | -                                          |

|             | $K = 0.5, N_{step} = 101, g_s^2 = 10^{-7}$            | $\beta = 1, \tau = 1, K = 0.1, N_{step} = 501$  |                     |                                            |

| Fig. 8      | $\Delta t = 0.1, p_{max} = 1.5, \chi = absolute$      | $\Delta t = 0.02,  p_{tr} = 1,  dp = 0.4$       | $\Delta t = 0.3$    | $N_{outer} = 51$                           |

|             | $K = 0.25, N_{step} = 51, g_s^2 = 10^{-7}$            | $\beta = 1, \tau = 1, K = 0.1, N_{step} = 1001$ | $N_{step} = 1001$   | $\eta_{init} = 0.8,  \eta_{end} = 0.18$    |

| Fig. 9      | $\Delta t = 0.1, p_{max} = 1.5, \chi = absolute$      | $\Delta t = 0.02,  p_{tr} = 1,  dp = 0.6$       | $\Delta t = 0.1$    | $N_{outer} = 11$                           |

|             | $K = 0.25, N_{step} = 51, g_s^2 = 10^{-7}$            | $\beta = 1, \tau = 1, K = 0.1, N_{step} = 501$  | $N_{step} = 1001$   | $\eta_{init} = \eta_{end}$ (see main text) |

TABLE I Parameter settings for each experiment

TABLE II Hierarchy and overview of implemented modules

| Layer 1  | Layer 2    | Layer 3    | Layer 4 | Overview                                                           |

|----------|------------|------------|---------|--------------------------------------------------------------------|

| FPGA_TOP |            |            |         | Whole circuit for CIM                                              |

|          | IP_TOP     |            |         | External interface and clock generator                             |

|          |            | IP cores   |         | PCIe interface, Phase locked loop, AXI interconnect, etc.          |

|          |            | AXI_SLV_IF |         | AXI slave interface coded in RTL                                   |

|          | CIM_TOP    |            |         | Main circuit for CIM coded in RTL                                  |

|          |            | REG_TOP    |         | Register sets for storing parameters and settings                  |

|          |            | CTL_TOP    |         | Module for controlling calculation and memory access               |

|          |            | CAL_CSR    |         | Modules for time evolution calculation. 64 parallel modules        |

|          |            | CAL_H      |         | MAC modules for local field calculation. 64 parallel modules       |

|          |            | MEM        |         | Memory group for storing data                                      |

|          |            |            | JMEM    | Store J matrix                                                     |

|          |            |            | HMEM    | Store local field h                                                |

|          |            |            | HEMEM   | Store Zeeman terms $g$                                             |

|          |            |            | CMEM    | Store in-phase amplitudes c                                        |

|          |            |            | SMEM    | Store quadrature phase amplitudes $s$ or feedback errors $e$       |

|          |            |            | RMEM    | Store auxiliary variables r                                        |

|          |            |            | ADMEM   | Store inverse of J's diagonal elements $d$                         |

|          |            |            | PMEM    | Store pump rate sequence <i>p</i>                                  |

|          |            | RND_GEN    |         | Normal random number generator                                     |

|          |            | J_MUX      |         | Read out symmetric matrix from stored upper triangular matrix data |

|          | INT_AXI_IF |            |         | AXI bus interface                                                  |

$\mathbf{g}_{\mathbf{n}}$  and  $\mathbf{J}_{\mathbf{n}}$   $(n = 1, \dots, P_b)$ . For each of the partitioned blocks, the following equation holds.

$$\mathbf{h}_{\mathbf{n}} = \mathbf{g}_{\mathbf{n}} + \mathbf{J}_{\mathbf{n}} \left( \boldsymbol{\mu} \circ \boldsymbol{\sigma} \right), \quad \boldsymbol{n} = 1, \cdots, P_{b}.$$

These calculations are independent of each other, so they can be operated in parallel for each block. For each of these  $P_b$  blocks, the following process is performed in parallel.

As shown in Fig. 2 (B), the matrix-vector multiplication is performed for each block as follows. There are  $P_r$  modules of  $P_c$ -input multiplier-accumulator (MAC), which are used to operate the multiplication of  $P_r \times P_c$  submatrices of  $\mathbf{J_n}$ , with  $P_c$ dimensional partial vectors of  $\mu \circ \sigma$ , in parallel. This is repeated  $N/P_c$  times to complete the calculation of  $P_r$  entries of  $\mathbf{h_n}$ . Then, this calculation is repeated  $N/P_b/P_r$  times to complete the calculation of  $\mathbf{h_n}$ . These operations are performed on  $P_b$ blocks, in parallel.

There are also assumed to be  $P_b \times P_r$  parallel modules to perform the TE calculation, which is the same as the  $P_b \times P_r$ parallelism as the local field calculation described above.

#### B. Architecture overview

The implementation we present is highly versatile and capable of performing the three algorithms above on an identical architecture, as well as being able to represent the coupling matrix J with FP32 accuracy up to the size of  $4096 \times 4096$ . We now give an overview of the architecture we have developed to achieve this. Fig. 3 (A) is a block diagram showing the relationships among each of the modules implemented in the FPGA. The modules in the red part (IP\_TOP) include the external interfaces and clock generation implemented using mainly Xilinx intellectual property (IP) core functions. The modules in the other parts (CIM\_TOP and INT\_AXI\_IF) mainly compute the algorithms described above, which are coded in register transfer level (RTL). Table II gives the hierarchy and overview of these modules shown in Fig. 3 (A). CTL\_TOP, CAL\_H, CAL\_CSR and J\_MUX, which perform the algorithm computations, are described below.

The calculation control module CTL\_TOP controls the calculation sequence. For the FPGA calculation, the MAC process in CAL\_H, the multipliers and accumulators in CAL\_CSR and so on are switched for each cycle. Settings to memory addresses and the switching configuration for multiplexers for each cycle are stored in control code memory. Then, each stored content is sequentially read from the memory at each cycle to control the calculation sequence. Therefore, by rewriting the control code on the memory, various algorithms such as not only the CIM algorithms but also the SB algorithm can be calculated in our architecture in principle.

The functional diagram of the CAL\_CSR module, which calculate TE of each algorithm, is shown in Fig. 3 (B). Memory (in MEM) also appears in the schematic diagram to show connections clearly, but this memory is not actually included in the CAL\_CSR module. Details of MEM are given in Table II. The values of the various parameters ( $g_s$ ,  $\eta$ ,  $\tau$ ,  $\beta$ ,  $\Delta t$ , etc.)

are read out from registers where they are stored. The pump rate for each step is read from PGEN in MEM. CAL\_CSR is composed of two accumulators (FADD), two multipliers (FMUL), a square-root module (FSQRT), a module to perform  $F_{\xi}$  described above and six flip-flops (FFs) to temporarily store calculation results, and these are connected to a databus through selector (SEL). A random-number generator (RND) is also connected to the databus. All these arithmetic modules are FP32. The calculation proceeds by switching the inputs and outputs of these arithmetic modules and the FFs at each cycle under the sequential control from the CTL\_TO described above. The CAL\_CSR has 64 branches in our FPGA system, so it can calculate 64 TE equations simultaneously.

A functional diagram of CAL H, which calculate the local field, is shown in Fig. 3 (C). Memory (in MEM) also appears in the schematic diagram to show connections clearly, but this memory is not actually included in the CAL H module. Details of MEM are shown in Table II. Heaviside in Fig. 3 (C) switches between  $\mu \leftarrow c$  for Ising optimization, and  $\sigma \leftarrow H(c)$  for QUBO, and performs the element-wise multiplication  $\mu \circ \sigma$ . Then inner products of 32-element vectors are performed in one cycle by 32-input FP32 MACs. The CAL H is composed of 64 parallel MAC modules in our FPGA system, so it can multiply a  $64 \times 32$  matrix with a 32-element vector in one cycle. Therefore, there are 2048 MAC processing elements (PEs). Under the sequential control from CTL TO, CAL H also performs addition of the Zeeman term (stored in HEMEM) to the local field, as shown in Fig. 3 (C). However, to prioritize parallel processing, CAL H does not conform to rounding rules in the IEEE 754 FP32.

It is difficult to store the  $4096 \times 4096$  coupling matrix J in FP32 in the internal memory of the FPGA we are using (Xilinx ALVEO U250) while reserving space for the other variables and parameters. However, using external memory would greatly reduce the speed of the calculation. Since almost all optimization problems we deal with have symmetric coupling matrices, it is sufficient to store the upper triangle of coupling matrix J, so only half the space needed for the entire matrix needs to be stored. As such, we store the matrix J in the internal memory in a special format shown in Fig. 3 (D). However, for the calculation of CAL Hit is necessary to read the original symmetric matrix from the J data stored in this special format. J MUX is a multiplexer that fills-in the symmetric matrix entries from the data in memory. This enables us to implement the local field calculation under full-coupling with FP32 representation up to the system size of N = 4096 on a single FPGA.

Table III summarizes the specifications of the FPGA architecture we have constructed. For comparison, the specifications for FPGA-SB are shown in Table IV [39], [40]. Our architecture allows the configuration of Zeeman terms with FP32, which is not configurable in the FPGA-SB. In the FPGA-SB, the entries of the coupling matrix J are represented with one bit as [-1, 1], but in our implementation, those of J are represented with FP32 values. For calculating TE of equations, FPGA-SB uses 16-bit fixed-point operations, while our system uses FP32 operations.

For the parallelization indices for the local field calculation defined in the previous section, FPGA-SB uses  $P_r = 32$ ,  $P_c = 32$  and  $P_b = 8$ , while our implementation uses  $P_r = 64$ ,

$P_c = 32$  and  $P_b = 1$ . Thus, the number of MAC PEs in our implementation is 2048 while that in FPGA-SB is 8192, which is four times as many as our implementation. However, in our implementation the coupling marix *J* is represented with FP32, while in FPGA-SB that is represented with one bit. Table III also summarizes the number of cycles and processing time per TE step when processing Algorithms 1, 2 and 3 for different system sizes *N*. Detail evaluations of the numbers of cycles and processing times are given in the next sections.

TABLE III Specification of FPGA Cyber CIM

|                                           | N = 1024     | N = 2048     | N = 4096     |

|-------------------------------------------|--------------|--------------|--------------|

| Zeeman terms                              | Configurable | Configurable | Configurable |

| Architecture                              |              |              |              |

| Precision of J                            | Single float | Single float | Single float |

| Precision of TE                           | Single float | Single float | Single float |

| $P_r/P_c/P_b$                             | 64/32/1      | 64/32/1      | 64/32/1      |

| # of MAC PEs                              | 2048         | 2048         | 2048         |

| Cycles per step                           |              |              |              |

| Algorithm 1                               | 1030         | 3075         | 10245        |

| Algorithm 2                               | 1030         | 3075         | 10245        |

| Algorithm 3                               | 580          | 2180         | 8453         |

| <b>Processing time per step</b> $[\mu s]$ |              |              |              |

| Algorithm 1                               | 34.3         | 102.5        | 341.5        |

| Algorithm 2                               | 34.3         | 102.5        | 341.5        |

| Algorithm 3                               | 19.3         | 72.7         | 281.8        |

| Operating Clock Frequency                 |              |              |              |

| $F_{sys}$ [Mhz]                           | 30           | 30           | 30           |

TABLE IVSpecification of FPGA SB [39], [40]

| N = 2048           | N = 4096                                                             |

|--------------------|----------------------------------------------------------------------|

| none               | none                                                                 |

|                    |                                                                      |

| 1 bit              | 1 bit                                                                |

| 16-bit fixed point | 16-bit fixed point                                                   |

| 32/32/8            | 32/32/8                                                              |

| 8192               | 8192                                                                 |

| 624                | 2224                                                                 |

| 2.2                | 8.3                                                                  |

|                    |                                                                      |

| 279                | 269                                                                  |

|                    | none<br>1 bit<br>16-bit fixed point<br>32/32/8<br>8192<br>624<br>2.2 |

TABLE V Estimated cycles per step

|             | $C_e$ | N = 1024 | N = 2048 | N = 4096 |

|-------------|-------|----------|----------|----------|

| Algorithm 1 | 32    | 1024     | 3072     | 10240    |

| Algorithm 2 | 32    | 1024     | 3072     | 10240    |

| Algorithm 3 | 4     | 576      | 2176     | 8448     |

| SB          | ?     | -        | 576      | 2176     |

#### C. Evaluation of number of cycles

In this section, according to the indices of the parallelization scheme described above, we evaluate the number of cycles required by the proposed architecture to perform calculations.

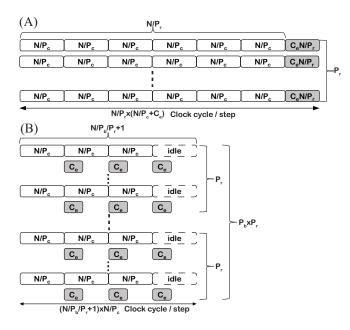

We first evaluate the number of cycles needed to process one step including the local field and TE calculations for Algorithms 1, 2 and 3. Fig. 4 (A) shows a schematic diagram of the number of cycles required for one step in the parallelization scheme used by the proposed architecture. Our FPGA implementation does not adopt the block parallelization, so  $P_b = 1$ . For processing of one step, the TE computation is performed immediately after the local field calculation. The individual MAC operation for local field calculation requires one cycle and the individual TE calculation requires different numbers of cycles depending on the algorithm. To derive a general expression that does not depend on the algorithm implemented, we express the number of cycles for TE as  $C_e$ . As described above, a  $P_r \times P_c$  parallel MAC operation is repeated  $N/P_c$  times, and this calculation is repeated  $N/P_r$  times to complete all local field calculations. Thus, the calculation of local field requires  $N/P_c \times N/P_r$  cycles. For the TE calculation, there are  $P_r$  modules so calculating NTE equations will require  $N/Pr \times C_e$  cycles. Totaling these cycle counts gives an estimate of the number of cycles required to process one step.

$$N/P_r \times (N/P_c + C_e) \,. \tag{20}$$

As shown in Table III, our FPGA architecture adopts  $P_b = 1$ ,  $P_r = 64$  and  $P_c = 32$ . Table **V** gives  $C_e$  for each Algorithm and estimates of the number of cycles per step depending on the system size N. There is a difference of several cycles between these estimates and the measured values shown in Table III. These differences are due to processing overhead.

Fig. 4. Parallelization scheme and number of cycles per step. (A) Our architecture ( $P_b = 1$ ). (B) FPGA-SB ( $P_b > 1$ ).

#### D. Comparison with cycles for FPGA-SB

We now compare the number of cycles required for FPGA-SB with that required for our system.

FPGA-SB adopts block parallelization, so  $P_b > 1$ . Fig. 4 (B) shows a schematic diagram of the number of cycles per step in the parallelization scheme used by FPGA-SB [39]. The local field and TE calculations are parallelly operated by shifting those initial timings as shown in Fig. 4 (B). The individual MAC operation for local field calculation requires one cycle and the individual TE calculation requires  $C_e$  cycles. As described above, the  $P_r \times P_c$  parallel MAC operation is repeated  $N/P_c$  times, and this calculation is repeated  $N/P_b/P_r$ times. These computations are performed on  $P_b$  blocks in parallel, to complete all local field calculations. As such, the number of cycles required for local field calculations is  $N/P_c \times N/P_b/P_r$ . Then, as shown in Fig. 4 (B), the TE calculation is executed after the first  $N/P_c$  cycles in which the local field calculation required for this calculation is completed, and thereafter similarly executed every  $N/P_c$  cycles. In order to secure the interval necessary for the final TE calculation, an idle interval of  $N/P_c$  cycles is reserved. Thus, an estimate of the number of cycles required to process one step is given by:

$$(N/P_b/P_r + 1) \times N/P_c \tag{21}$$

As shown in Table IV, the single-FPGA implementation of SB adopts  $P_b = 8$ ,  $P_r = 32$  and  $P_c = 32$  [39], [40]. Table V shows the estimated number of cycles for FPGA-SB depending on the system size N. These estimates differ from the measured values in Table IV by about 50 cycles. These differences are due to processing overhead.

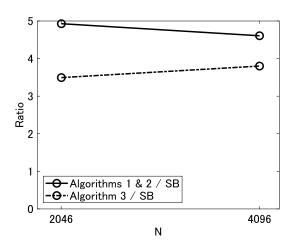

As can be seen in Fig. 4, the main reason of the difference in the number of cycles per one step between our FPGA system and FPGA-SB is the difference in the degree of parallelism. The number of parallels in our architecture is  $P_r = 64$ , while that in FPGA-SB is  $P_b \times P_r = 256$ , so we can estimate that our architecture requires about four-times as many cycles as FPGA-SB. We calculate the ratios of number of cycles per step for our architecture (Table III) and FPGA-SB (Table IV), and show these in Table VI and Fig. 5. For Algorithms 1 and 2, the ratio is greater than four, and for Algorithm 3, it is less than four. This difference is due to the difference in the size of  $C_e$ . However, each entry of the coupling matrix J in our architecture is a single-precision floating point representation, whereas each entry of J in FPGA-SB is a 1 bit representation.

TABLE VI Ratios of cycles per step for our architecture and FPGA-SB

|                  | N = 2048 | N = 4096 |

|------------------|----------|----------|

| Algorithm 1 / SB | 4.928    | 4.607    |

| Algorithm 2 / SB | 4.928    | 4.607    |

| Algorithm 3 / SB | 3.494    | 3.801    |

#### V. PERFORMANCE EVALUATION

Here, we evaluate the performance of the FPGA system we have developed. As evaluation benchmarks, we used the CDMA multi-user detector, which is an optimization problem in the form of the Ising Hamiltonian including Zeeman terms, and LORBCS, which is an optimization problem in the form of the QUBO Hamiltonian including Zeeman terms. Earlier large-scale FPGA systems implementing such as SB and CIM have not been able to handle these problems [35], [39], [40], [41], [56]. Below, we evaluate the performance of our FPGA system for these problems through comparing calculated results and running times with those obtained using the GPU described in the section **Experimental environment**.

Fig. 5. Ratios of cycles-per-step for our architecture and FPGA-SB for N = 2048 and N = 4096

#### A. CDMA multi-user detector (Ising Hamiltonian)

This section focuses on the CDMA multi-user detector, which is an optimization problem in the form of the Ising Hamiltonian with Zeeman terms [57]. In the section **Implemented Algorithms**, we described the optimization problem for the CDMA multi-user detector used in this research. Here, for each entry of the spreading code series,  $\xi_i^{\mu}$ , is set to either +1 or -1 independently with the probability of 1/2 with respect to *i* and  $\mu$ . In this experiment, each user's bit of the information data bits,  $\sigma_i$  is set to 1. Note that an arbitrary bit string of  $[\sigma_1, \dots, \sigma_N]$  can be transformed to  $[1, \dots, 1]$  by performing a Gauge transformation (i.e. a variable transformation with  $\sigma_i c_i := c_i$ ). We then compared the calculated results and running times for parallel implementations with FPGA and GPU of both Algorithm 1 (open-loop CIM) and Algorithm 2 (closedloop CIM).

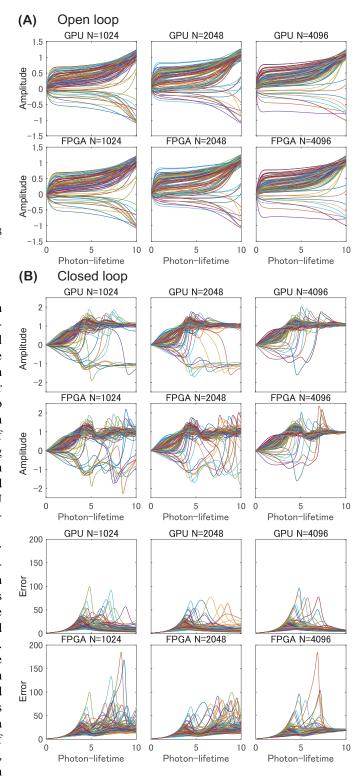

1) Comparison of trajectories during solution exploration: Examples of trajectories during solution exploration by openloop CIM and closed-loop CIM on GPU and FPGA are shown in Fig. 6. In this experiment, using the spreading code series randomly generated with the same random seed under the same diffusion rate of  $\alpha = 0.6$ , the same coupling matrix J and Zeeman terms were configured for all CIMs on GPU and FPGA. For open-loop CIM on both GPU and FPGA in Fig. 6 (A), the initial values for OPO pulse amplitudes were the same, with  $c_{init} = 0$  and  $s_{init} = 0$ . For closed-loop CIM on both GPU and FPGA in Fig. 6 (B), the initial values for OPO pulse amplitudes were the same, with  $c_{init}$  set to the same random values from a standard normal distribution with a mean of 0 and a variance of 0.02, and initial values of feedback errors were also the same, with  $e_{init} = 1$ . Parameter values for this experiment are shown in Table I. Three system sizes were used: N = 1024, N = 2046and N = 4096.

Figure 6 (A) shows 100 OPO pulse amplitudes,  $c_1, \dots, c_{100}$  during solution exploration by open-loop CIM on GPU and FPGA. Figure 6 (B) shows 100 OPO pulse amplitudes,  $c_1, \dots, c_{100}$ , and 100 feedback errors,  $e_1, \dots, e_{100}$  during solution exploration by closed-loop CIM on GPU and FPGA. Under the above conditions, open-loop CIMs on GPU and FPGA

Fig. 6. Trajectories during solution exploration by cyber CIMs on GPU and FPGA. Application of the CDMA multi-user detector. (A) Open-loop CIM. Temporal profiles of OPO pulse amplitudes  $c_1, \dots, c_{100}$ . (B) Closed-loop CIM. Temporal profiles of OPO pulse amplitudes  $c_1, \dots, c_{100}$  and feedback error  $e_1, \dots, e_{100}$ . For both (A) and (B), Spreading code series and initial values used in cyber CIMs on GPU and FPGA were the same. The system sizes of these are N = 1024, N = 2046 and N = 4096. All  $\alpha = 0.6$ .

had the same solution trajectories for each system size *N*. In contrast, even though closed-loop CIMs on GPU and FPGA had the same conditions including initial values, those solution trajectories differed. This difference in solution trajectories for closed-loop CIM may have been because our FPGA system does not adhere to rounding rules of IEEE 754 FP32. Closed-loop CIM has more dynamical complexity due to the CAC [54], so it is more sensitive to this sort of error from rounding in MAC, which could account for differences in solution trajectory for GPU and FPGA.

2) Comparison of decoding performance and running time: We evaluated the decoding performance and running time of open-loop CIM and closed-loop CIM implemented on GPU and FPGA. We generated spreading code series from 50 different random seeds to obtain 50 samples of different coupling matrices J and Zeeman terms. We then compared the decoding accuracy and running times for the open-loop CIM and closed-loop CIM on the parallel FPGA and GPU implementations, using the same 50 samples of coupling matrices J and Zeeman terms. The parameter values used in this experiments are shown in Table I. Three system sizes were used: N = 1024, N = 2046 and N = 4096.

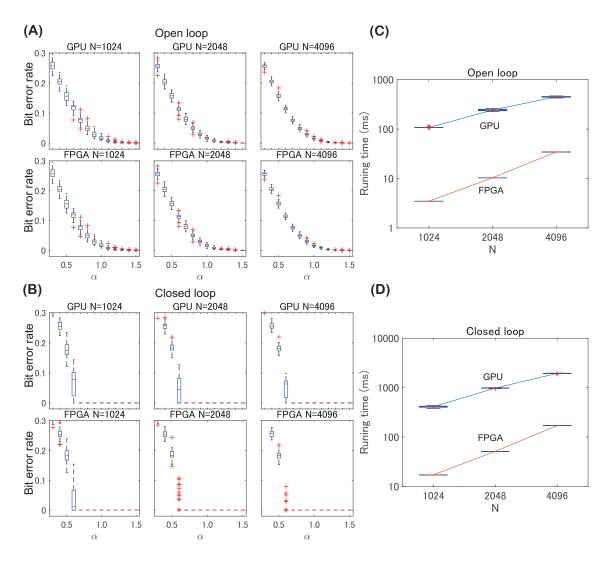

Figure 7 (A) shows a box plot of the relationship between spreading rate  $\alpha$  and bit-error rate for open-loop CIM on GPU and FPGA, and Figure 7 (C) shows the running times for each system size N. Figure 7 (B) and (D) similarly show the relationship between spreading rate  $\alpha$  and bit-error rate, and running times for closed-loop CIM on GPU and FPGA.

As shown in Fig. 7 (A) and (B), with both FPGA and GPU, the bit-error rates were lower for closed-loop CIM than for openloop CIM. This is due to the function of the CAC in closed-loop on FPGA and GPU, establishing the balance between the size of Zeeman and interaction terms, and further the destabilization of local minimum states improving the performance of finding an optimal solution [50], [51], [52], [53], [54], [55], [61]. As also can be seen in Fig. 7 (A), for open-loop CIMs on GPU and FPGA, the bit-error-rate distributions of both were the same for all values of N. On the other hand, as shown in Fig. 7 (B), for closed-loop CIM, even though the same samples of the spreading code series were used for FPGA and GPU, for all values of N the bit-error rate for FPGA at  $\alpha = 0.6$  was lower than the value for GPU. As discussed in the previous section, this difference could be because our FPGA system does not conform to rounding rules of IEEE 754 FP32. Due to the increased dynamical complexity inherent in closed-loop CIM resulting from CAC, they exhibit sensitivity to rounding errors in numerical calculations. Consequently, differing solution trajectories were observed between FPGA and GPU, leading to disparities in decoding performance.

As shown in Fig. 7 (C) and (D), for both open-loop CIM and closed-loop CIM, running time on GPU was 11-times longer than on FPGA. Table VII summarize the median values of running times on FPGA and GPU and their ratios for each system size N. The running times of closed-loop CIM were around five-times longer than those of open-loop CIM for both FPGA and GPU because the number of repetitions  $N_{step}$  was five-times higher. The running times on the FPGA for each system sizes N coincide with the number of cycles estimated using Eq. 20

|                 | N=1024 | N=2048 | N=4096  |

|-----------------|--------|--------|---------|

| Open-loop CIM   |        |        |         |

| FPGA [ms]       | 3.47   | 10.35  | 34.49   |

| GPU [ms]        | 107.20 | 243.42 | 449.85  |

| Time ratio      | 30.89  | 23.52  | 13.04   |

| Closed-loop CIM |        |        |         |

| FPGA [ms]       | 17.20  | 51.35  | 171.09  |

| GPU [ms]        | 411.50 | 979.81 | 1947.52 |

| Time ratio      | 23.92  | 19.08  | 11.38   |

(Table V) divided by the clock frequency (30 MHz). Comparing the time ratios in Table VII, the differences in running times for FPGA and GPU were more noticeable for smaller values of N, suggesting that there is more processing overhead for the GPU case.

#### B. LORBCS (QUBO Hamiltonian)

In this section we focus on LORBCS as an example of the QUBO Hamiltonian with Zeeman terms [36], [37], [61]. In the section **Implemented Algorithms**, we described the LORBCS optimization problems handled in this research. As shown in Fig. 1 and Algorithm 4, our architecture performs LORBCS optimization by alternating between either open-loop CIM (Algorithm 1) or closed-loop CIM (Algorithm 2) and Jacobi SOR (Algorithm 3). When performing CS with open-loop CIM (Algorithm 1) and Jacobi SOR (Algorithm 3) it is called open-loop CS [36], and when performing CS with closed-loop CIM (Algorithm 2) and Jacobi SOR (Algorithm 3) it is called closed-loop CS [37], [61].

We compared the reconstruction accuracy and running times for open-loop CS and closed-loop CS on FPGA and GPU, using the same observation matrices and observed signals.

1) Evaluation of performance with randomly generated observation matrices and observed signals: Under conditions where the ground state can be verified through statistical mechanics, we checked whether the reconstruction by openloop and closed-loop CSs on GPU and FPGA matched the theoretically predicted ground state, and evaluated the running times on the different hardware-implemented CSs.

According to conditions for realizing statistical mechanics analysis for LORBCS in our previous research [36], we configured variables in the observation model defined in Eq. 15 as follows. Each entry  $A_i^{\mu}$  of the observation matrix  $\hat{A}$ was randomly generated from independent identical normal distribution, satisfying  $\langle A_i^{\mu} \rangle = 0$  and  $\langle A_i^{\mu} A_j^{\nu} \rangle = \frac{1}{M} \delta_{ij} \delta_{\mu\mu}$ . For the sparseness a, aN elements of source signal x were generated randomly from independent identical normal distribution with a mean of 0 and a standard deviation of 1, and other elements of x were set to zero. For these experiments, the observation noise standard deviation  $\zeta$  was set to 0.05 and the compression rate  $\alpha$  was set to 0.8. Under these conditions, we used 16 different random seeds to randomly generate observation matrices, source signals and observation noise and then created observation signals according to Eq. 15. This produced 16 samples of coupling matrices J and Zeeman terms according to Eq. 19.

Fig. 7. Comparison of decoding performance and running time for the CDMA multi-user detectors on cyber CIMs implemented with GPU and FPGA. System sizes of these are N = 1024, N = 2046 and N = 4096. (A) Relationship between spreading rate  $\alpha$  and bit-error rate for open-loop CIM on GPU and FPGA. (B) Relationship between  $\alpha$  and bit-error rate for closed-loop CIM on GPU and FPGA. (C) Running time for open-loop CIM on GPU and FPGA. (D) Running time for closed-loop CIM on GPU and FPGA.

For this experiment, we set  $\Gamma_k = 0$ . We then compared the reconstruction accuracy and running times for open-loop CS and closed-loop CS on FPGA and GPU using the same samples of coupling matrices *J* and Zeeman terms. The parameter values for this experiment are given in Table I. Three system sizes were used: N = 1024, N = 2046 and N = 4096.

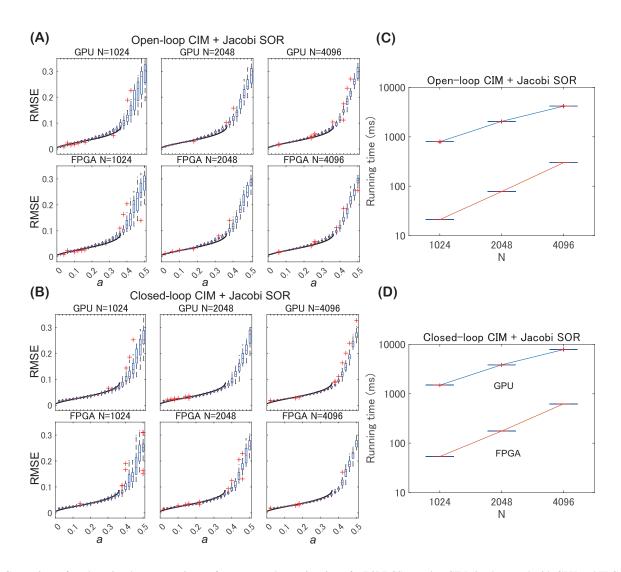

Figure 8 (A) is a box plot showing the relationship between sparseness a and RMSE for open-loop CS on GPU and FPGA, and Fig. 8 (C) is a box plot of running time for one repetition of alternating optimization for each system size N. Similarly, Figures 8 (B) and (D) show the relationship between a and RMSE and the running time per repetition for closed-loop CS on GPU and FPGA. The solid black lines in Fig. 8 (A) and (B) are predicted RMSE values in the ground state for each a, obtained using statistical mechanics analysis.

As shown in Fig. 8 (A) and (B), for both open-loop CS and closed-loop CS, the RMSE distributions for all *N* are the same on both GPU and FPGA. In this experiment, unlike with the CDMA

multi-user detector, we were not able to confirm a difference in reconstruction accuracy between FPGA and GPU for closed-loop CS. Also, as shown in Fig. 8 (A) and (B), when 0.2 < a < 0.35, the RMSE for closed-loop CS on both FPGA and GPU was closer to the theoretically-predicted ground-state RMSE than it was with open-loop CS [37], [61]. This could be due to the function of the CAC in closed-loop CIM on FPGA and GPU, which destabilizes local minimum states, leading to a solution closer to the ground state [50], [51], [52], [53], [54], [55], [61].

Figure 8 (C) and (D) show that for both open-loop CS and closed-loop CS, GPU running times were more than 12-times longer than FPGA times. Table VIII shows the median values of running time on FPGA and GPU and their ratios for each system sizes N. For both FPGA and GPU, running times for closed-loop CS were more than twice as long as for open-loop CS, because the total number of iterations of CIM and Jacobi SOR,  $N_{step}$ , is about double. The running times on the FPGA for each system sizes N coincide with the number of cycles estimated

Fig. 8. Comparison of random signal reconstruction performances and runnning times for L0RBCS on cyber CIMs implemented with GPU and FPGA. For a comparison of cyber CIMs implemented with GPU and FPGA, the same randomly-generated observation matrices and observation signals were set in the both, and these performances and calculation times were evaluated. System sizes of these are N = 1024, N = 2046 and N = 4096. (A) Relationship between sparseness *a* and RMSE for open-loop CS on GPU and FPGA. (B) Relationship between *a* and RMSE for closed-loop CS on GPU and FPGA. The solid-black lines in (A) and (B) are RMSE at a ground state for each *a* predicted with statistical mechanics analysis. (C) Running time per single reputation of alternating optimization in open-loop CS on GPU and FPGA. (D) Running time per single reputation of alternating optimization in closed-loop CS on GPU and FPGA. The compression rate for all figures was  $\alpha = 0.8$ .

TABLE VIII Running-time median value of GPU and FPGA processing L0RBCS with random observation matrix and random source signal

|                      | N=1024  | N=2048  | N=4096  |

|----------------------|---------|---------|---------|

| Open-loop + Jacobi   |         |         |         |

| FPGA [ms]            | 21.10   | 77.97   | 299.47  |

| GPU [ms]             | 796.91  | 2056.85 | 4164.35 |

| Time ratio           | 37.77   | 26.38   | 13.91   |

| Closed-loop + Jacobi |         |         |         |

| FPGA [ms]            | 53.72   | 175.34  | 623.89  |

| GPU [ms]             | 1493.55 | 3855.67 | 7830.34 |

| Time ratio           | 28.18   | 21.99   | 12.55   |

using Eq. 20 (Table V) divided by the clock frequency (30 MHz). Comparing the time ratios in Table VIII, the differences in running times for FPGA and GPU were more noticeable for smaller values of N, suggesting that there is more processing overhead for the GPU case.

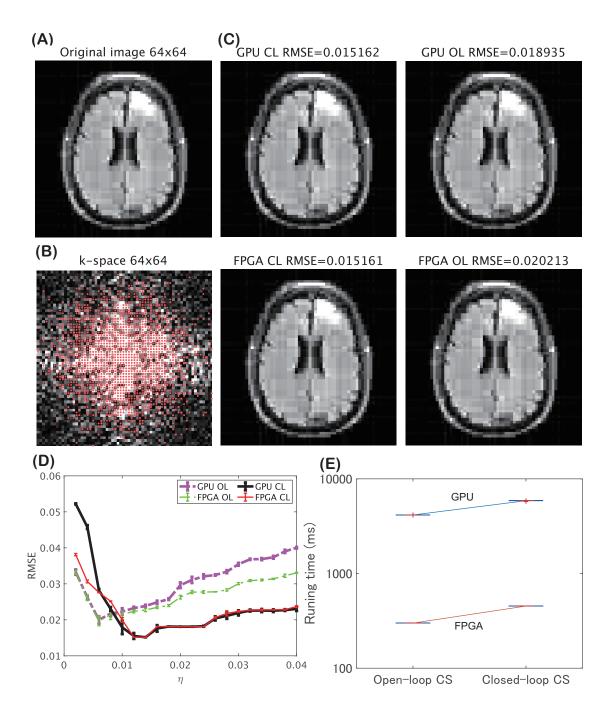

2) Performance evaluation with MRI data: Using MRI data, we evaluate the performance of open-loop CS [36] and closedloop CS [61] on GPU and FPGA. The image used for this evaluation is a cross-sectional image from the fastMRI data set [67], converted to a 64x64 pixel size. We applied a Haarwavelet transform (HWT) to the data, and selected the top 18.2% components with large HWT coefficients to create a signal spanned by Haar basis functions with a sparseness of 0.182 (Fig. 9 (A)). We applied a discrete Fourier transform (DFT) to the image to obtain the k-space data shown in Fig. 9 (B). From this k-space data, we sampled 40% of the k-space data at random red points obeying a two-dimensional normal distribution. Thus, we performed random undersampling with a compression rate of  $\alpha = 0.4$ . In this experiment, we generated 16 sets of random undersampling points from 16 different random seeds. The red scattered points in Fig. 9 (B) show an example of the random sampling points.

Fig. 9. Comparing MRI image reconstruction performances and running times for open-loop CS and closed-loop CS on GPU and FPGA. Using 64x64 pixel (N=4096) MRI data, we evaluate performance of open-loop CS and closed-loop CS on GPU and FPGA. (A) 64x64 pixel original image. This image is composed of 18.2% of all Haar bases. Thus, sparseness a = 0.182. (B) k-space data for original image. The red points are random sampling points obeying a normal distribution. Undersampling was executed at a compression rate of  $\alpha = 0.4$ . (C) Example of images reconstructed with open-loop CS and closed-loop CS on FPGA and GPU from observed data obtained through random under-sampling in (B). Minimum error images and corresponding RMSE under each of the different hardware implemented the CSs. CL: closed-loop CS. OL: open-loop CS. Thresholds for minimum RMSE in each are  $\eta = 0.006$  for GPU OL,  $\eta = 0.006$  for FPGA OL,  $\eta = 0.014$  for FPGA CL. (D) The relationship between RMSE and threshold  $\eta$  in each case calculated with the same 16-samples of the random sampling point set. (E) Running time per repetition of alternating optimization in each case.

Based on the above conditions, we performed LORBCS optimization on the Haar space. The coupling matrix J and Zeeman terms for compressed sensing as defined in Eq. 19 were set as follows.

$$A = SF\Psi^{T}, \ \Gamma_{1} = \Delta_{h}\Psi^{T}, \ \Gamma_{2} = \Delta_{v}\Psi^{T},$$