# Empowering Malware Detection Efficiency within Processing-in-Memory Architecture

Sreenitha Kasarapu\*, Sathwika Bavikadi\*, Sai Manoj Pudukotai Dinakarrao

Department of Electrical and Computer Engineering, George Mason University, Fairfax, VA, USA {skasarap, sbavikad, spudukot}@gmu.edu

Abstract—The widespread integration of embedded systems across various industries has facilitated seamless connectivity among devices and bolstered computational capabilities. Despite their extensive applications, embedded systems encounter significant security threats, with one of the most critical vulnerabilities being malicious software, commonly known as malware. In recent times, malware detection techniques leveraging Machine Learning have gained popularity. Deep Neural Networks (DNNs) and Convolutional Neural Networks (CNNs) have proven particularly efficient in image processing tasks. However, one major drawback of neural network architectures is their substantial computational resource requirements. Continuous training of malware detection models with updated malware and benign samples demands immense computational resources, presenting a challenge for real-world applications. In response to these concerns, we propose a Processing-in-Memory (PIM)-based architecture to mitigate memory access latency, thereby reducing the resources consumed during model updates. To further enhance throughput and minimize energy consumption, we incorporate precision scaling techniques tailored for CNN models. Our proposed PIM architecture exhibits a  $1.09 \times$  higher throughput compared to existing Lookup Table (LUT)-based PIM architectures. Additionally, precision scaling combined with PIM enhances energy efficiency by 1.5× compared to full-precision operations, without sacrificing performance. This innovative approach offers a promising solution to the resource-intensive nature of malware detection model updates, paving the way for more efficient and sustainable cybersecurity practices.

#### I. INTRODUCTION

With the technical developments in hardware architecture and embedded systems, IoT applications have procured enormous interest in the past few decades [1]. The immense desire to automate user applications and interactive software systems such as smart homes, smart grids, and digital monitoring has led manufacturers to produce massively. These automated devices connect to the internet over a network for communicating between devices. As these devices have medical and activitytracking abilities, it is important for them to communicate. They handle vast amounts of user data daily and are targeted by cyber-attackers. These systems are vulnerable to security threats [2] due to malware. Malware is malicious software developed to infect a system to explore and steal information such as passwords, and financial data, and manipulate the stored data without the user's consent. In the year 2021 alone, there were more than 5.4 billion recorded malware attacks [3]. The first half of the year 2022 had 2.8 billion malware attacks. Despite the advanced anti-malware software, malware attacks increase in millions each year [3]. This is due to the newer emerging malware each year. Adversaries generate millions of new signatures of malware each year [4] to steal valuable information for financial benefit and stay undetectable. The massive increase in cyber attacks due to malware poses a huge threat to hardware security [5]. The exploitation of confidential user information leads to substandard user experience, so it is vital to detect the malware. Realizing the threat caused by malware in terms of access to sensitive information, stolen information, and billions of revenue loss, severe measures are being taken to abate malware escalation.

Static and dynamic analysis [6] is employed for malware detection. Static analysis [6] is performed in a non-runtime environment by examining the internal structure of malware binaries and not by actually executing the binary executable files. In dynamic analysis, the binary applications are inspected for malware traces by executing them in a harmless, isolated environment [6]. Unlike static analysis, dynamic analysis is a functionality test. The static analysis serves as quick testing but is not efficient. Though efficient dynamic analysis is a bulky and time-consuming process.

Malware detection using Machine Learning (ML) is seen as an efficient technique [7]. A variety of Machine Learning (ML) and Federated Learning techniques [8] depict superior malware detection capability than the static and dynamic analysis methods [9]. Among the ML-based malware detection techniques, the CNN-based image classification technique [10] is more robust and efficient due to its prime ability to learn image features. However, one of the main challenges with adopting such a technique is the requirement of enough samples for training. With the exponential increase in the generation of newer malware families each year, it is complex to train a model on heterogeneous data and update it frequently. With the increase in the need for updating, the training overhead increases consistently.

In this study, we propose a novel approach for malware detection to utilize the in-memory computing technique. Processing-in-memory (PIM) is a novel computing paradigm in which the memory chip is enhanced with computing capabilities. This essentially restricts the circulation of the data within the memory chip and thereby drastically minimizes the power consumption and latency caused by the data movements. In addition, a PIM architecture takes advantage of its proximity to the data to perform massively parallel

<sup>§\*</sup>Both authors contributed equally to this research

computing. Therefore, such a PIM paradigm is particularly suitable for data-intensive applications like deep learning (DL) and optimization problem.

Several recent studies have proven that PIM architectures outperform GPU and CPU designs for training deep neural networks (DNN) and combinational optimization problems in terms of throughput and energy efficiency. While traditional PIM architecture, like bitline-wise architecture [11] and analog crossbar array architecture [12], have been regarded as better alternatives to conventional computing hardware for executing the heavy computational load of DNN. These architectures suffer from the complexity and overhead associated with digitalto-analog (DAC) and analog-to-digital (ADC) conversions. Unlike the bitwise processing PIMs, the recently developed Look-up-table based (LUT-based) PIMs have been found to be more flexible, with superior energy efficiency for a similar level of performance, such as LAcc [13] and pPIM [14]. This feature makes the LUT-based PIM architecture more suitable for performing adversarial attack generation.

In this work, we address all the issues mentioned above. We propose a technique that can effectively detect malware with limited resources. We propose a PIM-based technique that changes the memory access capabilities. Thus improving the inference throughput. We further employ precision scaling to decrease power consumption.

The novel contributions of this work can be outlined in a three-fold manner:

- A memory-efficient malware detection by using an inmemory computation technique.

- Precision scaling to decrease the power consumption of malware detection model.

- Scaling malware samples to 16-bit, 8-bit, and 4-bit integer types and still retaining a malware detection accuracy of 98%.

The rest of the paper is organized as follows: Section II describes the related work and its shortcomings and comparison with the proposed model. Section III describes the problem formulation. Section IV describes the proposed architecture, which assists with the proposed PIM-based malware detection model training. The experimental evaluation of the proposed model and comparison with various ML architectures is illustrated in Section V, and then we conclude in Section VI.

#### II. RELATED WORK

# A. Malware Detection Techniques

Static analysis [6] on malware data is performed by comparing the opcode sequences of binary executable files, control flow graphs, and code patterns. The main drawback of static analysis is, it cant detect malware when adversaries add junk of unrelated functionalities, which decreases the malware similarity score [15]. Malware detection using dynamic analysis is performed based on detecting system calls or HPC [6]. But they are not efficient in detecting hidden malware code blocks and are computationally expensive.

Later [9] introduced a technique for malware detection using image processing where binary applications are converted into grayscale images. The generated images have identical patterns because of the executable file structural distributions. The paper used the K-Nearest Neighbour ML algorithm for the classification of malware images. Other approaches [7] include image visualization and classification using machine learning algorithms such as SVM. However, these approaches don't address the problem of classifying newer complex malware that is code obfuscated, polymorphed, etc. Neural networks such as ANNs are used extensively to solve the problem [16], as neurons can capture the features of the images more accurately than other machine learning algorithms. But, the fully connected layers of artificial neural networks tend to exhaust computational resources. In [10], [17], [18], [19], [20], [21], [22], [23], [24], [25], [26], [27], [28], [29], [30], [31], [32], [33], [34], [35], [36], [37], [38], [39], [40], [41] authors used Convolutional neural networks, as they are popular for their ability to efficiently handle image data through feature extraction by Convolutional 2D layers and using Maxpooling 2D layers to downsample the input parameters, thus, reducing the computational resources. The drawback here is, they need to be trained with a balanced dataset to perform classification efficiently, but with an increase in malware families, collecting each type of malware for training is challenging.

#### B. Processing-in-Memory (PIM)

In recent years, PIM designs have received a lot of attention from DNN/CNN applications. PIMs have been regarded as a better alternative to conventional computing hardware for executing the heavy computational load imposed by the convolutional layers of a CNN. In contrast to the CPU or GPU-based architecture, computational functions for the PIM architecture are executed in the memory itself. Thus, this eliminated the need for time- and energy-intensive data movement. Consequently, the PIM architecture can reduce the latency and energy costs associated with data movement.

Moreover, with the integration of memory and processing capability, the PIM architecture is able to efficiently execute matrix-vector multiplication (MVM) operations, which are fundamental computing operations in various disciplines of research such as signal processing, machine learning [14], deep learning [42], [43], [44], [45], [46], and stochastic computing, image processing, and recognition [47], data mining [14], and cryptographic [48].

Numerous works have been proposed on in-memory computing hardware accelerators on different memory platforms including the traditional memory platforms of Static and Dynamic Random Access Memory (SRAM & DRAM) [49] as well as novel non-volatile Resistive RAM (ReRAM) [50], Phase-changing Memory (PCM), and Magnetic RAMs such as Spin Transfer Torque MRAM (STT-MRAM) [12], and Spin-Orbit Torque MRAM (SOT-MRAM) [51] technologies. It has been found that a satisfactory level of accuracy can be retained even despite performing various levels of quantization/downscaling of data parameters in CNN algorithms [42]. This opens up an exploration space for high-performance and low-power CNN implementations for real-time application domains such as IoT, mobile, and edge applications. The PIM architecture is gaining popularity in real-time application domains. To the best of the authors' knowledge, the PIM architecture has not been utilized in the context of malware detection.

#### **III. PROBLEM FORMULATION**

With technology advancements, attackers are introducing, any complex malware families, making it impossible for embedded systems to keep track. Even advanced anti-malware software fails to detect these advanced malware families [52]. One can define the problem of reliable malware detection in embedded devices as follows:

$$\mathbb{D} \leftarrow [B_1^m, M_1^n, B_2^m, M_2^n, B_3^m, M_3^n, \cdots, B_q^m, M_r^n]$$

(1)

As shown in Equation (1), B represents benign and M represents the malware executables for embedded systems. The  $B^m$  represents the  $m^{th}$  benign sample,  $B_q^m$  represent the q number of patterns in a given  $m^{th}$  sample. Similarly,  $M^n$  represents the  $n^{th}$  malware sample,  $M_r^n$  represent the r number of patterns in a given  $n^{th}$  sample. These benign and malware are stored in dataset  $\mathbb{D}$ .

$$C(\mathbb{D}): X \to Y$$

s.t.  $\mathbb{D} \leftarrow \iint_{a}^{b}(B_{q}^{m}, M_{r}^{n}) dq dr$  (2)

In Equation 2, C is a classifier model trained with dataset  $\mathbb{D}$  to perform malware detection. After training, the classifier C will be able to classify any input sample X and map it to either malware class M or benign class B. The output class is represented as Y. New benign and malware samples are needed to train and keep the malware detection model updated. As represented by the integral of (B, M), for each new pattern of benign q and malware r, the classifier C needs to be updated. The limit a, b represent the newer patterns of data to be added for training.

$$S = f_0 + \sum_{i=1}^d f_1 \cdot P^{-i} + \sum_{j=1}^d f_2 \cdot I^{-j}$$

(3)

So the problem that arises with consistent data updation i.e,. the need for huge computational resources can be formulated as shown in Equation 3. We build a dual optimization problem, by considering input data precision P and in-memory data processing steps I. The aim is to optimize these both parameters, as by doing so we can decrease the computational resources. Where,  $f_0$ ,  $f_1$  and  $f_2$  are optimization constants. The d represent the size of the dataset  $\mathbb{D}$ . For each data point ranging from  $(1, 2, \dots, d)$  the input precision P and the inmemory processing speed I is optimized.

Our proposed technique solves this by introducing a novel malware detection framework using PIM-based memory access, processing technique and also employing input precision scaling. These improve the resource consumption and throughput of machine learning model used for malware detection.

# IV. PROPOSED TECHNIQUE

# A. Overview of the Proposed Technique

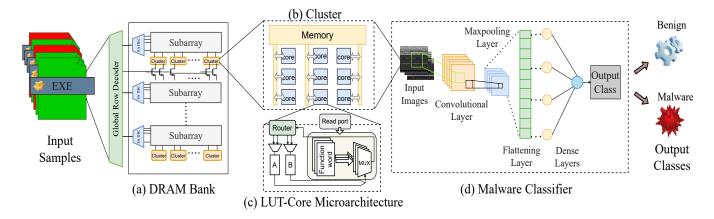

The overview of the proposed technique follows the flow as shown in Figure 1. The input data samples are stored in the DRAM memory bank represented in Figure 1(a). Inmemory processing is employed using a DRAM cluster to improve memory access time. The architecture of each DRAM cluster is represented in 1(b). Each cluster has the LUT-core represented as 1(c). The input binary samples are processed in the memory and converted into images. As this is done using an in-memory processing technique, there was no need for excessive data movement. Once the data is accessed from memory it is given as input to the malware classifier given in 1(d). The test data used for inference is precision scaled using uniform quantization. The different elements in the proposed technique are:

- *PIM Unit*: A novel PIM architecture is employed to decrease the memory access latency. In-memory processing would improve throughput and limit resource consumption.

- *Precision-scaling*: While retaining the malware detection accuracy, a low-precision version of data is employed to decrease the power consumption.

- *Malware Classifier*: Optimized input samples are fed to the Convolutional Neural Network for training the classification model.

#### B. Malware Detection Model

Computer vision-based machine learning (ML) techniques need images for localized feature extraction. So the input binaries (malware and benign) are converted into grayscale images. The binary applications files are converted into a raw binary bitstream. This binary bitstream is then converted to an 8-bit vector. Each 8-bit vector containing the binary values is taken as a byte, representing different image pixels. Each of these 8-bit vectors is arranged to form an image. The size of the gray-scale image varies with the size of the binary file. To train a CNN, the input data must be uniform. To address this challenge, we perform image resizing and scaling in order to make its size uniform. As the pattern or sub-pattern of malware cannot alter despite embedding the malware to launch malicious payload, through this technique the malware can be detected with a higher performance (around 98% accuracy).

Using this process, a training dataset is generated as shown in equation (1) which consists of several sequences for a variety of classes of malware (backdoor, rootkit, trojan, virus, and worm) and benign applications. So, a CNN model is trained using these data samples for classification as shown in Figure 1(d). As the processing is done in memory, this data is not circulated within the memory chip. Thus, decreasing the computation steps and resources. Feature extraction is done on the images using the convolutional 2D layers of the CNN architecture, followed by the max-pooling 2D layers. The data is then flattened to pass it to the dense layers, to decide the output class. The mac operations in each of these layers are

Fig. 1. Hierarchical view of the architecture implementation of malware detection on the processing in-memory architecture

accommodated by PIM architecture by programming the LUT cores inside the cluster as shown in Figure 1(c). The CNN classifier trained on input data can be defined as shown in equation 2. The classifier C: trained on data X, maps the input to the class label Y.

The classification accuracy  $a(\cdot)$ , can be defined as the difference in probability of the predicted class  $P(Y_{pred})$  to the real class  $P(Y_{true})$ .

$$a(\cdot) \leftarrow P(Y_{true}) - P(Y_{pred}) \tag{4}$$

#### C. The PIM Architecture

This work utilizes a PIM architecture designed to support compute-intensive applications including convolution neural networks (CNNs) and DNNs. This PIM architecture is depicted hierarchically in Figure 1, including (a) the arrangement of clusters within a DRAM bank, (b) the architecture of a cluster, and (c) the architecture of the LUT core.

1) Core Architecture: In order to provide functional programmability, a LUT-based design is adopted for the PIM core instead of a pre-defined logic circuit. The LUT-based PIM is capable of performing in-memory arithmetic operations such as addition, multiplication, substitution, and comparison operations with a significantly lower delay compared to bitwise computations. A collection of these operations can therefore be used to implement various ML algorithms.

Figure 1(c) shows a detailed view of the architecture of a single LUT core. The LUT cores inside the cluster are formed of an 8-bit 256:1 multiplexer, accompanied by eight 256-bit latch arrays. The pre-calculated outputs of any particular 8-bit operation are stored in the latches as eight 256-bit function words. These latches can read new function words from the bit lines of the DRAM subarrays. Each LUT can produce a 4-bit data output for two input data operands with a size of 4-bit width, as shown by A and B registers in Figure 1(c). These registers together drive the select pins of the multiplexers and make them 'look up' specific 8-bit data from the eight latches that represent the output of the operation.

2) Cluster Architecture: In order to perform operations necessary for CNN acceleration, such as convolution operations, the PIM cluster integrates all the operations done by the LUT core. Nine of the PIM cores are arranged as shown in Figure 1(b) and placed inside the memory unit to form a PIM cluster and perform in-memory computations. Inside the PIM cluster, the PIM core performs various logic and arithmetic operations associated with the CNN acceleration for malware detection. In order to perform a specific operation, such as multiplication and accumulation operations all the cores inside the cluster are connected by a router. The router also makes it possible to access data from any core at any moment throughout the implementation in order to perform the operations.

3) Router Architecture: All nine LUT cores in a cluster are connected via a router mechanism as shown in Figure 1(c), which enables direct and parallel communication between them. A router that connects the read/write ports on all components of the cluster in order to facilitate parallel communication among all the cores in the cluster. This enables the router to access any data at any point of implementation to perform operations required for CNN acceleration for malware detection.

#### D. Implementation on the PIM Architecture

Malware detection performs similar mathematical operations as the CNN classifier, which contains max pooling layers and convolution layers with activation layers. The PIM architecture can easily accommodate these operations by programming the LUT cores inside the cluster to perform these operations. With the help of the cores and the routing mechanism, the PIM architecture can perform the mathematical operations required by the CNN layers. Since the clusters in the PIM architecture are capable of performing the required mathematical operations for CNN, an array of these clusters can be utilized to implement different layers of the CNN model. The key advantage of using LUTs in a PIM architecture is that the LUT core in the PIM architecture can be re-programmed to perform an entirely different operation. As a result, the functional flexibility required for implementing malware detection using CNNs is provided.

# E. Data Format Optimization Using Precision Scaling

Precision scaling is a process of scaling the precision point of input data to the desired decimal point. Precision scaling helps lower the number of mac operations, thus, decreasing the throughput and memory consumption. In this paper, we attain this by using uniform quantization. The input images (malware and benign) are stored in the DRAM memory bank as binary bits. As shown in Figure 1, while retrieving the data uniform quantization is applied. The test samples used for inference are quantized from floating point 32-bit to integer types 16bit, 8-bit and 4-bit. This massively decreases the computations on top of the in-memory processing. The quantization process can be described through equation 5.

$$\mathbb{D}(r) = S \cdot (q - Z) \tag{5}$$

In equation 5, q is the quantized value, S and Z are quantization parameters. Z is the zero point buffer, the same type as the quantized q. It may be used to pad zeros for the input quantized data so that it can meet the requirement of real value r. For 4-bit quantization, q is quantized as a 4-bit integer (for N-bit quantization, q is quantized as an N-bit integer). The quantized value q is written into the dataset  $\mathbb{D}$  as a real number r. Each of the input images are quantized into either 16-bit, 8-bit or 4-bit integer types and written back into the dataset.

## V. EXPERIMENTAL RESULTS

#### A. Experimental Setup

The proposed methodology is implemented on an Intel core Nvidia GeForce GTX 1650 GPU with 16GB RAM. We have obtained malware applications from VirusTotal [53] with 12500 malware samples that encompass 5 malware classes: backdoor, rootkit, trojan, virus, and worm. We collected about 13700 benign application files, which are harmless to work with. These binary files are converted into grayscale images of size 32 x 32 and fed to an ML model to build a malware detection classifier. We use the malware and benign samples to train a model such as AlexNet, ResNet18, ResNet34, ResNet50, VGG-16, and MobileNetV2. We analyze the malware detection accuracy, energy efficiency, and throughput of these models. Further, the inference accuracy of these models on precision scaling schemes such as 16-bit, 8-bit and 4-bit are evaluated.

# B. Evaluation of Malware Detection Accuracy on Various Precision Schemes

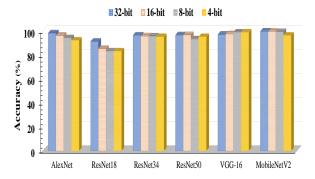

The integer precision schemes such as 16-bit, 8-bit and 4-bit are applied to data that is given as input to various ML algorithms. The effect of precision scaling on malware detection capability is observed in various algorithms. The base accuracy of models trained using 32-bit floating point data is compared to that of 16-bit, 8-bit and 4-bit data. As shown in Figure 2, the performance of various CNN models on different data precisions is compared. We can observe a considerable performance decay with the decrease in precision for models such as AlexNet and ResNet18. But other models such as ResNet34, ResNet50, VGG-16, and MobileNetV2 retain the accuracy despite the low precisions. We can observe a malware detection accuracy of about 98% in models VGG-16 and MobileNetV2 for an 8-bit precision scheme. And for 4-bit precision models ResNet34, VGG-16, and MobileNetV2 have an accuracy of about 95%. So even with precision scaling schemes, we can still retain effective malware detection capability.

Fig. 2. Performance Evaluation of AlexNet, ResNet18, ResNet34, ResNet50, VGG16 and MobileNetV2 on the PIM accelerator with precision scaling (a) 32-bit floating point, (b) 16-bit integer type, (c) 8-bit integer type and (d) 4-bit integer type

Table I presents the comparison of the proposed technique with the existing malware detection techniques. We compare the performance of the proposed technique in terms of accuracy, F1 score, and recall. All the models in table I focus on malware detection based on malware and benign features. Compared to the existing techniques the proposed PIM-based malware detection achieves high throughput without performance decay. It maintains a malware detection accuracy of 98%. It is also evident that the proposed technique achieves efficient malware detection accuracy even in low-precision settings.

|                                                         | TABLE I  |          |        |  |  |  |  |

|---------------------------------------------------------|----------|----------|--------|--|--|--|--|

| COMPARISON WITH EXISTING HPC-BASED DETECTION TECHNIQUES |          |          |        |  |  |  |  |

| Model                                                   | Accuracy | F1-score | Recall |  |  |  |  |

| Model             | Accuracy | F1-score | Recall |

|-------------------|----------|----------|--------|

|                   | (%)      |          |        |

| OneR [54]         | 0.81     | 0.81     | 0.82   |

| JRIP [54]         | 0.83     | 0.83     | 0.84   |

| PART [54]         | 0.81     | 0.815    | 0.831  |

| J48 [54]          | 0.82     | 0.82     | 0.82   |

| Adaptive-HMD [55] | 0.853    | 0.853    | 0.858  |

| SVM [56]          | 0.739    | 0.736    | 0.772  |

| RF [56]           | 0.835    | 0.834    | 0.822  |

| NN [56]           | 0.811    | 0.811    | 0.816  |

| SMO [57]          | 0.932    | 0.933    | 0.931  |

| Proposed          | 0.987    | 0.987    | 0.982  |

#### C. PIM core and cluster characteristics

The delay & power for the PIM core and cluster are obtained from Synopsys Design Compiler using 28nm standard cell libraries from TSMC and are presented in Table II. The delay of a single 8-bit MAC performed within a cluster involves computations inside the PIM cores as well as communication among the cores. The power consumption of the cluster is that of all the cores and the core-to-core communication. The power and delay for intra and inter-subarray data transfers are obtained from [58] and [59]. These metrics are used in the system-level performance evaluation of the PIM in the next subsections.

TABLE II

CHARACTERISTICS OF PROPOSED PIM COMPONENTS IN 28 NM NODE

| Component                      | Delay (ns) | Power        | Active Area |

|--------------------------------|------------|--------------|-------------|

|                                |            | (mW)         | $(\mu m^2)$ |

| Proposed PIM Core              | 0.8        | 2.7          | 4196.64     |

| Proposed PIM Cluster (MAC      | 6.4        | 8.2-11       | 37769.81    |

| Operation)                     |            |              |             |

| Intra-Subarray Communica-      | 63.0       | 0.028        | N/A         |

| tion [59]*                     |            | µJ/comm      |             |

| Inter-Subarray Communica-      | 148.5/     | 0.09/        | N/A         |

| tion [58] for subarrays 1/7/15 | 196.5/     | 0.12/ 0.17   |             |

| hops away*                     | 260.5      | $\mu$ J/comm |             |

\*Represented in 28nm technology node

### D. Performance Evaluation

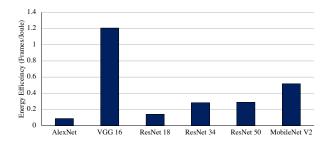

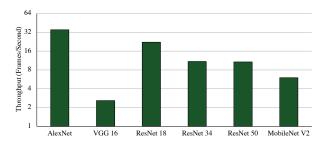

This section presents the comparative analysis of the algorithm implemented on PIM in terms of throughput (in Frames per second) and Energy Efficiency (Frames/Joules). For evaluation purposes, we have implemented AlexNet, ResNet 18, 34, 50, VGG16, and MobileNetV2 networks on the PIM accelerator. Figure 3 presents comparisons of the throughput (in Frames per second) and Figure 4 energy efficiency (in Frames per Joule) of inference on all these CNNs deployed on the PIM accelerator.

Fig. 3. Comparison of Energy efficiency (Frames/Joules) for AlexNet, ResNet18, ResNet34, ResNet50, VGG16, and MobileNetV2 on the PIM accelerator

From Figure 3 it can be observed that the proposed PIM model is capable of performing malware detection tasks with an impressive performance of low latency. For example, ResNet-50, the largest network consisting of 50 layers and thirty-eight billion computations, is processed within 10 mS.

A similar trend is observed for energy consumption, from Figure 4 it can be observed that the proposed PIM model is capable of performing malware detection tasks with high energy efficiency. This is because the PIM module supports 8bit precision mode in order to perform the operations required for CNN acceleration. These tasks can be performed by distributing the data across the cluster which contains nine cores connected by a router which inherently offers a higher degree of parallelization and performs all the operations in comparatively fewer steps.

Fig. 4. Comparison of Throughput (Frames/second) for AlexNet, ResNet18, ResNet34, ResNet50, VGG16, and MobileNetV2 on the PIM accelerator

# *E. Performance Comparison with State-of-the-Art Hardware Accelerators for CNN Implementation*

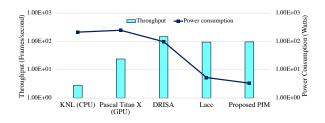

Performance is evaluated by comparing the proposed architecture with state-of-the-art hardware accelerator architectures in terms of power consumption (Watt) and throughput (Frames/second), as shown in Figure 5.

Fig. 5. Comparative performance analysis of PIM with respect to state-of-theart hardware accelerator architectures in terms of throughput (Frames/second) and power consumption (Watt)

As a proof of concept, we evaluate and implement AlexNet [60] on the proposed architecture with the 8-bit width precision. We envision a 256 PIM cluster arrangement in a DRAM chip as this configuration provides a fine balance between performance, power consumption, and on-chip area overhead. An input dimension of 224x224x3 has been considered for performance benchmarking with the other CNN accelerators and different operational modes of PIM. The PIM architectures under comparison in this section include DRAM-based bulk bit-wise processing devices DRISA [61], and LUT-based PIM implemented on the DRAM platforms such as LAcc [13]. On the other hand, the von Neumann devices under comparison are Intel Knights Landing (KNL), a state-of-the-art CPU [62], and Pascal Titan X, a state-of-the-art GPU.

It can be observed from Figure 5, that the PIM architectures in general outperform both the CPU and the GPU by a huge margin since all these PIMs can avoid the significant overhead and latency associated with off-chip communications, unlike the CPU and the GPU. In fact, the most computation-intensive 8-bit fixed-point operation mode PIM ideally provides  $4.02\times$ ,  $45\times$  higher throughput compared to Pascal Titan X GPU and Knights Landing Processor while being  $74.62\times$ ,  $64.13\times$  more energy-efficient. On the other hand, a relatively higher throughput is observed for DRISA [61] due to its ability to parallelize operations across multiple banks, albeit at significantly low power efficiency. The benefits of adopting LUTs in order to utilize pre-calculated results instead of performing in-memory logic operations are convincingly demonstrated by LAcc [13] which achieves impressive inference performance at quite a low power consumption. From Figure 5, it is also observed that the proposed PIM outperforms DRISA and LAcc in both the throughput by  $0.065 \times$ ,  $1.09 \times$  as well as power efficiency by  $29.25 \times$ ,  $1.5 \times$  respectively for AlexNet inference.

# VI. CONCLUSION

In this paper, we proposed a PIM-based ML modeling technique for malware detection. The proposed approach not only achieves low latency for implementing malware detection task but also provides high energy efficiency. Which in turn makes the real-time malware detection task in embedded devices more approachable. The performance of the proposed PIM is evaluated by comparing it with state-of-the-art CPU, GPU, and other PIM architectures. The experimental results indicate that the proposed PIM is  $74.62\times$ ,  $64.13\times$  more energy-efficient and has  $4.02\times$ ,  $45\times$  higher throughput compared to the GPU and CPU respectively. It is also observed that the PIM is  $1.5 \times$  energy efficient and has  $1.09 \times$  higher throughput than other LUT-based PIM architecture. Multiple CNN models were trained using data that was precision scaled into 16-bit, 8-bit and 4-bit samples, to further aid the energy efficiency and throughput. The performance of these models is compared with state-of-the-art malware detectors. And from experimental results, it is evident that the proposed technique is efficient for malware detection as it doesn't experience any performance decay.

#### REFERENCES

- T. Adiono, "Challenges and opportunities in designing internet of things," 2014 The 1st International Conference on Information Technology, Computer, and Electrical Engineering, 2014.

- [2] O. Abbas and et al., "Big data issues and challenges," 2016.

- J. Johnson, "Number of malware attacks per year 2020," Aug 2021. [Online]. Available: https://www.statista.com/statistics/873097/ malware-attacks-per-year-worldwide/

- [4] "Malware statistics trends report: Av-test," 2021. [Online]. Available: https://www.av-test.org/en/statistics/malware/

- [5] M. S. Jalali and et al., "The internet of things promises new benefits and risks: A systematic analysis of adoption dynamics of iot products," *IEEE Security Privacy*, 2019.

- [6] A. Damodaran et al., "A comparison of static, dynamic, and hybrid analysis for malware detection," Journal of Computer Virology and Hacking Techniques, 2015.

- [7] K. Kancherla and et.al, "Image visualization based malware detection," in *Computational Intelligence in Cyber Security (CICS)*, 2013.

- [8] S. Shukla and et.al, "On-device malware detection using performanceaware and robust collaborative learning," in *Design Automation Conference*, 2021.

- [9] L. Nataraj and et al., "Malware images: Visualization and automatic classification," in *Int. Symposium on Visualization for Cyber Security*, 2011.

- [10] D. Gibert and et.al, "Using convolutional neural networks for classification of malware represented as images," *Journal of Computer Virology* and Hacking Techniques, 2019.

- [11] V. S. et al., "Ambit: In-memory accelerator for bulk bitwise operations using commodity dram technology," *IEEE/ACM International Sympo*sium on Microarchitecture (MICRO), 2017.

- [12] A. D. P. et al., "An mram-based deep in-memory architecture for deep neural networks," in *IEEE International Symposium on Circuits and Systems*, 2019.

- [13] Q. Deng and et al., "Lacc: Exploiting lookup table-based fast and accurate vector multiplication in DRAM-based CNN accelerator," in ACM/IEEE Design Automation Conf. (DAC), 2019.

- [14] P. R. Sutradhar, M. Connolly, S. Bavikadi *et al.*, "pPIM: A programmable processor-in-memory architecture with precision-scaling for deep learning," *IEEE Computer Architecture Letters*, vol. 19, no. 2, pp. 118–121, 2020.

- [15] A. Moser and et.al, "Limits of static analysis for malware detection," in Annual Computer Security Applications Conference (ACSAC 2007), 2007.

- [16] A. Makandar and A. Patrot, "Malware class recognition using image processing techniques," in *Int. Conf. on Data Management, Analytics* and Innovation (ICDMAI), 2017.

- [17] A. Dhavlle, S. Shukla, S. Rafatirad *et al.*, "Hmd-hardener: Adversarially robust and efficient hardware-assisted runtime malware detection," in 2021 Design, Automation and Test in Europe Conference and Exhibition (DATE), 2021.

- [18] S. Shukla, G. Kolhe, S. M. P. D et al., "Microarchitectural events and image processing-based hybrid approach for robust malware detection: Work-in-progress," in *Proceedings of the International Conference on Compliers, Architectures and Synthesis for Embedded Systems Companion*, ser. CASES '19. New York, NY, USA: Association for Computing Machinery, 2019.

- [19] S. Shukla, P. D. Sai Manoj, G. Kolhe et al., "On-device malware detection using performance-aware and robust collaborative learning," in 2021 58th ACM/IEEE Design Automation Conference (DAC), 2021.

- [20] S. Shukla, S. Rafatirad, H. Homayoun *et al.*, "Federated learning with heterogeneous models for on-device malware detection in iot networks," in 2023 Design, Automation and Test in Europe Conference and Exhibition (DATE), 2023.

- [21] A. Dhavlle and S. Shukla, "A novel malware detection mechanism based on features extracted from converted malware binary images," 2021.

- [22] S. Shukla, G. Kolhe, H. Homayoun *et al.*, "Rafel robust and data-aware federated learning-inspired malware detection in internet-of-things (iot) networks," in *Proceedings of the Great Lakes Symposium on VLSI 2022*, ser. GLSVLSI '22. New York, NY, USA: Association for Computing Machinery, 2022.

- [23] S. Shukla, A. Dhavlle, S. M. P. D et al., "Iron-dome: Securing iot networked systems at runtime by network and device characteristics to confine malware epidemics," in 2022 IEEE 40th International Conference on Computer Design (ICCD), 2022.

- [24] S. Shukla, G. Kolhe, S. M. PD et al., "Rnn-based classifier to detect stealthy malware using localized features and complex symbolic sequence," in 2019 18th IEEE International Conference On Machine Learning And Applications (ICMLA), 2019.

- [25] S. Shukla, G. Kolhe, S. M. P D et al., "Stealthy malware detection using rnn-based automated localized feature extraction and classifier," in 2019 IEEE 31st International Conference on Tools with Artificial Intelligence (ICTAI), 2019.

- [26] S. Shukla and P. D. Sai Manoj, "Bring it on: Kinetic energy harvesting to spark machine learning computations in iots," in 2024 International Symposium on Quality Electronic Design (ISQED), 2024.

- [27] S. Barve, S. Shukla, S. M. P. Dinakarrao et al., "Adversarial attack mitigation approaches using rram-neuromorphic architectures," in Proceedings of the 2021 on Great Lakes Symposium on VLSI, ser. GLSVLSI '21. New York, NY, USA: Association for Computing Machinery, 2021.

- [28] S. Shukla, G. Kohle, S. M. P. Dinakarrao et al., "A robust malware detection framework using computer vision and deep learning," in *Athens Institute for Education and Research (ATINER)*, 2020.

- [29] S. Kasarapu, R. Hassan, S. Rafatirad *et al.*, "Demography-aware covid-19 confinement with game theory," in 2021 IEEE 3rd International Conference on Artificial Intelligence Circuits and Systems (AICAS). IEEE, 2021, pp. 1–4.

- [30] S. Kasarapu, R. Hassan, H. Homayoun *et al.*, "Scalable and demographyagnostic confinement strategies for covid-19 pandemic with game theory and graph algorithms," *COVID*, vol. 2, no. 6, pp. 767–792, 2022.

- [31] S. Kasarapu, S. Shukla, and S. M. P. Dinakarrao, "Resource- and workload-aware malware detection through distributed computing in iot

networks," in 2024 29th Asia and South Pacific Design Automation Conference (ASP-DAC), 2024, pp. 368–373.

- [32] S. Kasarapu, S. Shukla, R. Hassan *et al.*, "Cad-fsl: Code-aware data generation based few-shot learning for efficient malware detection," 2022.

- [33] S. Kasarapu, S. Shukla, and S. M. Pudukotai Dinakarrao, "Resource- and workload-aware model parallelism-inspired novel malware detection for iot devices," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 42, no. 12, pp. 4618–4628, 2023.

- [34] S. Shukla, S. Kasarapu, R. Hasan *et al.*, "Ubol: User-behavior-aware one-shot learning for safe autonomous driving," in 2022 Fifth International Conference on Connected and Autonomous Driving (MetroCAD), 2022, pp. 7–12.

- [35] S. Kasarapu, S. Bavikadi, and S. M. P. Dinakarrao, "Processing-inmemory architecture with precision-scaling for malware detection," in 2024 37th International Conference on VLSI Design and 2024 23rd International Conference on Embedded Systems (VLSID), 2024, pp. 529–534.

- [36] R. Saravanan, S. Bavikadi, S. Rai *et al.*, "Reconfigurable fet approximate computing-based accelerator for deep learning applications," in 2023 *IEEE International Symposium on Circuits and Systems (ISCAS)*, 2023, pp. 1–5.

- [37] G. P. C. R. S. Bharani Surya, S and N. Mohankumar, "Evolving reversible fault-tolerant adder architectures and their power estimation," in *International Conference on Communication, Computing and Electronics Systems: Proceedings of ICCCES 2019*, 2020.

- [38] M. N. Raghul, S, "Microcontroller based ann for pick and place robot coordinate monitoring system," in *Proceedings of the 1st International Conference on Data Science, Machine Learning and Applications* (ICDSMLA), 2020.

- [39] R. S, Y. Akhileswar, and M. N, "N configuration trng based scrambler protocol for secured file transfer," in *Proceedings of the International Conference on IoT Based Control Networks and Intelligent Systems* (ICICNIS), 2021.

- [40] Y. Akhileswar, S. Raghul, C. Meghana et al., Hardware-Assisted QR Code Generation Using Fault-Tolerant TRNG, 2020.

- [41] A. Krishna, L. Anusree Raj, G. Priyadarsini et al., "A low power binary square rooter using reversible logic," in 2019 5th International Conference on Advanced Computing and Communication Systems (ICACCS), 2019, pp. 619–623.

- [42] P. R. Sutradhar, S. Bavikadi, M. Connolly *et al.*, "Look-up-table based processing-in-memoryarchitecture with programmable precisionscalingfor deep learning applications," *IEEE TPDS*, 2021.

- [43] P. R. Sutradhar, S. Bavikadi, M. Connolly *et al.*, "Look-up-table based processing-in-memory architecture with programmable precision-scaling for deep learning applications," *IEEE Transactions on Parallel and Distributed Systems*, vol. 33, no. 2, pp. 263–275, 2022.

- [44] S. Bavikadi, A. Dhavlle, A. Ganguly *et al.*, "A survey on machine learning accelerators and evolutionary hardware platforms," *IEEE Design and Test*, vol. 39, no. 3, pp. 91–116, 2022.

- [45] S. Bavikadi, P. R. Sutradhar, A. Ganguly et al., "upim: Performanceaware online learning capable processing-in-memory," in 2021 IEEE 3rd International Conference on Artificial Intelligence Circuits and Systems (AICAS), 2021, pp. 1–4.

- [46] S. Bavikadi, P. R. Sutradhar, A. Ganguly *et al.*, "Heterogeneous multifunctional look-up-table-based processing-in-memory architecture for deep learning acceleration," in 2023 24th International Symposium on Quality Electronic Design (ISQED), 2023, pp. 1–8.

- [47] S. Bavikadi, P. R. Sutradhar, A. Ganguly et al., "upim: Performanceaware online learning capable processing-in-memory," in 2021 IEEE 3rd International Conference on Artificial Intelligence Circuits and Systems (AICAS), 2021, pp. 1–4.

- [48] P. R. Sutradhar, K. Basu, S. M. P. Dinakarrao et al., "An ultra-efficient look-up table based programmable processing in memory architecture for data encryption," in 2021 IEEE 39th International Conference on Computer Design (ICCD), 2021, pp. 252–259.

- [49] Q. D. et al., "Dracc: a dram based accelerator for accurate cnn inference," in ACM/ESDA/IEEE Design Automation Conference (DAC), 2018.

- [50] P. C. et al., "Prime: A novel processing-in-memory architecture for neural network computation in reram-based main memory," in ACM/IEEE International Symposium on Computer Architecture (ISCA), 2016.

- [51] S. A. et al., "Imce: Energy-efficient bit-wise in-memory convolution engine for deep neural network," in Asia and South Pacific Design Automation Conference (ASP-DAC), 2018.

- [52] B. Bashari Rad and et.al, "Camouflage in malware: From encryption to metamorphism," *IJCSNS*, 2012.

- [53] "Virustotal package," 2021. [Online]. Available: https://www.rdocumentation.org/packages/virustotal/versions/0.2.1

- [54] N. Patel, A. Sasan, and H. Homayoun, "Analyzing hardware based malware detectors," in ACM/EDAC/IEEE Design Automation Conference (DAC), 2017, pp. 1–6.

- [55] Y. Gao, H. M. Makrani, M. Aliasgari *et al.*, "Adaptive-hmd: Accurate and cost-efficient machine learning-driven malware detection using microarchitectural events," in *IEEE International Symposium on On-Line Testing and Robust System Design (IOLTS)*, 2021.

- [56] A. P. Kuruvila, S. Kundu, and K. Basu, "Analyzing the efficiency of machine learning classifiers in hardware-based malware detectors," in *IEEE Computer Society Annual Symposium on VLSI (ISVLSI)*, 2020.

- [57] H. Sayadi and et.al, "Customized machine learning-based hardwareassisted malware detection in embedded devices," in *IEEE International Conference On Trust, Security And Privacy In Computing And Communications*, 2018.

- [58] K. K. Chang, P. J. Nair, D. Lee *et al.*, "Low-cost inter-linked subarrays (lisa): Enabling fast inter-subarray data movement in dram," in 2016 *IEEE International Symposium on High Performance Computer Architecture (HPCA)*, March 2016, pp. 568–580.

- [59] V. Seshadri, Y. Kim, C. Fallin *et al.*, "Rowclone: Fast and energyefficient in-dram bulk data copy and initialization," in 2013 46th Annual IEEE/ACM International Symposium on Microarchitecture (MICRO), Dec 2013, pp. 185–197.

- [60] M. Z. Alom, T. M. Taha, C. Yakopcic *et al.*, "The history began from alexnet: A comprehensive survey on deep learning approaches," *arXiv*, 2018.

- [61] S. L. et al., "Drisa: A dram-based reconfigurable in-situ accelerator," in IEEE/ACM International Symposium on Microarchitecture, 2017.

- [62] A. Sodani, "Knights landing (knl): 2nd generation intel® xeon phi processor," in 2015 IEEE Hot Chips 27 Symposium (HCS), Aug 2015, pp. 1–24.