# R5Detect: Detecting Control-Flow Attacks from Standard RISC-V Enclaves

Davide Bove and Lukas Panzer

Friedrich-Alexander-Universität Erlangen-Nürnberg, Germany {davide.bove,lukas.panzer}@fau.de

Abstract. Embedded and Internet-of-Things (IoT) devices are ubiquitous today, and the uprising of several botnets based on them (e.g., Mirai, Ripple20) raises issues about the security of such devices. Especially lowpower devices often lack support for modern system security measures, such as stack integrity, Non-eXecutable bits or strong cryptography. In this work, we present R5Detect, a security monitoring software that detects and prevents control-flow attacks on unmodified RISC-V standard architectures. With a novel combination of different protection techniques, it can run on embedded and low-power IoT devices, which may lack proper security features. R5Detect implements a memory-protected shadow stack to prevent runtime modifications, as well as a heuristics detection based on Hardware Performance Counters to detect controlflow integrity violations. Our results prove that regular software can be protected against different degrees of control-flow manipulations with an average performance overhead of below 5 %. We implement and evaluate R5Detect on standard low-power RISC-V devices and show that such security features can be effectively used with minimal hardware support.

Keywords:  $cfi \cdot risc-v \cdot monitoring \cdot shadow stack \cdot performance counter$

## 1 Introduction

Today there are many internet-connected devices on the market that, once deployed, are difficult to manage remotely by a vendor. Some of these are so-called Internet-of-Things (IoT) consumer devices, such as smart fridges, but there are also embedded systems that are used in critical infrastructure deployments. The more devices there are, the more interesting they become for potential attackers, which may discover a vulnerability in one device and compromise millions of targets, as seen in IoT-based botnets like Mirai [4] or Mozi [33].

One problem of IoT and embedded devices is that the majority of devices on the market are mostly designed to be low-power and cheap customer devices. Therefore, low-end hardware is often used or critical security features that may require more processing power, such as strong encryption, are not available [44]. An increasing number of IoT devices is being deployed in consumer homes, and a vulnerable device may compromise the security of several households [3]. It is therefore desirable to have both affordable devices and strong security measures against attacks. Both complex software like a Linux kernel and more lightweight Operating System (OS) kernels like FreeRTOS are prone to vulnerabilities and attacks [15]. In this work, we are looking at detecting firmware and software manipulation attacks at runtime to prevent devices from going rogue.

There are several ways to detect runtime manipulations of the firmware or software on a device. Mostly we look at control flow manipulations, where an attacker may change the order of existing instructions or introduce new ones using vulnerabilities in the deployed software. On most architectures, there are so-called Hardware Performance Counters (HPCs) that count specific events occurring at runtime. This information can be used to detect potential modifications [36]. During execution, the performance of a software is measured and continuously compared to the expected output. Another method is to observe the execution of the software and check for integrity violations of the control flow. We are the first to explore both methods and to combine them in a single monitoring system that will detect Control Flow Integrity (CFI) violations and unexpected software behavior on low-power IoT and embedded devices based on the RISC-V architecture.

Therefore, we created R5Detect, a security monitoring software for low-power devices that combines the following contributions:

- We implement CFI security checks with a Shadow Stack implementation using standard RISC-V features.

- We implement a monitoring heuristics based on Hardware Performance Counters.

- We improve the overall security using built-in defenses to protect R5Detect against strong attackers.

- We test and successfully deploy R5Detect on an FPGA and a low-power RISC-V board. We also quantify both the effectiveness and the performance of the different detection methods.

We provide some additional background information for the reader in section 2. In section 3 we describe the security constraints of our approaches. We present the two separate security monitoring approaches used in R5Detect, namely our implementation of a CFI monitor in section 4 and the HPC monitoring in section 5. Regarding existing related work (see section 6), we discuss our results in section 7 and summarize our results in section 8.

## 2 Background

In order to achieve a robust monitoring on a mostly untrusted device, we require hardware support for specific security features. For our implementation of R5Detect, memory protection features and a separation of hardware resources in different privilege levels are required. This is found on several platforms and processors, but both features are also natively covered by the RISC-V standard architecture. RISC-V is a license-free and open-standard instruction set architecture. Therefore, we can easily implement our monitoring setup with unmodified commodity hardware boards. We implement R5Detect on top of MultiZone, a Trusted Execution Environment (TEE) framework for RISC-V, to guarantee that the monitoring is safe from attackers. MultiZone uses standard features available on most RISC-V devices to protect software from manipulations even in the presence of a compromised OS kernel.

### 2.1 RISC-V Security

In this work, we use several standardized features of the RISC-V architecture. Since most low-power devices on the market only have limited CPU features, most devices cannot run a full Linux kernel and often rely on more adapted Real-Time Operating System (RTOS). R5Detect targets such devices and only requires two different privilege levels, which is recommended in the RISC-V Instruction Set Architecture (ISA) for "Secure embedded systems" [39]. Our solution also relies on memory protection, as described below.

**Privilege Levels** Comparable to "Rings" in x86 and "Exception Levels" in ARM, the RISC-V Privileged Architecture defines different privilege levels in which software can run. On a platform level, we require at least two levels to achieve some secure separation. The mandatory Machine Mode (M-Mode) has the highest privileges and is always present on compliant RISC-V devices. In our solution, the most important software is called "Secure Monitor" (SM) and runs in M-Mode, such that any compromise of the OS might not directly affect the security of the whole system. The second mode is the User Mode (U-Mode), which is intended for running the operating system with its user apps. In the specification there are even more modes, such as the Hypervisor Mode (H-Mode) or the Supervisor Mode (S-Mode) which are intended for running more complex systems using virtualized environments or a Linux kernel. Since our focus is on low-power and embedded devices, we do not require these modes to be implemented.

**Physical Memory Protection** In order to manage memory access from different privilege modes, RISC-V includes Physical Memory Protection (PMP), a hardware-based security feature. PMP regulates the access to specific memory regions from lower-privileged S-Mode and U-Mode. With special registers, M-Mode software can set rules for memory that can be any combination of read, write and execute permissions. There is also the *Lock Bit*, which allows locking such a rule until the next device reboot. The Lock Bit enforces rules for all modes, and locked PMP entries cannot be "unlocked" during runtime (not even in M-Mode) until the device is restarted.

### 2.2 Trusted Execution Environment

A Trusted Execution Environment is a processor feature that offers some kind of isolation inside the hardware for processing data. The goal is to have a secure execution of specific applications even in the presence of a compromised OS. Such applications, called trusted apps or trustlets, are responsible for processing security-critical operations, such as encryption or authentication. Often they also provide services that handle sensitive user data, which may need extra protection from strong attackers. These isolated environments are often called *enclaves*, while this work will reference them as **zones**. Zones run in U-Mode and have only access to other zones by shared memory spaces, which are defined and assigned by the Secure Monitor.

### 2.3 OpenMZ

**R5Detect** is built on top of OpenMZ, an open-source implementation of Multi-Zone Security [16]. MultiZone is a TEE framework for RISC-V devices, which allows different applications to run in isolated environments. Our solution can monitor such an environment as a privileged entity, while still being protected from attacks itself.

OpenMZ splits the system into different *zones*, which can contain up to 8 memory regions. Memory isolation between zones is implemented using PMP. OpenMZ is used as a Secure Monitor, which is the software running in M-Mode and which manages the context switches between zones. The framework implements the MultiZone Application Programming Interface and has a code base of 758 Lines of Code. The compiled binary size is approximately 4 KiB, which makes it a suitable TEE for embedded and resource-constrained systems.

## 3 Threat Model

"IoT" describes a vast amount of different devices, so without a precise definition, it might be unclear why some decisions were made. There is no consensus how to define low-power or ultra-low-power devices, but when talking about IoT devices we mean systems that are "equipped with sensors, actuators, computers, and network connectivity" [44]. Most devices we target have a flash memory chip and limited system resources, such that they cannot run fully-featured operating systems. Our two test boards, for example, are not suited to run a Linux Kernel, which is why our test applications are bare-metal apps or rely on a small-scale OS like FreeRTOS, a Real-Time Operating System. In our experience, a lot of these devices do also not support many security features, such as Secure Boot or Address Space Layout Randomization. Moreover, we do not require a Memory Management Unit (MMU), which we found is often not available. Most RTOS for these devices operate on the memory model of "logical address space equals physical address space" and do not support address space translations. Especially with RISC-V, most low-power devices support only one and a maximum of two CPU privilege levels (see more in section 2). Embedded devices share similar limitations and are often a central part of IoT systems.

Before describing the technical details of our defenses, we define our general threat model. On our target devices, we run R5Detect in the privileged Machine

Mode, while the monitoring code and other applications (bare-metal, FreeRTOS app) run in a zone in User Mode (U-Mode). Since the monitoring is running in the unprivileged U-Mode, even a compromise of it would prevent further escalation to the Secure Monitor.

We assume an unprivileged U-Mode attacker, which means that the Secure Monitor is uncompromised and the attacker may exploit one or all of the user zones, except the monitoring zone. The attacker may modify stack contents of each individual zone, use memory-based vulnerabilities to manipulate the control flow of apps, and ultimately take over a zone. The attacker may also introduce own code, eventually circumventing the detection methods of R5Detect.

Our work assumes that the integrity of the Secure Monitor is safe and there are Secure Boot mechanisms, such that manipulations of the Secure Monitor or the firmware are detected and prevented. The monitoring zone does not leak sensitive information, such as stack contents or register values. If the monitoring zone is compromised, all user-mode apps can be considered compromised, but not the Secure Monitor.

Denial-of-Service (DoS) attacks are considered in the design. Attackers may try to stop or tamper with the monitoring, or completely shut down the device. While unprivileged apps may perform actions that damage the board or manipulate computing states, attackers cannot block or starve out the monitoring, as the Secure Monitor includes an own scheduler, which prevents zones from blocking the execution of other zones. A DoS attack may only be possible if the trusted monitoring zone is directly compromised (out of scope for this work), in which case the detection results become unreliable.

Furthermore, we focus on software-based attacks, meaning that hardware attacks are out of scope. This includes fault-injection [22, 42] and side-channel attacks [2, 21], which in general are too powerful to protect against, especially on low-power devices as described in this chapter. Side-channels may reveal the presence of the monitoring, but not manipulate its functioning. While *all* attacks need to be considered for a secure platform, we consider the overall impact of a physical attacker on IoT devices to be quite low compared to large-scale software-based vulnerabilities and attacks.

## 4 Control-Flow-Integrity Using a Shadow Stack

Many software-based attacks exploit the control flow of vulnerable apps to change or delay the execution of specific functions. Therefore, these attacks are called control-flow integrity attacks. Most modern systems already implement protections against CFI attacks, such as non-executable data segments, stack canaries [8] or runtime randomization [43].

Unfortunately, some of these protections can be circumvented, for example by reusing code segments in Return-Oriented Programming (ROP) attacks [6,28]. Randomized code layouts and stack canaries can also be predicted and circumvented using side-channels [1,27,30]. CFI defenses may offer a robust protection specifically against ROP attacks and buffer overflow attacks. Furthermore, CFI

protections can be implemented in software, or one can extend and customize the hardware to support them [10]. Since we try to make such protections available for many devices, we implemented a software-based solution which targets the standard RISC-V Instruction Set Architecture (ISA).

## 4.1 Setup

Before designing our protection, we consider the threat model that we want to protect against (see section 3). We assume an attacker that may control main memory data contents of the executing user application. This may be done using vulnerabilities in the program, stack manipulation techniques etc. The goal of the attacker is to redirect the execution, such that instructions controlled by the attacker may be executed instead of the original instructions. This threat model has only three limitations that need to be guaranteed for our solution:

- 1. The .text segment of the program, the actual code executed on the system, is not writable.

- 2. Data segments of the program are marked as non-executable.

- 3. The attacker may not directly manipulate registers.

From experience with actual devices, most of the above points are already covered by the processor. Therefore, we do not consider these to be too limiting for real-world use cases. (1) prevents an attacker from manipulating or circumventing our security checks. As we rely on the integrity of our binary instrumentation, this is a crucial requirement. Since shared libraries on embedded devices are often statically linked into a binary, the code segment does not need to be writable. (2) prevents an attacker from transforming data into instructions such that they can be executed. An attacker may manipulate any data on the stack, but not change the execution flags. Since our protection uses some registers to do the security checks, (3) must be guaranteed to some extent for our solution to work. This limitation may also be restricted to certain registers, depending on the number of available registers on the system.

### 4.2 Implementation

In general, software running on a machine uses branching and jumps to redirect the execution of the code to different functions. There are direct jumps, that specify the next address to execute, and there are *indirect* jumps, that specify a location where the target address is stored (e.g., a register). A problem with indirect jumps is that they can target any executable address, as register contents may be changed during execution.

A similar challenge exists with return instructions. RISC-V encodes a ret instruction as an indirect jump jalr x0, ra, 0. In this instruction, the return address (e.g., the caller function) saved in register ra may be saved on the stack, where an attack might manipulate it. This manipulation of return addresses is the basis for ROP attacks. Furthermore, while return instructions on other architectures target one fixed address (the next instruction of the caller function),

the indirect jump on RISC-V may lead to multiple targets, as register contents may be changed or manipulated. Therefore, we cannot check the validity of a return "jump" before it is executed.

So, our goal here is to prevent such arbitrary jumps to counter CFI attacks. The implementation of the CFI monitoring requires instrumentation of the program's binary. We present two approaches to do security checks for the different cases described above.

**Indirect jumps** RISC-V has two instructions for indirect jumps: jalr (jump and link register) and jr (jump register). In order to provide a protection, our monitor needs to check if the target addresses are in an allowed set of addresses. For this, we use assembly **labels** that are injected into a binary after compilation (binary rewriting) and define which locations an indirect jump may target inside a program, derived from the call graph of the application. At runtime, we check if the target has the correct label (*forward check*) before executing a jump. If the label does not match, the jump is not executed.

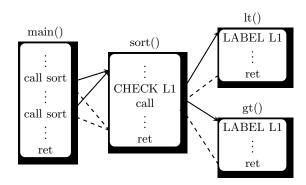

Fig. 1. Example program with indirect jumps and forward checks using labels. The sort function has two valid sub-functions (lt and gt), which are determined and annotated at compile time.

An example of this is found in Figure 1. The target address of the sort function is passed by parameter, but the only valid targets are the functions lt() and gt(). The target addresses are labeled, and these labels are checked before the jump in the sort function.

**Return instructions** As return addresses are saved on the stack, which may be manipulated by overflow and stack corruption attacks, we need to move them out of reach of a program's execution. Our solution implements a **Shadow Stack**, a data structure used to store all the return addresses. For this, every instruction that saves a return address on the stack is replaced by a call to the Shadow Stack. The Shadow Stack is managed by the Secure Monitor and located in the isolated monitoring *zone*. This zone may contain more than one Shadow Stack: one for every zone or multiple ones for a zone. Whenever a program pushes or pulls from the stack, an environment call (ecall) instruction is executed that moves the execution to the Secure Monitor. The Secure Monitor handles the request and loads or saves the previously saved stack address into the **ra** register. Moreover, checks are included to prevent stack overflows and underflows. This does introduce a minor performance overhead (see next section), but does not interfere with the correct execution of applications.

### 4.3 Evaluation

In order to test the effectiveness of our approach, we tested R5Detect on two hardware devices. We used the HiFivel Rev B with the native RISC-V chip FE310 with a clock speed of 320 MHz. As an alternative with more RAM, we used the Artix-7 35T FPGA with the Hex Five X300 RV32ACIMU bit stream and a clock speed of 65 MHz.

We evaluate the security of our approach by checking our implementation against the security guarantees and assumptions of our threat model (see subsection 4.1). In addition, we used generic buffer overflow attacks to simulate an attack and evaluate how R5Detect may detect such attacks. Furthermore, we run benchmarks to evaluate the impact on the system as well as the general performance of our approach.

**Security** As shown in related work, correctly implementing the Shadow Stack should yield no potential vulnerabilities for the chosen threat model [1]. The implementation checks all indirect jumps, and these checks can not be circumvented as long as the Secure Monitor and the Monitoring Zone are safe. Attacks that follow a regular "legal" control flow may still go undetected, so our approach does not necessarily detect other types of vulnerabilities. The security of our CFI monitoring is based on three pillars:

- 1. **Memory protection**: This is achieved using PMP. Executable code is made read-only, and the data segments are non-executable, so there is no possibility for an attacker to inject new code.

- 2. Labels: Since our approach annotates compiled software binaries, the label IDs in the program must be unique. This property is statically checked by the Secure Monitor before code execution, such that an attacker might not introduce own labels during runtime.

- 3. Jump checking: With our forward and backward jump checks, we make sure that jump instructions may only occur for the defined "legal" paths. If the attacker succeeds to inject a label into the writable memory space, the jump will succeed as it is considered legal to the Secure Monitor. In this case, (1) will still ensure that code in writable segments may not be executed. For the Shadow Stack, an application never has direct access to it, as only the

Secure Monitor may read or write to it. Therefore, stack vulnerabilities do not affect the security of the system.

For our security testing, we used an exemplary vulnerable binary that, using **memcpy**, allows stack buffer overflows. We implemented a total of three proof-of-concept attacks that target this vulnerable binary.

Our first attack tries to redirect the execution of the binary by overwriting the return address on the stack. Such an attack is easily detected by R5Detect, but it may also be prevented using a shadow stack implementation managed by the application itself, as offered by some compilers (e.g., Clang's ShadowCallStack<sup>1</sup>).

The second attack assumes an attacker that knows about the shadow stack, its position in memory and the stack pointer. In a real-world scenario, the presence of our solution may be discovered, either by trial-and-error, luck or through side-channel information leaks. In this scenario, the attacker tries to overwrite a pointer address and a local variable to manipulate a value on the shadow stack. This attack would be successful if the shadow stack would be managed by the application (e.g., using the above *ShadowCallStack*). Since PMP protects our shadow stack implementation from any access outside the app's zone, the system throws a "Load access fault" exception and prevents the manipulation.

The third attack overwrites the address of an indirect jump. We assume the vulnerable binary has the following call graph, with func1 and func2 as functions that call other functions (labeled TARGET\*) based on a conditional parameter:

The attack replaces the jump target on the stack of func1 with the address of TARGET3 of the program.

#### func1 $\rightarrow$ TARGET3

While TARGET3 is a "legal" label, the control flow above does not exist in the call graph. Therefore, it is an illegal control flow and R5Detect prevents the jump. On the other hand, replacing TARGET1 with TARGET2 on the stack for func1 may not be detected, as it is a legal path. If an attacker injects a legal (e.g., a duplicate) label in the data segment of the memory and manipulates the stack accordingly, PMP still prevents the execution, as all data segments are marked as non-executable.

**Performance** In order to measure the performance of our approach and the overhead caused, we run several benchmarks from the BEEBS suite [25]. The suite is designed to measure the energy consumption of embedded devices, which is not relevant for our target devices. But it also combines a decent range of different benchmarks focused on specific processor features, such as branching, memory access and more, which makes it suitable for our purposes. It is one

<sup>&</sup>lt;sup>1</sup> https://clang.llvm.org/docs/ShadowCallStack.html

of very few frameworks that can be easily ported and compiled to the RISC-V architecture, which was a major factor for choosing it. In addition, there is related work using BEEBS, so we can compare our results more easily.

We evaluate the runtime overhead by running the benchmarks with and without the CFI instrumentation. The benchmarks run in a single zone with default settings and 128 iterations. We compiled the benchmarks with gcc and optimization level O3. For timing the benchmarks, we use the real-time clock mtime and the internal BEEBS functions start\_trigger and stop\_trigger.

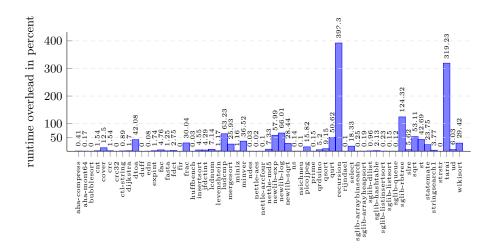

The results of our measurements can be seen in Figure 2. Our binary label checking approach combined with the Shadow Stack causes a runtime overhead of < 5 % for over 50 % of the benchmarks. Individual benchmarks with many indirect jumps, such as mergesort, as well as recursive functions with many calls to small methods, such as recursion and tarai, have a significant overhead to their runtime. These results are expected, as software with many function calls causes more jump checks. On the other hand, recursion and excessive function calls are mostly avoided in embedded systems, so not many real-world applications achieve such high runtime overhead [34]. As a solution, the label checking can be disabled for single functions or after a certain depth of sub-functions is reached.

Fig. 2. Run-time overhead of different BEEBS benchmarks for the Shadow Stack implementation compared to unmodified benchmarks

Since labels are injected into the binary files, the code segments increased with the number of functions. Overall, the binary size increases by 7.21 % on average with a median of 4.32 %. Again, the benchmarks with more functions tend to get bigger because of the instrumentation method. Moreover, being optimized for embedded systems and with compiler optimizations enabled, most

benchmarks are minimal binaries (5-50 KB depending on benchmark and flags), such that even few bytes lead to a high percentage increase.

The results indicate that the security goals can be achieved with our CFI method with relatively low performance overhead. We discuss the limitations of this approach in section 7, while the next section will present our method for anomaly detection.

## 5 Hardware Performance Counters to Monitor Suspicious System Activity

Since the above CFI defense has some drawbacks (see section 7), we implemented a separate detection method based on Hardware Performance Counters. HPCs are special registers that allow to count specific internal processor events. There are plenty of events that can be tracked, but the counters are limited, such that not all events can be monitored simultaneously. These counters may also be used for integrity checks of programs [20] or for anomaly detection [13].

Observable events depend on the actual hardware implementation and may include:

- cache misses,

- branches and jumps,

- arithmetic operations

A monitoring software may use these and other events to detect unexpected system behavior [20]. The RISC-V ISA defines its own set of machine-level performance counters, implemented as so-called Control and Status Registerss (CSRs) [39]. Every higher-privileged mode (e.g., M-, H-, and S-Mode) has their own set of CSRs, which include:

- the number of processor cycles: mcycle

- the number of *retired* (executed) instructions: minstret

- a high-resolution real-time counter: mtime

Processors may use more unprivileged registers for event counting, so the actual number of usable HPCs depends on the implementation of the hardware.

### 5.1 Setup

In order to profile and monitor different zones, we adapted our Secure Monitor to save and manage HPCs for every zone individually. We assume the same threat model as before (see subsection 4.1). Therefore, every zone has its own active counters, which are saved when a context switch happens (to another zone or the Secure Monitor). The monitoring runs on the same privilege level than other zones (U-Mode), but has added privileges, which means it can access the counters of all the other zones. This is achieved by adapting the PMP settings for the privileged zone during execution. We also adapted the Secure Monitor scheduler such that the monitoring zone is executed regularly and may not starve out. Since U-Mode software has no access to privileged CSRs, only the Secure Monitor can access the performance counters.

For the detection, we use a signature-based approach where we profile the performance of counters in an "offline" learning phase with several executions. During the actual execution, the Secure Monitor is notified when a violation is detected. The actual reaction to the violation can differ depending on the use-case.

### 5.2 Implementation

Monitoring with HPCs requires hardware registers to count the events. RISC-V defines up to 29 different general-purpose registers (31 registers excluding x1/ra for the return address and x2/sp for the stack pointer) [38], but most devices only implement a fraction of these to be used with HPC. An overview of available HPC can be usually found in the data sheet of the devices. For our test boards, 23 different events can be counted [31].

Since HPCs are a hardware feature, they have no awareness of the system or the OS running on the device. We need to add the context of current zones and privilege levels in the implementation of the Secure Monitor. The data structure for *zones* was extended such that it manages the current value of a specific HPC. Whenever a zone is entered or exited, we respectively load or save the current value of the counters. Therefore, every zone is assigned its own HPC counters, and we can differentiate and compare them easily.

In the offline phase, we collect and create a unique signature with expected HPCs for a specific application, which is known to the Secure Monitor when the device is running. This also means that an attacker has no access to the signature (stored in the monitor zone) and therefore cannot anticipate if and which manipulations might be detected. After the monitor has collected enough HPC values for every zone, it matches the values with the static signature for every application and may raise an alarm if there is a mismatch. The reaction to this event is left to the vendor and developer of the system and is out of scope.

### 5.3 Evaluation

For our experiment, we selected six HPC values and two test binaries from the BEEBS benchmark suite.

**Effectiveness** The binary *picojpeg* is a JPEG decoder for low-power devices and microcontrollers<sup>2</sup>. The binary *nettle-aes* is an Advanced Encryption Standard (AES) implementation and part of the cryptographic library Nettle<sup>3</sup>. Because of their implementations, the two programs perform very differently, which is why we selected them for our evaluation. In order to test the security, we simulate

<sup>&</sup>lt;sup>2</sup> https://github.com/richgel999/picojpeg

<sup>&</sup>lt;sup>3</sup> https://www.lysator.liu.se/~nisse/nettle/nettle.html

|                 | Deviation in $\%$ |       |      |      |        |      |

|-----------------|-------------------|-------|------|------|--------|------|

| Binary          | INT               | JAL   | CB   | MIO  | PFE    | BDM  |

| picojpeg-inp2   | 42.5              | 24.4  | 31.0 | 45.6 | 111.8  | 31.0 |

| picojpeg-inp3   | 32.2              | 35.3  | 18.0 | 33.7 | 120.2  | 12.4 |

| picojpeg-mod1   | 12.4              | 33.0  | 15.6 | 3.3  | 18.9   | 4.0  |

| picojpeg-mod2   | 14.9              | 148.3 | 2.2  | 24.6 | 2040.5 | 5.9  |

| nettle-aes-inp2 | 0.1               | 0.0   | 0.2  | 0.1  | 0.2    | 0.4  |

| nettle-aes-inp3 | 0.2               | 0.2   | 0.0  | 0.1  | 0.1    | 0.3  |

| nettle-aes-mod1 | 1.8               | 21.4  | 10.8 | 0.4  | 0.1    | 4.3  |

| nettle-aes-mod2 | 0.4               | 95.2  | 3.0  | 0.1  | 0.7    | 4.5  |

**Table 1.** Deviation of HPC values from default run for different modifications and events: integer arith inst retired (INT), JAL instruction retired (JAL), cond branch retired (CB), memory-mapped I/O access (MIO), pipeline flush other events (PFE), branch direction misprediction (BDM).

code manipulations by modifying the benchmark binaries. In addition to their normal execution, we inject code to achieve a control-flow manipulation and to simulate an attack. The modifications are as follows:

- picojpeg-mod1 changes an AND to an OR, modifying the output while still retaining a valid call graph.

- picojpeg-mod2 introduces a new function that calls a number of different sub-functions. This simulates a buffer overflow and a ROP attack, invalidating the original call graph.

- nettle-aes-mod1 changes the key size for the AES encryption from 256 to 192, which retains a valid call graph.

- nettle-aes-mod2 is modified in the same way as above and introduces (and calls) a new function. Again, this simulates a buffer overflow and a ROP attack.

In addition to that, we experimented with different inputs to show how much they would influence the HPC values for the unmodified binary. For *picojpeg*, we selected two JPEG files with the same resolution, but different quality (and therefore different sizes). For the *nettle-aes* binary we changed the input file for encryption (inp1) as well as the encryption key (inp2). While we experimented with all available HPCs, only six of them were suited to be used for our test binaries. The resulting HPC value differences (deviations from the unmodified binary averaged over 1000 executions) are shown in Table 1.

The results indicate that some events perform better at detecting control flow modifications than others, e.g., PFE for picojpeg-mod2 and JAL for nettleaes-mod2. We also see why we chose these binaries for the experiment. The control flow of the JPEG decoder greatly depends on the input, which is why we have such variations for different inputs. This is not true for AES, which always executes the same number of encryption "rounds" for different input files and keys.

The next insight is that for every modification, not every HPC performs well. For AES, as in its implementation most instructions happen in a loop, the number of executed instructions is more significant than other factors. Therefore, minor modifications which do not breach the allowed call graph (\*-mod1) are, in general, more difficult to detect. Furthermore, selection of appropriate HPCs greatly depends on the executable, which is why you need to use more different inputs to "train" the system better. We can see with the example of *picojpeg* why that is not feasible. As an infinite number of files can be legal JPEG files, you cannot cover all inputs. Therefore, training data will always be missing some valid execution paths for the program.

A solution to this problem might be to build dependencies between HPCs [20]. In our case, the HiFive1 board only supports two active HPCs, which does not allow building robust correlations between events. In general, this is a severe limitation of our experiment, which we discuss in section 8.

**Performance** The HPC detection approach requires a separate *zone* in the MultiZone system. In our experiment, the monitoring zone takes 32 KiB of ROM. During execution, the zone occupies 1 KiB of main memory for stack and heap, which is approximately 8.33 % for the HiFive1 Rev B. On the Arty A7 board, the total memory overhead is 1.67 %, due to its bigger available memory.

The runtime performance depends on the chosen scheduler strategy. We selected an interval of 100 ms for our round-robin scheduler, which leads to a performance overhead of 0.1 % compared to non-monitored applications. Since our monitoring zone finishes its execution before this interval, the overhead is realistically below the above number. We found that the memory bus of the HiFive1 Rev B is significantly slower than comparable boards (e.g., the Arty A7), which slows down all zones that access main memory more often, such as the monitoring zone. Therefore, we estimate that the overhead might be even lower on production-ready devices and will only be influenced by the detection's complexity.

## 6 Related Work

The existing works most related to R5Detect are implementations of secure monitoring for mostly other architectures, such as ARM and x86. Only a few papers focus on CFI and RISC-V, and most of these require an extension of the ISA [10,11,26,37,45].

Regarding TEE on RISC-V, numerous designs and implementations are proposed, which are based again on non-standard extensions of the ISA [7,24,41]. To our knowledge, only the open-source Keystone Enclave [19] and proprietary MultiZone<sup>4</sup> adhere to the most recent RISC-V ISA standards. There have also been recent efforts to bring TEE features to standard RISC-V architectures [5].

Our Shadow Stack is also based on some previous works in the field. In [1] the authors present their CFI methods using a user-level shadow stack implementation and dynamic memory checks to achieve protection. Subsequent works build on this idea to monitor bare-metal apps and smaller real-time operating

<sup>&</sup>lt;sup>4</sup> https://hex-five.com/multizone-security-tee-riscv/

systems [34]. With RIMI [17], the authors propose an instruction-level memory isolation RISC-V extension, which can then be used to protect a shadow stack. Currently, there are efforts to implement and ratify a new extension ("Zisslpcfi") for CFI that includes a shadow stack [29].

The topic of Hardware Performance Counters has been extensively researched for different use cases, including security [9]. More specifically, HPCs are used in malware detection [12, 35, 46], side-channel attack detection [23], kernel rootkit detection [32] and more. There are also approaches combining HPCs with TEEs, such as ARM TrustZone [14] or Intel Software Guard Extensions [18]. There are no works that implement universal HPC monitoring on standard RISC-V architectures.

## 7 Discussion

In this section, we are discussing limitations and problems raised by related work (see section 6) regarding our work on R5Detect. In our implementation, we focused on two different detection methods, each with their own implications.

## 7.1 CFI

CFI monitoring is limited by the target's program structure. Small functions may cause problems, as there might not be enough space to introduce our label. Therefore, not every function may be able to use the CFI protection. In addition, our current Shadow Stack implementation is static, which means that its size and the number of stacks must be known at compile time. This is not much of a problem for our target low-power IoT devices, as they are usually already limited in processing power and memory space, and developers need to account for the size and execution requirements of their applications anyway. Therefore, a dynamic implementation would not significantly benefit our detection and would require more code and resources to implement. For more powerful devices, that also may use a more complex Unix-based OS, a dynamic approach might be preferable.

We did not consider the power consumption of devices, which was out-ofscope for our experiments. There may be use cases where devices are attached to batteries instead of a power supply, but this sparks a number of other security considerations that our threat model does not cover. Our goal is to show the potential of low-power hardware for security applications, regardless of energy consumption.

## 7.2 HPC

Our HPC monitoring is mainly limited by the number of available counters on the hardware device. In our case, we could choose from 23 different events, but we found that some events inherently depend on the execution environment and might be unsuited for some applications. In future work, it would be interesting to find out what and how many real-world devices implement HPCs to find the sweet spot between hardware requirements and suitable event selection.

In previous work on the x86 and ARM architectures, two main issues with HPCs have been observed: *overcounting* and *non-determinism* [40]. The former describes the problem of incorrect performance counter values observed on some processors and architectures. The latter issue concerns the tools, techniques, and methods used to obtain HPC values, which may yield very different results even in a "strictly controlled environment for the same application" [9]. Especially these two issues evoke doubts on the effectiveness of performance counters for security applications.

We addressed these potential problems early in our design. Non-determinism, coupled with race conditions between different processor cores and threads, is mostly excluded in our use case. Our design is based on the MultiZone architecture, and our implementation features an own *round-robin scheduler*, which cleanly separates different zone executions from each other. Since we collect HPC values per zone, it is impossible that other zones may interfere with the currently active zone and HPCs. Therefore, we prevented the problem of non-determinism early in the design, which works regardless of the presence of multiple cores.

For the problem with overcounting, we unfortunately could not reproduce the problems described in previous works in our validation and evaluation experiments. Being a pretty new field of research, there is a lack of research about the problem of overcounting for RISC-V. We agree that security should not be solely based on HPC measurements, but we disagree with works that dismiss them completely. We see overcounting as a problem that might be based on individual processor implementations, but can be circumvented with better detection strategies, such as using a "moving average" approach to measurements instead of using fixed thresholds. Nonetheless, further research is needed to assess the scale of this problem on RISC-V.

We observed an additional challenge to consider for HPC monitoring on RISC-V: interrupts. When interrupts are triggered (e.g., by sensors or other peripherals), the Secure Monitor calls the registered interrupt handler. If these handlers are not considered during training and not included in the characteristic signature of a program, it may trigger a false positive in our detection, as the handler will influence the selected HPC differently than the main program. Since interrupts are triggered at unpredictable intervals all over the system, one needs to count and manage all interrupts in the Secure Monitor in order to even out the detection. In our opinion, this is an often overlooked problem with HPC measurements, and we did not find any mentions of this in related work.

## 8 Conclusion

In this work we present R5Detect, a software-based CFI detection with hardwarebased security measures. We implemented R5Detect on top of standard RISC-V features for IoT and embedded devices that lack proper security features. With our Shadow Stack approach, the majority of applications become resilient to CFI and ROP attacks at the cost of below 5 % runtime overhead and with minimal ROM size requirements. We expect this number to decrease significantly in the future, as Shadow Stacks might become a standard extension of the RISC-V ISA, shifting the solution to the hardware-accelerated micro-architectural implementation.

We combine the above protection with a detection based on Hardware Performance Counters. While severely limited on our test device, HPCs may become a significant building block for detecting unexpected and unwanted software behavior. We also address common problems related to security based on HPCs in our discussion. Combined with TEE-related features, R5Detect can protect itself from a full compromise of the OS and its user apps.

With our work, we hope to inspire more research in the field of IoT and embedded security, as these devices have become ubiquitous and deserve more attention from the security community.

## References

- Abadi, M., Budiu, M., Erlingsson, Ú., Ligatti, J.: Control-flow integrity principles, implementations, and applications. ACM Trans. Inf. Syst. Secur. 13(1), 4:1–4:40 (2009). https://doi.org/10.1145/1609956.1609960, https://doi.org/10.1145/1609956.1609960

- Ahmadi, M.M., Khalid, F., Shafique, M.: Side-channel attacks on RISC-V processors: Current progress, challenges, and opportunities. CoRR abs/2106.08877 (2021), https://arxiv.org/abs/2106.08877

- Alrawi, O., Lever, C., Antonakakis, M., Monrose, F.: Sok: Security evaluation of home-based iot deployments. In: 2019 IEEE Symposium on Security and Privacy, SP 2019, San Francisco, CA, USA, May 19-23, 2019. pp. 1362–1380. IEEE (2019). https://doi.org/10.1109/SP.2019.00013, https://doi.org/10.1109/SP.2019.00013

- Antonakakis, M., April, T., Bailey, M., Bernhard, M., Bursztein, E., Cochran, J., Durumeric, Z., Halderman, J.A., Invernizzi, L., Kallitsis, M., Kumar, D., Lever, C., Ma, Z., Mason, J., Menscher, D., Seaman, C., Sullivan, N., Thomas, K., Zhou, Y.: Understanding the mirai botnet. In: Kirda, E., Ristenpart, T. (eds.) 26th USENIX Security Symposium, USENIX Security 2017, Vancouver, BC, Canada, August 16-18, 2017. pp. 1093–1110. USENIX Association (2017), https://www.usenix.org/conference/usenixsecurity17/technical-sessions/presentation/antonakakis

- RISC-V architectures. 5. Bove, D.: Secure services for standard In: ARES 2022: The 17th International Conference on Availability, Reliability and Vienna, Austria, August 23 – 26, 2022. pp. Security, https://doi.org/10.1145/3538969.3538998, 23:1-23:7.ACM (2022).https://doi.org/10.1145/3538969.3538998

- Cloosters, T., Paaßen, D., Wang, J., Draissi, O., Jauernig, P., Stapf, E., Davi, L., Sadeghi, A.: Riscyrop: Automated return-oriented programming attacks on RISC-V and ARM64. In: 25th International Symposium on Research in Attacks, Intrusions and Defenses, RAID 2022, Limassol, Cyprus, October 26-28, 2022. pp. 30–42. ACM (2022). https://doi.org/10.1145/3545948.3545997, https://doi.org/10.1145/3545948.3545997

- Costan, V., Lebedev, I.A., Devadas, S.: Sanctum: Minimal hardware extensions for strong software isolation. In: Holz, T., Savage, S. (eds.)

25th USENIX Security Symposium, USENIX Security 16, Austin, TX, USA, August 10-12, 2016. pp. 857–874. USENIX Association (2016), https://www.usenix.org/conference/usenixsecurity16/technical-sessions/presentation/costan

- 8. Cowan. C.: Stackguard: Automatic adaptive detection preand buffer-overflow In: Rubin, Provention of attacks. A.D. (ed.)Security ceedings of the 7th USENIX Symposium,  $\operatorname{San}$ Anto-(1998).nio, TX, USA, January 26-29, 1998. USENIX Association https://www.usenix.org/conference/7th-usenix-security-symposium/stackguard-automatic-adaptive-detection-and

- 9. Das, S., Werner, J., Antonakakis, M., Polychronakis, M., Monrose, F.: Sok: The challenges, pitfalls, and perils of using hardware performance counters for security. In: 2019 IEEE Symposium on Security and Privacy, SP 2019, San Francisco, CA, USA, May 19-23, 2019. pp. 20–38. IEEE (2019). https://doi.org/10.1109/SP.2019.00021, https://doi.org/10.1109/SP.2019.00021

- De, A., Basu, A., Ghosh, S., Jaeger, T.: FIXER: flow integrity extensions for embedded RISC-V. In: Teich, J., Fummi, F. (eds.) Design, Automation & Test in Europe Conference & Exhibition, DATE 2019, Florence, Italy, March 25-29, 2019. pp. 348–353. IEEE (2019). https://doi.org/10.23919/DATE.2019.8714980, https://doi.org/10.23919/DATE.2019.8714980

- Delshadtehrani, L., Canakci, S., Egele, M., Joshi, A.: Sealpk: Sealable protection keys for RISC-V. In: Design, Automation & Test in Europe Conference & Exhibition, DATE 2021, Grenoble, France, February 1-5, 2021. pp. 1278–1281. IEEE (2021). https://doi.org/10.23919/DATE51398.2021.9473932, https://doi.org/10.23919/DATE51398.2021.9473932

- Demme, J., Maycock, M., Schmitz, J., Tang, A., Waksman, A., Sethumadhavan, S., Stolfo, S.J.: On the feasibility of online malware detection with performance counters. In: Mendelson, A. (ed.) The 40th Annual International Symposium on Computer Architecture, ISCA'13, Tel-Aviv, Israel, June 23-27, 2013. pp. 559–570. ACM (2013). https://doi.org/10.1145/2485922.2485970, https://doi.org/10.1145/2485922.2485970

- Garcia-Serrano, A.: Anomaly detection for malware identification using hardware performance counters (2015). https://doi.org/10.48550/ARXIV.1508.07482, https://arxiv.org/abs/1508.07482

- Jung, B., Eichler, C., Röckl, J., Schlenk, R., Hönig, T., Müller, T.: Trusted monitor: Tee-based system monitoring. In: XII Brazilian Symposium on Computing Systems Engineering, SBESC 2022, Fortaleza, CE, Brazil, November 21-24, 2022. pp. 1–8. IEEE (2022). https://doi.org/10.1109/SBESC56799.2022.9964869, https://doi.org/10.1109/SBESC56799.2022.9964869

- 15. Karliner, O.: Freertos tcp/ip stack vulnerabilities the details. https://www.zimperium.com/blog/freertos-tcpip-stack-vulnerabilities-details/ (dec 2018), last access: 2022-11-01

- 16. Karlsson, H.: OpenMZ: a C implementation of the MultiZone API. Master's thesis, School of Electrical Engineering and Computer Science (EECS) (Sep 2020), http://kth.diva-portal.org/smash/get/diva2:1466978/FULLTEXT01.pdf

- 17. Kim, H., Lee, J., Pratama, D., Awaludin, A.M., Kim, H., Kwon, D.: RIMI: instruction-level memory isolation for embedded systems on RISC-V. In: IEEE/ACM International Conference On Computer Aided Design, ICCAD 2020, San Diego, CA, USA, November 2-5, 2020. pp. 34:1–34:9. IEEE (2020). https://doi.org/10.1145/3400302.3415727, https://doi.org/10.1145/3400302.3415727

- Lantz, D., Boeira, F., Asplund, M.: Towards self-monitoring enclaves: Side-channel detection using performance counters. In: Reiser, H.P., Kyas, M. (eds.) Secure IT Systems - 27th Nordic Conference, NordSec 2022, Reykjavic, Iceland, November 30-December 2, 2022, Proceedings. Lecture Notes in Computer Science, vol. 13700, pp. 120–138. Springer (2022). https://doi.org/10.1007/978-3-031-22295-5\_7, https://doi.org/10.1007/978-3-031-22295-5%5F7

- Lee, D., Kohlbrenner, D., Shinde, S., Asanovic, K., Song, D.: Keystone: an open framework for architecting trusted execution environments. In: Bilas, A., Magoutis, K., Markatos, E.P., Kostic, D., Seltzer, M.I. (eds.) EuroSys '20: Fifteenth EuroSys Conference 2020, Heraklion, Greece, April 27-30, 2020. pp. 38:1–38:16. ACM (2020). https://doi.org/10.1145/3342195.3387532, https://doi.org/10.1145/3342195.3387532

- Malone, C., Zahran, M., Karri, R.: Are hardware performance counters a cost effective way for integrity checking of programs. In: Chen, Y., Xu, S., Sadeghi, A., Zhang, X. (eds.) Proceedings of the sixth ACM workshop on Scalable trusted computing, STCCCS 2011, Chicago, Illinois, USA, October 17, 2011. pp. 71–76. ACM (2011). https://doi.org/10.1145/2046582.2046596, https://doi.org/10.1145/2046582.2046596

- Mulder, E.D., Gummalla, S., Hutter, M.: Protecting RISC-V against side-channel attacks. In: Proceedings of the 56th Annual Design Automation Conference 2019, DAC 2019, Las Vegas, NV, USA, June 02-06, 2019. p. 45. ACM (2019). https://doi.org/10.1145/3316781.3323485, https://doi.org/10.1145/3316781.3323485

- Nashimoto, S., Suzuki, D., Ueno, R., Homma, N.: Bypassing isolated execution on RISC-V using side-channel-assisted fault-injection and its countermeasure. IACR Trans. Cryptogr. Hardw. Embed. Syst. 2022(1), 28–68 (2022). https://doi.org/10.46586/tches.v2022.i1.28-68, https://doi.org/10.46586/tches.v2022.i1.28-68

- 23. Nomani, J., Szefer, J.: Predicting program phases and defending against sidechannel attacks using hardware performance counters. In: Lee, R.B., Shi, W., Szefer, J. (eds.) Proceedings of the Fourth Workshop on Hardware and Architectural Support for Security and Privacy, HASPISCA 2015, Portland, OR, USA, June 14, 2015. pp. 9:1–9:4. ACM (2015). https://doi.org/10.1145/2768566.2768575, https://doi.org/10.1145/2768566.2768575

- 24. Noorman, J., Agten, P., Daniels, W., Strackx, R., Herrewege, A.V., Huygens, C., Preneel, B., Verbauwhede, I., Piessens, F.: Sancus: Low-cost trustworthy extensible networked devices with a zero-software trusted computing base. In: King, S.T. (ed.) Proceedings of the 22th USENIX Security Symposium, Washington, DC, USA, August 14-16, 2013. pp. 479–494. USENIX Association (2013), https://www.usenix.org/conference/usenixsecurity13/technical-sessions/presentation/noorman

- Pallister, J., Hollis, S.J., Bennett, J.: BEEBS: open benchmarks for energy measurements on embedded platforms. CoRR abs/1308.5174 (2013), https://arxiv.org/abs/1308.5174

- Park, S., Kang, D., Kang, J., Kwon, D.: Bratter: An instruction set extension for forward control-flow integrity in RISC-V. Sensors 22(4), 1392 (2022). https://doi.org/10.3390/s22041392, https://doi.org/10.3390/s22041392

- 27. Pincus, J.D., Baker, B.: Beyond stack smashing: Recent advances in exploiting buffer overruns. IEEE Secur. Priv. 2(4), 20–27 (2004). https://doi.org/10.1109/MSP.2004.36, https://doi.org/10.1109/MSP.2004.36

- Prandini, M., Ramilli, M.: Return-oriented programming. IEEE Secur. Priv. **10**(6), 84–87 (2012). https://doi.org/10.1109/MSP.2012.152, https://doi.org/10.1109/MSP.2012.152

- RISC-V International: Specification Status. https://wiki.riscv.org/display/HOME/Specification+Status (2022), last access: 2022-01-19

- 30. Shacham, H., Page, M., Pfaff, B., Goh, E., Modadugu, N., Boneh, D.: On the effectiveness of address-space randomization. In: Atluri, V., Pfitzmann, B., McDaniel, P.D. (eds.) Proceedings of the 11th ACM Conference on Computer and Communications Security, CCS 2004, Washington, DC, USA, October 25-29, 2004. pp. 298–307. ACM (2004). https://doi.org/10.1145/1030083.1030124, https://doi.org/10.1145/1030083.1030124

- 31. SiFive Inc.: SiFive FE310-G002 manual. https://www.sifive.com/documentation (sep 2022), last access: 2022-12-01

- 32. Singh, B., Evtyushkin, D., Elwell, J., Riley, R., Cervesato, I.: On the detection of kernel-level rootkits using hardware performance counters. In: Karri, R., Sinanoglu, O., Sadeghi, A., Yi, X. (eds.) Proceedings of the 2017 ACM on Asia Conference on Computer and Communications Security, AsiaCCS 2017, Abu Dhabi, United Arab Emirates, April 2-6, 2017. pp. 483–493. ACM (2017). https://doi.org/10.1145/3052973.3052999, https://doi.org/10.1145/3052973.3052999

- 33. Tu, T., Qin, J., Zhang, H., Chen, M., Xu, T., Huang, Y.: A comprehensive study of mozi botnet. Int. J. Intell. Syst. 37(10), 6877–6908 (2022). https://doi.org/10.1002/int.22866, https://doi.org/10.1002/int.22866

- 34. Walls, R.J., Brown, N.F., Baron, T.L., Shue, C.A., Okhravi, H., Ward, B.C.: Control-flow integrity for real-time embedded systems. In: Quinton, S. (ed.) 31st Euromicro Conference on Real-Time Systems, ECRTS 2019, July 9-12, 2019, Stuttgart, Germany. LIPIcs, vol. 133, pp. 2:1–2:24. Schloss Dagstuhl - Leibniz-Zentrum für Informatik (2019). https://doi.org/10.4230/LIPIcs.ECRTS.2019.2, https://doi.org/10.4230/LIPIcs.ECRTS.2019.2

- 35. Wang, X., Chai, S.M., Isnardi, M.A., Lim, S., Karri, R.: Hardware performance counter-based malware identification and detection with adaptive compressive sensing. ACM Trans. Archit. Code Optim. 13(1), 3:1–3:23 (2016). https://doi.org/10.1145/2857055, https://doi.org/10.1145/2857055

- 36. Wang, X., Konstantinou, C., Maniatakos, M., Karri, R.: Confirm: Detecting firmware modifications in embedded systems using hardware performance counters. In: Marculescu, D., Liu, F. (eds.) Proceedings of the IEEE/ACM International Conference on Computer-Aided Design, ICCAD 2015, Austin, TX, USA, November 2-6, 2015. pp. 544–551. IEEE (2015). https://doi.org/10.1109/ICCAD.2015.7372617, https://doi.org/10.1109/ICCAD.2015.7372617

- 37. Wang, Y., Wu, J., Yue, T., Ning, Z., Zhang, F.: Rettag: hardwareassisted return address integrity on RISC-V. In: Lindorfer, M., Polakis, J. (eds.) EuroSecEUROSYS 2022: Proceedings of the 15th European Workshop on Systems Security, Rennes, France, April 5-8, 2022. pp. 50–56. ACM (2022). https://doi.org/10.1145/3517208.3523758, https://doi.org/10.1145/3517208.3523758

- Waterman, A., Asanović, K.: The RISC-V instruction set manual, volume i: Userlevel isa, document version 2019121. Tech. rep., RISC-V Foundation (Jul 2019), https://github.com/riscv/riscv-isa-manual/releases/download/Ratified-IMAFDQC/riscv-spec-20191213.pdf

- 39. Waterman, Asanović, Κ., Hauser. J.: The Α., risc-v instruction manual, volume ii: Privileged architecture, document set version 2021120. Tech. rep., RISC-V International (Dec 2021),https://github.com/riscv/riscv-isa-manual/releases/download/Priv-v1.12/riscv-privileged-20211203.pdf

- 40. Weaver, V.M., Terpstra, D., Moore, S.: Non-determinism and overcount on modern hardware performance counter implementations. In: 2012 IEEE International Symposium on Performance Analysis of Systems & Software, Austin, TX, USA, 21-23 April, 2013. pp. 215–224. IEEE Computer Society (2013). https://doi.org/10.1109/ISPASS.2013.6557172, https://doi.org/10.1109/ISPASS.2013.6557172

- 41. Weiser, S., Werner, M., Brasser, F., Malenko, M., Mangard, S., Sadeghi, A.: TIMBER-V: tag-isolated memory bringing fine-grained enclaves to RISC-V. In: 26th Annual Network and Distributed System Security Symposium, NDSS 2019, San Diego, California, USA, February 24-27, 2019. The Internet Society (2019), https://www.ndss-symposium.org/ndss-paper/timber-v-tag-isolated-memory-bringing-fine-grained-enclaves-to-ris

- Werner, M., Schilling, R., Unterluggauer, T., Mangard, S.: Protecting RISC-V processors against physical attacks. In: Teich, J., Fummi, F. (eds.) Design, Automation & Test in Europe Conference & Exhibition, DATE 2019, Florence, Italy, March 25-29, 2019. pp. 1136– 1141. IEEE (2019). https://doi.org/10.23919/DATE.2019.8714811, https://doi.org/10.23919/DATE.2019.8714811

- Xu, J., Kalbarczyk, Z., Iyer, R.K.: Transparent runtime randomization for security. In: 22nd Symposium on Reliable Distributed Systems (SRDS 2003), 6-8 October 2003, Florence, Italy. p. 260. IEEE Computer Society (2003). https://doi.org/10.1109/RELDIS.2003.1238076, https://doi.org/10.1109/RELDIS.2003.1238076

- 44. Yang, K., Blaauw, D.T., Sylvester, D.: Hardware designs for security in ultra-low-power iot systems: An overview and survey. IEEE Micro 37(6), 72–89 (2017). https://doi.org/10.1109/MM.2017.4241357, https://doi.org/10.1109/MM.2017.4241357

- Zgheib, A., Potin, O., Rigaud, J., Dutertre, J.: A CFI verification system based on the RISC-V instruction trace encoder. In: 25th Euromicro Conference on Digital System Design, DSD 2022, Maspalomas, Spain, August 31 - Sept. 2, 2022. pp. 456–463. IEEE (2022). https://doi.org/10.1109/DSD57027.2022.00067, https://doi.org/10.1109/DSD57027.2022.00067

- 46. Zhou, B., Gupta, A., Jahanshahi, R., Egele, M., Joshi, A.: Hardware performance counters can detect malware: Myth or fact? In: Kim, J., Ahn, G., Kim, S., Kim, Y., López, J., Kim, T. (eds.) Proceedings of the 2018 on Asia Conference on Computer and Communications Security, AsiaCCS 2018, Incheon, Republic of Korea, June 04-08, 2018. pp. 457–468. ACM (2018). https://doi.org/10.1145/3196494.3196515, https://doi.org/10.1145/3196494.3196515