# Enhanced OpenMP Algorithm to Compute All-Pairs Shortest Path on x86 Architectures

Sergio Calderón $^{1,2}$ , Enzo Rucci $^{1,3[0000-0001-6736-7358]\star}$ , and Franco Chichizola  $^{1[0000-0001-8857-6343]}$

III-LIDI, Facultad de Informática, UNLP - CIC.

La Plata (1900), Bs As, Argentina

{scalderon,erucci,francoch}@lidi.info.unlp.edu.ar

Becario de Entrenamiento, CIC

Comisión de Investigaciones Científicas (CIC).

La Plata (1900), Bs As, Argentina

**Abstract.** Graphs have become a key tool when modeling and solving problems in different areas. The Floyd-Warshall (FW) algorithm computes the shortest path between all pairs of vertices in a graph and is employed in areas like communication networking, traffic routing, bioinformatics, among others. However, FW is computationally and spatially expensive since it requires  $O(n^3)$  operations and  $O(n^2)$  memory space. As the graph gets larger, parallel computing becomes necessary to provide a solution in an acceptable time range. In this paper, we studied a FW code developed for Xeon Phi KNL processors and adapted it to run on any Intel x86 processors, losing the specificity of the former. To do so, we verified one by one the optimizations proposed by the original code, making adjustments to the base code where necessary, and analyzing its performance on two Intel servers under different test scenarios. In addition, a new optimization was proposed to increase the concurrency degree of the parallel algorithm, which was implemented using two different synchronization mechanisms. The experimental results show that all optimizations were beneficial on the two x86 platforms selected. Last, the new optimization proposal improved performance by up to 23%.

**Keywords:** Floyd-Warshall · Multicore · APSP · Xeon · Xeon Phi Knights Landing · Core · OpenMP

This version of the contribution has been accepted for publication, after peer review (when applicable) but is not the Version of Record and does not reflect post-acceptance improvements, or any corrections. The Version of Record is available online at: https://doi.org/10.1007/978-3-031-62245-8\_4.

Use of this Accepted Version is subject to the publisher's Accepted Manuscript terms of use https://www.springernature.com/gp/open-research/policies/accepted-manuscript-terms

<sup>\*</sup> Corresponding author.

#### 1 Introduction

The Floyd-Warshall (FW) [3,17] algorithm computes the shortest path between all pairs of vertices in a graph and is employed in areas like communication networking [8], traffic routing [7], bioinformatics [9], among others. However, FW is computationally and spatially expensive since it requires  $O(n^3)$  operations and  $O(n^2)$  memory space, where n is the number of vertices in a graph. As the graph gets larger, parallel computing becomes necessary to provide a solution in an acceptable time frame. This is why the scientific community has made multiple efforts for this purpose [10,16,5,4,18,15,14,13]. Focusing on Intel Xeon Phi platforms, Rucci et al. [12] explored its use to accelerate FW in the first generation (KNC, Knights Corner), while Costi et al. [2] extended it to the second (Knights Landing, KNL).

In [1], we studied the code developed by [2] and adapted it to run on Intel x86 processors, losing the specificity of the Xeon Phi KNL. To do so, we verified one by one the optimizations proposed by [2], making adjustments to the base code where necessary, and analyzing its performance on two Intel servers under different test scenarios. This paper is an extended and thoroughly revised version of [1]. The work has been extended by providing:

- The proposal of a new optimization for the parallel FW algorithm (*intra-round parallelism*) and its implementation using different synchronization mechanisms (semaphores vs. condition variables).

- A performance analysis of the proposed optimization on 2 different Intel x86 servers

- The creation of a public git repository with the different codes developed for this paper <sup>4</sup>.

The rest of the paper is organized as follows. Section 2 introduces the background of this work. Section 3 details the adaptation process and the new optimizacion proposal. In Section 4, performance results are presented and finally, in Section 5, conclusions and some ideas for future research are summarized.

# 2 Background

## 2.1 Intel Xeon Phi

Xeon Phi is the brand name that Intel used for a series of many-core, HPC-oriented processors. In 2012, Intel launched the first Phi generation (KNC) with 61 x86 pentium cores (4 hardware threads per core) equipped with a 512-bit vector unit (VPU) each. In contrast to KNC co-processors connected via a PCI Express bus to the host, the second Phi generation (KNL) can act as self-boot processors. KNL processors feature a large number of cores with hyper-threading support, the incorporation of AVX-512's 512-bit vector instructions, and the integration of a high-bandwidth memory (HBM), among others [11]. The latest

<sup>4</sup> https://bit.ly/cacic23-fw

generation (Knight Mills, KNM) was released in late 2017, being a KNL variant with specific instructions for deep machine learning. Finally, Intel announced that it would discontinue the Xeon Phi series in 2018 to focus on the development of graphics boards (GPUs)  $^{5}$ .

#### 2.2 Intel Xeon and Core

Currently, Intel offers two processor segments in the x86 family: Xeon and Core. Intel Xeon processors are designed for enterprise and server tasks that require high-performance computing and reliability, while Intel Core processors are ideal for general-purpose use, including gaming, office applications and multimedia entertainment.

In terms of architectural features, Xeon processors tend to have more cores, specific technologies for virtualization and security, support for multi-socket configuration, among other advanced features. In opposite sense, Core processors tend to have higher frequencies, lower power consumption and lower price.

The choice between Xeon and Core will depend on the specific application needs, budget and user preferences.

#### 2.3 FW Algorithm

The pseudocode of FW is shown in Fig. 1. Given a graph G of N vertexes, FW receives as input a dense  $N \times N$  matrix D that contains the distances between all pairs of vertexes from G, where  $D_{i,j}$  represents the distance from node i to node j <sup>6</sup>. FW computes N iterations, evaluating in the k-th iteration all possible paths between vertexes i and j that have kas the intermediate vertex. As a result, it produces an updated matrix D, where  $D_{i,j}$  now contains the shortest distance between nodes i and j up to that step. Also, FW builds an additional matrix P that records the paths associated with the shortest distances.

```

\begin{array}{l} \mathbf{for} \ k \leftarrow 0 \ \mathbf{to} \ N-1 \ \mathbf{do} \\ \mathbf{for} \ i \leftarrow 0 \ \mathbf{to} \ N-1 \ \mathbf{do} \\ \mathbf{for} \ j \leftarrow 0 \ \mathbf{to} \ N-1 \ \mathbf{do} \\ \mathbf{if} \ D_{i,j} \geq D_{i,k} + D_{k,j} \ \mathbf{then} \\ D_{i,j} \leftarrow D_{i,k} + D_{k,j} \\ P_{i,j} \leftarrow k \\ \mathbf{end} \ \mathbf{if} \\ \mathbf{end} \ \mathbf{for} \\ \end{array}

```

Fig. 1. Pseudocode of the FW algorithm

**Blocked FW Algorithm.** At first glance, the nested triple loop structure of this algorithm is similar to that of dense matrix multiplication (MM). However, since read and write operations are performed on the same matrix, the three

<sup>&</sup>lt;sup>5</sup> https://hardzone.es/2018/07/25/intel-adios-xeon-phi-reemplazados-tarjetas-graficas/

<sup>&</sup>lt;sup>6</sup> If there is no path between nodes i and j, their distance is considered to be infinite (usually represented as the largest positive value)

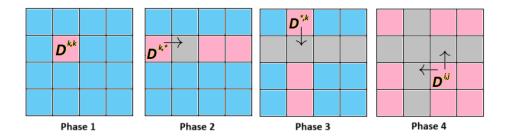

Fig. 2. BFW computation phases and block dependencies

loops cannot be freely exchanged, as is the case with MM. Despite this, the FW algorithm can be computed by blocks under certain conditions [16].

The blocked FW algorithm (BFW) divides matrix D into blocks of size  $BS \times BS$ , totaling  $(N/BS)^2$  blocks. Computation is organized in R = N/BS rounds, where each round consists of 4 phases ordered according to the data dependencies between the blocks:

- 1. Phase 1: Update the  $D^{k,k}$  block because it only depends on itself.

- 2. Phase 2: Update the blocks in row k of blocks  $(D^{k,*})$  because each of these depends on itself and on  $D^{k,k}$ .

- 3. Phase 3: Update the blocks in column k of blocks  $(D^{*,k})$  because each of these depends on itself and on  $D^{k,k}$ .

- 4. Phase 4: Update the remaining  $D^{i,j}$  blocks of the matrix because each of these depends on blocks  $D^{i,k}$  and  $D^{k,j}$  on its row and column of blocks, respectively.

Figure 2 shows each of the computation phases and the dependencies between blocks. The pink squares represent blocks that are being computed, gray squares are those that have already been processed, and sky-blue squares are the ones that have not been computed yet. Last, arrows show the dependencies between blocks for each phase.

## 2.4 Base code

As base code, we used the one from [2], which is a FWB algorithm specifically developed for Intel's Xeon Phi KNL processors. The following is a description of the different optimizations considered in the previous work:

- Opt-0: Multi-threading. A multi-threaded version is obtained using OpenMP. In Phases 2 to 4, the blocks are distributed among the different threads utilizing the for directive with dynamic scheduling. In the case of Phase 1, since it consists of a single block, the iterations within it are distributed among the threads.

- Opt-1: MCDRAM. Since this is a bandwidth-limited application, using this special memory is greatly beneficial. Executions are done using the numactl -p command to use the DDR memory as an auxiliary one.

Table 1. Experimental platforms

| ID                     | Core i5              | Xeon Platinum               |

|------------------------|----------------------|-----------------------------|

| Processor              | Intel Core i5-10400F | 2×Intel Xeon Platinum 8276L |

| Cores (ht)             | 6 (12)               | 56 (112)                    |

| Clock Frequency (base) | $2.9 \mathrm{Ghz}$   | $2.2 \mathrm{Ghz}$          |

| RAM memory             | 32  GB               | 250  GB                     |

| OS                     | Debian 11            | Ubuntu 20.04 LTS            |

- Opt-2: SSE vectorization. Using the OpenMP simd directive, the operations of the innermost loop are vectorized when computing each block. Typically, compilers use the 128-bit SSE instruction set by default, which allows the CPU to pack 2 double-precision multiply-add operations (4 flops) or 4 single-precision multiply-add operations (8 flops).

- Opt-3: AVX2 vectorization. AVX2 doubles the number of simultaneous operations concerning SSE. Thus, the CPU is guided to use 256-bit AVX instructions by adding the -xAVX2 flag to the compilation process (if supported).

- Opt-4: AVX-512 vectorization. As the previous case, the -xMIC-AVX512 flag is included to use 512-bit AVX512 extensions. In this way, the CPU can compute 8 double-precision multiply-add operations (16 flops) or 32 single-precision multiply-add operations (64 flops).

- Opt-5: Data alignment. mm\_malloc() allocates aligned blocks of memory,

i.e., data is stored aligned to the beginning of each cache line. In this way,

subsequent read and write operations are optimized.

- Opt-6: Branch prediction. The distance comparison is a hotspot of FW. By including the built-in \_\_builtin\_expect compiler macro, if statement branches can be better predicted. The more the scheduler gets right, the more instruction-level parallelism the processor can exploit.

- Opt-7: Loop unrolling. By fully unrolling the innermost loop and loop i only once.

- Opt-8: Thread affinity. Threads are distributed among cores according

to the variable KMP\_AFFINITY. Different affinity types (balanced, compact or

scatter) and granularities (fine, core or tile) can be specified.

## 3 Implementation

#### 3.1 Code adaptation to x86 architectures

The code base from Section 2 was adapted for its execution on the two x86 servers (see Table 1). In both cases, the Intel ICC compiler was used, which is part of the oneAPI suite (v2021.7.1).

The adjustments carried out to the different code versions are detailed below:

- **Opt-0:** No changes are required in this version.

- Opt-1: None of the platforms has MCDRAM memory, so the command numactl is ruled out.

- Opt-2 / Opt-3: No changes are required in these version.

- Opt-4: The associated flag is replaced by the one recommended for the Xeon Platinum (from -xMIC-AVX512 to -xCORE-AVX512); at the same time, it is discarded on Intel Core i5 because that extension set is not available on that processor.

- Opt-5: The Xeon Platinum keeps SIMD\_WIDTH = 512; while Core i5 reduces to 256 because AVX2 is the widest vectorization set available.

- Opt-6 / Opt-7: No changes are required in these versions.

- Opt-8: No changes are required in this version. The best affinity and granularity configuration is empirically selected.

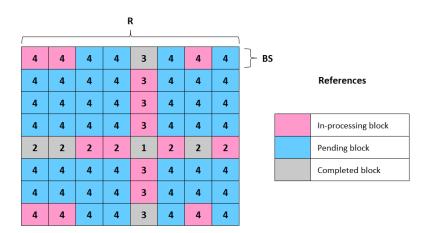

#### 3.2 Opt-9: Intra-round concurrency

This section describes a new optimization proposal, which seeks to increase the concurrency in block computation. In the FWB algorithm, phase 4 of each round must wait for the end of phases 2 and 3 above. However, as phases 2 and 3 progress, some blocks of phase 4 could already be computed (those whose dependencies have already been resolved), without waiting for the end of phases 2 and 3. Fig. 3 illustrates this improvement opportunity, where the computed blocks are shown in gray (five blocks of phase 2-3), and those in processing are shown in pink (six blocks of phase 4). This possible optimization becomes more relevant when T is large and BS is small.

**Fig. 3.** Example of optimization opportunity when R=8 and k=4

From a coding perspective, this proposal requires finer-grained synchronization than OpenMP directives can provide; thus, it must work at the Pthreads level. In this sense, two possible implementations for this idea are described below, differing in the synchronization mechanism that it is used.

**Semaphores** The first version employs semaphores to synchronize threads, through the POSIX library (semaphore.h). A semaphore matrix of dimension  $R \times R$  is added and initialized to zero. Each cell represents a block of the D matrix. The computation of a phase 4 block is conditioned by d sem\_wait operations, where d is the number of dependencies it possesses (in this case d=2). The threads that compute the dependent blocks of phases 2 and 3 are responsible for performing the corresponding sem\_post operations.

After a phase 2 block is computed, a sem\_post is performed on each semaphore of its same column j (except on its own position). Similarly, after processing a phase 3 block, a sem\_post is performed on each semaphore of its same row i (except on its own position). To compute a  $D_{i,j}$  block of phase 4, two sem\_wait operations are performed on its own position (i,j). In this way, the dependencies of phase 4 are respected at the block level.

When a round ends, all semaphores are set to zero again. The Fig. 4 shows the value of the semaphores before sem\_wait operations by phase 4.

Fig. 4. Example of semaphores values during the execution of phases 2 and 3

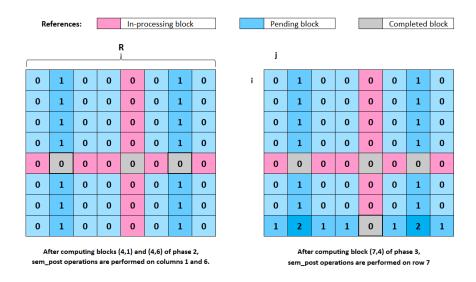

Condition variables The second version employs condition variables (cv) to synchronize threads, which are included in Pthreads library. Three additional data structures are required for this version: a cv matrix (CV), a mutex matrix (M), and an integer matrix (F); all containing  $R \times R$  elements. M is neces-

sary to operate over CV while each cell  $F_{i,j}$  indicates the number of pending dependencies to enable the computation of a block  $D_{i,j}$ , located in phase 4.

As in the previous case, d=2 in phase 4. Therefore, F is initialized with this value for all its cells in each round. A thread will only continue when  $F_{i,j}=0$ ; otherwise, it will remain suspended. After computing a phase 2 block, the remaining R-1 positions of the F matrix in the same j column are first decremented by one (ensuring mutual exclusion). Then, a cond\_signal operation is performed on the associated condition variables. Analogously, after processing a phase 3 block, one unit is subtracted from the positions of the same column i in F (again, ensuring mutual exclusion). Then, a cond\_signal is performed on the corresponding condition variables. Fig. 5 illustrates F for the same case analyzed in Fig. 4.

Fig. 5. Example of F values during the execution of phases 2 and 3

The matrix F must necessarily be included in this solution. When a <code>cond\_signal</code> is performed on a cv, it will wake up the first thread in the queue (if any); otherwise, it will have no effect. Since the <code>cond\_wait</code> operation always suspends a thread, it should only be called when pending dependencies exist. Additionally, each F update must be placed in a critical section, due to modification conflicts between phase 2 and 3 blocks (different threads could update the same cell).

# 4 Experimental Results

#### 4.1 Experimental Design

The experiments were carried out on the experimental platforms described in Table 1. The tests considered the variation of workload ( $N = \{4096, 8192, 16384\}$ ), data type (float, double), number of threads ( $T_{Core} = \{6,12\}, T_{Xeon} = \{56,112\}$ ) and block size ( $BS = \{32, 64, 128, 256\}$ ), where necessary.

All code versions work with the same input data, considering 30% of null values in the distance matrix. Each particular test was executed 8 times to minimize fluctuation, and the performance was computed based on the average of these multiple runs. Last, all code versions are available in a public web repository: https://bit.ly/cacic23-fw.

## 4.2 Experimental results of x86 adaptation

The GFLOPS (billion FLOPS) metric is used to evaluate performance: GFLOPS= $\frac{2\times N^3}{t\times 10^9}$ , where t is execution time (in seconds), and the factor 2 represents the number of floating point operations in the inner loop of any FW algorithm.

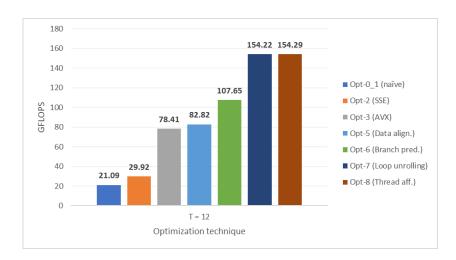

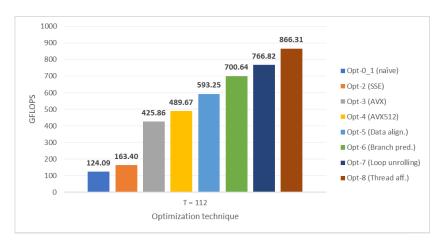

Considering an intermediate input size (N=8192) and data type=float, the results obtained for each platform are presented in Tables 2 (Core i5) and 3 (Xeon Platinum). It can be seen that the best performance for both servers is achieved using one thread per logical core and BS=128 from Opt-3 onwards.

| $\overline{\mathbf{T}}$ | $\mathbf{BS}$ | Opt-0 | Opt-2 | Opt-3 | Opt-5 | Opt-6  | Opt-7  | Opt-8  |

|-------------------------|---------------|-------|-------|-------|-------|--------|--------|--------|

| 6                       | 32            | 12.35 | 20.62 | 61.92 | 65.95 | 78.89  | 103.11 | 103.44 |

|                         | 64            | 14.37 | 19.38 | 73.58 | 78.41 | 95.47  | 136.61 | 137.42 |

|                         | 128           | 19.99 | 23.40 | 77.06 | 83.50 | 104.07 | 146.66 | 146.70 |

|                         | 256           | 20.34 | 24.61 | 55.09 | 56.99 | 86.83  | 110.86 | 111.34 |

| 12                      | 32            | 16.24 | 28.15 | 66.85 | 70.26 | 87.15  | 112.24 | 112.65 |

|                         | 64            | 19.99 | 25.52 | 78.29 | 81.36 | 101.56 | 146.24 | 147.05 |

|                         | 128           | 21.09 | 29.92 | 78.41 | 82.82 | 107.65 | 154.22 | 154.29 |

|                         | 256           | 21.22 | 32.13 | 60.51 | 62.12 | 94.19  | 110.68 | 110.80 |

Table 4 presents the improvement factor for each version over its predecessor, including their comparison with [2]. Fig. 6 and 7 show the performance achieved using the aforementioned optimal configuration on the Core i5 and Xeon Platinum machines, respectively. It can be seen that each optimization proposal effectively leads to an increase in the GFLOPS obtained on both machines. The largest improvement is achieved in the Opt-3 version by vectorizing with AVX-2 (approximately  $2.6\times$ ). Then, when comparing the widest vectorization option

**Table 3.** Performance (average GFLOPS) on Xeon Platinum when N=8192 and datatype=float

| $\overline{\mathbf{T}}$ | $\mathbf{BS}$ | Opt-0                            | Opt-2  | Opt-3  | Opt-4  | Opt-5  | Opt-6  | Opt-7  | Opt-8  |

|-------------------------|---------------|----------------------------------|--------|--------|--------|--------|--------|--------|--------|

| 56                      | 32            | 62.03<br>62.95<br>87.15<br>87.90 | 111.06 | 116.07 | 185.12 | 222.85 | 346.40 | 374.78 | 494.90 |

|                         | 64            | 62.95                            | 81.35  | 111.03 | 189.76 | 230.82 | 472.82 | 480.55 | 710.57 |

|                         | 128           | 87.15                            | 110.83 | 132.55 | 215.53 | 334.13 | 507.52 | 559.67 | 831.70 |

|                         | 256           | 87.90                            | 111.65 | 112.06 | 185.94 | 232.88 | 441.03 | 444.93 | 641.24 |

| 112                     | 32            | 79.23                            | 157.39 | 224.92 | 261.30 | 273.38 | 422.60 | 440.06 | 463.17 |

|                         | 64            | 78.10                            | 101.26 | 402.67 | 447.31 | 491.73 | 587.05 | 611.58 | 664.20 |

|                         | 128           | 124.09                           | 163.40 | 425.86 | 489.67 | 593.25 | 700.64 | 766.82 | 866.31 |

|                         | 256           | 124.47                           | 169.32 | 336.85 | 354.80 | 372.23 | 432.98 | 456.85 | 470.91 |

Table 4. Incremental improvement for each x86 platform when N=8192

| x86 platform     | Opt-1 | Opt-2 | Opt-3 | Opt-4 | Opt-5 | Opt-6 | Opt-7 | Opt-8  |

|------------------|-------|-------|-------|-------|-------|-------|-------|--------|

| Core i5          | -     | 1.42  | 2.62  | -     | 1.06  | 1.30  | 1.43  | < 1.01 |

| $Xeon\ Platinum$ | -     | 1.32  | 2.61  | 1.15  | 1.21  | 1.18  | 1.09  | 1.13   |

| $Xeon\ Phi\ KNL$ | 1.03  | 1.57  | 2.19  | 2.10  | 1.05  | 2.63  | 1.40  | < 1.01 |

versus the one that does not vectorize (Opt- $\theta$ ), a total improvement of  $3.96\times$  and  $3.72\times$  are obtained on the Xeon Platinum and the Core i5 platforms, respectively. On its behalf, branch prediction leads to a remarkable performance improvement (Opt- $\theta$ ), reaching  $1.30\times$  for Core i5, and  $1.18\times$  for Xeon Platinum. In the same line, loop unrolling provides good acceleration rates, especially for Core i5  $(1.43\times)$ .

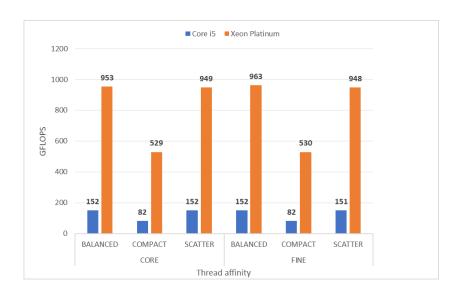

For the implementation *Opt-8*, six combinations of granularity (*core*, *fine*) and affinity (*balanced*, *compact and scatter*) were tested on both platforms [6] (see Fig. 8). The best configuration was *balanced* closely followed by *scatter* on the Xeon Platinum when using one OpenMP thread per physical core. On its behalf, no significant differences are observed between *balanced* and *scatter* on the Core i5, probably due to the small number of available cores. Last, the granularity option does not seem to affect the performance of both machines while the *compact* affinity, on the contrary, affects it negatively.

When comparing Opt-8 to  $Opt-\theta$ , an overall improvement of  $7.31 \times$  and  $6.98 \times$  are reached for Core i5 and Xeon Platinum, respectively. Like the Xeon Phi KNL case, it can be noted that all optimizations were beneficial, although not all of them impacted in the same way.

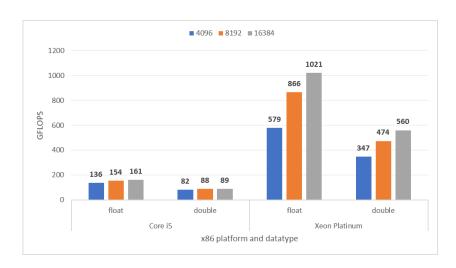

Finally, Fig. 9 shows performance achieved with the best implementation for each platform, data type, and input size tested, using the optimal configuration of T and BS. First, higher GFLOPS are obtained in the Xeon server than in the Core i5, considering its computational power. Second, it is observed that performance improves as N increases, given the higher ratio of compute versus synchronization. In particular, the magnitude of this difference is more noticeable

Fig. 6. Performance on Core i5 when N=8192 and data type=float (optimal configuration for each version)

Fig. 7. Performance on Xeon Platinum when N=8192 and data type=float (optimal configuration for each version)

when more threads are available (Xeon Platinum case). Third, using a wider precision data type such as double can lead to a more reliable result; however, it should be noted that it will come at a cost in response time, as performance drops by as much as 45%.

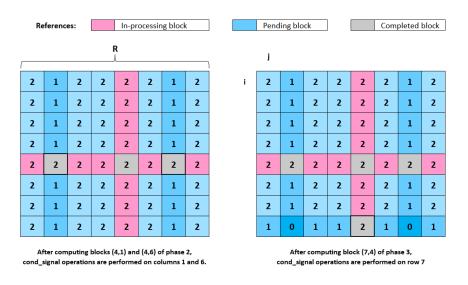

## 4.3 Experimental results of Opt-9

Table 5 shows the performance for the *Opt-9-Sem* and *Opt-9-Cond* versions on the Xeon Platinum machine. It can be seen that the optimal block size is

Fig. 8. Performance for all combinations of thread affinity on Xeon Platinum and Core i5 when N=16384, data type = float, and one thread per physical core is set

stabilized at BS=128, regardless of the data type, number of threads, or problem size used. This represents an advantage over previous versions with variable optimal BS since it requires adjustment for each situation.

${\bf Fig.\,9.}$  Performance of optimal implementation on Xeon Platinum and Core i5 varying N and data type

Table 5. Performance results for  $Opt ext{-}9 ext{-}Sem$  and  $Opt ext{-}9 ext{-}Cond$  implementations

| N     | Т   | BS  |           | double)    | GFLOP     |            |

|-------|-----|-----|-----------|------------|-----------|------------|

|       |     |     | Opt-9-Sem | Opt-9-Cond | Opt-9-Sem | Opt-9-Cond |

|       |     | 32  | 272.76    | 277.13     | 408.88    | 372.02     |

|       | 56  | 64  | 397.35    | 398.82     | 485.91    | 479.04     |

|       | 90  | 128 | 423.49    | 423.66     | 581.04    | 585.81     |

| 4096  |     | 256 | 326.07    | 326.21     | 446.40    | 451.08     |

| -000  |     | 32  | 245.19    | 252.80     | 357.67    | 350.46     |

|       | 112 | 64  | 352.83    | 353.72     | 484.72    | 476.35     |

|       | 112 | 128 | 402.84    | 387.35     | 586.41    | 594.38     |

|       |     | 256 | 220.53    | 201.16     | 315.45    | 319.62     |

|       | 56  | 32  | 317.65    | 333.33     | 469.88    | 497.63     |

|       |     | 64  | 494.51    | 499.41     | 639.82    | 738.00     |

|       | 50  | 128 | 550.83    | 554.76     | 855.15    | 857.87     |

| 8192  |     | 256 | 424.43    | 427.21     | 657.77    | 657.24     |

| 0-0-  | 112 | 32  | 315.18    | 326.49     | 436.02    | 483.08     |

|       |     | 64  | 466.42    | 468.68     | 623.87    | 688.01     |

|       |     | 128 | 585.31    | 549.29     | 905.83    | 909.03     |

|       |     | 256 | 316.91    | 297.33     | 480.62    | 499.98     |

|       | 56  | 32  | 409.05    | 426.83     | 582.79    | 631.27     |

|       |     | 64  | 584.32    | 583.84     | 717.50    | 904.71     |

| 16384 | 50  | 128 | 593.36    | 590.39     | 976.98    | 978.05     |

|       |     | 256 | 456.67    | 455.32     | 750.52    | 754.21     |

|       | 112 | 32  | 414.55    | 429.33     | 534.50    | 627.63     |

|       |     | 64  | 556.36    | 541.68     | 706.58    | 828.90     |

|       |     | 128 | 629.38    | 589.54     | 1034.44   | 1038.15    |

|       |     | 256 | 339.68    | 316.24     | 797.82    | 561.74     |

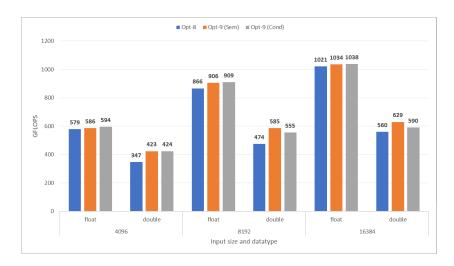

**Fig. 10.** Performance of implementation Opt-9 on the Xeon Platinum when varying N and data type

Fig. 10 summarizes the performances obtained for both versions on the Xeon Platinum (T=112), when varying N and data type. First, it can be seen that both versions of Opt-9 outperform Opt-8. From the synchronization mechanism perspective, no significant performance difference can be appreciated between using semaphores or condition variables. Finally, the improvement achieved with double data type is significantly larger than with float. In particular, performance improves up to 5% and 23% when float and double are used, respectively. The improvement factor is higher with double because idle time is (proportionally) shorter than with float, since operations with the former are more expensive than with the latter.

## 5 Conclusions and Future Work

In this paper, we studied the code developed by [2] and adapted it to run on Intel x86 processors, losing the specificity of the Xeon Phi KNL. To do so, we verified one by one the optimizations proposed by [2], making adjustments to the base code where necessary, and analyzing its performance on two Intel servers under different test scenarios. In addition, a new optimization was proposed to increase the concurrency degree of the parallel algorithm, which was implemented using two different synchronization mechanisms. From the results obtained and their subsequent analysis, the following conclusions can be mentioned:

Opt-1 was discarded because of the absence of MDCDRAM memory on the x86 platforms used. In addition, the vectorization flags were modified to the corresponding SIMD sets.

- Like the Xeon Phi KNL case, all optimizations were beneficial on the two x86 platforms selected. Particularly, the use of SIMD instructions provided the greatest performance improvement.

- The performance improves as N increases, given the higher ratio of compute versus synchronization. Besides, using wider precision data can lead to a more reliable result although at the cost of a significant increase in response time.

- Both versions of Opt-9 outperform Opt-8. From the synchronization mechanism perspective, no significant performance difference can be appreciated between using semaphores or condition variables. In the opposite sense, the improvement achieved with double data type is significantly larger than with float.

- Beyond the reduction in execution time, an indirect benefit of Opt-9 results in no variation of optimal BS. Using Opt-9 the optimal block size is stabilized at BS = 128, regardless of the data type, number of threads, or problem size used. This represents an advantage over previous versions with variable optimal BS since it requires adjustment for each situation.

#### Future work will focus on:

- Proposing new algorithmic optimizations as an inter-round optimization, to remove the synchronization barrier at the end of each round. Then, performing the corresponding tests to evaluate their feasibility.

- Making adjustments to the code to enable its compilation using Intel's new ICX compiler, which incorporates LLVM as backend. This will guarantee long-term support for the code.

- Developing a library to facilitate the inclusion and use of the optimized,

parallel FW algorithm in third-party C/C++ programs.

#### References

- Calderon, S., Rucci, E., Chichizola, F.: Adaptación de algoritmo openmp para computar caminos mínimos en grafos en arquitecturas x86. In: Actas del XXIX Congreso Argentino de Ciencias de la Computación (CACIC 2023). pp. 489–500 (2023)

- Costi, U.: Aceleración del Algoritmo Floyd-Warshall sobre Intel Xeon Phi KNL. Tesina de Licenciatura en Informática, Universidad Nacional de La Plata (2020)

- Floyd, R.W.: Algorithm 97: Shortest path. Commun. ACM 5(6), 345– (Jun 1962). https://doi.org/10.1145/367766.368168

- 4. Han, S.C., Franchetti, F., Püschel, M.: Program generation for the all-pairs shortest path problem. In: Proceedings of the 15th International Conference on Parallel Architectures and Compilation Techniques. p. 222–232. PACT '06, ACM, New York, NY, USA (2006). https://doi.org/10.1145/1152154.1152189

- 5. Han, S., Kang, S.: Optimizing all-pairs shortest-path algorithm using vector instructions. Tech. rep., Carnegie Mellon University, USA (2006)

- 6. Intel Corporation: Thread Affinity Interface, https://www.intel.com/content/www/us/en/develop/documentation/cpp-compiler-developer-guide-and-reference/top/optimization-and-programming/openmp-support/openmp-library-support/thread-affinity-interface.html

- 7. Jalali, S., Noroozi, M.: Determination of the optimal escape routes of underground mine networks in emergency cases. Safety Science 47(8), 1077 1082 (2009). https://doi.org/http://dx.doi.org/10.1016/j.ssci.2009.01.001

- Khan, P., Konar, G., Chakraborty, N.: Modification of floyd-warshall's algorithm for shortest path routing in wireless sensor networks. In: 2014 Annual IEEE India Conference (INDICON). pp. 1–6 (Dec 2014). https://doi.org/10.1109/INDICON. 2014.7030504

- Nakaya, A., Goto, S., Kanehisa, M.: Extraction of correlated gene clusters by multiple graph comparison. Genome Informatics 12, 44–53 (2001)

- Penner, M., Prasanna, V.: Cache-friendly implementations of transitive closure.

In: Proceedings 2001 International Conference on Parallel Architectures and Compilation Techniques. pp. 185–196 (2001). https://doi.org/10.1109/PACT.2001.953299

- Reinders, J., Jeffers, J., Sodani, A.: Intel Xeon Phi Processor High Performance Programming Knights Landing Edition. Morgan Kaufmann Publishers Inc., Boston, MA, USA (2016)

- Rucci, E., De Giusti, A., Naiouf, M.: Blocked All-Pairs Shortest Paths Algorithm on Intel Xeon Phi KNL Processor: A Case Study. In: De Giusti, A.E. (ed.) Computer Science – CACIC 2017. pp. 47–57. Springer Int. Pub., Cham (2018). https://doi. org/10.1007/978-3-319-75214-3\_5

- 13. Schoeneman, F., Zola, J.: Solving all-pairs shortest-paths problem in large graphs using apache spark. In: Proceedings of the 48th International Conference on Parallel Processing. ICPP '19, ACM (2019). https://doi.org/10.1145/3337821.3337852

- 14. Solomonik, E., Buluç, A., Demmel, J.: Minimizing communication in all-pairs shortest paths. In: 2013 IEEE 27th International Symposium on Parallel and Distributed Processing. pp. 548–559. IEEE (2013). https://doi.org/10.1109/IPDPS.2013.111

- Srinivasan, T., Balakrishnan, R., Gangadharan, S., Hayawardh, V.: A scalable parallelization of all-pairs shortest path algorithm for a high performance cluster environment. In: 2007 International Conference on Parallel and Distributed Systems. pp. 1–8 (2007). https://doi.org/10.1109/ICPADS.2007.4447721

- 16. Venkataraman, G., Sahni, S., Mukhopadhyaya, S.: A Blocked All-Pairs Shortest-Paths Algorithm, pp. 419–432. Springer Berlin Heidelberg (2000). https://doi.org/10.1007/3-540-44985-X\_36

- 17. Warshall, S.: A theorem on boolean matrices. J. ACM **9**(1), 11–12 (Jan 1962). https://doi.org/10.1145/321105.321107

- Zhang, L.y., Jian, M., Li, K.p.: A parallel floyd-warshall algorithm based on tbb. In: 2010 2nd IEEE International Conference on Information Management and Engineering. pp. 429–433 (2010). https://doi.org/10.1109/ICIME.2010.5477752