HAGIT ATTIYA, Technion-Israel Institute of Technology, Israel MICHAEL A. BENDER, Stony Brook University, USA MARTIN FARACH-COLTON, New York University, USA ROTEM OSHMAN, Tel-Aviv University, Israel NOA SCHILLER, Tel-Aviv University, Israel

A data structure is called *history independent* if its internal memory representation does not reveal the history of operations applied to it, only its current state. In this paper we study history independence for concurrent data structures, and establish foundational possibility and impossibility results. We show that a large class of concurrent objects cannot be implemented from smaller base objects in a manner that is both wait-free and history independence, then at least one object in the class, multi-valued single-reader single-writer registers, *can* be implemented from smaller base objects.

On the other hand, using large base objects, we give a strong possibility result in the form of a universal construction: an object with *s* possible states can be implemented in a wait-free, history-independent manner from compare-and-swap base objects that each have  $O(s + 2^n)$  possible memory states, where *n* is the number of processes in the system.

#### **1 INTRODUCTION**

A data structure is said to be *history independent* (HI) if its internal representation reveals nothing about the history of operations that have been applied to it, beyond the current state of the data structure. For example, if a set is history independent, its internal representation may (and must, for correctness) reveal the elements that are currently in the set, but it must not reveal elements that were previously inserted and then removed.

The notion of history independence was introduced by Micciancio [33], who showed how to build a search tree with a history-independent structure. Naor and Teague [36] formalized two now-classical notions of history independence: a data structure is *weakly history independent* (WHI) if it leaks no information to an observer who sees the memory representation once, and it is *strongly history independent* (SHI) if it leaks no information even to an observer who sees the memory representation at multiple points in the execution. These notions differ significantly: for example, a set where each item inserted is stored at a freshly-chosen random location in memory may be weakly HI but not strongly HI, because if an item is inserted, removed, and then inserted again, it may be placed in different locations each time it is inserted; an observer who sees the memory after each of the two insertions would know that the item was removed and re-inserted.

History independence has been extensively studied in sequential data structures (see below), and the foundational algorithmic work on history independence has found its way into systems like voting machines and storage. However, history independence was studied only peripherally in *concurrent* data structures. This paper initiates a thorough study of history-independent concurrent data structures, and establishes fundamental possibility and impossibility results.

We focus on a concurrent notion of strong history independence for deterministic data structures, and characterize the boundaries of what can be achieved. Defining history independence for concurrent objects is non-trivial, because the sequential definition of history independence allows the observer to examine the memory only *in-between* operations—that is, in a quiescent state—while

Authors' addresses: Hagit Attiya, Technion-Israel Institute of Technology, Israel, Haifa, hagit@cs.technion.ac.il; Michael A. Bender, Stony Brook University, USA, bender@cs.stonybrook.edu; Martin Farach-Colton, New York University, USA, martin@farach-colton.com; Rotem Oshman, Tel-Aviv University, Israel, roshman@tau.ac.il; Noa Schiller, Tel-Aviv University, Israel, noaschiller@mail.tau.ac.il.

a concurrent implementation might *never be* in a quiescent state. One of our main questions is whether it should be permissible for the observer to open the "black box" of a single operation and inspect the memory when the system is not quiescent, and what are the implications of this choice in terms of what can be implemented concurrently in a history independent manner.

We begin by asking whether a concurrent object *A* can be implemented out of "smaller" base objects of type *B* in a manner that is history independent; here, "smaller" means that *B* has fewer states than A. Our motivating example is the famous implementation of a multi-valued single-writer single-reader wait-free register from Boolean registers [46]. We observe that this implementation is not history independent even in the weakest sense (see Section 4), and in fact, there is a good reason for this: we prove that for a fairly general class of objects, which includes read/write registers, there is no wait-free history independent implementation out of smaller base objects, regardless of the type of the smaller objects. This result holds even if the observer can only inspect the memory when there are no state-changing operations pending (but read operations may be ongoing). If the observer can inspect the memory at any point (including while state-changing operations are ongoing), then even a lock-free implementation is impossible. On the other hand, for multi-valued single-writer single-reader registers, there is a wait-free history independent implementation from binary registers, if we restrict the observer's inspections to points where the system is completely quiescent. While our results are stated for deterministic algorithms, our impossibility result also applies to randomized implementations of reversible objects, which are objects where every state can be reached from every other state (see Section 2).

Since it is impossible to implement objects out of smaller objects in a wait-free, history independent manner (except possibly in the weakest, quiescent sense), we turn to concurrent implementations where the base object *B* is large enough to store the full state of the abstract object *A* that we want to implement. For this regime we give a strong possibility result, in the form of a *universal implementation* from compare-and-swap (CAS) objects: we show that any object *A* can be implemented in a wait-free, history independent manner from sufficiently-large CAS objects. Our implementation reveals nothing about past states of the object or operations that completed prior to the invocation of any currently-pending operations; and when no state-changing operation is pending, the state of the memory reflects only the current abstract state of the object. Our implementation uses an extended version of an LL/SC object, inspired by [30, 31], which we implement from atomic CAS.

Additional Related Work. Hartline et al. [24, 25] showed that a data structure with a stronglyconnected state graph is strong HI if and only if each state of the state graph has a unique *canonical* representation. We rely on a similar characterization for both possibility and impossibility results.

There is a large literature on figuring out which data structures can be made history independent without an asymptotic slow down. These results include fast HI constructions for cuckoo hash tables [35], linear-probing hash tables [15, 23], other hash tables [15, 36], trees [1, 33], memory allocators [23, 36], write-once memories [34], priority queues [16], union-find data structures [36], external-memory dictionaries [12, 20–22], file systems [8, 10, 11, 40], cache-oblivious dictionaries [12], order-maintenance data structures [15], packed-memory arrays/list-labeling data structures [12, 13], and geometric data structures [45]. Given the strong connection between history independence and unique representability [24, 25], some earlier data structures can be made history independent, including hashing variants [2, 17], skip lists [38], treaps [5], and other less well-known deterministic data structures with canonical representations [3, 4, 39, 43, 44].

The foundational algorithmic work on history independence has found its way into systems. There are now voting machines [14], file systems [8, 9, 11], databases [10, 37, 41], and other storage systems [18] that support history independence as an essential feature.

To the best of our knowledge, the only prior work to consider history independence in concurrent implementations is by Shun and Blelloch [42]. They implement a concurrent hash table, based on a sequential SHI hash table [15, 36], in which only operations of the same type can be executed concurrently. The implementation of [42] guarantees that if there are no ongoing insert or delete operations, each state of the hash table has a unique canonical representation in memory. This work does not provide a formal definition of history independence for concurrent implementations, and does not support concurrent operations of different types.

Our universal implementation draws inspiration from prior universal implementations, using CAS [26], hardware LL/SC [28], and consensus objects [27]. These implementations are not history independent: the implementation in [27] explicitly keeps tracks of all the operations that have ever been invoked, while the implementations in [26, 28] store information that depends on the sequence of applied operations. Moreover, they use dynamic memory, and allocate new memory every time the state of the object is modified, which risks revealing information about the history of operations. While there is work on sequential history-independent memory allocation (e.g., [36]), to our knowledge, no *concurrent* history-independent memory allocator is known.

Fatourou and Kallimanis [19] give a universal implementation from hardware LL/SC, where the full state of the object, along with additional information, is stored in a single memory cell. Our history-independent universal implementation bears some similarity to [19], but their implementation keeps information about completed operations, such as their responses, and is therefore not history independent. Clearing this type of information from memory so as not to reveal completed operations is non-trivial, and we address this in our implementation.

#### 2 PRELIMINARIES

Abstract Objects. An abstract object is defined by a set of states and a set of operations, each of which may change the state of the object and return a response. Formally, an abstract object O is a tuple  $(Q, q_0, O, R, \Delta)$ , where Q is the object's set of states,  $q_0 \in Q$  is a designated initial state, O is the object's set of operations, R is the object's set of responses and  $\Delta : Q \times O \rightarrow Q \times R$  is the function specifying the object behavior, known as the *sequential specification* of the object. We assume that the abstract object is deterministic, i.e., the function  $\Delta$  is deterministic. We also assume that all states in Q are reachable from the initial state  $q_0$ .

A sequential implementation specifies how each operation should be concretely implemented in memory. The object's abstract state is represented in memory using some *memory representation*, and the implementation specifies how each operation should modify this memory representation when it is applied. We note that in general, a single state  $q \in Q$  may have multiple possible memory representations associated with it; for example, if we implement a set (i.e., a dictionary) using a balanced search tree, then the abstract state of the object consists of the contents of the set, but the layout in memory may also depend on the order of insertions, etc.

*Sequential History Independence.* A *history-independent* implementation is one where the memory representation of the object reveals only its current abstract state, and not the sequence of operations that have led to that state.

**Definition 1** (Weak History Independence (WHI) [36]). A sequential implementation of an object is weakly history independent if any pair of operation sequences that take the object from the initial state to the same state, induce the same distribution on the memory representation.

Intuitively, WHI assumes the adversary examines the memory representation only once. If an adversary can gain access to the memory representation multiple times along the sequence of operations, assuming WHI is not enough to conceal the sequence of operations. Hence, a stronger

definition is required, which considers an adversary that may access the memory representation at multiple points during the execution.

**Definition 2** (Strong History Independence (SHI) [36]). A sequential implementation of an object is strongly history independent if for any pair of operation sequences  $o_1^1, \ldots, o_{l_1}^1$  and  $o_1^2, \ldots, o_{l_2}^2$ , and two lists of points  $P_1 = \{i_1^1, \ldots, i_\ell^1\}$  and  $P_2 = \{i_1^2, \ldots, i_\ell^2\}$ , such that for all  $b \in \{1, 2\}$  and  $1 \le j \le \ell$  we have that  $1 \le i_j^b \le l_b$  and the two operations' prefixes  $o_1^1, \ldots, o_{l_j}^1$  and  $o_1^2, \ldots, o_{l_j}^2$  take the object from the initial state to the same state, then the distributions of the memory representations at the points of  $P_1$  and the corresponding points of  $P_2$  are identical.

When deterministic implementations are concerned, both versions of history independence weak and strong history independence—converge, since in the absence of randomness it does not matter whether the adversary examines the memory only at one point, or whether it may examine the memory at multiple points in the execution.

One way to achieve history independence is to ensure that whenever the object is the same abstract state, the memory representation is the same. Implementations that have this property are called *canonical*: every abstract state  $q \in Q$  corresponds to exactly one memory representation, can(q), which we call its *canonical memory representation*, and every sequence of operations that leads the object to state q must leave the memory in state can(q). A canonical sequential implementation is, by definition, strongly history independent, but when randomization is allowed, not every strongly history-independent implementation must be canonical. Nevertheless, it was shown in [24, 25] that for *reversible* objects, which are objects where every state is reachable from every other state,<sup>1</sup> the use of randomization is somewhat limited: [24, 25] show that strong history independence requires that the implementation must fix a canonical representation when the object is initialized, meaning the randomness cannot affect the memory representation except to fix the mapping from states to their canonical representations at the very beginning of the execution.

As we said above, for deterministic implementations, weak and strong history independence coincide; both require the implementation to be canonical:

## **Proposition 3.** For deterministic sequential implementations, WHI and SHI are equivalent to requiring that a unique canonical memory representation is determined for each state at initialization.

Since we consider only deterministic implementations in this paper, we do not distinguish between SHI and WHI, and refer to them simply as *HI*.

The Asynchronous Shared-Memory Model. We use the standard model in which *n* processes,  $p_1, \ldots, p_n$ , communicate through shared *base objects*. An implementation of an abstract object *O* specifies for each process a program for every operation in *O*. When receiving an *invocation* of an operation  $o \in O$ , process  $p_i$  takes *steps* according to this program. Each step by process  $p_i$  consists of some local computation and a single primitive operation on a *base object*. The process possibly changes its local state after a step and possibly returns a *response* to a higher-level operation.

A configuration *C* specifies the state of every process and the state of every base object. The *initial* configuration is denoted by  $C_0$ , and we assume that it is unique. An *execution*  $\alpha$  is an alternating sequence of configurations and steps. An execution can be finite or infinite. Given two executions  $\alpha_1, \alpha_2$ , where  $\alpha_1$  ends at configuration *C* and  $\alpha_2$  begins at configuration *C*, we denote by  $\alpha_1\alpha_2$  the concatenation of the two executions, and we say that  $\alpha_1\alpha_2$  extends execution  $\alpha_1$ .

The *memory representation* of a configuration C, denoted mem(C), is a vector specifying the state of each base object; note that this does not include local private variables held by each process, only

<sup>&</sup>lt;sup>1</sup>For example, a register is reversible, while an increment-only counter is not.

the shared memory. Formally, if there are *m* base objects with state spaces  $Q_1, \ldots, Q_m$  respectively, then mem(*C*) is a vector in  $Q_1 \times \ldots \times Q_m$ , and we denote by mem(*C*)[*i*] the state of the *i*-th base object. For a finite execution  $\alpha$ , we let mem( $\alpha$ ) denote the memory representation in the last configuration in the execution  $\alpha$ .

In this paper we frequently make use of two types of base objects: the first is a simple *read/write register*, and the second is a *compare-and-swap* (*CAS*) object. A CAS object *X* supports the operation CAS(X, old, new), which checks if the current value of the object is *old*, and if so, replaces it by *new* and returns *true*; otherwise, the operation leaves the value unchanged, and returns *false*. We assume that the CAS object supports standard read and write operations. For both read/write registers and CAS objects, the *state* of the object is simply the value stored in it.

An execution  $\alpha$  induces a *history*  $H(\alpha)$ , consisting only of the invocations and responses of higher-level operations. An invocation *matches* a response if they both belong to the same operation. An operation *completes* in *H* if *H* includes both the invocation and response of the operation; if *H* includes the invocation of an operation, but no matching response, then the operation is *pending*. If  $\alpha$  ends with a configuration *C*, and there is no pending operation in  $\alpha$ , then *C* is *quiescent*.

A history *H* is *sequential* if every invocation is immediately followed by a matching response. For a sequential history *H*, let state(*H*)  $\in Q$  be the state reached by applying the sequence of operations implied by *H* from the initial state according to  $\Delta$ . This state is well-defined, since the sequence of operations is well-defined in a sequential history.

*Linearizability.* A *completion* of history *H* is a history *H'* whose prefix is identical to *H*, and whose suffix includes zero or more responses of pending operations in *H*. Let comp(H) be the set of all of *H*'s completions. A sequential history *H'* is a *linearization* of an execution  $\alpha$  that arises from an implementation of an abstract object *O* if:

- H' is a permutation of a history in comp $(H(\alpha))$ ,

- H' matches the sequential specification of O, and

- *H'* respects the real-time order of non-overlapping operations in  $H(\alpha)$ .

An execution  $\alpha$  is *linearizable* [29] if it has a linearization, and an implementation of an abstract object is linearizable if all of its executions are linearizable. A *linearization function h* maps an execution  $\alpha$  to a sequential history  $h(\alpha)$  that is a linearization of  $\alpha$ .

*Progress Conditions.* An implementation is *lock-free* if there is a pending operation, then some operation returns in a finite number of steps. An implementation is *wait-free* if there is a pending operation by process  $p_i$ , then this operation returns in a finite number of steps by process  $p_i$ .

#### **3 HISTORY INDEPENDENCE FOR CONCURRENT OBJECTS**

As we noted in Section 1, when defining history independence for concurrent objects, we must grapple with the fact that a concurrent system might never be in a quiescent state. In Section 5.2 we prove that if we allow the internal memory to be observed at *any* point in the execution, then there is a strong impossibility result ruling out even lock-free implementations of a wide class of objects. This motivates us to consider weaker but more feasible definitions, where the observer may only examine the internal memory at certain points in the execution.

The following definition provides a general framework for defining a notion of history independence that is parameterized by the points where the observer is allowed to access the internal memory; these points are specified through a set of finite executions, and the observer may access the memory representation only at the end of each such finite execution. Informally, the definition requires that at any two points where the observer is allowed to examine the internal memory, if the object is in the same state, then the memory representation must be the same; we use a linearization function to determine what the "state" of the object is at a given point.

**Definition 4.** Consider an implementation of an abstract object with a linearization function h, and let E be a set of finite executions that arise from the implementation. The implementation is HI with respect to E if for any pair of executions  $\alpha, \alpha' \in E$  such that  $state(h(\alpha)) = state(h(\alpha'))$ , then  $mem(\alpha) = mem(\alpha')$ . An implementation of an abstract object is HI with respect to E, if it is HI with respect to E for some linearization function h.

To prove that an implementation satisfies Definition 4, it suffices to prove that for every finite execution  $\alpha$  in the set *E*, if *E* ends with the object in state *q* according to the linearization function *h*, then the memory is in the canonical memory representation can(q) for state *q*.

The strongest form of history independence that one might ask for is one that allows the observer to examine the memory at any point in the execution:

**Definition 5.** An implementation of an abstract object is perfect HI, if the implementation is HI with respect to the set containing all finite executions of the implementation.

Perfect HI imposes a very strong requirement on the implementation: intuitively, any two adjacent high-level states must have adjacent memory representations. Formally, we say that the *distance* between two memory representations  $mem_1$ ,  $mem_2$  is *d* if there are exactly *d* indices  $i \in [m]$  where  $mem_1[i] \neq mem_2[i]$  (recall that *m* is the number of base objects used in the implementation). The following proposition holds for *obstruction-freedom*,<sup>2</sup> a progress guarantee even weaker than lock-freedom and wait-freedom.

**Proposition 6.** In any obstruction-free perfect HI implementation of an abstract object with state space Q, for any  $q_1 \neq q_2 \in Q$  such that  $q_2$  is reachable from  $q_1$  in a single operation, the distance between  $can(q_1)$  and  $can(q_2)$  is at most 1.

PROOF. Assume that  $can(q_1)$  and  $can(q_2)$  are at distance at least 2. Consider a sequential execution  $\alpha$  that ends in a quiescent configuration such that only one process  $p_i$  takes steps in  $\alpha$  and state $(H(\alpha)) = q_1$ . Since the implementation is perfect HI,  $mem(\alpha) = can(q_1)$ . Let  $\beta = \alpha \alpha'$  be an extension of  $\alpha$ , such that  $\alpha'$  consists of a single operation by process  $p_i$  and state $(H(\alpha)) = q_2$ . This extension exists since  $q_2$  is reachable from  $q_1$  by a single operation. Since the implementation is perfect HI,  $mem(\beta) = can(q_2)$ . This means that  $p_i$  changes the state of two base objects in two separate steps in  $\alpha'$ , since  $can(q_1)$  and  $can(q_2)$  are at distance at least 2. Let  $\beta'$  be the shortest prefix of  $\beta$  that includes the first step that changes the state of a base object during the operation executed in  $\alpha'$ . Then,  $mem(\beta') \neq can(q_1)$  and also  $mem(\beta') \neq can(q_2)$ . However, for every linearization function h, state $(h(\beta')) = q_1$  or state $(h(\beta')) = q_2$ , in contradiction.

Proposition 14 (Section 5.2) shows that a large class of objects cannot meet the requirement above, and therefore, no obstruction-free implementation can be perfect HI. This motivates us to consider weaker definitions, where the observer may only observe the memory at points that are "somewhat quiescent", or fully quiescent.

We say that an operation  $o \in O$  is *state-changing* if there exist states  $q \neq q'$  such that o causes the object to transition from state q to q'. An operation is *read-only* if it is not state-changing. A configuration *C* is *state-quiescent* if there are no pending state-changing operations in *C*. Note that a quiescent configuration is also state-quiescent.

**Definition 7.** An implementation of an abstract object is state-quiescent HI if the implementation is HI with respect to all finite executions ending with a state-quiescent configuration.

<sup>&</sup>lt;sup>2</sup>An implementation is *obstruction-free* if an operation by process  $p_i$  returns in a finite number of steps by  $p_i$ , if  $p_i$  runs solo.

Fig. 1. Illustration of the three HI definitions. Perfect HI allows the observer to examine the memory at any point; state-quiescent HI allows examination only when there is no state-changing operation pending (points 1, 2 and 4); while quiescent HI allows examination only when the configuration is quiescent (points 1 and 4).

The final definition is the weakest one that we consider, and it allows the observer to examine the memory only when the configuration is fully quiescent:

**Definition 8.** An implementation of an abstract object is quiescent HI, if the implementation is HI with respect to all finite executions ending with a quiescent configuration.

Figure 1 depicts the definitions, on an execution of a register implementation, highlighting several different points where an observer is or is not allowed to examine the memory according to each definition. Clearly, if an implementation of an abstract object with linearization function h is HI with respect to an execution set E, then it is also HI with respect to any execution set  $E' \subseteq E$ . Since the respective sets of executions are contained in each other, this means that perfect HI implies state-quiescent HI, which in turn implies quiescent HI.

#### 4 MOTIVATING EXAMPLE: MULTI-VALUED REGISTER FROM BINARY REGISTERS

To better understand the notion of history independence, and the challenges in achieving it, consider the problem of implementing a *single-writer single-reader (SWSR) K*-valued register, for  $K \ge 3$ , from *binary registers*, i.e., registers whose value is either 0 or 1.

Algorithm 1 presents Vidyasankar's wait-free implementation of a SWSR *K*-valued register from binary registers [46]. The algorithm is for multiple readers, but we assume a single reader here.

The value of the register is represented by a binary array A of size K, and intuitively, the register's value at any given moment is the smallest index  $i \in [K]$  such that A[i] = 1.<sup>3</sup> In a READ operation, the reader r scans up to find the smallest index  $i \in [K]$  such that A[i] = 1, and then scans down from i and returns the smallest index  $j \leq i$  such that when A[j] was read, its value was 1. (If the reader executes solo, we will have i = j, but if there is a concurrent WRITE, we may have j < i.) In a WRITE(v) operation, the writer w writes 1 to A[v], then writes 0 to all indices i < v, starting from index v - 1 and proceeding down to index 1.

Since a WRITE(v) operation does not clear values larger than v, the state of the array A leaks information about past values written to the register: e.g., if K = 3 and there is a WRITE(2) operation followed by WRITE(1), we will have A = [1, 1, 0], whereas if we have only a WRITE(1), the state will be A = [1, 0, 0]. This will happen even in sequential executions, so this implementation is not history independent even in the minimal sense: it does not satisfy the sequential definition of history independence, even if we consider only sequential executions.

One might hope that this can be fixed by having a WRITE(v) operation clear the entire array A, except for A[v] = 1, but this would break the wait-freedom of the implementation: if the writer zeroes out all positions in the array except one, the reader might never be able to find an array position *i* where A[i] = 1, and it might not find a value that it can return. In fact, the impossibility

<sup>&</sup>lt;sup>3</sup>This is true in the sense that a READ operation that does not overlap with a WRITE will return the smallest index  $i \in [K]$  such that A[i] = 1; for a READ that does overlap with a WRITE, the picture is much more complicated [46].

result that we prove in the next section (Theorem 17) rules out any wait-free implementation that is history-independent, even if we examine the memory only when no WRITE operation is pending.

Nevertheless, if we are willing to settle for lockfreedom instead of wait-freedom, then the approach of clearing out the array after a WRITE can be made to work. We can modify Algorithm 1 by having a WRITE(v) operation first clear values down from v - 1 to 1 (as in the original implementation), and then clear values up from v + 1 to K (which it would not do in the original implementation). As a result, when there is no WRITE operation pending, the register has a unique representation: if its value is v, then the array A is 0 everywhere except at v, where we have A[v] = 1. Since the reader does not write to memory, this implies that the algorithm is statequiescent HI. The READ operation is nearly identical to Algorithm 1, except that, as we said above, if a READ operation overlaps with multiple WRITES, it may never find a 1 in the array, and thus it may never find a value to return. Thus, the reader repeatedly tries to execute the READ operation, until it finds a value to return. We call each such attempt a TRYREAD (Algorithm 3), and it returns  $\perp$  to indicate a failed attempt to find a 1 in A. The code of the modified algorithm appears in Algorithm 2. While the WRITE operation remains wait-free, the READ operation is only lock-free, and it is only guaranteed to terminate if it eventually runs by itself.

*Proof of Algorithm 2.* We define a linearization function for Algorithm 2, the same way as it is done in the proof of Algorithm 1 (see [7, Section 10.2.1]).

Let  $\alpha$  be an execution of Algorithm 2. We say that a low-level read of A[v] in  $\alpha$  reads from a low-level write to A[v] if this is the latest write to A[v] that precedes this read. We say that a high-level READ operation R in  $H(\alpha)$  reads from WRITE operation W, if R returns the value v, and W is the WRITE operation containing the low-level write to A[v] that R's last low-level read of A[v] reads from. Assume there is an initial logical WRITE $(v_0)$  operation  $W_0$ of the initial value, and any READ that returns the initial value reads from  $W_0$ .

We linearize the operations in execution  $\alpha$  according to the *reads from* order. Since there is a single writer *w*, the order of WRITE operations is well-

| Algorithm 1 Wait-free SWSR multi-valued reg- |

|----------------------------------------------|

| ister from binary registers [46]             |

| $A[1K]$ , all entries are initially 0, except $A[v_0]$ , where $v_0$ is the initial value |

|-------------------------------------------------------------------------------------------|

| READ(): code for the reader $r$                                                           |

| 1: $j \leftarrow 1$                                                                       |

| 2: while $A[j] = 0$ do $j \leftarrow j + 1$                                               |

| 3: $val \leftarrow j$                                                                     |

| 4: <b>for</b> $j = val - 1 \dots 1$ <b>do</b>                                             |

| 5: <b>if</b> $A[j] = 1$ <b>then</b> $val \leftarrow j$                                    |

| 6: return val                                                                             |

| WRITE( <i>v</i> ): code for the write <i>w</i>                                            |

| 7: $A[v] \leftarrow 1$                                                                    |

8: for  $j = v - 1 \dots 1$  do  $A[j] \leftarrow 0$

Algorithm 2 Lock-free state-quiescent HI SWSR multi-valued register from binary registers

A[1...K], all entries are initially 0, except  $A[v_0]$ , where  $v_0$  is the initial value

READ(): code for the reader r

- 1:  $val \leftarrow \bot$

- 2: while  $val = \perp do$

- 3:  $val \leftarrow \text{TryRead}()$

4: return val

WRITE(v): code for the write w

- 5:  $A[v] \leftarrow 1$ 6: **for**  $j = v - 1, \dots, 1$  **do**  $A[j] \leftarrow 0$

- 7: for  $j = v + 1 \dots K$  do  $A[j] \leftarrow 0$

| Algorithm 3 Read wit                | h failure indication                |

|-------------------------------------|-------------------------------------|

| TRYREAD(): code for                 | the reader <i>r</i>                 |

| 1: <b>for</b> $j = 1 K$ <b>do</b>   |                                     |

| 2: <b>if</b> $A[j] = 1$ <b>then</b> | 1                                   |

| 3: $val \leftarrow j$               |                                     |

| 4: <b>for</b> $j' = val$            | – 1 1 <b>do</b>                     |

| 5: <b>if</b> $A[j']$                | = 1 <b>then</b> $val \leftarrow j'$ |

| 6: return val                       |                                     |

| 7: return ⊥                         |                                     |

|                                     |                                     |

defined. The READ operations are also ordered by the order they occur in  $\alpha$ , which again is welldefined since there is a single reader *r*. As for the ordering between READS and WRITES, immediately after each WRITE operation we place all the READ operations that read from it, ordered by the order in which they were invoked.

The next theorem is proved in Appendix A.

# THEOREM 9. Algorithm 2 is a linearizable lock-free state-quiescent HI SWSR multi-valued register from binary registers.

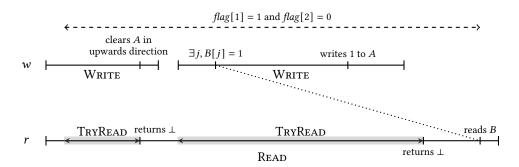

There is another way to relax our requirements and circumvent the impossibility result: we could settle for *quiescent* history independence, where the adversary is not allowed to inspect the internal representation except when the system is fully quiescent. Algorithm 4 is a SWSR multi-valued register from binary registers, that is both wait-free and quiescent HI. Our algorithm employs the following simple principle: the reader announces its presence to the writer whenever it begins a read operation. The writer, if it sees that the reader might not find a value to return, *helps* it by writing a value that the reader is allowed to return, in an area of shared memory dedicated to this purpose. We must carefully manage the footprints left in memory by both the reader and the writer, and ensure that when all operations complete, the memory is left in a canonical representation, but at the same time, that the reader is never left hanging without a value that it may return.

In more details, in addition to the array A, which has the same functionality as in Algorithm 2, there is an additional array B of size K. In a READ operation, first, the reader sets flag[1] to 1, to announce itself to the writer. Then, the reader tries to read A twice, and if it succeeds in finding an index equal to 1 in A, it returns a value as done in Algorithm 2. Otherwise, the reader reads B and returns an index in B that is equal to 1 (we claim that it will always find such an index). Before returning, the reader sets flag[2] to 1 and then clears B by writing 0 to all the indices in B. In addition, it writes 0 to flag[1] and then to flag[2], and returns the value read either from A or from B (whichever one succeeded).

In a WRITE operation, the writer reads the entire array *B* to check if there is any non-zero cell there. If *B* contains only zeroes, and the writer identifies a concurrent READ operation by observing that flag[1] = 1, then it writes 1 to B[last-val], where last-val is the last value written to the register (there is only one writer and it retains the last value it wrote before the current one). After the writer writes to *B*, it reads flag[2] and then flag[1], and if it reads flag[2] = 1 or flag[1] = 0, the writer clears the *B* array by writing 0 to B[last-val]. These flag values indicate that either there is no pending READ operation, or the concurrent READ operation is done reading *B*. This ensures that *B* is cleared by either the writer, or by a concurrent READ operation, and therefore, all cells in *B* are equal to zero when in a quiescent configuration.

Following this interaction with the array *B*, the writer proceeds in the same manner as in Algorithm 2, writing 1 to location A[v], then clearing *A* downwards from v - 1 to 1, and finally clearing *A* upwards from v + 1 to *K*.

By having the writer first write to *B* (if it observes a concurrent reader) and then to *A*, we ensure that if the reader fails twice to find a 1 in *A*, then it is guaranteed that in-between its two scans of *A*, the writer has written to *A* in at least two separate WRITE operations; but the writer must have "seen" the reader by the time that it wrote to *A* in its second WRITE operation (since the reader immediately sets *flag*[1] = 1 when it begins), and at this point is guaranteed to help the reader by setting a cell in *B* to 1.

We also prove (in Proposition 19) that it is essential for the reader to write to shared memory, otherwise it is impossible to obtain even a quiescent HI wait-free implementation.

*Proof of Algorithm 4.* The next two lemmas (proved in Appendix B) are used to show that Algorithm 4 is linearizable. The next lemma proves that a READ operation returns a valid value. It is proved by showing that if two TRYREAD return  $\perp$  in a READ operation, then there is a WRITE operation,

Algorithm 4 Wait-free quiescent HI SWSR multi-valued register from binary registers

A[1...K], all entries are initially 0, except  $A[v_0]$ , where  $v_0$  is the initial value B[1...K], all entries are initially 0 flag[1, 2], both entries are initially 0 local *last-val* at the writer *w*, initially  $v_0$

```

READ(): code for the reader r

WRITE(v): code for the write w

1: flag[1] \leftarrow 1

11: if \forall 1 \le j \le K, B[j] = 0 then

2: for it = 1, 2 do

if flag[1] = 1 then

12:

3:

val \leftarrow TRYREAD()

B[last-val] \leftarrow 1

13:

if val \neq \bot then goto Line 7

if flag[2] = 1 or flag[1] = 0 then

4:

14:

B[last-val] \leftarrow 0

15.

5: for j = 1 ... K do

if B[j] = 1 then val \leftarrow j

16: A[v] \leftarrow 1

6:

17: for j = v - 1 \dots 1 do A[j] \leftarrow 0

7: flag[2] \leftarrow 1

8: for j = 1 \dots K do B[j] \leftarrow 0

18: for j = v + 1 \dots K do A[j] \leftarrow 0

19: last-val \leftarrow v

9: flag[1] \leftarrow 0; flag[2] \leftarrow 0

10: return val

```

which overlaps the second TRYREAD, which, if *B* has no index equal to 1, writes to *B* before *R* starts reading *B*.

**Lemma 10.** If a READ operation R reaches Line 7, then val  $\neq \perp$ .

In the next lemma we show that if the reader returns a value read from B, it was written by an overlapping WRITE operation

**Lemma 11.** Consider a read of 1 from B[j],  $1 \le j \le K$ , in Line 6 by READ operation R and let W be the WRITE operation that writes this value of 1 to B[j] that R reads, then W overlaps R.

A READ operation *R* reads *A* if *R* performs a successful TRYREAD in Line 3 that returns a non- $\perp$  value, and *R* reads *B* if *R* reads 1 from *B*[*j*] in Line 6. If *R* reads *A*, it reads *A* from WRITE operation *W*, if *R* returns *v* and *W* contains the low-level write to *A*[*v*] that *R*'s last low-level read of *A*[*v*] reads from. If *R* reads *B*, it reads *B* from WRITE operation *W*, if *R* returns *v* and *W* contains the low-level write to *A*[*v*] that *R*'s last low-level read of *A*[*v*] reads from. If *R* reads *B*, it reads *B* from WRITE operation *W*, if *R* returns *v* and *W* contains the low-level write to *B*[*v*] that *R*'s low-level read of *B*[*v*] reads from.

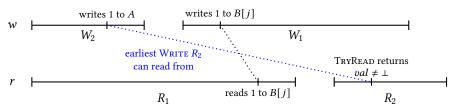

Construct a linearization H of  $\alpha$  similarly to the one constructed for Algorithm 2. Consider the READ operations in the order they occur in  $\alpha$ , this order is well-defined since there is a single reader r. For every READ operation R in  $H(\alpha)$  that reads A, let W be the WRITE operation R reads A from. R is placed immediately after W in H. For every READ operation R in  $H(\alpha)$  that reads B, let  $W_1$  be the WRITE operation R reads B from and  $W_2$  the WRITE operation that precedes  $W_1$  in  $\alpha$ , i.e., the last WRITE operation that returns before  $W_1$  starts. R is placed before  $W_1$  and immediately after  $W_2$  in H. Note that the read operations that are placed after a write operation W are ordered by the order in which they were invoked.

Algorithm 4 is clearly wait-free. History independence (proved in Appendix B) follows by showing that if the writer writes 1 to an index in *B* in a WRITE operation, then this write is overwritten either by the writer or by an overlapping READ operation. This implies that in a quiescent configuration all entries in *B* are equal to 0. We next argue linearizability.

THEOREM 12. Algorithm 4 is a linearizable wait-free quiescent HI SWSR multi-valued register from binary registers.

PROOF OF LINEARIZABILTY. By construction, H is in the sequential specification of the register and by Lemma 10, it includes all completed operations in  $H(\alpha)$ . It is left to show that the linearization respects the real-time order of non-overlapping operations. The order between two WRITE

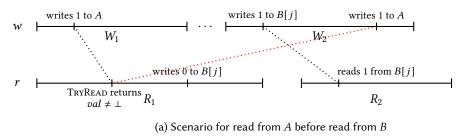

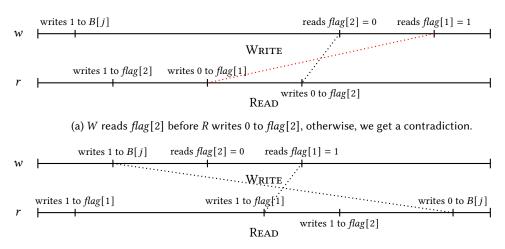

(b) Scenario for read from B before read from A

Fig. 2. Illustrating the proof of Theorem 12

operations respects the real-time order by the construction of *H*, and a READ operation cannot be placed after a WRITE operation that follows it, as a reader cannot read from the future.

The primitive read and write operations on array *A* follow exactly Algorithm 2. Additionally, the projection of *H* that includes all WRITE operations and only READ operations that read *A*, is built in the same manner as a linearization of an execution of Algorithm 2. Therefore, the order of the WRITE operations and READ operations that read *A* respects the real-time order among themselves. Next, we consider the order between two operations, where one of the operations is a READ operation that reads *B*.

**Write before read:** Consider a READ operation *R* that reads *B*. By Lemma 11, *R* reads *B* from WRITE operation  $W_1$  that overlaps *R*, and by the construction of *H*, if *R* is placed between  $W_1$  and  $W_2$ , the WRITE operation that precedes  $W_1$ . Thus, *R* is placed after any WRITE operation that precedes it in  $\alpha$ .

**Read before read:** assume a READ operation  $R_1$  returns before a READ operation  $R_2$  begins, but  $R_2$  is placed before  $R_1$  in the linearization. There are three cases:

(1) both  $R_1$  and  $R_2$  read B: Let  $W_1$  be the WRITE operation  $R_1$  reads B from and let  $W_2$  be the WRITE operation  $R_2$  reads B from. Since  $R_2$  is placed before  $R_1$  in the linearization,  $W_2$  precedes  $W_1$  in  $\alpha$ . By Lemma 11,  $W_1$  overlaps  $R_1$  and  $W_2$  overlaps  $R_2$ . This implies that  $W_1$ , which begins after  $W_2$  returns, begins before  $R_1$  returns, but this contradicts that  $W_2$  overlaps  $R_2$ .

(2)  $R_1$  reads *A* and  $R_2$  reads *B*: Let  $W_2$  be the WRITE operation  $R_2$  reads *B* from (Figure 2a).  $W_2$  writes 1 to B[j] in Line 13 after  $R_1$  writes 0 to B[j] in Line 6. Thus,  $W_2$  first writes to *A* after  $R_1$  finishes reading *A*, and  $R_1$  reads *A* from WRITE operation  $W_1$  that precedes  $W_2$  in  $\alpha$ . By the construction of *H*,  $R_2$  is placed between  $W_2$  and the previous WRITE operation  $W_3$  that directly precedes  $W_2$ . If  $W_1 = W_3$ , then by the construction of *H*,  $R_1$  is placed before  $R_2$  in *H*. Otherwise,  $W_1$ precedes  $W_3$  and this also implies that  $R_1$  is placed before  $R_2$  in *H*.

(3)  $R_1$  reads B and  $R_2$  reads A: Let  $W_1$  be the WRITE operation  $R_1$  reads B from (Figure 2b). By Lemma 11,  $W_1$  overlaps  $R_1$ . Let  $W_2$  be the WRITE operation that directly precedes  $W_1$ , then  $R_1$  is placed between  $W_1$  and  $W_2$ . Since  $W_1$  starts before  $R_2$  starts, the earliest WRITE operation  $R_2$  can read A from is  $W_2$ , that is,  $R_2$  reads A from  $W_2$  or from WRITE operation that follows  $W_2$  in  $\alpha$ . By the construction of H,  $R_1$  is placed before  $R_2$ .

#### 5 HISTORY INDEPENDENT IMPLEMENTATIONS FROM SMALLER BASE OBJECTS

In this section, we show that for a large class of objects, a reasonably strong notion of history independence—*state-quiescent history independence* (Definition 7)—cannot be achieved from smaller base objects, if we require wait-freedom.

### 5.1 The class $C_t$

Informally, our impossibility result applies to all objects with the following properties:

- The object has a "non-trivial" read operation, which is able to distinguish between *t* different subsets of the object's possible states; and

- The object can be "moved freely" from any state to any other state, in a single operation.

In fact, the impossibility result applies to other objects, including a queue, which do not fall into this class because they cannot be moved from any possible state to any other possible state in a single operation; for example, if a queue currently has two elements, we cannot reach the state where it is empty in one operation. For simplicity, we present here the proof for the simpler, more restricted class described above, and we discuss a generalization for a queue in Section 5.4.

The class  $C_t$  is formally defined as follows:

**Definition 13** (The class  $C_t$ ). An object O is in the class  $C_t$  for  $t \ge 2$  if its state space Q can be partitioned into t nonempty subsets  $X_1, \ldots, X_t$ , such that

- The object has some operation  $o_{read}$ , which does not change the state of the object, such that for any two states  $q_i \in X_i, q_j \in X_j$  where  $i \neq j$ , the response to  $o_{read}$  from state  $q_i$  differs from the response to  $o_{read}$  from state  $q_j$ .

- For any two states  $q \neq q' \in Q$  there is some operation  $o_{change}(q, q')$  that causes the object to transition from state q to state q'.

An object in the class  $C_t$  has at least t different states, and any pair of states are mutually reachable from each other by a single operation. Thus, the memory representations that arise from an implementation of an object in  $C_t$ ,  $t \ge 3$ , from base objects with fewer than t states cannot all be at distance 1 from each other. By Proposition 6 we obtain:

**Proposition 14.** There is no obstruction-free perfect HI implementation of an object in  $C_t$ ,  $t \ge 3$ , from base objects with fewer than t states.

PROOF. Consider an object in  $C_t$ ,  $t \ge 3$ , and for each  $1 \le i \le t$ , choose a state  $q_i \in X_i$ . Let  $can(q_1), \ldots, can(q_t)$  be a possible configuration of canonical memory representations that arise from a perfect HI implementation. Since  $o_{change}$  returns a different response from  $q_i$  and from  $q_j$ ,  $i \ne j, q_1, \ldots, q_t$  are t distinct states that also induce t distinct memory representations, since an  $o_{change}$  that runs solo from the same memory representation must return the same response. By Proposition 6, this implies that for every  $2 \le i \le t$ , there is an index  $j_i$  such that  $can(q_1)[j_i] \ne can(q_i)[j_i]$ , and for any other index, the memory representations are equal. Assume there are  $2 \le i, k \le t$  such that  $j_i \ne j_k$ , this implies that  $can(q_i)[j_k] = can(q_1)[j_k] \ne can(q_k)[j_k]$  and  $can(q_k)[j_i] = can(q_1)[j_i] \ne can(q_i)[j_i]$  and therefore,  $can(q_i)$  and  $can(q_k)$  are at distance at least 2. Thus, for every,  $2 \le i, k \le t$ ,  $j_i = j_k$ . However, since the base object has less than t state this implies that for some  $i \ne k$ ,  $can(q_i) = can(q_k)$ , which is a contradiction.

*Examples of objects in the class*  $C_t$ . A *t*-valued read/write register is in the class  $C_t$ : it has *t* different states, each representing the value the register holds, and the READ operation distinguishes between them; the WRITE operation can move us from any state (i.e., any value) to any other state in a single operation. We have already seen in Section 4 that multi-valued registers *can* be implemented

| Perfect HI (Def. 5)   | State-quiescent HI (Def. 7) | Quiescent HI (Def. 8)      | Progress  |

|-----------------------|-----------------------------|----------------------------|-----------|

| Impossible (Prop. 14) | Impossible (Cor. 18)        | Possible (Alg. 4)          | Wait-free |

| Impossible (Prop. 14) | Possible (Alg. 2)           | Possible (Alg. 2 & Alg. 4) | Lock-free |

Table 1. Summary of results for implementing a SWSR multi-valued register from binary registers

from binary registers, if we weaken either the progress or the history independence requirements. Our results for SWSR multi-valued registers are summarized in Table 1.

Another example of an object in the class  $C_t$  is a *t*-valued CAS object that supports a read operation: the state is again the current value of the CAS, and the read operation distinguishes between all *t* possible values; as for the  $o_{change}$  operation, we can move from any state *q* to any state *q'* by invoking CAS(*X*, *q*, *q'*).

To illustrate the importance of the state-connectivity requirement in the definition of the class  $C_t$ , we argue that a *max register* [6], returning the maximum value ever written in it, is *not* in the class. The state space of a max register is not well-connected: as soon as we visit state *m*, the object can never go back to a state smaller than *m*. A simple modification to Algorithm 1, where the writer only writes to *A* if the new value is bigger than all the values it has written in the past, results in a wait-free state-quiescent HI max register from binary registers.

Another object that is not in the class  $C_t$  is a *set* over t elements, with insert, remove and lookup operations. Even though the set has  $2^t$  possible abstract states, its operations return only two responses, "success" or "failure"; thus, we cannot *distinguish* via a single operation between all  $2^t$  states, or even between t states (the number of elements that could be in the set). There is a simple wait-free perfect HI implementation of a set over the domain  $\{1, \ldots, t\}$ , using t binary registers: we simply represent the set as an array S of length t, with S[i] = 1 if and only if element i is in the set, with the obvious implementation of insert, delete and lookup.

#### 5.2 Impossibility of Wait-Free, State-Quiescent HI Implementations for the Class $C_t$

Let  $O \in C_t$  be a high-level object with state space Q. Consider a wait-free state-quiescent HI implementation of O using  $m \ge 1$  base objects  $obj_1, \ldots, obj_m$ . For each base object  $obj_i$ , let  $Q_i$  be the state space of  $obj_i$ ; we assume that  $|Q_i| \le t - 1$ . This is the only assumption we make about the base objects, and our impossibility result applies to arbitrary read-modify-write base objects as well as to simple read-write base registers. Let h be a linearization function for the implementation.

We consider executions with two processes:

- A "reader" process r, which executes a single oread operation, and

- A "changer" process *c*, which repeatedly invokes *o*<sub>change</sub> operations.

For the purpose of the impossibility result, we assume, that the local state of a process  $p_i$  contains the complete history of  $p_i$ 's invocations and responses. Our goal is to show that we can construct an execution where r does not return from its single  $o_{read}$  operation, violating wait-freedom.

The executions that we construct have the following form:

$$\alpha_{q_0,\dots,q_k} = o_{change}(q_0, q_1), r_1, o_{change}(q_1, q_2), r_2, \dots, o_{change}(q_{k-1}, q_k), r_k$$

where  $o_{change}(q_i, q_{i+1})$  is an operation executed by the changer process during which the reader process takes no steps, and  $r_i$  is a single step by the reader process. The reader executes a single  $o_{read}$  operation that is invoked immediately after the first  $o_{change}$  operation completes, and we will argue that the reader never returns.

In any linearization of  $\alpha_{q_0,\ldots,q_k}$ , the operations  $o_{change}(q_0,q_1),\ldots,o_{change}(q_{k-1},q_k)$  must be linearized in order, as they do not overlap. Furthermore, the  $o_{read}$  operation carried out by the reader

is not state-changing. Thus, the linearization of  $\alpha_{q_0,\ldots,q_k}$  ends with the object in state  $q_k$ , and we abuse the terminology by saying that the execution "ends at state  $q_k$ ".

We say that execution  $\alpha_{q_0,...,q_k}$  avoids a subset  $X \subseteq Q$  if  $\{q_1,...,q_k\} \cap X = \emptyset$ . (Note that we may have  $q_0 \in X$  and still say that  $\alpha_{q_0,...,q_k}$  avoids X; this is fine for our purposes, because the reader only starts running after the first  $o_{change}$  operation completes.)

**Lemma 15.** There exists a partition of the possible return values R for the  $o_{read}$  into subsets  $R_1, \ldots, R_t$ ,<sup>4</sup> such that if an execution  $\alpha_{q_0,\ldots,q_k}$  avoids  $X_i \subseteq Q$ , then the  $o_{read}$  operation cannot return any value from  $R_i$  at any point in  $\alpha_{q_0,\ldots,q_k}$ .

**PROOF.** For each  $1 \le i \le t$ , let  $R_i$  be the set of values r such that for some state  $q \in X_i$ , the  $o_{read}$  operation returns r when executed from state q. By the definition of the class  $C_t$ , the sets  $R_1, \ldots, R_t$  are disjoint, and since the sets  $X_1, \ldots, X_t$  partition the state space Q, the sets  $R_1, \ldots, R_t$  partition the set of responses R.

Fix an execution  $\alpha_{q_0,...,q_k}$  that avoids  $X_i$ , and recall that in any linearization, the operations  $o_{change}(q_0, q_1), \ldots, o_{change}(q_{k-1}, q_k)$  must be linearized in-order, as they are non-overlapping operations by the same process. The  $o_{read}$  operation cannot be linearized before the first operation  $o_{change}(q_0, q_1)$ , because it is only invoked after this operation completes. Thus, the  $o_{read}$  operation either does not return in  $\alpha_{q_0,...,q_k}$ , or it is linearized after some operation  $o_{change}(q_j, q_{j+1})$  where  $j \ge 0$ . In the latter case, let  $\ell \neq i$  be the index such that  $q_{j+1} \in X_\ell$ ; we know that  $\ell \neq i$  as  $\alpha_{q_0,...,q_k}$  avoids  $X_i$ . The value returned by the  $o_{read}$  is in the set  $R_\ell$ , which is disjoint from  $R_i$ . Therefore in  $\alpha_{q_0,...,q_k}$  the  $o_{read}$  operation either does not return, or returns a value that is not in  $R_i$ .

Using the fact that each base object has at most t - 1 possible states, we can construct t arbitrarily long executions that the reader cannot distinguish from one another, such that each subset  $X_i$  is avoided by one of the t executions. Two execution prefixes  $\alpha_1$  and  $\alpha_2$  are *indistinguishable* to the reader, denoted  $\alpha_1 \stackrel{r}{\sim} \alpha_2$ , if the reader is in the same state in the final configurations of  $\alpha_1$  and  $\alpha_2$ .

The construction is inductive, with each step extending the executions by one operation and a single step of the reader:

**Lemma 16.** Fix  $k \ge 0$ , and suppose we are given t executions of the form  $\alpha_i = \alpha_{q_0^i,\ldots,q_k^i}$  for  $i = 1, \ldots, t$ , such that  $\alpha_1 \stackrel{r}{\sim} \ldots \stackrel{r}{\sim} \alpha_t$ , and each  $\alpha_i$  avoids  $X_i$ . Then we can extend each  $\alpha_i$  into an execution  $\alpha'_i = \alpha_{q_0^i,\ldots,q_{k-1}^i}$  that also avoids  $X_i$ , such that  $\alpha'_1 \stackrel{r}{\sim} \ldots \stackrel{r}{\sim} \alpha'_t$ .

PROOF. Let  $\alpha_i = \alpha_{q_0^i,...,q_k^i}$  for i = 1, ..., t be executions satisfying the conditions of the lemma, and let us construct extensions  $\alpha'_i = \alpha_{q_0^i,...,q_k^i,q_{k+1}^i}$  for each i = 1, ..., t. By assumption, the reader is in the same local state at the end of all executions  $\alpha_i$  for  $1 \le i \le t$ , and so its next step is the same in all of them. Our goal is to choose a next state  $q_{k+1}^i$  for each i = 1, ..., t, and extend each  $\alpha_i = \alpha_{q_0^i,...,q_k^i}$  into  $\alpha'_i = \alpha_{q_0^i,...,q_k^i}$  by appending an operation  $o_{change}(q_k^i, q_{k+1}^i)$ , followed by a single step of the reader. We must do so in a way that continues to avoid  $X_i$ , and maintains indistinguishability to the reader.

Since the implementation of O is state-quiescent HI and since each execution  $\alpha_i$  ends in a state-quiescent configuration, if  $\alpha_i$  ends in state q, then the memory must be in its canonical representation, can(q) (as defined in Section 2).

Let  $obj_{\ell}$  be the base object accessed by the reader in its next step in all t executions. Because  $obj_{\ell}$  has only t - 1 possible memory states and there are t subsets  $X_1, \ldots, X_t$ , there must exist two distinct subsets  $X_j, X_{j'}$   $(j \neq j')$  and two states  $q \in X_j, q' \in X_{j'}$  such that  $can(q)[\ell] = can(q')[\ell]$ .

<sup>&</sup>lt;sup>4</sup>We assume there are no unused values in *R*, that is, for any  $r \in R$ , there is some state  $q \in Q$  such that when  $o_{read}$  is executed from state q, it returns r.

For every  $1 \le i \le t$ , there is a state  $q_{k+1}^i \in \{q, q'\}$  such that  $q_{k+1}^i \notin X_i$ : if  $i \notin \{j, j'\}$  then we choose between q and q' arbitrarily, and if i = j or i = j' then we choose  $q_{k+1}^i = q'$  or  $q_{k+1}^i = q$ , respectively.

We extend each  $\alpha_i = \alpha_{q_0^i,...,q_k^i}$  into  $\alpha'_i = \alpha_{q_0^i,...,q_k^i,q_{k+1}^i}$  by appending a complete  $o_{change}(q_k^i, q_{k+1}^i)$  operation, followed by a single step of the reader. The resulting execution  $\alpha'_i$  still avoids  $X_i$ , as we had  $\{q_1^i,...,q_k^i\} \cap X_i = \emptyset$ , and the new state also satisfies  $q_{k+1}^i \notin X_i$ . Moreover, when the reader takes its step, it observes the same state for the base object  $obj_\ell$  that it accesses in all executions, as all of them end in either state q or state q', and  $can(q)[\ell] = can(q')[\ell]$ . Therefore, the reader cannot distinguish the new executions from one another.

By repeatedly applying Lemma 16, we can construct arbitrarily long executions, with the reader taking more and more steps (since in an execution  $\alpha_{q_0,...,q_k}$  the reader takes *k* steps) but never returning. This contradicts the wait-freedom of the implementation, to yield:

THEOREM 17. For any object O in the class  $C_t$ , there is no wait-free implementation that is statequiescent HI using base objects with fewer than t states.

PROOF. We construct *t* arbitrarily long executions, in each of which an  $o_{read}$  operation takes infinitely many steps but never returns. The construction uses Lemma 16 inductively: we begin with empty executions,  $\alpha_1^0 = \ldots = \alpha_t^0 = \alpha_{q_0}$ . These executions trivially satisfy the conditions of Lemma 16, as each  $\alpha_i^0$  avoids  $X_i$  (technically, it avoids *all* subsets  $X_j$ ), and furthermore, since the reader has yet to take a single step in any of them, it is in the same local state in all executions. We repeatedly apply Lemma 16 to extend these executions, obtaining for each  $k \ge 0$  a collection of *t* executions  $\alpha_1^k = \alpha_{q_0^1, q_1^1, \ldots}, \alpha_t^k = \alpha_{q_0^t, q_1^t, \ldots}$ , such that each  $\alpha_i^k$  avoids  $X_i$ , and the reader cannot distinguish the executions from one another.

Suppose for the sake of contradiction that the reader returns a value r at some point in  $\alpha_1^k$ . Then it returns the same value r at some point in each execution  $\alpha_i^k$  for each i = 1, ..., t, as it cannot distinguish these executions, and its local state encodes all the steps it has taken, including whether it has returned a value, and if so, what value. Let  $R_1, ..., R_t$  be the partition from Lemma 15. By the lemma, for each i = 1, ..., t, since execution  $\alpha_i^k$  avoids  $X_i$ , we must have  $r \notin X_i$ . But this means that there is no value that the reader can return, a contradiction.

Continuing on in this way, we can construct arbitrarily long executions, with the reader taking more and more steps (since in an execution  $\alpha_{q_0,...,q_k}$  the reader takes *k* steps) but never returning. This contradicts the wait-freedom of the implementation.

#### 5.3 Multi-Valued Register

For read/write registers, we obtain the following impossibility result:

**Corollary 18.** There is no wait-free state-quiescent HI implementation of a t-valued register,  $t \ge 3$ , from binary registers.

This impossibility result is complemented by the register implementations we described in Section 4, where we relaxed either the progress condition or the history independence condition to circumvent the impossibility. Corollary 18 also implies:

**Proposition 19.** The reader must write in any wait-free quiescent HI implementation of a SWSR multi-valued register from binary registers.

**PROOF.** Assume there is a wait-free quiescent HI implementation with linearization function h where the reader never writes to the shared memory. Let  $\alpha$  be a finite execution of the implementation, which ends with a configuration without a pending WRITE operation. If there is also no

pending READ operation in  $\alpha$ , the execution ends in a quiescent configuration and the memory of this configuration is equal to the canonical memory representation of the value state( $h(\alpha)$ ).

Otherwise, since the implementation is wait-free, there is an extension of  $\alpha$ ,  $\beta = \alpha \alpha'$ , such that only the reader takes steps in  $\alpha'$  and completes the pending READ operation, and  $\beta$  ends in a quiescent configuration. Since the reader does not write to the shared memory, and the writer did not take steps in  $\alpha'$ , mem( $\alpha$ ) = mem( $\beta$ ). In addition, the last high-level value written in  $\alpha$  and  $\beta$  are identical, i.e., state( $h(\alpha)$ ) = state( $h(\beta)$ ). Since  $\beta$  ends with a quiescent configuration, the memory of this configuration is equal to the canonical memory representation of the last written value in  $\beta$  and the same is true for  $\alpha$ . This shows the implementation is state-quiescent HI, contradicting Corollary 18, which states that there is no wait-free state-quiescent HI implementation.

#### 5.4 Extension to a Queue

The state space of a *queue* is described as a list, that is, an ordered set of elements. An ENQUEUE(v) operation adds the element v to the end of the list and a DEQUEUE() operation removes the first element from the list and returns it. We consider a queue that supports a PEEK() operation, which returns the first element in the list, without changing the object's state. The elements added to the queue are taken from the finite domain  $\{1, \ldots, t\}, t \ge 2$ . The response space  $R = \{r_0, \ldots, r_t\}$  is of size t + 1, where response  $r_i = i, 1 \le i \le t$ , indicates that i is the first element in the list, and response  $r_0 = \emptyset$  indicates that the queue is empty. For simplicity, response  $r_0$  is also used as a default response from an ENQUEUE operation.

A queue is not in the class  $C_t$  since not all states are reachable from each other by a single operation. Items can be added to the queue using ENQUEUE operations without changing the value of the item in the front of the queue, which is the response from a PEEK operation. We can use this property to move from state to state, without going through a state that returns a response we wish to avoid. To fully control the response values the PEEK operation can return in the executions we construct, we pick a *representative* state for each response value, instead of partitioning the whole state space, and construct executions alternating between these states.

We pick t + 1 representative states from Q,  $q_0, \ldots q_t$ , such that the response of PEEK from state  $q_i$ ,  $0 \le i \le t$ , is  $r_i$ ; let  $q_i = \{i\}$ ,  $1 \le i \le t$ , that is, a queue that contains exactly one element *i*, and  $q_0 = \emptyset$  is the initial state where the queue is empty.

For  $i_1 \neq i_2$ ,  $0 \leq i_1, i_2 \leq t$ , define a sequence of operations  $S(i_1, i_2)$  that moves the object's state from  $q_{i_1}$  to  $q_{i_2}$  as follows:

- (1) If  $i_1 = 0$ : Define  $S(i_1, i_2) = \text{ENQUEUE}(i_2)$ .

- (2) If  $i_2 = 0$ : Define  $S(i_1, i_2) = \text{Dequeue}()$ .

- (3) Otherwise, if  $i_1, i_2 \neq 0$ : Define  $S(i_1, i_2) = \text{ENQUEUE}(i_2)$ , DEQUEUE().

If  $i_1 = 0$ ,  $\Delta(\emptyset, \text{ENQUEUE}(i_2)) = (\{i_2\}, \_)$  and for  $i_2 = 0$ ,  $\Delta(\{i_1\}, \text{DEQUEUE}()) = (\emptyset, \_)$ . If  $i_1, i_2 \neq 0$ , we have that  $\Delta(\{i_1\}, \text{ENQUEUE}(i_2)) = (\{i_1, i_2\}, \_)$  and then,  $\Delta(\{i_1, i_2\}, \text{DEQUEUE}()) = (\{i_2\}, \_)$ . That is, the sequence of operations goes through a third state  $\{i_1, i_2\}$ , different than  $q_0, \ldots, q_t$ , such that a PEEK operation returns the same response from this state and state  $q_{i_1}$ . Therefore, even though this sequence has two operations and not one, the response the PEEK operation can return goes from  $r_{i_1}$  to  $r_{i_2}$ , without going through a third response value. This allows to provide a lower bound for a queue with a similar proof to the one for class  $C_t$ , where the changer moves the object's state to a representative state between each step of the reader. For more details and proof of the next theorem, refer to Appendix C.

THEOREM 20. There is no wait-free implementation of a queue with a PEEK operation and elements from domain  $\{1, \ldots, t\}$  that is state-quiescent HI using base objects with fewer than t + 1 states.

### 6 A HISTORY-INDEPENDENT UNIVERSAL IMPLEMENTATION

In the previous sections, we considered history-independent implementations of objects from base objects that are too small to store the state of the abstract object in its entirety, and showed that certain tradeoffs are unavoidable in this setting: for many objects, one must sacrifice either wait-freedom or state-quiescent history independence. We now turn to study large base objects, which can store the entire state of the abstract object, together with auxiliary information; we show that in this regime, a wait-free implementation that is state-quiescent HI *is* possible. Our implementation actually satisfies a somewhat stronger property than state-quiescent HI: at any point in the execution, the observer cannot gain information about operations that completed before a pending operation started, except for the state of the object when the earliest pending operation began.

When the full state of the object can be stored in a single memory cell, there is a simple lock-free universal implementation, using *load-link/store-conditional* (LLSC).<sup>5</sup> The current state of the object is stored in a single cell, an operation reads the current value of this cell, using *LL*, and then tries to write the new value of the object (after applying its changes) in this cell, using *SC*.

This implementation is clearly perfect HI. However, it is not wait-free since an operation may repeatedly fail, since other operations may modify the memory cell in between its LL and its SC. The standard way to make the universal implementation wait-free relies on *helping* [19, 27]: When starting, an operation *announces* its type and arguments in shared memory. Operations check whether other processes have pending operations and help them to complete, obtaining the necessary information from their announcement; after helping an operation to complete, they store a response to be returned later. This breaches history independence, revealing the type and arguments of prior and pending operations, as well as the responses of some completed operations.

Our wait-free, history-independent universal implementation follows a similar approach, but ensures that announcements and responses are cleared before operations complete, to guarantee that forbidden information are not left in shared memory. This is done very carefully in order to erase information only after it is no longer needed.

To use the more standard and commonly-available atomic CAS, we implement an abstraction of a *context-aware* variant of LLSC [31], which explicitly manages the set of processes that have load-linked this cell as *context*. This again breaches history independence, as the context reveals information about prior accesses. To erase this information, the implementation clears the context of a memory cell using an additional *release* operation, added to the interface of context-aware *releasable LLSC* (R-LLSC). This allows us to obtain a *wait-free state-quiescent HI universal implementation from atomic CAS*.

The next section presents the universal implementation using linearizable R-LLSC objects. Its basic properties are proved in Section 6.2, including showing that the algorithm is state-quiescent HI, when the R-LLSC implementation is HI. We then give a lock-free R-LLSC perfect HI implementation from atomic CAS (Section 6.3), and obtain a *wait-free state-quiescent HI universal* implementation from atomic CAS, in Section 6.4.

#### 6.1 Universal HI Implementation from Linearizable Releasable LLSC

A context-aware *load-link/store-conditional* (LLSC) object over a domain V is defined as follows: the state of an LLSC object O is the pair (O.val, O.context), where  $O.val \in V$  is the value of the object, and O.context is a set of processes. The initial state is  $(v_0, \emptyset)$ , where  $v_0 \in V$  is a designated initial value. Process  $p_i$  can perform the following operations:

<sup>&</sup>lt;sup>5</sup>In hardware, *load-linked* reads a memory cell, while *store-conditional* changes this memory cell, provided that it was not written since the process' most recent load-linked.

- LL(O): adds  $p_i$  to *O.context* and returns *O.val*.

- **VL**(*O*): returns *true* if  $p_i \in O$ .context and *false* otherwise.

- **SC**(*O*, *new*): if  $p_i \in O.context$ , sets O.val = new and  $O.context = \emptyset$ , and returns *true*; otherwise, it returns *false*.

- **LOAD**(*O*): returns *O*.*val* without changing *O*.*context*.

**STORE**(*O*, *new*): sets *O*.*val* = *new* and *O*.*context* =  $\emptyset$  and returns *true*.

A VL, SC or STORE is *successful* if it returns *true*; note that STORE is always successful. LOAD and STORE operations are added to simplify the code and proof.

The universal implementation appears in Algorithm 5. The right side of Lines 6, 18 and 25, marked in blue, as well as Lines 22 and 27, marked in red, are only used to ensure history independence; we ignore them for now, and explain their usage later. We assume that the set of possible responses R of the object is disjoint from its set of operations O, i.e.,  $R \cap O = \emptyset$ , and  $\perp \notin R \cup O$ .

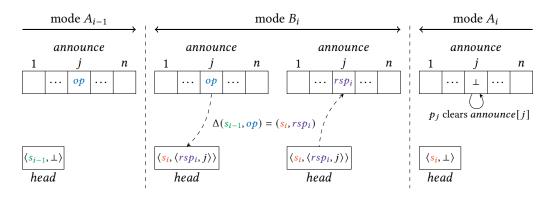

An array *announce* [1..*n*] stores information about pending operations, while *head* holds the current state of the object, along with some auxiliary information, like the response to the most recently applied operation *o*, and the identifier of the process that invoked *o*. In-between operations, the value of *head* is  $\langle q, \perp \rangle$ , where *q* is the current state of the object.

A process invoking a read-only operation calls APPLYREADONLY, which simply reads the object's state from *head* and returns a response according to the sequential specification of the object. This does not change the memory representation of the implementation.

A process  $p_i$  invoking a state-changing operation calls APPLY. First,  $p_i$  announces the operation by writing its description to *announce*[*i*], and then,  $p_i$  repeatedly tries to apply operations (either its own operation or operations announced by other processes) until it identifies that its own operation has been applied. The choice of which operation to apply (Lines 8-12) is determined by a local variable *priority<sub>i</sub>*, which is not part of the memory representation. If there is a pending operation by process  $p_j$ ,  $j = priority_i$ , then  $p_i$  applies  $p_j$ 's operation; otherwise, it applies it own operation. Each time  $p_i$  successfully changes the state of the object, it increments *priority<sub>i</sub>* (modulo *n*). This ensures that all pending operations will eventually help the same process.

Applying an operation o, with  $\Delta(q, o) = (q', r)$ , consists of three stages, each of which can be performed by any process (not just the process that invoked o, and not necessarily the same process for all three stages).

In the first stage, head is changed from  $\langle q, \perp \rangle$  to  $\langle q', \langle r, j \rangle \rangle$ , where  $p_j$  is the process that invoked operation *o*. The stage starts when some process  $p_i$  reads  $\langle q, \perp \rangle$  from *head* with LL(*head*) (Line 6L), and decides which operation to try to apply, say *o* by process  $p_j$ . To do so,  $p_i$  performs SC(*head*,  $\langle q', \langle r, j \rangle \rangle$ ) (Line 14). If the SC is successful, the value of *head* did not change between the LL and the SC of  $p_i$ . This ensures that the chosen operation, read from *announce*[*j*] in Line 8 or Line 11 after the LL(*head*), is not applied more than once.

In the second stage, the response r is written into announce[j], overwriting o itself, to notify the invoking process  $p_j$  that its operation was performed, and what value  $p_j$  should return. A process  $p_i$  that writes the response to announce[j] has read  $\langle q', \langle r, j \rangle \rangle$  from *head* with LL(*head*) (Line 6L) and then performs a successful VL(*head*) in Line 19. If  $p_i$  performs a successful SC(*announce*[j], r) in Line 20, then it previously performed a LL(*announce*[j]) in Line 18L, i.e., between LL(*head*) and VL(*head*). This guarantees that the value of *head* does not change between LL(*head*) and SC(*announce*[j], r).

The third and final stage changes head from  $\langle q', \langle r, j \rangle \rangle$  to  $\langle q', \perp \rangle$ . This erases the response *r* and the process index *j*, ensuring that forbidden information about the history is not revealed. The invoking process  $p_j$  does not return until its response is cleared from *head* (Lines 25L and 26). This ensures that a successful SC(*announce*[*j*], *r*) (Line 20) writes the right response to the applied

**Algorithm 5** State-quiescent HI universal implementation from R-LLSC : code for process *p<sub>i</sub>*

```

head, R-LLSC variable initialized to \langle q_0, \perp \rangle, where q_0 is the initial state

announce [n], R-LLSC variable array all cells initialized to \perp

local priority<sub>i</sub>, initialized to i

ApplyReadOnly(op \in O):

▶ Read-only operations

1: \langle q, \_ \rangle \leftarrow \text{LOAD}(head)

2: _, rsp \leftarrow \Delta(q, op)

3: return rsp

Apply(op \in O):

State-changing operations

4: STORE(announce[i], op)

5: while LOAD(announce[i]) \notin R do

\langle q, r \rangle \leftarrow \text{LL}(head)

6R.1: wait until LOAD(announce[i]) \notin R

6L:

6R.2: goto Line 24

if r = \bot then

In-between operations

7:

help \leftarrow LOAD(announce[priority_i])

8:

if help \in O then apply \text{-}op \leftarrow help; j \leftarrow priority_i

9:

Try to apply another process operation

10:

else

if LOAD(announce[i]) \notin O then continue

▶ Go to the beginning of the loop

11:

apply-op \leftarrow op; j \leftarrow i

▶ Try to apply your own operation

12:

state, rsp \leftarrow \Delta(q, apply \text{-}op)

13:

if SC(head, \langle state, \langle rsp, j \rangle \rangle) then

▶ End of the first stage

14:

priority_i \leftarrow (priority_i + 1) \mod n

15:

else

16:

\langle rsp, j \rangle \leftarrow r

17:

18R.1: wait until LOAD(announce[i]) \notin R

a \leftarrow LL(announce[j])

18L:

18R.2: RL(announce[j])

18R.3: goto Line 24

if VL(head) = true then

19:

if a \in O then SC(announce[j], rsp)

▶ End of the second stage

20:

SC(head, \langle q, \perp \rangle)

▶ End of the third stage

21:

22:

if a = \perp then RL(announce[j])

continue

23:

▶ Go to the beginning of the loop

24: response \leftarrow LOAD(announce[i])

25L: \langle q, r \rangle \leftarrow \text{LL}(head)

Ш

25R.1: wait until LOAD(head) \neq \langle , \langle , i \rangle \rangle

25R.2: goto Line 27

26: if r = \langle \_, i \rangle then SC(head, \langle q, \bot \rangle)

Clear response from head before returning

27: else RL(head)

28: STORE(announce[i], \perp)

Clear response from announce[i]

29: return response

```