# SFVInt: Simple, Fast and Generic Variable-Length Integer Decoding using Bit Manipulation Instructions

Gang Liao Ye Liu Yonghua Ding Le Cai Jianjun Chen

ByteDance Infrastructure System Lab

gangliao1024@gmail.com {ye.liu, yonghua.ding, le.cai, jianjun.chen}@bytedance.com

# Abstract

The ubiquity of variable-length integers in data storage and communication necessitates efficient decoding techniques. In this paper, we present SFVInt, a simple and fast approach to decode the prevalent Little Endian Base-128 (LEB128) varints. Our approach, distilled into a mere 500 lines of code, effectively utilizes the Bit Manipulation Instruction Set 2 (BMI2) in modern Intel and AMD processors, achieving significant performance improvement while maintaining simplicity and avoiding overengineering. SFVInt, with its generic design, effectively processes both 32-bit and 64-bit unsigned integers using a unified code template, marking a significant leap forward in varint decoding efficiency. We thoroughly evaluate SFVInt's performance across various datasets and scenarios, demonstrating that it achieves up to a 2x increase in decoding speed when compared to varint decoding methods used in established frameworks like Facebook Folly and Google Protobuf.

# 1 Introduction

In data processing and storage, handling variable-length integers efficiently is of paramount importance. These integers feature prominently across numerous systems such as search engines like Apache Lucene [10], databases including IBM DB2 [5] and Apache Kudu [25], and popular file formats such as ORC [11] and Parquet [12], acting as a key component for compact data representation. Their significance extends to serialization frameworks, notably Google Protobuf [13], and the WebAssembly binary encoding [7]; they are also an essential part of the Go programming language's default API [14], highlighting its widespread adoption across various critical technological domains [6, 21–23]. The Little Endian

Base-128 (LEB128) encoding [32], used for these variablelength integers (varints), is widely adopted for its optimal balance of space efficiency and implementation simplicity. However, a critical challenge arises in varint decoding, particularly due to the unpredictable lengths of encoded integers, which often lead to frequent branch mispredictions and thus become a bottleneck in performance.

Recognizing this challenge, we turn our attention to the Bit Manipulation Instruction Set 2 (BMI2) [2], an advancement in processor instruction sets available in modern Intel [16] and AMD CPUs [4]. BMI2 offers a suite of instructions that are particularly adept at handling bitwise operations, a core component of varint decoding processes. Leveraging these capabilities, we propose SFVInt, a generic, simple, and fast approach to accelerate the decoding of LEB128 varints. Condensed into around 500 lines of code, our approach significantly outperforms traditional methods, offering up to a 2x increase in decoding speed over techniques used in well-established systems and libraries. Our approach is both simple and highly effective, capable of handling 32-bit and 64-bit unsigned integers with a unified C++ template. We provide a detailed analysis, highlighting how the use of BMI2 instructions contributes to this substantial performance enhancement.

To the best of our knowledge, this is the first time the BMI2 technique has been applied in the context of varint decoding, marking a significant advancement in this field. This research presents a critical enhancement in the efficiency of varint decoding, opening pathways for more refined data processing optimizations. The ramifications of this discovery are extensive, potentially influencing the design and performance optimization of databases, network systems, and big data applications, crucial in a data-centric era.

### 2 Background

#### 2.1 Variable-Length Integers

Varints, or variable-length integers, are a method of encoding integers using one or more bytes. They are widely adopted in computing for their ability to optimize space usage. The principal idea behind varints is to use a dynamic number of bytes for representation, depending on the integer's magnitude. Smaller numbers consume fewer bytes, making this method highly space-efficient for data that predominantly consists of smaller integers.

<sup>&</sup>lt;sup>†</sup> Work performed at ByteDance Infrastructure System Lab.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

Conference acronym 'XX, June 03-05, 2018, Woodstock, NY

<sup>© 2018</sup> Association for Computing Machinery.

ACM ISBN 978-1-4503-XXXX-X/18/06...\$15.00

Varint encoding, essential in data format optimization, encompasses several schemes, including Group Varint [8], Prefix Varint [8], and Stream Varint [18], each with its unique characteristics. Among these, LEB128 stands out for its simplicity and widespread adoption. LEB128 operates on a simple yet effective principle: it encodes an integer into a sequence of bytes, where each byte holds 7 bits of the integer plus a continuation bit. This continuation bit indicates the presence of subsequent bytes. In this scheme, the integer's least significant 7-bit group is positioned in the first byte, adhering to the little-endian convention. Despite the existence of more complex varint formats, LEB128's simplicity makes it a prevalent choice in various applications, underlining its effectiveness in efficiently handling integer encoding.

The decoding process of LEB128 involves reading each byte, extracting the 7 bits of the integer, and assembling them to reconstruct the original integer. This process continues byte by byte until a byte with the continuation bit set to 0 is encountered, indicating the end of the encoded integer.

LEB128 decoding, a bottleneck in high-volume data processing, faces challenges due to encoded integers' unpredictable lengths. This variability frequently leads to branch mispredictions, exacerbating CPU overhead. The need for per-byte decision-making during decoding amplifies this issue, especially in large-scale or real-time processing environments. Addressing these inefficiencies is crucial for optimizing LEB128's decoding performance.

#### 2.2 Bit Manipulation Instructions (BMI)

Bit Manipulation Instructions (BMI2) [2] are advanced CPU instruction sets designed for efficient bit-level operations, introduced with Intel's Haswell architecture and adopted by AMD. These instructions, including PDEP and PEXT, enable faster and more effective manipulation of bits in registers or memory. BMI2's inclusion in modern processors optimizes critical operations in high-performance computing, data processing, and cryptographic applications, reflecting a broader trend towards enhancing computational efficiency through specialized hardware capabilities.

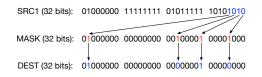

PDEP (Parallel Bit Deposit): This instruction streamlines the process of depositing bits from a source operand into a destination operand based on a mask. It allows for selectively placing bits in specific positions, enabling precise control over bit placement. PDEP is particularly useful in scenarios where bits from a variable need to be reorganized or masked in a specific pattern, as illustrated in Figure 1.

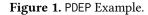

PEXT (Parallel Bit Extract): PEXT complements PDEP by enabling the extraction of bits from a source operand based on a mask. This instruction allows for the selective extraction of bits, effectively 'filtering' the source operand through the mask to produce the desired bit pattern in the destination operand. PEXT is invaluable for operations that require isolating specific bits from a larger set, such as decoding varints where bits need to be extracted from a sequence of bytes. An example of PEXT in action is depicted in Figure 2.

#### Figure 2. PEXT Example.

Our motivation for utilizing BMI2 in LEB128 varint decoding lies in its ability to simplify the bit extraction and assembly process, crucial for efficient decoding. Traditional LEB128 decoding, characterized by sequential bitwise operations, benefits from the parallelism and efficiency offered by BMI2 instructions.

# **3** SIMD Implementation

This section outlines traditional varint encoding/decoding methods, then focuses on optimizing operations like varint sequence skipping and storage size determination. We explore BMI2-enhanced implementation, detailing how it improves decoding efficiency and performance, demonstrating a progression from basic to advanced techniques in varint processing.

#### 3.1 Basic Varint Operations

**Varint Encoding**: LEB128 encodes integers into a compact, variable-length format by dividing each integer into 7-bit blocks, each represented by a single byte. All bytes, barring the final one, mark their most significant bit as 1 to denote the sequence's continuation. The final byte's most significant bit is set to 0, indicating the end of the encoding. This method is efficient for storing integers, particularly smaller values. The pseudocode below details this encoding process:

Algorithm: LEB128 Integer Encoding

Input: Integer val, BufferPointer buf, Output: None

- 1. while val  $\geq 0x80$  do

- 2. \*buf = 0x80 | (val & 0x7f);

- 3. val >>= 7; buf++;

- 5. end while

- 6. \*buf = val; buf++;

If val is 128 (0x80) or greater, the function stores the lowest 7 bits of val into the buf, setting the 8th bit of this byte (denoted by 0x80) to signal that more bytes follow. The buffer pointer buf is then advanced, and val is right-shifted by 7 bits to prepare the next 7 bits for encoding. This process repeats until val is less than 128. At this point, val is small enough to fit into the final byte, indicating the end of the variable-length integer.

**Varint Decoding**: LEB128 extracts the original integer from its encoded representation. It involves iteratively processing each byte, reconstructing the integer by aggregating 7-bit segments.

```

Algorithm: LEB128 Integer Decoding (Basic Version)

Input: BufferPointer buf

Output: T res (either uint32_t or uint64_t)

1. res = 0; max_shift = std::is_same_v<T, uint32_t> ? 28 : 63;

2. for shift = 0 to max_shift step 7 do

3. res |= ((*buf & 0x7f) << shift);

4. if (likely(!(*buf++ & 0x80))) break;

5. end for</pre>

```

The decoding algorithm reads each byte, combining its lower 7 bits into the result. The most significant bit indicates if subsequent bytes are part of the integer. The decoding concludes when a byte with the most significant bit unset is encountered, indicating the final byte of the varint. In line 1, the maximum shift values for LEB128 decoding - 28 for 32bit integers and 63 for 64-bit integers – are determined by the integer size and the 7-bit grouping used in this encoding. For example, for a 32-bit unsigned integer, which has a maximum value of 4,294,967,295 (2<sup>32</sup> - 1), it would require up to 5 bytes for representation, as 32 divided by 7 is approximately 4.57. Varint Skipping: In columnar storage systems, efficient skip operations are vital for effective filtering and scanning of varint-encoded data streams. We employ a technique that processes 64-bit data blocks, enabling simultaneous handling of multiple varints.

Algorithm: LEB128 Integer Skipping Input: uint64\_t n (# integers to skip), BufferPointer buf Output: Updated BufferPointer 1. res = 0; w = (const uint64\_t\*)(buf); 2. while n >= 8 do 3. n -= \_\_builtin\_popcountll(~(\*w++) & 0x80808080808080808080); 4. end while 5. buf = (const char\*)(w); 6. while n-- do 7. while \*buf++ & 0x80 do {;} end while // fallback

8. end while

In line 3, applying the bitwise NOT operation (~) inverts all bits of a 64-bit integer, turning continuation bits from '1's to '0's and vice versa. With the mask 0x80808080808080808080, highlighting MSBs in each 8-bit segment, the AND operation (&) then isolates these MSBs. Utilizing SIMD instructions, specifically POPCNT, this step efficiently identifies varint terminations within the 64-bit block.

**Varint Sizing**: In varint-based systems, accurately estimating storage needs is crucial. We utilize precomputed lookup tables (LUTs) to quickly calculate the exact byte size needed for varint encoding, based on the position of the most significant set bit in integers. This approach optimizes computational efficiency with low overhead in caching, facilitating rapid estimations for dynamic storage allocation.

Algorithm: LEB128 Integer Sizing

Input: vec<T> values (T is either uint32\_t or uint64\_t)

Output: uint64\_t size

```

4, 4, 4, 4, 4, 4, 4, 3, 3, 3, 3, 3, 3, 3,

2, 2, 2, 2, 2, 2, 2, 1, 1, 1, 1, 1, 1, 1};

2. kLUT64 = \{10,

9, 9, 9, 9, 9, 9, 9, 8, 8, 8, 8, 8, 8, 8,

7, 7, 7, 7, 7, 7, 7, 6, 6, 6, 6, 6, 6, 6,

5, 5, 5, 5, 5, 5, 5, 4, 4, 4, 4, 4, 4, 4,

3, 3, 3, 3, 3, 3, 3, 2, 2, 2, 2, 2, 2, 2, 2,

1, 1, 1, 1, 1, 1, 1, 1\};

3. size = 0;

4. for each val in values do

5.

if constexpr (std::is_same_v<val, uint32_t>) then

6.

size += kLUT32[__builtin_clz (val | 1)]

7.

else

8.

size += kLUT64[__builtin_clzll(val | 1)]

```

```

9. end for

```

This algorithm computes the total storage requirement for varint-encoded integers by iteratively applying the LZCNT/BSR instruction to count leading zeros, adjusted for zero values with (val|1). The outcome indexes into predefined lookup tables (LUTs) for 32-bit and 64-bit integers (kLUT32, kLUT64) to retrieve byte sizes.

#### 3.2 BMI2-Enhanced Bulk Varint Decoding

This section enhances varint decoding with BMI2 instructions, advancing beyond the basic methods in Section 3.1.

**Mask Configuration**: The first step involves employing a 64-bit mask with the \_pext\_u64 BMI2 instruction for efficient extraction of most significant bits (MSBs) from byte sequences. Configurations like 0x0000808080808080 for six bytes, 0x0080808080808080 for seven bytes, and 0x808080808080808080 for eight, cater to different ranges of extracted values (0-63, 0-127 and 0-255, respectively), influencing the number of processed bytes. Our implementation adopts the six-byte mask 0x0000808080808080, based on findings that longer masks risk L1 instruction cache spillage, compromising performance. This choice ensures an optimized balance between decoding efficiency and CPU resource utilization, in line with the operational constraints of modern CPU architectures.

Utilizing \_pext\_u64(word, mask), we decipher the count and positions of integers within a 64-bit block. For example, using an 8-byte mask (0x80808080808080808080) that yields zero indicates eight complete integers in the segment. Initially setting aside carryover or boundary effects for simplicity, we employ \_pext\_u64 instructions strategically to isolate individual integers:

| <pre>int1 = _pext_u64(word,</pre> | 0x00000000000007f); |

|-----------------------------------|---------------------|

| <pre>int2 = _pext_u64(word,</pre> | 0x000000000007f00); |

| <pre>int3 = _pext_u64(word,</pre> | 0x0000000007f0000); |

| <pre>int4 = _pext_u64(word,</pre> | 0x00000007f000000); |

| <pre>int5 = _pext_u64(word,</pre> | 0x0000007f0000000); |

| <pre>int6 = _pext_u64(word,</pre> | 0x00007f000000000); |

| <pre>int7 = _pext_u64(word,</pre> | 0x007f00000000000); |

| <pre>int8 = _pext_u64(word,</pre> | 0x7f0000000000000); |

For a masked result of 63, indicating two integers spanning six and two bytes respectively in the original varint sequence. To extract them efficiently, we apply the \_pext\_u64 instruction with specific masks tailored to these lengths:

> int1 = \_pext\_u64(word, 0x00007f7f7f7f7f7f); int2 = \_pext\_u64(word, 0x7f7f000000000000);

This method showcases adaptability to varint structures, identified by mask results, reducing the need for conditional byte-by-byte checks that can cause branch mispredictions and pipeline stalls.

**Cross-Boundary Cases**: In addressing cross-boundary cases where integers span two or even three consecutive blocks, we adopt a refined approach crucial for accurate and complete decoding. Our approach employs two key variables: shift\_bits and partial\_value. shift\_bits tracks the necessary bit displacement for integers crossing block boundaries, while partial\_value retains the already decoded segment from a previous block. This system ensures proper alignment and integration of integer segments across blocks, merging partial\_value with new segments to reconstruct complete integers.

Continuing from our previous example where a masked result of 63 suggests two integers with the first spanning six bytes and the second two, we encounter the complexity of int1 extending across 64-bit block boundaries. Here, partial\_value retains int1's initial segment from the preceding block, while shift\_bits tracks the decoded bit count. The subsequent processing extracts int1's remainder, aligns it using shift\_bits, and merges it with partial\_value, forming the complete integer, as demonstrated below:

This method effectively handles integers crossing 64-bit block boundaries, ensuring their precise and complete reconstruction.

**Algorithm**: The following presents an advanced varint decoding algorithm optimized for bulk processing with a 6-byte MASK, integrating cross-boundary case handling and fully leveraging BMI2 instructions for improved efficiency and speed. Line 7 employs \_pext\_u64 to extract MSBs from a 64-bit word using a defined mask, revealing the varint structure, including the count and distribution of integers. The algorithm then uses this output (mval) in a switch-case to customize the decoding for each integer's unique encoding pattern.

In an example from lines 38-42, the algorithm manages a case where a significant part of an integer starts in a preceding 64-bit block and continues into the current one. The binary pattern 62 (represented as 111110) under a 6-byte MASK indicates an integer's end within the current block. Using \_pext\_u64, the algorithm merges this block's decoded segment with the preceding block's pt\_val, completing the integer. Additionally, the presence of five leading 1s (1111)

```

Algorithm: Optimized Bulk Varint Decoding with BMI2

Input: uint64_t n, BufferPointer buf, T* res (uint32/uint64)

Output: Updated BufferPointer in the data stream

1: mask_length = 6; mask = 0x000080808080808080;

shift_bits = 0; pt_val = partial_value = 0;

2.

3:

buf -= mask_length;

4:

while n \ge 8 do

5:

buf += mask_length;

6:

word = *(const uint64_t*)(buf);

7:

mval = _pext_u64(word, mask);

8:

switch (mval)

9:

case 0:

10:

cu_val = _pext_u64(word, 0x0000000000007f);

*res++ = (cu_val << shift_bits) | pt_val;</pre>

11:

12:

*res++ = _pext_u64(word, 0x000000000007f00);

13:

*res++ = _pext_u64(word, 0x0000000007f0000);

14:

*res++ = _pext_u64(word, 0x00000007f000000);

*res++ = _pext_u64(word, 0x0000007f00000000);

15:

16:

*res++ = _pext_u64(word, 0x00007f000000000);

17:

shift_bits = 0; pt_val = 0; n -= 6;

18:

case 15:

19:

cu_val = _pext_u64(word, 0x000007f7f7f7f7f);

*res++ = (cu_val << shift_bits) | pt_val;</pre>

20:

21:

*res++ = _pext_u64(word, 0x00007f000000000);

22:

shift_bits = 0; pt_val = 0; n -= 2;

23:

case 32:

24:

cu_val = _pext_u64(word, 0x00000000000007f);

*res++ = (cu_val << shift_bits) | pt_val;</pre>

25:

*res++ = _pext_u64(word, 0x000000000007f00);

26:

27:

*res++ = _pext_u64(word, 0x0000000007f0000);

28:

*res++ = _pext_u64(word, 0x00000007f000000);

29.

*res++ = _pext_u64(word, 0x0000007f00000000);

30:

pt_val = _pext_u64(word, 0x00007f000000000);

31:

shift_bits = 7; n -= 5;

32:

case 45:

cu_val = _pext_u64(word, 0x000000000007f7f);

33.

34.

*res++ = (cu_val << shift_bits) | pt_val;</pre>

35:

*res++ = _pext_u64(word, 0x000007f7f7f0000);

36:

pt_val = _pext_u64(word, 0x00007f000000000);

37:

shift_bits = 7; n -= 2;

38:

case 62:

39:

cu_val = _pext_u64(word, 0x0000000000007f);

40:

*res++ = (cu_val << shift_bits) | pt_val;</pre>

pt_val = _pext_u64(word, 0x00007f7f7f7f7f00);

41:

42:

shift_bits = 35; n -= 1;

43:

case 63:

pt_val |= _pext_u64(word, 0x00007f7f7f7f7f7f7f7f7

44:

45:

<< shift_bits;

46:

shift_bits += 42;

case ... // Other cases omitted for brevity

47:

48: end while // fallback later

```

Figure 3. BMI2-enhanced Bulk Decoding.

signals an incomplete integer extending into the next block, which is extracted and stored in pt\_val for subsequent decoding, with shift\_bits adjusted to 35 for alignment, i.e., the five 7-byte sequences. This decrement in n by 1 ensures the algorithm's seamless management of cross-boundary integers, maintaining decoding continuity and precision.

Case 63, depicted in lines 44-45, addresses a binary representation of 111111, signaling an integer spanning three data blocks, with the current block as its mid-segment. This specific case requires extracting six bytes (42 bits) via \_pext\_u64, appending this data to the partial value to maintain integer continuity across blocks.

# 4 Performance Evaluation

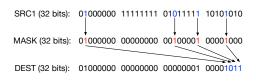

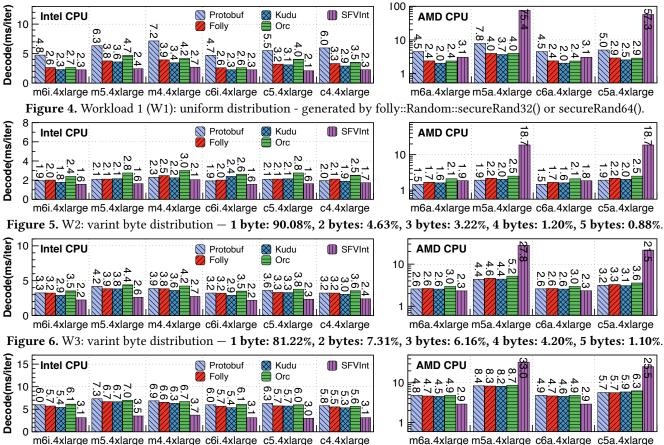

In our evaluation of the BMI2-enhanced varint decoding technique, we leveraged various AWS EC2 instances with diverse Intel and AMD CPU architectures (refer to Table 1). We created datasets encoded as varints, following uniform and skewed distributions. The uniform distribution served as a stable benchmark, while the skewed distribution, biased towards smaller integers (1-byte or 2-bytes LEBs), mirrored real-world varint patterns.

We employed four distinct workloads for evaluation: W1 featured uniformly distributed 32-bit integers as a benchmark; W2 used real-world LEB lengths from the WebAssembly build suite [1], providing practical insights; and Workloads W3 and W4 derived from our proprietary systems' data distributions, offering a realistic view of their application. Notably, W2 to W4 exhibited a skew towards 1-byte integers, aligning with typical data trends observed in practical scenarios. The specific distributions for these workloads are detailed in the figure captions of Figures 4 to 7.

Our evaluation compares our BMI2-based decoding technique against established varint encoding solutions from Apache Kudu (a columnar storage system)[25], Google Protobuf (a serde library)[13], Apache ORC (a columnar format)[11], and Facebook Folly (a C++ std lib)[9], which **all support 32-bit and 64-bit integer encoding**. This benchmark situates our approach within the current industry practices<sup>1</sup>, focusing on in-memory decoding performance given the widespread use of the LEB128 algorithm. Performance gains were assessed in a **single-threaded** environment to attribute improvements directly to our method.

| EC2 | CPU Architecture                               |

|-----|------------------------------------------------|

| m6i | Intel Xeon Ice Lake 8375C                      |

| m5  | Intel Xeon Skylake 8175M / Cascade Lake 8259CL |

| m4  | Intel Xeon Broadwell E5-2686 / Haswell E5-2676 |

| c6i | Intel Xeon Ice Lake 8375C                      |

| c5  | Intel Xeon Cascade Lake                        |

| c4  | Intel Xeon Haswell E5-2666 v3                  |

| m6a | 3rd Gen AMD EPYC (Milan)                       |

| c6a | 3rd Gen AMD EPYC (Milan)                       |

| m5a | 2nd Gen AMD EPYC 7571                          |

| c5a | 2nd Gen AMD EPYC 7R32                          |

Table 1. AWS EC2 Types and CPU Architectures

#### 4.1 Intel CPU Microarchitectures

In Figures 4-7, the left panel showcases the varint decoding performance across six EC2 instance types featuring Intel CPUs, detailed in Table 1. Each figure within the panel includes benchmarks for each EC2 instance type, with the yaxis representing the time required per iteration (in milliseconds), where each iteration involves decoding one million integers generated according to a specific distribution. Here, SFVInt consistently excels, surpassing all other systems in decoding speed across every instance type and under various distributions. For example, in W1 (Figure 4), SFVInt demonstrates a significant performance edge, nearly doubling the speed of Protobuf. Similarly, in W4 (Figure 7), SFVInt outperforms all other systems by nearly a factor of two.

The varint byte distribution evolves from W2 to W4, indicating a transition to a more varied spread of integer sizes. In W2 (Figure 5), the distribution heavily favors 1-byte integers, constituting 90.08% of the data, with a minor representation of 2-byte at 4.63%, and even less for 3-byte (3.22%), 4-byte (1.20%), and 5-byte integers (0.88%). Progressing to W4, there's a noticeable decrease in 1-byte integers to 72.13%, with corresponding increases across the board-2-byte integers rise to 12.31%, 3-byte to 8.53%, 4-byte to 5.31%, and 5-byte to 1.72%. This shift implies an increase in the number of bytes subject to the decoding process, logically resulting in prolonged iteration times as the byte distribution broadens. Specifically, on the m6i.4xlarge instance, the iteration time for SFVInt extends from 1.6ms in W2, to 2.2ms in W3, ultimately reaching 3.1ms in W4. Such an increment reflects the additional computational overhead necessitated by the decoding of a higher proportion of multi-byte integers.

On the other hand, the performance gap between SFVInt and other systems widens most notably in W4. Taking the c6i.4xlarge instance as an example, SFVInt achieves a 2x speed increase compared to Protobuf in W4, while in W3 and W2, the gains are 45% and 19%, respectively. This indicates that SFVInt's BMI2-fortified decoding mechanism gains a significant edge when dealing with varints exceeding the single-byte range. This is because with shorter bytelength encodings, our approach requires a sequence of serial instructions similar to traditional byte-by-byte processing. This is exemplified by case 0 (lines 10 - 17) in Figure 3, which involves a greater number of sequential executions than case 63 (lines 44 - 46), hence, SFVInt's relatively subdued enhancement for 1-byte integers reflects this similarity to conventional decoding approaches.

#### 4.2 AMD CPU Microarchitectures

In our analysis detailed in Figures 4-7, we observe that SFVInt demonstrates up to 40% faster varint decoding on 3rd generation AMD EPYC processors (m6a and c6a), in contrast to the slower performance on 2nd generation CPUs (m5a and c5a). This performance disparity is consistent with the known emulation overhead of PEXT/PDEP instructions on AMD platforms, which can significantly lag behind Intel's native execution [3, 17]. Studies indicate that on AMD hardware, these instructions' latency can vary widely, from 18 to approximately 300 cycles [15]. The improved results with

<sup>&</sup>lt;sup>1</sup>Our assessment directly interacted with the varint decoding interfaces of these libraries, ensuring no additional overhead is incurred.

Figure 7. W4: varint byte distribution – 1 byte: 72.13%, 2 bytes: 12.31%, 3 bytes: 8.53%, 4 bytes: 5.31%, 5 bytes: 1.72%.

newer AMD generations suggest advancements in BMI2 instruction handling. For enhanced consistency across CPU architectures, we can incorporate a dynamic selection mechanism between BMI2-accelerated and standard decoding or employs ZP7 [31], a branchless alternative for AMD processors.

# 5 Related Works

Varint Formats. In byte-oriented integer compression, various techniques aim to improve decoding efficiency. Traditional LEB128, using a 7-bit structure, lacks SIMD optimization. In contrast, Google's VARINT-GB [8] offers an alternative by encoding a constant block of integers with a unified control byte, streamlining decoding for data with variable lengths. The patented VARINT-G8IU [30] further advances this innovation, employing SIMD to process variable counts of integers within a fixed byte structure, controlled by an initial byte. Stream VByte [18] segregates control and data bytes into separate streams to fully leverage SIMD's parallel processing strengths. However, these techniques, despite their SIMD-enabled efficiency gains, diverge from the prevalent LEB128 standard, limiting their seamless integration into existing infrastructures. Conversely, the Masked VByte method [26] retains the LEB128 form while harnessing SIMD for improved performance, yet it is not without its drawbacks—namely, a non-generic and maintenance-intensive codebase exceeding 2300 lines, tailored specifically for 32-bit unsigned integers. Our proposed SFVInt is a simple, elegant, fast, and generic solution that effectively addresses the limitations present in earlier methods.

**BMI in DBMS.** The pursuit of SIMD optimizations for data scanning operations and operator vectorization has been prominent in data management research [20, 27–29]. Kudu was seminal in applying BMI2 for data scan filtering [24, 25], a similar idea extended by Parquet-Select [19], which utilizes BMI2 for optimized selection pushdown in columnar storage.

# 6 Conclusions

In this paper, we introduced SFVInt, a simple, fast and generic varint decoding approach leveraging BMI2 instructions, significantly enhancing the performance of varint decoding. Through rigorous evaluation across diverse CPU architectures, SFVInt consistently demonstrated up to a 2x increase in decoding speed over traditional methods on modern processors. This performance boost is crucial for applications dealing with large-scale data processing. SFVInt: Simple, Fast and Generic Variable-Length Integer Decoding using Bit Manipulation Instruction XX, June 03-05, 2018, Woodstock, NY

# References

- [1] [n.d.]. WebAssembly Build Suite. Retrieved Jan 2, 2024 from https: //github.com/WebAssembly/build-suite

- [2] 2013. x86 Bit manipulation instruction set. Retrieved Jan

6, 2023 from https://en.wikipedia.org/wiki/X86\_Bit\_manipulation\_ instruction\_set

- [3] 2017. Ryzen and BMI2: Strange behavior and high latencies. Retrieved Jan 2, 2024 from https://www.reddit.com/r/Amd/comments/60i6er/ ryzen\_and\_bmi2\_strange\_behavior\_and\_high\_latencies/

- [4] AMD. 2023. AMD64 Architecture Programmer's Manual. Retrieved Jan 6, 2023 from https://www.amd.com/content/dam/amd/en/documents/ processor-tech-docs/programmer-references/24594.pdf

- [5] Bishwaranjan Bhattacharjee, Lipyeow Lim, Timothy Malkemus, George Mihaila, Kenneth Ross, Sherman Lau, Cathy McArthur, Zoltan Toth, and Reza Sherkat. 2009. Efficient Index Compression in DB2 LUW. Proc. VLDB Endow. 2, 2 (aug 2009), 1462–1473. https://doi.org/ 10.14778/1687553.1687573

- [6] Souvik Bhattacherjee, Gang Liao, Michael Hicks, and Daniel J. Abadi. 2021. BullFrog: Online Schema Evolution via Lazy Evaluation. In Proceedings of the 2021 International Conference on Management of Data (Virtual Event, China) (SIGMOD '21). Association for Computing Machinery, New York, NY, USA, 194–206. https://doi.org/10.1145/ 3448016.3452842

- [7] World Wide Web Consortium. 2022. WebAssembly Binary Format. Retrieved Jan 6, 2023 from https://webassembly.github.io/spec/core/ binary/values.html

- [8] Jeffrey Dean. 2009. Challenges in building large-scale information retrieval systems: invited talk. In WSDM '09: Proceedings of the Second ACM International Conference on Web Search and Data Mining. New York, NY, USA, 1–1. http://doi.acm.org/10.1145/1498759.1498761

- [9] Facebook. 2012. Folly: An open-source C++ library developed and used at Facebook. Retrieved Dec 30, 2023 from https://github.com/facebook/ folly

- [10] Apache Software Foundation. 2011. Apache Lucene. Retrieved Jan 4, 2023 from https://lucene.apache.org/

- [11] Apache Software Foundation. 2013. Apache ORC: the smallest, fastest columnar storage for Hadoop workloads. Retrieved Dec 30, 2023 from https://orc.apache.org

- [12] Apache Software Foundation. 2013. Apache Parquet: an open source, column-oriented data file format. Retrieved Jan 4, 2023 from https: //parquet.apache.org/

- [13] Google. 2001. Protocol Buffers: Google's data interchange format. Retrieved Dec 30, 2023 from https://github.com/protocolbuffers/protobuf

- [14] Robert Griesemer. 2011. Support for varint encoding in Go. Retrieved Jan 6, 2023 from https://github.com/golang/go/commit/ f30719dc89c2a41502fa584b790943170ad2d1ce

- [15] InstLatX64. 2019. Achilles heel of AMD Zens: data dependency of PDEP/PEXT instructions. Retrieved Jan 6, 2023 from https://mobile. twitter.com/InstLatX64/status/1209095219087585281

- [16] Intel Corporation. 2016. Intel® 64 and IA-32 Architectures Software Developer's Manual. Retrieved Jan 6, 2023 from https://www.intel. com/content/dam/www/public/us/en/documents/manuals/64-ia-32architectures-software-developer-vol-2b-manual.pdf

- [17] Kullberg. 2017. Ryzen Schach Performance BMI2 Problem. Retrieved Jan 2, 2024 from https://www.hardwareluxx.de/community/threads/ ryzen-schach-performance-bmi2-problem.1156117/

- [18] Daniel Lemire, Nathan Kurz, and Christoph Rupp. 2018. Stream VByte: Faster byte-oriented integer compression. *Inform. Process. Lett.* 130 (Feb. 2018), 1–6. https://doi.org/10.1016/j.ipl.2017.09.011

- [19] Yinan Li, Jianan Lu, and Badrish Chandramouli. 2023. Selection Pushdown in Column Stores Using Bit Manipulation Instructions. *Proc. ACM Manag. Data* 1, 2, Article 178 (jun 2023), 26 pages. https: //doi.org/10.1145/3589323

- [20] Yinan Li and Jignesh M. Patel. 2013. BitWeaving: Fast Scans for Main Memory Data Processing. In Proceedings of the 2013 ACM SIGMOD International Conference on Management of Data (New York, New York, USA) (SIGMOD '13). Association for Computing Machinery, New York, NY, USA, 289–300. https://doi.org/10.1145/2463676.2465322

- [21] Gang Liao. 2022. The Evolution of Cloud Data Architectures: Storage, Compute, and Migration. https://drum.lib.umd.edu/items/e591f36aa240-42db-8252-196ed4facee9.

- [22] Gang Liao and Daniel J. Abadi. 2023. FileScale: Fast and Elastic Metadata Management for Distributed File Systems. In *Proceedings of the* 2023 ACM Symposium on Cloud Computing (, Santa Cruz, CA, USA,) (SoCC '23). Association for Computing Machinery, New York, NY, USA, 459–474. https://doi.org/10.1145/3620678.3624784

- [23] Gang Liao, Amol Deshpande, and Daniel J. Abadi. 2023. Flock: A Low-Cost Streaming Query Engine on FaaS Platforms. arXiv:2312.16735 [cs.DB] https://github.com/flock-lab/flock

- [24] Todd Lipcon. 2020. Core algorithms for columnar serialization. Retrieved Jan 6, 2023 from https://github.com/apache/kudu/commit/ 0ba6cb8d6b38a992786e5027528349a43802fd31

- [25] Todd Lipcon, David Alves, Dan Burkert, Jean-Daniel Cryans, Adar Dembo, Mike Percy, Silvius Rus, Dave Wang, Matteo Bertozzi, Colin Patrick McCabe, et al. 2015. Kudu: Storage for fast analytics on fast data. *Cloudera, inc* 28 (2015), 36–77.

- [26] Jeff Plaisance, Nathan Kurz, and Daniel Lemire. 2017. Vectorized VByte Decoding. arXiv:1503.07387 [cs.IR]

- [27] Orestis Polychroniou and Kenneth A. Ross. 2014. Vectorized Bloom Filters for Advanced SIMD Processors. In Proceedings of the Tenth International Workshop on Data Management on New Hardware (Snowbird, Utah) (DaMoN '14). Association for Computing Machinery, New York, NY, USA, Article 6, 6 pages. https://doi.org/10.1145/2619228.2619234

- [28] Orestis Polychroniou and Kenneth A. Ross. 2015. Efficient Lightweight Compression Alongside Fast Scans. In *Proceedings of the 11th International Workshop on Data Management on New Hardware* (Melbourne, VIC, Australia) (*DaMoN'15*). Association for Computing Machinery, New York, NY, USA, Article 9, 6 pages. https://doi.org/10.1145/2771937. 2771943

- [29] Evangelia Sitaridi, Orestis Polychroniou, and Kenneth A. Ross. 2016. SIMD-Accelerated Regular Expression Matching. In Proceedings of the 12th International Workshop on Data Management on New Hardware (San Francisco, California) (DaMoN '16). Association for Computing Machinery, New York, NY, USA, Article 8, 7 pages. https://doi.org/10. 1145/2933349.2933357

- [30] Alexander A. Stepanov, Anil R. Gangolli, Daniel E. Rose, Ryan J. Ernst, and Paramjit S. Oberoi. 2011. SIMD-Based Decoding of Posting Lists. In Proceedings of the 20th ACM International Conference on Information and Knowledge Management (Glasgow, Scotland, UK) (CIKM '11). Association for Computing Machinery, New York, NY, USA, 317–326. https://doi.org/10.1145/2063576.2063627

- [31] Zach Wegner. 2019. ZP7: Zach's Peppy Parallel-Prefix-Popcountin' PEXT/PDEP Polyfill. Retrieved Jan 6, 2023 from https://github.com/ zwegner/zp7

- [32] Wikipedia. 2023. LEB128 (Little Endian Base 128). Retrieved Jan 6, 2023 from https://en.wikipedia.org/wiki/LEB128