# NeuraLUT: Hiding Neural Network Density in Boolean Synthesizable Functions

Marta Andronic and George A. Constantinides

Department of Electrical and Electronic Engineering

Imperial College London, UK

Email: {marta.andronic18, g.constantinides}@imperial.ac.uk

Abstract—Field-Programmable Gate Array (FPGA) accelerators have proven successful in handling latency- and resourcecritical deep neural network (DNN) inference tasks. Among the most computationally intensive operations in a neural network (NN) is the dot product between the feature and weight vectors. Thus, some previous FPGA acceleration works have proposed mapping neurons with quantized inputs and outputs directly to lookup tables (LUTs) for hardware implementation. In these works, the boundaries of the neurons coincide with the boundaries of the LUTs. We propose relaxing these boundaries and mapping entire sub-networks to a single LUT. As the subnetworks are absorbed within the LUT, the NN topology and precision within a partition do not affect the size of the lookup tables generated. Therefore, we utilize fully connected layers with floating-point precision inside each partition, which benefit from being universal function approximators, with rigid sparsity and quantization enforced only between partitions, where the NN topology becomes exposed to the circuit topology. Although cheap to implement, this approach can lead to very deep NNs, and so to tackle challenges like vanishing gradients, we also introduce skip connections inside the partitions. The resulting methodology can be seen as training DNNs with a specific sparsity pattern that allows them to be mapped to much shallower circuit-level networks, thereby significantly improving latency. We validate our proposed method on a known latency-critical task, jet substructure tagging, and on the classical computer vision task, the digit classification using MNIST. Our approach allows for greater function expressivity within the LUTs compared to existing work, leading to lower latency NNs for the same accuracy.

# I. INTRODUCTION AND MOTIVATION

The deployment of DNNs on the edge has led to many breakthroughs across a wide range of domains, for example, in particle collision [1], cybersecurity [2] and X-ray classification [3]. Edge devices, characterized by limited resources, demand specialized solutions that can deliver efficient and real-time inference without compromising accuracy. However, designing deep learning models capable of meeting the stringent requirements of edge devices has proven to be a great challenge. This difficulty arises from the inherent high computational complexity and substantial footprint of these models. In response to these challenges, research efforts come from both hardware and software perspectives [4].

Custom hardware accelerators have proven to reach performance levels that were previously unreachable by general-purpose processors. The efficacy of these hardware-efficient accelerators stems from innovative approximation methods employed to preserve accuracy on smaller, lower-precision, and sparse models [5]. Examples of such techniques include

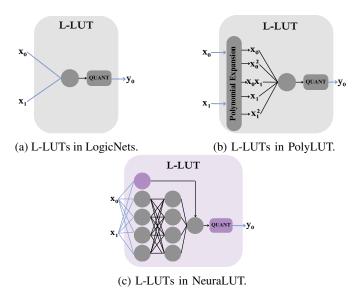

Fig. 1: Gray circle: Affine transformation + ReLU. Purple circle: Affine transformation for residual connections. Blue lines: Low precision. Black lines: Full precision.

parameter pruning, network quantization, and knowledge distillation. Moreover, FPGAs are ideal for prototyping and deploying cutting-edge DNNs because their reconfigurability allows for rapid design iteration [5].

LUT-based NNs have emerged as an alternative to binary neural networks (BNNs) due to the limitations of the latter in fully leveraging FPGA resources. Specifically, BNNs do not efficiently utilize *K*-input LUTs by implementing XNORs gates and popcount logic. Prior LUT-based NNs include Poly-LUT [6], LUTNet [7], LogicNets [8] and NullaNet [9]. The main motivation of these works was to utilize the fact that LUTs are able to implement *K*-input Boolean operations and encapsulate inside a single LUT more complex functions to increase the efficiency of traditional NNs.

LUTNet [7] is a NN architecture that replaces BNNs' XNORs with trainable *K*-input LUTs. We refer to these LUTs as Physical-LUTs (P-LUTs) to emphasize their direct correspondence to native FPGA *K*-input LUTs. LUTNet is not limited to training weighted sums and is able to train sums of arbitrary Boolean functions of *K* activations. However, LUTNet maintains the exposed datapaths of a BNN, including

the popcount operations, and inherits BNNs' restriction of having single-bit activations.

We refer to LUTs of arbitrary size as Logical-LUTs (L-LUTs) to underline the fact that they can exceed the number of P-LUT inputs, in which case they get implemented by the synthesis tools as circuits of multiple P-LUTs. PolyLUT [6], LogicNets [8], and NullaNet [9] absorb the full computation of a neuron inside a single L-LUT, leaving no exposed datapaths except the connections between layers, and allow multi-bit precision. Therefore, the NN gets converted to a network of L-LUTs. What differentiates these works is what functions get encapsulated inside the L-LUTs: LogicNets and NullaNet encapsulate traditional linear + activation neurons (Figure 1a), while PolyLUT encapsulates multivariate polynomials + activation neurons (Figure 1b).

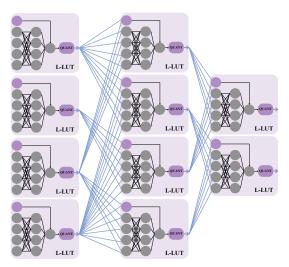

In latency-critical applications two considerations have to be regarded: the first one is reducing the latency associated with each layer, and the second one is reducing the number of layers. PolyLUT [6] and LogicNets [8] have succeeded in reducing the number of clock cycles associated with each layer to just one while maintaining a high frequency. However, the design of accurate models poses a challenge as the number of layers becomes constrained. This develops into a significant limitation for the traditional success of DNNs, where a higher number of layers is often correlated with improved performance. Therefore, we propose designing deep NNs with specific sparsity patterns that resemble sparsely connected dense partitions, enabling the encapsulation of sub-networks entirely within a single L-LUT (Figure 1c). The advantage is that the network can reach greater function expressibility while keeping the number of circuit-level layers minimal (Figure 2), and by hiding these sub-networks inside LUTs only the quantization of inputs and outputs is required, while the rest of the parameters maintain full precision. However, substantially increasing the depth of each partition, even though it does not impact the implementation complexity, does impact the training complexity, and can lead to vanishing/exploding gradients, an issue for which we also provide a solution.

In this paper, we present the following novel contributions:

- We introduce NeuraLUT, an open-source<sup>1</sup> framework designed to leverage the underlying structure of the FPGA architecture by hiding dense and full-precision sub-networks in synthesizable Boolean functions.

- We demonstrate that utilizing sub-networks in the places where prior works have used linear functions enhances the representational capacity of NNs, facilitating significant reductions in the depth and width of the circuit-level model architecture.

- We enhance the training by integrating skip-connections in our sub-networks which facilitate the flow of gradients, promoting stable and efficient learning. This proved to be particularly valuable when dealing with high complexity sub-networks.

Fig. 2: High-level view of NeuraLUT's architecture. Sparsely connected dense sub-networks with skip-connections.

• We assess NeuraLUT using two datasets with distinct applications. Our results demonstrate that, for comparable accuracies, NeuraLUT achieves the lowest latencies, with reductions of up to  $26\times$  on MNIST and  $5\times$  on Jet Substructure.

## II. BACKGROUND

Designing NNs that run in real-time and have minimal area footprint while maintaining good accuracy requires rethinking the model design to optimize performance on the target hardware. Previous efforts have centered on co-designing NN architectures for dedicated hardware platforms, which involves an intrinsic development loop between model architecture design, training, and deployment. Prior co-design works that have been specialized for FPGA platforms can be split into three categories based on their main computational block: DSP-based, XNOR-based, and LUT-based.

# A. DSP-based Neural Networks

hls4ml [1] is an open-source source framework that specializes in mapping NNs to FPGAs for low-latency applications. Duarte *et al.* [1] leverage the hls4ml framework to generate latency-efficient fully-unrolled and rolled designs. However, the work utilizes high network precision, which leads to hightened Digital Signal Processing (DSP) utilization. Fahim *et al.* [10] utilize hls4ml while incorporating techniques from prior works, such as boosted decision trees [11] and quantization-aware training [12]. They further propose quantization-aware pruning to achieve higher performance and power efficiency.

# B. XNOR-based Neural Networks

FINN [13] is an open-source framework, originally designed for building high-performing BNN accelerators on FPGAs. FINN introduces hardware-specific optimizations such as replacing additions with popcount operators, replacing batch

<sup>&</sup>lt;sup>1</sup>https://github.com/MartaAndronic/NeuraLUT

normalization and activation with thresholding, and replacing max-pooling with Boolean ORs. Another work that focuses on mapping binary or ternary NNs is proposed by Ngadiuba *et al.* [14] which utilizes hls4ml.

# C. LUT-based Neural Networks

LUTNet [15] innovatively departed from traditional machine learning operators by replacing the XNORs of a BNN with learned Boolean functions. At inference, each Boolean function is efficiently computed using a single LUT on the FPGA, thus taking advantage of the resources available on the FPGA fabric. While the XNORs are operating on a single input feature, the LUTs operate on *K*-features. Therefore, the structure of LUTNet supports for multiple occurrences of each input in the neuron function allowing redundant operations to be removed through network pruning, while maintaining high accuracy. However, LUTNet displays exponential scaling of training parameters with the size of LUT inputs, which proves feasible only in the context of binary activations.

NullaNet [9] and LogicNets [8], present layers as multiinput multi-output Boolean functions. In Nullanet, the Boolean functions undergo Boolean logic minimization and, in order to manage computational resources, output values are determined selectively for specific input combinations, leaving the remaining outputs as don't-care conditions. LogicNets, on the other hand, employs high sparsity to address the drawback of NullaNet's lossy truth table conversion. To achieve this high sparsity, LogicNets applies an *a priori* random sparsity technique, which is supported by expander graph theory [16]. This design approach allows the reduction of the input vector size of each neuron to a user-defined fan-in F, and combats the exponential growth of truth tables, thus leading to efficient implementations. Therefore the number of trainable parameters associated with each neuron has complexity  $\mathcal{O}(F)$  (Table I).

PolyLUT [6] is also a NN architecture which absorbs all the operations performed by a neuron within a L-LUT, but it distinctively expands the feature vector at each neuron by incorporating all monomials up to a user-defined degree D. Consequently, the number of trainable parameters has complexity  $\mathcal{O}\left(\binom{F+D}{D}\right)$  (Table I). This expansion allows the model to capture complex relationships within the data through higher-degree polynomial expressions. Notably, PolyLUT integrates multiplicative interactions within a LUT-based model, and avoids the need for additional multiplication hardware by encapsulating everything inside the L-LUT. The increased function complexity within each layer further contributes to the reduction of required layers for achieving a given accuracy level.

# D. Skip Connections

Training particularly deep NNs presents challenges due to the vanishing gradient problem [17] [18]. This phenomenon arises when gradients diminish significantly or "vanish" as they propagate backward through the network during training. Residual NNs mitigate this problem by accumulating the outputs of some layers with the activations from previous layers [19].

#### E. Network in Network

The concept of micro-networks within a larger network has been proposed before, in a very different context: the design of CNN structures and as part of the sliding window operation. For example, Lin *et al.* [20] introduced Network in Network (NIN). In the Network in Network [20] architecture, multilayer perceptrons (MLPs) are utilized as a replacement for the traditional linear filters in convolutional layers.

The use of MLPs in [20] is motivated by the desire for a universal function approximator that can capture more abstract representations of latent concepts without relying on assumptions about their distributions. Moreover, MLPs are chosen for their compatibility with the structure of CNNs. They can be seamlessly integrated into the network and trained using back-propagation, facilitating the end-to-end learning process. Finally, MLPs address limitations associated with traditional convolutional layers in capturing abstract representations of latent concepts.

In contrast to NIN, NeuraLUT utilizes MLPs to capture more meaningful relationships within a L-LUT. This approach capitalizes on the benefits of MLPs as universal function approximators and their compatibility with traditional NN training techniques.

# III. METHODOLOGY

The key novelty of our work lies in the design of LUT-based NNs, where each LUT is capable of performing functions more powerful than traditional linear mappings. The most important observation is that LUTs have the capability to implement arbitrary functions, and they have been used in machine learning to implement linear transformations as shown in LogicNets or polynomials as demonstrated in PolyLUT.

While linear functions are simpler, it has been shown in PolyLUT that they underutilize the full potential of LUTs, resulting in less efficiency compared to more complex functions like polynomials. Moreover, polynomial functions serve as universal function approximators and impose no prior assumptions regarding data distributions, unlike more specialized functions. However, multivariate polynomial functions come with potentially exponentially increasing degrees of freedom, and as observed in PolyLUT, NNs of this kind are challenging to train, with diminishing returns when the degree exceeds two [6].

Yet, there exists another universal function approximator with the advantage of ease of training: the multilayer perceptron [21], [22]. Consequently, we embed MLPs within LUT functions, increasing the function expressivity of each L-LUT, while keeping the number of L-LUTs fixed.

## A. Tackling LUT size

NeuraLUT manages the fact that the size of a LUT is exponential in its number of inputs by containing regions of

TABLE I: Breakdown of the main L-LUT characteristics. F is the L-LUT fan-in, D is the degree of the polynomials, L is the depth of the sub-networks, and N is the width of the hidden layers of the sub-networks.

|                      | Function hidden inside each L-LUT    | No. of parameters                                                                 | Scaling type                       |  |  |

|----------------------|--------------------------------------|-----------------------------------------------------------------------------------|------------------------------------|--|--|

| LogicNets [8]        | Linear + Activation                  | $\mathcal{O}(F)$                                                                  | Linear in $F$                      |  |  |

| PolyLUT [8]          | Multivariate polynomial + Activation | $\mathcal{O}\left(\left(\begin{smallmatrix}F+D\\D\end{smallmatrix}\right)\right)$ | Polynomial in $F$ (for fixed $D$ ) |  |  |

| NeuraLUT (this work) | Arbitrary neural network             | $\mathcal{O}(LN^2 + (F+L)N)$                                                      | Linear in $F$ (for fixed $N$ )     |  |  |

high NN density inside the L-LUTs while keeping the circuit-level model (between L-LUTs) highly sparse. Consequently, NeuraLUT adopts from LogicNets the *a priori* sparsity random technique which restricts the number of inputs to each L-LUT to a fan-in parameter F and restricts the bit-width of the circuit-level inputs to a bit-width parameter  $\beta$ .

#### B. Skip Connections

The circuit-level model NNs for ultra-low latency applications have limited depth and the problem of vanishing gradients has not been deemed as an issue in prior works. However, in the NeuraLUT context, the hidden sub-networks have high depth relative to the number of L-LUT inputs and are hard to train unless residual connections are employed. The advantage of using residual connections within the network partitions is that they come at a minimal cost because they can also be encapsulated inside the L-LUT.

# C. Function hidden inside the L-LUT

NeuraLUT's performance boost comes from the representational power of the hidden dense residual NN as a function of the depth, widths and residual connection step. To express it, we require some notation. We denote each NN hidden in an L-LUT by  $\mathcal{N}$ , which is characterized by the following integers: L representing the depth of  $\mathcal{N}$ ,  $n_{\rm in}=n_0$  the input size, and  $n_1,n_2,...,n_L=n_{\rm out}$  the widths of the layers, and S quantifying the number of layers that are skipped by the residual connections. S=0 is a special case for no skip connections. We say that  $\mathcal{N}$  computes the following function prior to the quantized activation (where, for simplicity, we assume that L is a multiple of  $S\neq 0$ ):

$$f_{\mathcal{N}} = F_{\frac{L}{S}} \circ \phi \circ F_{\frac{L}{S}-1} \circ \dots \circ F_2 \circ \phi \circ F_1, \tag{1}$$

where  $F_i: \mathbb{R}^{n_{S(i-1)}} \to \mathbb{R}^{n_{Si}}$  such that

$$F_i(\mathbf{x}) = \hat{F}_i(\mathbf{x}) + R_i(\mathbf{x}), \tag{2}$$

where  $\hat{F}_i(\mathbf{x}): \mathbb{R}^{n_{S(i-1)}} \to \mathbb{R}^{n_{Si}}$  such that

$$\hat{F}_i(\mathbf{x}) = A_{Si} \circ \phi \circ A_{Si-1} \circ \dots \circ \phi \circ A_{Si-S+1}, \tag{3}$$

where  $R_i: \mathbb{R}^{n_{S(i-1)}} \to \mathbb{R}^{n_{Si}}$  and  $A_i: \mathbb{R}^{n_{i-1}} \to \mathbb{R}^{n_i}$  are affine transformations and

$$\phi(\mathbf{x}) = \text{ReLU}(x_1, \dots, x_k)$$

=  $(\max(0, x_1), \dots, \max(0, x_L)).$  (4)

It is important to note that since the L-LUTs have fan-in number of inputs and one output,  $n_{in}=F$  and  $n_{out}=1$ . Moreover, in NeuraLUT all the widths of the hidden layer are equal, i.e.  $n_2=\cdots=n_{L-1}=N$ . Therefore, the number of trainable parameters of  $\mathcal N$  will be equal to the number of weights and bias terms for each layer and residual connection. We denote the total number of trainable parameters of  $\mathcal N$  with  $T_{\mathcal N}$  and the total number of trainable parameters associated with all  $A_i$  and  $R_i$  with  $T_A$  and  $T_R$ , respectively. Additionally, we define T to be the function that returns the number of trainable parameters associated with an affine transformation  $X:\mathbb R^{d_1}\to\mathbb R^{d_2}$ , i.e.  $T(X)=d_1\cdot d_2+d_2$ .

$$T_{A} = T(A_{1}) + T(A_{2}) + \dots + T(A_{L})$$

$$= \begin{cases} (F \cdot 1 + 1), & \text{if } L = 1\\ (F \cdot N + N) + (N \cdot 1 + 1), & \text{if } L = 2\\ (F \cdot N + N) + (N \cdot 1 + 1)\\ + (N \cdot N + N)(L - 2), & \text{if } L > 2. \end{cases}$$

$$= \begin{cases} F + 1, & \text{if } L = 1\\ (F + 2)N + 1, & \text{if } L = 2\\ (L - 2)N^{2} + (F + L)N + 1, & \text{if } L > 2. \end{cases}$$

$$(5)$$

Similarly,

$$T_{R} = T(R_{1}) + T(R_{2}) + \dots + T(R_{\frac{L}{S}})$$

$$= \begin{cases} F + 1, & \text{if } \frac{L}{S} = 1\\ (F + 2)N + 1, & \text{if } \frac{L}{S} = 2\\ (\frac{L}{S} - 2)N^{2} + (F + \frac{L}{S})N + 1, & \text{if } \frac{L}{S} > 2 \end{cases}$$

(6)

Therefore, as seen in Table I, the total number of trainable parameters for an F-input L-LUT is

$$T_{\mathcal{N}} = T_A + T_R$$

=  $\mathcal{O}(LN^2 + (F+L)N)$ . (7)

There are two main scalability advantages over PolyLUT, as apparent from the table. Firstly, the scaling in the fan-in for

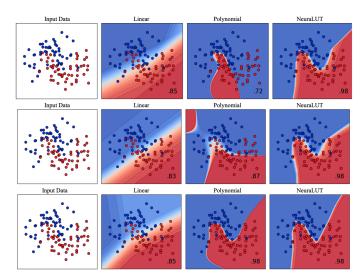

Fig. 3: Visualization of decision boundaries. Classifier comparison across three different seeds.

NeuraLUT is linear for fixed expressibility parameters N, L, whereas for PolyLUT it is polynomial for fixed expressibility parameter D. Secondly, the scaling in the expressibility parameters themselves is polynomial, whereas for PolyLUT it is exponential due to the combinatorial expression. Additionally, when N=L=1, and S=0, NeuraLUT is equivalent to Logic-Nets, making it, akin to PolyLUT, a strict generalization of LogicNets.

# D. Expressive power

In LogicNets, the L-LUT encapsulates a singular artificial neuron, comprising a linear transformation followed by a rectified linear unit. Consequently, the network computes a continuous piecewise linear function. In PolyLUT, the L-LUT is utilized for computing a multivariate polynomial function followed by a rectified linear unit, resulting in the network computing a continuous piecewise polynomial function. In NeuraLUT, the L-LUT incorporates a linear NN that independently computes a continuous piecewise linear function. Thus, the network also computes a continuous piecewise linear function, but with more (potentially many more) piecewise regions compared to LogicNets when L>1, because the number of regions can be exponential in L.

To visually illustrate the benefits of NeuraLUT's methodology, we train a 3-layer toy NN in three configurations. In the first configuration, each neuron contains a single linear function analogous to LogicNets and in the second configuration a single polynomial, similar to PolyLUT. The third configuration simulates NeuraLUT, replacing each neuron with a 2-layer NN. We trained these models with various seeds on a toy dataset featuring two semicircles, as shown in Figure 3. The contour graphs showcase the classification boundaries, where the blue and red regions indicate different output classifications of the network input and the white area serves as the decision boundary.

The experiment shows that compared to LogicNets, NeuraLUT has superior capability in discerning intricate data distributions with high accuracy when using a highly restricted number of layers. Compared to PolyLUT, we observed a trend across multiple seed runs. The NeuraLUT model consistently converges to highly precise solutions, while the polynomial network may yield impressive classifications like the one at the bottom of Figure 3, or it can reach a slightly inferior solution, as illustrated in the middle, or it can even fall short of the linear case's accuracy, as evident at the top. Although these performance disparities tend to diminish in larger NNs, they highlight a crucial distinction: NeuraLUT mitigates through simpler training PolyLUT's disadvantage of higher complexity bringing diminishing returns.

# E. Toolflow

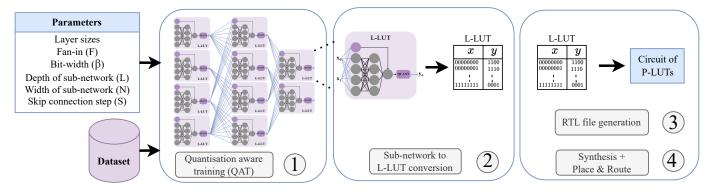

NeuraLUT extends LogicNets' toolflow [8], facilitating the DNN training, conversion to L-LUTs, RTL file generation, and hardware compilation. Modifications were made to the training implementation to accommodate the structure of NeuraLUT. The high-level view of the toolflow is illustrated in Figure 4.

1) Quantization-aware training (QAT): The DNN training is carried out using PyTorch. The initial step in the pipeline involves specifying learning-specific parameters, such as the learning rate, as well as topology parameters, as illustrated in Figure 4. The parameters L, N, and S are introduced in this framework to describe the topology of all sub-networks, while layer sizes fan-in and bit-width refer to the circuit-level topology.

Once these parameters are defined and the dataset is selected, the model is trained employing Decoupled Weight Decay Regularization [23] and Stochastic Gradient Descent with Warm Restarts [24]. Additionally, the inputs and outputs of each sub-network undergo batch normalization and quantization using Brevitas [25] quantized activation functions, which incorporate learned scaling factors. Additionally, each model undergoes training for 1000 epochs for the Jet Substructure dataset and 500 epochs for the MNIST dataset.

- 2) Sub-network to L-LUT conversion: The second stage in the pipeline involves converting each sub-network into an L-LUT. This process is carried out in PyTorch by first generating all input combinations based on their specified bitwidth and then evaluating the sub-network function on each of these combinations through inference. The number of entries in the L-LUT is defined by  $2^{\beta F}$ . Consequently, the area of the models is determined by a trade-off between activation precision and the level of sparsity between sub-networks.

- 3) RTL file generation: As part of the same Pytorch framework, the network can be automatically converted to Verilog RTL and each L-LUT is written out as read-only memories (ROMs) with registers at the input at the output.

- 4) Synthesis and Place & Route: To compile the Verilog RTL files, we utilize Vivado 2020.1, selecting the xcvu9p-flgb2104-2-i FPGA part, to mirror the approach of LogicNets and PolyLUT. To ensure consistency, we compile the projects using Vivado's

Fig. 4: Visualization of NeuraLUT's toolflow, consisting of four stages.

Flow\_PerfOptimized\_high settings, and execute synthesis in the Out-of-Context mode. Our target clock periods are set at 1 or 2 ns depending on the network size.

## IV. EXPERIMENTAL RESULTS

To evaluate our network architecture, we train our models on one ultra-low latency and size-critical dataset, the jet substructure tagging dataset as presented in [1], and on the MNIST dataset [26].

Jet substructure is a dataset from CERN, and efficiency is vital at their Large Hadron Collider (LHC). The deployment of ultra-low latency machine learning models at the LHC could enhance the experiments to preserve potential new physics signatures that would otherwise be lost as part of the initial stage of triggering. Therefore, we showcase NeuraLUT's effectiveness on this dataset which contains 16 substructure properties to classify 5 types of jets, offering potential applications in high-energy physics. To evaluate our method, we also utilize the MNIST, featuring  $28 \times 28$  pixel images of handwritten digits flattened into 784-dimensional inputs, with 10 output classes representing each digit.

Initially, we perform a case study on the MNIST dataset, aiming to understand NeuraLUT's training outcomes, including test accuracy, latency, and area footprint. Our primary goal is to showcase how integrating fully connected sub-networks with skip connections inside L-LUTs can increase training effectiveness and enable the generation of ultra-low latency and minimal area FPGA implementations. Focusing on the MNIST dataset provides valuable insights into the advantages of our approach, after which we evaluate multiple datasets and compare them against the state of the art to highlight the effectiveness of our method on different tasks.

## A. MNIST case study

1) Test accuracy: The primary advantage of training NeuraLUT models lies in their heightened expressibility, resulting in improved test accuracy. To illustrate this advantage, we conduct an analysis on MNIST using a fixed circuit-level model (Figure 5). Initially, we train it in the traditional setting hiding single neurons inside the L-LUTs, equivalent to LogicNets. Subsequently, we enhance the model by replacing each neuron

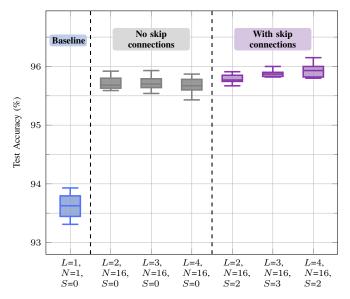

Fig. 5: Ablation study on MNIST across 10 seeds. Blue: baseline, Gray: NeuraLUT without skip connections, Purple: standard NeuraLUT. All models have a fixed circuit-level architecture with (256, 100, 100, 100, 100, 10) L-LUTs.

with dense sub-networks of increasing depth. Additionally, we evaluate the effectiveness of skip-connections by training NeuraLUT models both with (highlighted in purple) and without them (highlighted in gray).

The key highlight of this analysis is that, for a fixed number of L-LUTs, all NeuraLUT models significantly enhance test accuracy. Furthermore, skip-connections facilitate training to harness the capabilities of deeper sub-networks. Hence, gradually increasing the complexity of the sub-network results in a boost in test accuracy, a benefit that is not seen when skip-connections are omitted. For example, increasing sub-network depth from L=3 to L=4 leads to a boost in accuracy in the NeuraLUT model, whereas the accuracy drops if the skip-connections are omitted.

2) Latency and area: We have also investigated Neura-LUT's performance in terms of latency and area on the MNIST dataset. Models of different sizes were selected and tested

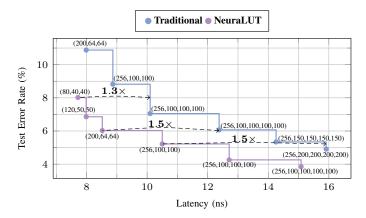

Fig. 6: Test error rate vs latency trade-off study, highlighting the top-performing runs across 10 seeds, with labeled L-LUTs per hidden layer. NeuraLUT features a fixed sub-network of N=16, L=4, S=2.

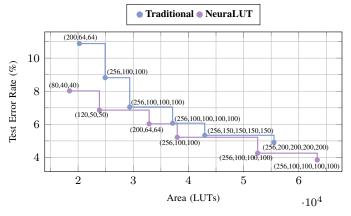

Fig. 7: Test error rate vs area trade-off study for the models in Figure 6. NeuraLUT's improved Pareto frontier highlights that the gains in latency shown in Figure 6 are accompanied by an decrease in area cost.

under both Traditional (N=1, L=1, S=0) and NeuraLUT (N=16, L=4, S=2) settings. Subsequently, the best design points were chosen to construct Pareto frontiers for latency vs. test error rate (Figure 6) and area vs. test error rate (Figure 7). The latency and the area are collected post Place & Route. It is important to note that each L-LUT layer is evaluated in one clock cycle, therefore the latency of the design is directly proportional to the number of layers.

In Figure 6, significant latency reductions are evident for NeuraLUT models compared to traditional models for the same test accuracy. Reductions range from at least  $1.3\times$  to up to  $1.5\times$ . Furthermore, NeuraLUT models demonstrate less pronounced increases in test error rate when circuit-level L-LUTs are reduced. For instance, reducing the network size from (256,100,100,100,100) L-LUTs to (200,64,64) L-LUTs results in a 2.18 percentage-point increase in error for NeuraLUT compared to a 4.81 percentage-point increase for traditional models. This highlights the ability of hidden sub-

networks in NeuraLUT to mitigate accuracy drops caused by reductions in L-LUTs, suggesting increasing advantages as network width and depth become constrained.

In Figure 7, NeuraLUT's Pareto frontier consistently outperforms the Pareto frontier of the traditional models, highlighting that NeuraLUT is not only latency-efficient, but it is also area-efficient. When the size of the L-LUTs matches or is smaller than that of the P-LUTs on the FPGA, the total LUT utilization for the traditional and NeuraLUT models is the same. However, as the size of the L-LUTs exceeds that of the P-LUTs in this case study, the LUT utilization is influenced by the size of the P-LUT circuits generated by Verilog for each L-LUT. We observe in Figure 7 that NeuraLUT implementations may require more P-LUTs LUTs for the same L-LUT model compared to traditional models, as a consequence of the fact that the L-LUTs offer less opportunity for logic simplification when they encode a more complex function. Nevertheless, this increase in LUTs is outweighed by reductions in model size such that for equivalent accuracy, NeuraLUT utilizes less area compared to traditional NNs.

# B. Comparison with prior work

We assess NeuraLUT based on accuracy, logic utilization, maximum frequency, and latency. However, our methodology targets edge device applications with a shared emphasis on low latency and area, hence we introduce another metric in our evaluation: the area-delay product.

We trained NeuraLUT using various model architectures and identified the ones that achieved comparable test accuracy to prior works. The selected models are detailed in Table II.

1) MNIST: In our evaluation, we benchmarked NeuraLUT's performance on the MNIST dataset against state-of-the-art results from existing work on ultra-low latency implementations. We compared it with the performance of PolyLUT on the HDR model [6], the values reported by FINN [13] on the SFC-max model (a binary and fully unfolded implementation), and the results of hls4ml [1] utilizing a ternary neural network model. The evaluation outcomes are detailed in Table III.

For this dataset, we employed the HDR-5L model, featuring a 5-layer circuit-level architecture comprising 4-layer subnetworks with 2 skip connections. Achieving the same accuracy or more, we outperform all prior work across all metrics. Compared to PolyLUT, FINN, and hls4ml, we achieved significant reductions in the area-delay product by 1.7×, 42.8×, and 74.9×, respectively. Our advantage over FINN and hls4ml is attributed to concealing all the computational components and dense parts of the network within LUTs, therefore reducing the number of logic and exposed datapaths to a minimum. Against PolyLUT, we achieve improved implementations due to the efficient handling of function complexity within the L-LUTs.

2) Jet Substructure: For the evaluation of NeuraLUT on the Jet Substructure dataset, we divided our analyses into two segments aimed at different test accuracies (Table III). The first segment focuses on achieving a lower test accuracy, comparing our method with PolyLUT's JSC-M Lite model [6]

TABLE II: Model architectures used for evaluation (Table III).

| Dataset          | Model Name | L-LUTs per Layer       | $\boldsymbol{\beta}$ | F | L | N  | S | Exceptions             |

|------------------|------------|------------------------|----------------------|---|---|----|---|------------------------|

| MNIST            | HDR-5L     | 256, 100, 100, 100, 10 | 2                    | 6 | 4 | 16 | 2 |                        |

| Jet substructure | JSC-2L     | 32, 5                  | 4                    | 3 | 4 | 8  | 2 |                        |

| Jet substructure | JSC-5L     | 128, 128, 128, 64, 5   | 4                    | 3 | 4 | 16 | 2 | $\beta_0 = 7, F_0 = 2$ |

TABLE III: Evaluation of NeuraLUT on the MNIST and Jet Substructure tagging datasets. Bold indicates best in class.

|                          |                                 | Accuracy | LUT    | FF              | DSP | BRAM | $\mathbf{F}_{\text{max}}$ | Latency | $Area{\times}Delay$   |

|--------------------------|---------------------------------|----------|--------|-----------------|-----|------|---------------------------|---------|-----------------------|

|                          |                                 | Accuracy | Lei    | r.r             | DSI | DKAM | (MHz)                     | (ns)    | $(LUT \times ns)$     |

| MNIST                    | NeuraLUT (HDR-5L)               | 96%      | 54798  | 3757            | 0   | 0    | 431                       | 12      | $6.6 	imes 10^5$      |

|                          | PolyLUT [6]                     | 96%      | 70673  | 4681            | 0   | 0    | 378                       | 16      | $11.3\times10^5$      |

|                          | FINN [13]                       | 96%      | 91131  | -               | 0   | 5    | 200                       | 310     | $282.5\times10^{5}$   |

|                          | hls4ml [14]                     | 95%      | 260092 | 165513          | 0   | 0    | 200                       | 190     | $494.2 \times 10^{5}$ |

| Jet substructure tagging | NeuraLUT (JSC-2L)               | 72%      | 4684   | 341             | 0   | 0    | 727                       | 3       | $1.4\times10^4$       |

|                          | PolyLUT [6]                     | 72%      | 12436  | 773             | 0   | 0    | 646                       | 5       | $6.2 \times 10^4$     |

|                          | LogicNets [8] <sup>a</sup>      | 72%      | 37931  | 810             | 0   | 0    | 427                       | 13      | $49.3 \times 10^{4}$  |

| Jet substructure tagging | NeuraLUT (JSC-5L)               | 75%      | 92357  | 4885            | 0   | 0    | 368                       | 14      | $1.3 	imes 10^6$      |

|                          | PolyLUT [6]                     | 75%      | 236541 | 2775            | 0   | 0    | 235                       | 21      | $5 \times 10^6$       |

|                          | Duarte et al. [1]               | 75%      | 887    | 97 <sup>b</sup> | 954 | 0    | 200                       | 75      | $6.7 \times 10^6$     |

|                          | <b>Fahim</b> <i>et al.</i> [10] | 76%      | 63251  | 4394            | 38  | 0    | 200                       | 45      | $2.8 \times 10^6$     |

<sup>&</sup>lt;sup>a</sup>New results can be found on the LogicNets GitHub page.

and LogicNets' JSC-M model [8]. In the second segment, we evaluate our approach against PolyLUT's HDR model [6], as well as implementations proposed by Duarte *et al.* [1] and Fahim *et al.* [10].

NeuraLUT's JSC-2L, comprising only two very shallow layers, achieves the same accuracy as PolyLUT and LogicNets while showcasing impressive reductions of  $4.4\times$  and  $35.2\times$  in the area-delay product, respectively. This aligns with the findings of the case study, underscoring the efficacy of NeuraLUT's highly expressive L-LUTs in restoring precision within highly constrained circuit-level networks.

NeuraLUT's JSC-5L, reaches the lowest latency and it is more efficient in minimizing the area-delay product compared to PolyLUT, the work by Duarte  $et\ al.$  [1] and the work of Fahim  $et\ al.$  [10] reaching reductions of  $3.8\times$ ,  $5.2\times$ , and  $2.2\times$ , respectively. NeuraLUT achieves this without utilizing DSPs at the expense of slightly higher LUT utilization compared to the works of Duarte  $et\ al.$  [1] and Fahim  $et\ al.$  [10].

# V. CONCLUSION AND FURTHER WORK

In conclusion, our work introduces a novel approach to LUT-based DNN acceleration, which involves mapping to L-LUTs entire sub-networks of arbitrary topology rather than individual neurons. This strategy offers greater precision to LUT-based models, resulting in lower-latency networks with improved function expressivity. By incorporating skip-connections within partitions, we mitigate challenges like van-

ishing gradients, enabling the training of deeper sub-networks while maintaining efficiency. Our proposed methodology is validated through experiments on latency-critical tasks such as jet substructure tagging and digit classification using MNIST, showcasing significant improvements in the area-delay product while preserving accuracy. Overall, our contributions offer valuable insights into enhancing LUT-based co-design for real-time applications.

Although NeuraLUT's sub-networks are dense and full precision, they are limited to a small number of low precision inputs. This constraint originates from the exponential scaling of L-LUTs, inherited from traditional LUT-based approaches. Consequently, restrictions are imposed on both input number and precision, hampering direct application to very large neural networks.

A possible next step is to explore automated search techniques like Neural Architecture Search (NAS) to optimize NeuraLUT's circuit-level topology or sub-network topology. NAS can maximize performance while addressing L-LUT constraints, enhancing efficiency, and unlocking the full potential of NeuraLUT's flexibility.

<sup>&</sup>lt;sup>b</sup>Paper reports "LUT+FF".

#### REFERENCES

- J. Duarte et al., "Fast inference of deep neural networks in FPGAs for particle physics," *Journal of Instrumentation*, vol. 13, no. 7, p. P07027, Jul. 2018, doi: 10.1088/1748-0221/13/07/P07027.

- [2] T. Murovič and A. Trost, "Genetically optimized massively parallel binary neural networks for intrusion detection systems," *Computer Communications*, vol. 179, no. 7, pp. 1–10, Nov. 2021, doi: 10.1016/j.comcom.2021.07.015.

- [3] A. C. Therrien, R. Herbst, O. Quijano, A. Gatton, and R. Coffee, "Machine Learning at the Edge for Ultra High Rate Detectors," in 2019 IEEE Nuclear Science Symposium and Medical Imaging Conference (NSS/MIC), 2019, pp. 1–4, doi: 10.1109/NSS/MIC42101.2019.9059671.

- [4] M. M. H. Shuvo, S. K. Islam, J. Cheng, and B. I. Morshed, "Efficient Acceleration of Deep Learning Inference on Resource-Constrained Edge Devices: A Review," *Proceedings of the IEEE*, vol. 111, no. 1, pp. 42–91, Jan. 2023, doi: 10.1109/JPROC.2022.3226481.

- [5] E. Wang et al., "Deep Neural Network Approximation for Custom Hardware," ACM Computing Surveys, vol. 52, no. 2, pp. 1–39, May 2019, doi: 10.1145/3309551.

- [6] M. Andronic and G. A. Constantinides, "PolyLUT: Learning Piecewise Polynomials for Ultra-Low Latency FPGA LUT-based Inference," in 2023 International Conference on Field Programmable Technology (ICFPT), 2023, pp. 60–68.

- [7] E. Wang, J. J. Davis, P. Y. K. Cheung, and G. A. Constantinides, "LUTNet: Rethinking Inference in FPGA Soft Logic," in 2019 IEEE 27th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM). San Diego, CA, USA: IEEE Computer Society, May 2019, pp. 26–34, doi: 10.1109/FCCM.2019.00014.

- [8] Y. Umuroglu, Y. Akhauri, N. J. Fraser, and M. Blott, "LogicNets: Co-Designed Neural Networks and Circuits for Extreme-Throughput Applications," in 2020 30th International Conference on Field-Programmable Logic and Applications (FPL). Gothenburg, Sweden: IEEE Computer Society, Sep. 2020, pp. 291–297, doi: 10.1109/FPL50879.2020.00055.

- [9] M. Nazemi, G. Pasandi, and M. Pedram, "Energy-Efficient, Low-Latency Realization of Neural Networks through Boolean Logic Minimization," in *Proceedings of the 24th Asia and South Pacific Design Automation Conference*. Tokyo, Japan: Association for Computing Machinery, Jan. 2019, p. 274–279, doi: 10.1145/3287624.3287722.

- [10] F. Fahim et al., "hls4ml: An Open-Source Codesign Workflow to Empower Scientific Low-Power Machine Learning Devices," in TinyML Research Symposium'21, San Jose, CA, USA, Mar. 2021. [Online]. Available: https://doi.org/10.48550/arXiv.2103.05579

- [11] S. Summers et al., "Fast inference of Boosted Decision Trees in FPGAs for particle physics," *Journal of Instrumentation*, vol. 15, no. 5, p. P05026, May 2020, doi: 10.1088/1748-0221/15/05/P05026.

- [12] C. N. Coelho, Jr. et al., "Automatic heterogeneous quantization of deep neural networks for low-latency inference on the edge for particle detectors," *Nature Machine Intelligence*, vol. 3, no. 6, pp. 675–686, Jun. 2021, doi: 10.1038/s42256-021-00356-5.

- [13] Y. Umuroglu et al., "FINN: A Framework for Fast, Scalable Binarized Neural Network Inference," in Proceedings of the 2017 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays, ser. FPGA '17. Monterey, CA, USA: Association for Computing Machinery, Feb. 2017, p. 65–74, doi: 10.1145/3020078.3021744.

- [14] J. Ngadiuba et al., "Compressing deep neural networks on FPGAs to binary and ternary precision with hls4ml," Machine Learning: Science and Technology, vol. 2, no. 1, p. 015001, Dec. 2020, doi: 10.1088/2632-2153/aba042.

- [15] E. Wang, J. J. Davis, P. Y. K. Cheung, and G. A. Constantinides, "Lutnet: Learning fpga configurations for highly efficient neural network inference," 2020.

- [16] A. Prabhu, G. Varma, and A. Namboodiri, "Deep Expander Networks: Efficient Deep Networks from Graph Theory," in *Computer Vision - ECCV 2018*, V. Ferrari, M. Hebert, C. Sminchisescu, and Y. Weiss, Eds. Munich, Germany: Springer International Publishing, Oct. 2018, pp. 20–36, doi: 10.1007/978-3-030-01261-8\_2.

- [17] Y. Bengio, P. Simard, and P. Frasconi, "Learning long-term dependencies with gradient descent is difficult," *IEEE Transactions on Neural Networks*, vol. 5, no. 2, pp. 157–166, 1994.

- [18] X. Glorot and Y. Bengio, "Understanding the difficulty of training deep feedforward neural networks," in *Proceedings of the Thirteenth International Conference on Artificial Intelligence and Statistics*, ser. Proceedings of Machine Learning Research, Y. W. Teh and M. Titterington, Eds., vol. 9. Chia Laguna Resort, Sardinia, Italy: PMLR, 13–15 May 2010, pp. 249–256.

- [19] K. He, X. Zhang, S. Ren, and J. Sun, "Deep Residual Learning for Image Recognition," 2015.

- [20] M. Lin, Q. Chen, and S. Yan, "Network In Network," in *International Conference on Learning Representations (ICLR)* 2014, 2014. [Online]. Available: https://doi.org/10.48550/arXiv.1312.4400

- [21] G. V. Cybenko, "Approximation by superpositions of a sigmoidal function," *Mathematics of Control, Signals and Systems*, vol. 2, pp. 303–314, 1989.

- [22] K. Hornik, "Approximation capabilities of multilayer feedforward networks," *Neural Networks*, vol. 4, no. 2, pp. 251–257, 1991.

- [23] I. Loshchilov and F. Hutter, "Fixing Weight Decay Regularization in Adam," in 7th International Conference on Learning Representations, New Orleans, LA, USA, May 2019. [Online]. Available: https://openreview.net/forum?id=Bkg6RiCqY7

- [24] —, "SGDR: Stochastic Gradient Descent with Warm Restarts," in 5th International Conference on Learning Representations, Toulon, France, Apr. 2017. [Online]. Available: https://openreview.net/forum?id=Skq89Scxx

- [25] A. Pappalardo, "Brevitas: neural network quantization in PyTorch," Jun. 2020, [Accessed: May 12, 2023]. [Online]. Available: https://github.com/Xilinx/brevitas

- [26] Y. LeCun, C. Cortes, and C. J. Burges, "The MNIST database of handwritten digits." [Online]. Available: http://yann.lecun.com/exdb/mnist/