# Taking GPU Programming Models to Task for Performance Portability

Joshua H. Davis<sup>†</sup>, Pranav Sivaraman<sup>†</sup>, Joy Kitson<sup>†</sup>, Konstantinos Parasyris<sup>\*</sup>, Harshitha Menon<sup>\*</sup>, Isaac Minn<sup>†</sup>, Giorgis Georgakoudis<sup>\*</sup>, Abhinav Bhatele<sup>†</sup>

†Department of Computer Science, University of Maryland \*Center for Applied Scientific Computing, Lawrence Livermore National Laboratory

Abstract—Portability is critical to ensuring high productivity in developing and maintaining scientific software as the diversity in on-node hardware architectures increases. While several programming models provide portability for diverse GPU platforms, they don't make any guarantees about performance portability. In this work, we explore several programming models CUDA, HIP, Kokkos, RAJA, OpenMP, OpenACC, and SYCL, to study if the performance of these models is consistently good across NVIDIA and AMD GPUs. We use five proxy applications from different scientific domains, create implementations where missing, and use them to present a comprehensive comparative evaluation of the programming models. We provide a Spack scripting-based methodology to ensure reproducibility of experiments conducted in this work. Finally, we attempt to answer the question - to what extent does each programming model provide performance portability for heterogeneous systems in real-world

*Index Terms*—performance portability, heterogeneous systems, programming models

#### I. Introduction

Heterogeneous on-node architectures have come to dominate the design of high performance computing (HPC) platforms. Nine of the top ten systems in the November 2023 TOP500 list, and ~37% of the full list, employ co-processors or accelerators [1]. Further, there is a diverse set of specific architectures in use, supplied by a range of vendors. The current top ten systems include CPUs from AMD, Fujitsu, IBM, and Intel, as well as GPUs from AMD, NVIDIA, and Intel. A similarly diverse range of programming models have emerged, all aiming to allow scientific application developers to write their code once and run it on any system. Programming models such as OpenMP [2], RAJA [3], and Kokkos [4] act as *portability layers*, bridging the gap between the programmer's high-level expression of an algorithm and the low-level implementation of that algorithm for correct execution on a given target architecture.

Running scientific applications efficiently on HPC machines requires more than just *functional* portability; code not only needs to execute correctly on a range of target platforms, it needs to perform well on those platforms, ideally without incurring the technical debt of platform-specific implementations. This need for *performance* portability has motivated the development of several existing on-node programming models. However, choosing a programming model for porting a CPU-only application to GPUs is a major commitment, requiring

significant time for developer training and programming. If a programming model turns out to be ill-suited for an application, and results in unacceptable performance, then that investment is wasted.

Thus, application developers would benefit from possessing a deeper understanding of the performance portability behaviors of different programming models on modern GPU platforms before porting their application to a particular framework. Nevertheless, it remains an open question how effective each programming model is at enabling performance portability, as well as how to precisely define and measure performance portability itself. Although developers' experiences comparing the performance portability of several models on a single application are valuable, we have observed that opensource applications or even proxy applications implemented in a majority of the available programming models are uncommon and difficult to find. Further, a single smaller application or benchmark implemented in most programming models is unlikely to be representative of the diverse and complex production applications typically run on HPC systems. Finally, conducting exhaustive combinatorial studies of programming model, compiler, system, and application combinations is a significant undertaking, as each programming model usually requires unique combinations of compilers flags and libraries for any given system.

In this paper, we seek to ease the burden on developers when choosing a programming model by providing a comprehensive empirical study of the performance portability of programming models on GPU-based platforms. We use a variety of proxy applications implemented in the most popular programming models, and benchmark them across multiple leadership-class production supercomputers. By selecting several proxy applications that are representative of production codes, we enable realistic comparisons of the performance portability of several programming models across different architectures. We study five proxy applications from different scientific domains, create implementations where missing, and comprehensively evaluate differences between these programming models.

We present a Spack-based [5] environment and scripting system to significantly lower the barriers to enter for new performance portability studies. This system encapsulates our methodology for systematically building, running and benchmarking a suite of applications in several programming mod-

$TABLE\ I$  Summary of programming models used in this study. Vendor support may be subject to change in the future.

| Prog. Model Year Introduced                                                                                                                                                                     | Developing Org.                                                                       | Category                                                                                                                           | GPU Vendors Supported                                                                                              |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|

| OpenMP         1997           OpenACC         2011           Kokkos         2017           RAJA         2019           SYCL         2014           HIP         2016           CUDA         2007 | OpenMP ARB OpenACC Org. Sandia Nat'l Lab Livermore Nat'l Lab Khronos Group AMD NVIDIA | Directive-based Directive-based C++ abstraction lib. C++ abstraction lib. Language extension Language extension Language extension | NVIDIA, AMD, Intel<br>NVIDIA, AMD<br>NVIDIA, AMD, Intel<br>NVIDIA, AMD, Intel<br>NVIDIA, AMD, Intel<br>NVIDIA, AMD |  |  |

els, in an manner which can be adapted for future studies. Our comparative evaluation of model performance on this benchmark includes specific insights into why certain programming models perform well or poorly for particular applications on different target systems. To the best of our knowledge, this is one of the most comprehensive performance portability studies to date, in terms of the breadth of programming models and applications studied, the level of detail in the analysis of performance results, and in being conducted on large-scale production supercomputers.

To summarize, our contributions include the following:

- We evaluate the performance portability enabled by seven different programming models using a diverse set of five proxy applications benchmarked across state-of-the-art NVIDIA and AMD GPUs in production supercomputers.

We provide several additional implementations of existing proxy applications in new programming models to ensure full coverage of programming models across applications.

- We describe a methodology employing Spack scripting and environment tools [5] to easily manage the process of building and running all 7 × 5 = 35 versions across four supercomputing platforms, each with unique software stacks. We provide this software to the community in order to substantially reduce the effort required to reproduce or extend our study.

- We evaluate the utility of the existing performance portability metric [6],  $\Phi$ , for summarizing the results of our study, comparing it with our more granular analysis.

- We conduct a thorough analysis of the reasons for key outliers in the performance portability cases studied, and describe and test optimizations that improve performance portability in some cases.

# II. BACKGROUND ON PORTABLE PROGRAMMING MODELS

In this section we provide relevant background information on the various programming models we evaluate. Table I displays key information about each programming model. HIP and CUDA act as our baselines in this study, as they are the native programming model for AMD and NVIDIA devices, respectively. Below, we describe the key characteristics of each category of programming model.

# A. Directive-based models

OpenMP and OpenACC are directive-based models. They provide compiler directives, or *pragmas*, to parallelize or

offload code. They are typically standard specifications implemented by a compiler front-end and a runtime library to implement parallel or offloaded execution that abstracts the underlying hardware architecture. Directive-based models are usually less verbose and less intrusive, as users can often annotate existing code with minimal refactoring. This facilitates incremental development.

#### B. C++ abstraction libraries

Kokkos and RAJA are C++ abstraction libraries. These are template-based C++ libraries that provide high-level functions and data types. Users write their code directly employing these data types and typically structure GPU code as lambdas to pass into library function calls. The library translates the user code to a device backend such as CUDA, HIP, or OpenMP at compile-time or runtime. Note that Kokkos provides both memory and compute abstractions, while RAJA provides compute abstractions and users must employ the related Umpire or CHAI libraries to abstract memory management.

# C. Language extensions

SYCL, HIP, and CUDA are language extensions, which add features to the base language (C++, C, and/or Fortran) for programming heterogeneous systems. SYCL and HIP are open standards, while CUDA is proprietary. The language extensions we consider are more verbose than the other programming models. Users call runtime functions to manage memory and write functions that they then invoke as kernels to offload execution. SYCL provides multiple methods of memory management, including *explicit USM*, which uses CUDA or HIP style runtime calls to move and allocate data, or the buffer/accessor API, which is more implicit, allowing the compiler to schedule data movement.

# III. RELATED WORK

Several studies on programming language extensions [2], [7], models [8], and libraries [3], [4] have been designed to assist developers achieve performance portability. Additionally, several studies have assessed the portability of certain frameworks. We categorize the related work on empirical performance portability studies into three groups: metric studies, application or programming model studies, and broader studies that are not scoped to a particular model or app. In this section, we provide an overview of recent work in each category.

# A. Studies of performance portability metrics

Pennycook et al. [6], [9]–[12] propose the metric  $\Phi$  for performance portability, defining it as the harmonic mean of the performance efficiencies of an application across different platforms. Daniel et al. [13] propose an alternative metric,  $P_D$ , which accounts for problem size, and Marowka [14], [15] compares  $\Phi$  with  $\overline{\Phi}$ , a similar metric that uses the arithmetic mean instead of the harmonic mean.

# B. Studies examining the portability of individual application categories or programming models

A number of studies compare performance portable programming models for either specific categories of applications [16]–[24] or specific programming models [7], [25]–[28]. For instance, Dufek et al. [21] compare Kokkos and SYCL for the Milc-Dslash benchmark, while Rangel et al. [24] examine the portability of a SYCL implementation of CRK-HACC. Other studies investigate the performance portability achievable using a particular programming model. Brunst et al. [26] benchmark the 2021 SPEChpc suite, which contains nine mini applications implemented in OpenMP and OpenACC, on Intel CPUs and NVIDIA and AMD GPUs. Kuncham et al. [27] evaluate the relative performance of SYCL and CUDA on the NVIDIA V100 using BabelStream, Mixbench, and Tiled Matrix-Multiplication.

While these studies provide useful information to developers working on similar applications or those interested in specific programming models, making more general statements about programming models themselves requires a more comprehensive evaluation of a diverse set of case studies.

# C. Broader performance portability studies

Deakin et al. [29], [30] present performance portability studies of five programming models across a wide range of hardware architectures, using BabelStream, TeaLeaf, CloverLeaf, Neutral, and MiniFMM. More recent papers by Deakin et al. [31], [32] focus on more specific problems such as reductions and GPU to CPU portability. Lin et al. [33] evaluate implementations of C++17 StdPar against five models on AMD devices. While these studies provide performance portability comparisons across platforms, applications, and models, they do not include RAJA and sometimes omit HIP and OpenACC. Furthermore, they do not provide extensive analysis of the reasons for performance differences between programming models or ways to address differences.

Several other studies are similar in scope but different in focus. Kwack et al. [34] evaluate portability development experiences for three full applications and three proxy applications across GPUs from multiple vendors. Harrell et al. [35] study performance portability alongside developer productivity. However, in these studies each application is only ported to a single portable programming model. This makes it difficult to draw conclusions about each programming model's relative suitability to particular applications. Koskela et al. [36] provide six principles for reproducible portability benchmarking, along with a demonstration of these principles in a Spack+Reframe

CI infrastructure for a study of BabelStream on some CPU architectures and an NVIDIA V100.

Despite the abundance of studies on various aspects of performance portability, they suffer from several limitations. Some are limited to a single application or benchmark, making it difficult to do a cross-application comparison of programming models. Others are focused on a single programming model, making it challenging to draw comparisons between different programming models. Our work aims to provide a comprehensive analysis of performance portability across multiple applications and libraries, each implemented in several different programming models and executed on production supercomputers. Additionally, unlike prior work, we conduct a detailed investigation of the performance of the most notable outliers we identify among our results, providing users with a better understanding of how application characteristics impact the performance portability of each model as well as potential workarounds to avoid portability pitfalls. Finally, prior studies do not provide a comprehensive description of the build and run infrastructure used to collect their results, leaving the task of consistently building applications on a wide range of hardware platforms with complex library and compiler flag dependencies to the reader. Our study is the first to apply the principles of reproducible benchmarking [36] in a comprehensive study of performance-portable programming models.

# IV. METHODOLOGY FOR EVALUATING PERFORMANCE PORTABILITY ON GPU PLATFORMS

In this section, we outline our strategy for comprehensively comparing programming models that provide portability on GPU platforms, explaining our choices of programming models, proxy applications, hardware platforms, and metrics.

#### A. Choice of programming models

Our goal in this work is to empirically compare the performance portability provided by popular programming models. In Section II, we described three categories of programming models with a few examples in each category. We identified those representative models by surveying a broad range of proxy applications in order to determine how common existing implementations of each model were. Once armed with that knowledge, we decided to focus on CUDA, HIP, Kokkos, OpenACC, OpenMP, RAJA, and SYCL, as they were most commonly found in the proxy applications we surveyed.

# B. Choice of proxy applications

From a survey of a range of sources, including the ECP Proxy Apps suite [41], the NERSC Proxy suite [42] and the Mantevo Applications Suite [43], we identify five proxy applications that represent the range of typical GPU scientific computing workloads. These five applications include a pure memory bandwidth benchmark as well as proxy applications. They range from highly compute-intensive (miniBUDE) to highly memory-intensive (BabelStream), and also include one representative from each of the three large proxy application

Summary of proxy applications and benchmarks used in this study as well as which programming model ports and Spack packages required updates or creation by the authors. Here, E = already exists, M = modified by us, C = created by us.

|                  |                    |                                  |                                 |         | cup | P R | <b>&amp;</b> | 0° JA | ~  | MP er | ACC 1CC | r spack |

|------------------|--------------------|----------------------------------|---------------------------------|---------|-----|-----|--------------|-------|----|-------|---------|---------|

| Application      | Domain(s)          | Method(s)                        | Publishing Org.                 | Suite   | 0   | HIR | 40,          | 2/2   | Ob | Ob    | 5       | Spr     |

| XSBench [37]     | Nuclear physics    | Monte Carlo                      | Argonne<br>Nat'l Lab            | ECP     | Е   | Е   | C            | C     | Е  | C     | M       | M       |

| BabelStream [22] | N/A                | Bandwidth benchmark              | Univ. of Bristol                | N/A     | Е   | E   | Е            | M     | E  | Е     | Е       | M       |

| CloverLeaf [38]  | Hydrodynamics      | Structured grid                  | Atomic Weapons<br>Establishment | Mantevo | Е   | E   | Е            | C     | E  | C     | M       | M       |

| su3_bench [39]   | Particle physics   | Structured grid, dense lin. alg. | Lawrence Berkeley<br>Nat'l Lab  | NERSC   | Е   | E   | E            | C     | E  | Е     | Е       | C       |

| miniBUDE [40]    | Molecular dynamics | N-body                           | Univ. of Bristol                | N/A     | Е   | E   | Е            | M     | E  | E     | M       | C       |

TABLE III

ARCHITECTURAL DETAILS OF THE PLATFORMS USED IN THIS PAPER. NOTE THAT WE USE THE HIGH-MEMORY NODES ON SUMMIT, AND LIST THE DETAILS FOR ONE GCD OF AN MI250X FOR FRONTIER.

| System     | CPU Model              | CPU Cores/node | CPU Memory (GB) | GPU Model   | GPU Memory (GB) | Hosting Facility     |

|------------|------------------------|----------------|-----------------|-------------|-----------------|----------------------|

| Summit     | IBM POWER9             | 44             | 512             | NVIDIA V100 | 32*             | OLCF (Oak Ridge)     |

| Perlmutter | AMD EPYC 7763          | 64             | 256             | NVIDIA A100 | 40              | NERSC (Berkeley Lab) |

| Corona     | AMD Rome               | 48             | 256             | AMD MI50    | 32              | LC (Livermore)       |

| Frontier   | AMD Opt. 3rd Gen. EPYC | 64             | 512             | AMD MI250X  | 64*             | OLCF (Oak Ridge)     |

suites we surveyed. These proxy applications include hydrodynamics (CloverLeaf), molecular dynamics (miniBUDE), nuclear physics (XSBench), and particle physics (su3\_bench) codes, and the structured grid (CloverLeaf and su3\_bench), dense linear algebra (su3\_bench), n-body (miniBUDE) and Monte Carlo (XSBench) computational methods. miniBUDE is compute-bound and the rest are memory-bound.

CloverLeaf, miniBUDE, and XSBench were missing implementations in some programming models, and we created these in order to obtain full coverage of the space of application and model combinations. Table II summarizes the key details of each proxy application and which programming model ports we created or modified in this study. Here, modifications are adjustments to the memory management library or style to ensure portability and ease of timing. Below, we describe the five proxy applications that we use in this study:

**BabelStream** is a memory bandwidth benchmark with five kernels: copy, add, mul, triad, and dot [22]. The dot kernel includes a reduction operation, a challenging operation for some programming models [44].

CloverLeaf is is a 2D structured compressible Euler equation solver, with 14 kernels [38]. The advec\_mom, advec\_cell, PdV, and calc\_dt kernels are typically the most intensive, and calc\_dt contains a reduction.

miniBUDE is a proxy for the Bristol University Docking Engine (BUDE), a molecular dynamics simulation designed to simulate molecular docking for drug discovery [40]. miniBUDE computes the energy field for a single configura-

tion of a protein repeatedly.

**XSBench** is a proxy for OpenMC [37]. XSBench runs OpenMC's macroscopic cross-section lookup kernel, in which we use the event-based transport method with the hash-based grid as it is preferred for GPUs. XSBench consists of one kernel that computes a large number of lookups.

**su3\_bench** is a proxy application of the MILC Lattice Quantum Chromodynamics code [39]. It implements the SU(3) matrix-matrix multiply routine in its lone kernel.

# C. Choice of hardware platforms

Evaluating performance portability requires selecting a range of hardware platforms with diverse hardware architectures. An important goal of this study is to evaluate performance portability on production GPU-based supercomputers, because eight out of the top ten systems on the Top500 list use either NVIDIA or AMD GPUs as of November 2023 [1]. We select four different supercomputers for our experiments: Summit and Frontier at ORNL, Perlmutter at NERSC, and Corona at LLNL (architectural details in Table III). These systems cover the majority of the GPU architectures in the top ten systems. Frontier and Summit are in the top ten, and Perlmutter is in the top fifteen. Additionally, we include Corona (AMD MI50) to provide additional context with older AMD hardware. We note that our Spack environment-based methodology minimizes the effort required to deploy our suite of portability tests on a new system. Note that for Frontier's MI250X GPUs we run on one Graphics Compute Die (GCD) but refer to the GCD as a GPU in consistency with the system's documentation.

#### D. Measurement and evaluation strategy

In this study, we modify applications where necessary to consider both the efficiency of the generated GPU kernel(s) and that of any data movement between host and device needed to run the application. However, as will be discussed in Sec. VII, the impact of data movement on overall execution time is minimal and not presented in detail.

For all applications we add a runtime option to specify a number of warmup iterations at the start of the simulation which are excluded from timing. XSBench originally runs only for only a single iteration, so we add a loop that repeatedly runs the kernel a number of times specified on the command line, in order to reduce variability and ensure consistency across applications.

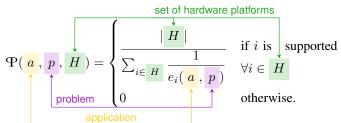

With the figure-of-merit chosen for each application, we can also derive additional higher-level metrics about performance portability for each combination of application and programming model. In this work, we use  $\mathfrak{P}$  with application efficiency proposed by Pennycook et al. [6].  $\mathfrak{P}$  is defined, for some application  $\mathfrak{a}$ , problem  $\mathfrak{p}$ , set of hardware platforms  $\mathfrak{H}$ , and measure of application efficiency e, as:

Intuitively, this is the harmonic mean of the application efficiencies of an application running a single problem across a set of hardware platforms. The application efficiency  $e_i(a,p)$  of an application a solving problem p is the ratio  $\frac{t_{min}}{t}$ , where t is the runtime of a solving p on the particular hardware i, and  $t_{min}$  the best observed runtime across all variants of a solving p on i.

# E. Spack-based deployment and run scripting

In our experiments, we place great importance on ensuring all compilers, dependency versions, and flags are uniform. We accomplish this with Spack [5], a popular HPC package manager. For each system, we have a single Spack environment file which specifies the exact compiler, app, and library dependency versions along with any needed flags. As listed in Table II, we have created or updated Spack package files for each proxy app, and where applicable these updates will be provided to the community. The Spack environments created for this project can be easily adapted to any new system, allowing for simple reproduction of our experiments and significantly reducing the extremely time-consuming effort of building every combination of application and programming model

Additionally, we employ Spack Python to develop robust scripting tools for our experiments — we can create jobs with a single-line invocation leveraging Spack's spec syntax to adjust which application, models, or compilers are used,

and save profile data to a CSV format that can be directly read by our plotting scripts. These scripts and environments will be published on GitHub to allow the community to use our portability study methodology. These infrastructural contributions dramatically reduce the effort required to reproduce our results and create new studies of portable programming models.

#### V. PORTING TO NEW PROGRAMMING MODELS

Most of the proxy applications we used provided a working implementation of most of the evaluated programming models. In these existing proxy versions we performed minor modifications to consistently align timing measurements across different programming models. RAJA ports were created for CloverLeaf, XSBench, and su3\_bench and BabelStream and miniBUDE were updated to use Umpire for portable memory allocations.

For all development of additional ports, we maintained similarity in the level of effort applied to creating the new ports, in order to avoid granting an unfair advantage to any particular model arising from excess optimization. Furthermore, we specifically did not tune any GPU kernel launch parameters for any port. For programming models that require the user to specify these values (CUDA, HIP, RAJA, SYCL), we used the default values provided by the respective proxy application developers. For programming models that can select their own default parameter values (OpenMP, OpenACC, Kokkos), we allowed the model to do so if compatible with the existing application code. Our results reflect "out of the box" performance that a user would encounter with minimal porting effort.

In the following subsections, we discuss the porting experiences for each programming model we worked with. Table II summarizes the development efforts we undertook for this study. We plan to merge these contributions to their respective upstream repositories.

# A. Porting to OpenACC

Since OpenMP ports already existed for XSBench and su3\_bench, for example, the process of creating a similar OpenACC port was relatively easy, requiring just a one-to-one conversion of the relevant OpenMP pragmas to OpenACC. For example, the OpenMP pragma omp target teams distribute parallel for becomes acc parallel loop. This extremely rote method made our experience with porting from OpenMP to OpenACC very productive.

#### B. Porting to Kokkos

Porting the XSBench code to Kokkos required converting the existing for loop to be a lambda function passed into a Kokkos::parallel\_for call and converting the data structures to be used in Kokkos calls to Kokkos:Views. For example, XSBench's SimulationData struct contains several dynamic arrays which would need to be Views in order to work on the GPU. To avoid rewriting the data setup code,

COMPILERS AND VERSIONS USED FOR BUILDING DIFFERENT PROGRAMMING MODEL IMPLEMENTATIONS ON DIFFERENT PLATFORMS. NOTE WE USE ADAPTIVE CPP 23.10.0 FOR SYCL CLOVER LEAF AND ROCMCC FOR OPENMP SU3 BENCH ON AMD DUE TO IMPROVED PERFORMANCE.

| Prog. Model | Summit           | Perlmutter       | Corona           | Frontier         |

|-------------|------------------|------------------|------------------|------------------|

| CUDA        | GCC 12.2.0       | GCC 12.2.0       | N/A              | N/A              |

| HIP         | N/A              | N/A              | ROCmCC 5.7.0     | ROCmCC 5.7.0     |

| Kokkos      | GCC 12.2.0       | GCC 12.2.0       | ROCmCC 5.7.0     | ROCmCC 5.7.0     |

| RAJA        | GCC 12.2.0       | GCC 12.2.0       | ROCmCC 5.7.0     | ROCmCC 5.7.0     |

| OpenMP*     | NVHPC 24.1       | NVHPC 24.1       | LLVM 17.0.6      | LLVM 17.0.6      |

| OpenACC     | NVHPC 24.1       | NVHPC 24.1       | Clacc 2023-08-15 | Clace 2023-08-15 |

| SYCL*       | DPC++ 2024.01.20 | DPC++ 2024.01.20 | DPC++ 2024.01.20 | DPC++ 2024.01.20 |

we set up the grid data as ordinary C++ dynamic arrays, and then converted the data to Views before copying them to the device and launching the kernel. Listing 1 provides an example. In summary, we construct an unmanaged View in the HostSpace called u\_cocns using the heap memory of the SD.concs array, construct a new View in the device space called SD.d\_concs, and finally deep\_copy the unmanaged host View to the new device View.

Listing 1. Example of converting a C++ dynamic array to a device View for incremental development.

# C. Porting to RAJA

In contrast to Kokkos, the RAJA portability ecosystem uses multiple independent libraries to provide portability. Briefly, the RAJA library provides C++ lambda-capturing to allow developers to express portable computations across architectures. The developer can either use a custom portable memory management library or use Umpire [45], which provides portable memory allocation primitives and memory pools. The hierarchical structure of the RAJA ecosystem can provide greater capability for incremental porting of an existing codebase (i.e., compute first, then data structures), avoiding more extensive refactoring. In our case, this gradual modification was useful for CloverLeaf and XSBench, which had more extensive existing code for managing and initializing data structures. However, we encountered several challenges building the RAJA applications. Relying on multiple independent libraries increases the expertise required and frequency of errors in setting up build systems, a process that is already complicated for a single library containing device kernels. Package managers such as Spack [5] can mitigate these problems for end users, although this solution pushes the responsibility of ensuring the libraries are build and install correctly onto the package maintainers.

#### VI. EXPERIMENTAL SETUP

In this section, we describe the setup for the experiments conducted in this work. We run all the applications on all four machines selected (listed in Table III).

Table IV lists the compilers used with each programming model alongside their versions. We use GCC 12.2.0 as the host compiler on NVIDIA systems and ROCmCC 5.7.0 on AMD. We use CUDA version 12.2 on NVIDIA systems, and HIP 5.7.0 on AMD systems, as well as Kokkos version 4.2.00 and RAJA v2023.06.1. OpenACC, OpenMP, and SYCL are all supported by multiple compilers on the systems where we perform our experiments, so we test all the available compilers for these models<sup>1</sup> and choose the best-performing compiler for each model and system. In all models except SYCL and OpenMP, the best-performing compiler is consistent across applications on each system. For the SYCL port of CloverLeaf, AdaptiveCpp is consistently superior, so we present AdaptiveCpp results for that application and DPC++ for all others. For OpenMP, ROCmCC wins on AMD systems for su3\_bench and Clang wins for all other applications. Note also that we are unable to build CloverLeaf with Clacc due to lack of support for the host\_data clause, and hence we cannot run CloverLeaf on AMD systems with OpenACC.

We select input decks and command line inputs for each proxy application based on recommended settings from their respective developers. When given a choice of problem size, we select the largest representative problem available that fits on all tested GPUs. We also choose the number of iterations for each application to ensure about a minute of execution time, so as to reduce variability. Section IV-D describes how we modify the proxy applications to ensure consistent timings. We present the final command line arguments in Table V.

TABLE V

INPUT PARAMETERS TO THE PROXY APPLICATIONS.

| Application | Input parameters                          |

|-------------|-------------------------------------------|

| BabelStream | -n 1500 -w 150 -s \$((1<<29))             |

| CloverLeaf  | in clover_bm64_mid.in -w 52               |

| su3_bench   | -1 32 -i 100000 -w 10000                  |

| XSBench     | -s large -m event -G hash -n 150 -w 15    |

| miniBUDE    | deck bm2 -p 2wgsize 128<br>-i 10warmups 1 |

Note that for all cases tested the time spent in data movement was negligible (less than 2%) compared to time spent in device kernels, so our result figures present **only** GPU

<sup>1</sup>OpenMP: CLANG, GCC, ROCmCC, NVHPC, CCE; OpenACC: Clacc, GCC, NVHPC; SYCL: DPC++, AdaptiveCpp

kernel time. For all performance results presented we run the application three times and present the average result. Variability is generally low; the largest range of times recorded as a percentage of mean runtime for a case is 3.3%, and the mean is 0.1%. We report total runtime for BabelStream kernels rather than memory bandwidth in order to ensure that "lower is better" across all performance results we present. The values collected can be converted to bandwidth (GB/s) by dividing the total data moved by the time.

# VII. RESULTS AND DISCUSSION

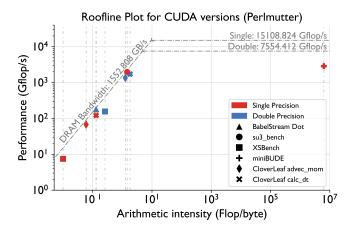

We first present a roofline analysis of the native port implementations of each proxy application to understand their compute and memory behavior. Next we present the results of our detailed performance comparison across programming models, systems, and applications, first in summary and then in depth.

#### A. Roofline analysis

Figure 1 shows the empirical roofline for the NVIDIA A100 GPU on Perlmutter along with the position of the most time-consuming kernel in the CUDA implementations of the five proxy applications in single and double precision where applicable. For BabelStream, this is the dot kernel; for CloverLeaf, this is the advec\_mom and calc\_dt kernels; for miniBUDE, this is the fasten main kernel. XSBench and su3\_bench contain a single kernel each. We can quickly observe that all kernels evaluated are memory-bound except for miniBUDE, which is highly compute-bound. BabelStream is overall the least operationally intense, which is expected given that it is a memory bandwidth benchmark. XSBench also falls relatively on the more memory-bound side, while CloverLeaf and su3\_bench are much closer to the knee point. These kernels are relatively close to the roofline, suggesting these CUDA versions are relatively close to optimal for the algorithms they implement.

Fig. 1. Roofline plot for the most time-consuming kernel in the CUDA versions of each application, run on Perlmutter (NVIDIA A100). Red points are single precision, and blue points are double precision.

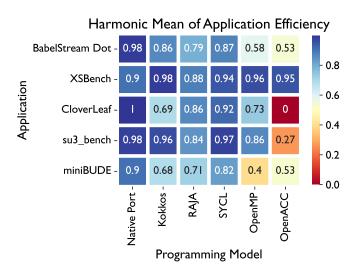

#### B. Performance portability metric

Figure 2 displays the P metric for each programming model and proxy application combination. The "Native Port" column is provided for context, and simply indicates what the metric would report if a team decided to maintain both a HIP and CUDA version of the application. Note that because we were unable to run OpenACC on AMD systems with CloverLeaf, that cell is zero per the official formulation of the metric. For the subset of platforms (Summit and Perlmutter) we were able to run OpenACC on, the value is 0.98. According to P, we observe a strong preference for SYCL, RAJA, and Kokkos as performance portable programming models. Kokkos's difficulties with CloverLeaf appear to be an outlier, as it outperforms RAJA on all other applications except miniBUDE, where it is only slightly behind. Between Kokkos and SYCL, SYCL scores higher more often, and encounters much less difficulty with CloverLeaf and miniBUDE. We will revisit these metric results in comparison to our own observations in Sec. VII-G.

Fig. 2.  $\Phi$  of GPU kernel performance for each programming model and application combination. Applications are listed in ascending order of arithmetic intensity from top to bottom. Note for OpenACC we are unable to compile CloverLeaf on AMD systems.

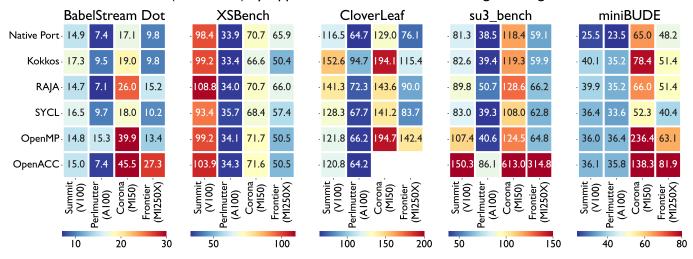

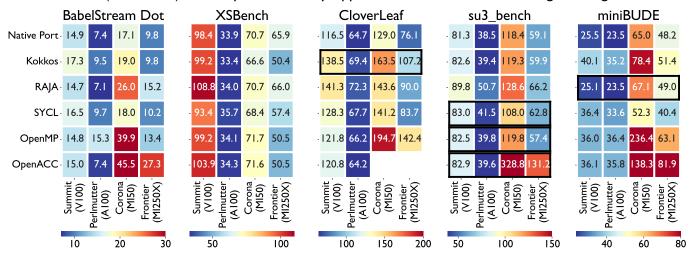

Next, we present performance results for XSBench, su3\_bench, CloverLeaf, and the Dot kernel of BabelStream in Figure 3. We omit the BabelStream Copy, Add, Triad and Mul kernels due to the high degree of consistency across models for those kernels. Each heatmap cell represents the average total **GPU kernel execution time** over three runs of the application, as described in Section IV. Note that while we do measure data movement time, we do not report it here in detail, as it is consistently negligible (<2%) compared to time spent in GPU kernels. The "Native Port" row in each plot represents CUDA performance on Summit and Perlmutter (the NVIDIA systems) and HIP performance on Corona and Frontier (the AMD systems). We organize our initial insights into these results into five observations.

# Runtimes (in seconds) by Application, Architecture, and Programming Model

Fig. 3. Average execution time of all proxy applications across all platforms and programming models. Lower is better.

#### C. Performance of native ports

**Observation 1:** On NVIDIA systems, CUDA often performs at or near the best observed performance.

CUDA is the best or within 3% of the best performing model in eight out of ten cases. For these applications, this is a useful validation of the maturity of the CUDA baseline for each application, and confirms our expectation that the low-level vendor model would be the most performant and portable across GPUs from the same vendor. In one notable exception, RAJA BabelStream Dot on Perlmutter, we observe that RAJA is taking advantage of warp-level primitives in addition to shared memory to perform the reduction, maximizing utilization of hardware-specific features for such operations.

**Observation 2:** On AMD systems, HIP does not always guarantee the best performance.

For most cases on AMD systems, including CloverLeaf, BabelStream Dot, and su3 bench on Frontier, AMD's HIP programming model achieves the best performance, as expected. However in multiple instances HIP does not achieve the best performance, particularly for XSBench. From Omniperf profiling we note that the HIP port achieves lower GFLOP/s and lower L1 cache bandwidth but at a higher arithmetic intensity and higher L1 cache hit rate. We note that Kokkos uses a larger workgroup size and arranges L1 cache read requests in a larger number of smaller requests for a similar number of bytes. This suggests Kokkos is selecting a more ideal workgroup size and arranges data access patterns more efficiently for AMD GPUs in XSBench. Meanwhile, OpenMP appears to be able to take advantage of Local Data Share (LDS) implicitly, while HIP is not, reducing stalls for accesses to memory.

XSBench is a performance test case used in the development of LLVM OpenMP offloading, which Clacc also uses for OpenACC on Frontier, helping explain why both directivebased models perform so well with XSBench. However, given that Kokkos is a C++ abstraction over HIP code, it is surprising that it can outperform HIP. We note that HIP XSBench performance on Frontier is only slightly better than HIP XSBench on Corona, suggesting that the XSBench HIP implementation is not a fully optimized and mature baseline.

The XSBench developers directly state that they used the Hipify tool to create the XSBench HIP port, and in comparing the HIP and CUDA versions it is clear that they are identical aside from simple substitution of CUDA syntax for HIP syntax. It is possible that writing HIP kernels by translating existing CUDA kernels without additional modification or optimization does not guarantee optimal performance on AMD hardware. Portable programming models are able to achieve superior performance in some cases with a similar level of effort.

# D. Portability of C++ abstraction libraries

**Observation 3:** Kokkos and RAJA can be competitive with CUDA and HIP, on many system and application pairs.

Kokkos and RAJA compare favorably with CUDA and HIP on NVIDIA and AMD systems, with one of the two ports either nearing or exceeding the native port's performance on every combination of system and app, besides those involving CloverLeaf on any system or miniBUDE on an NVIDIA system. However, which model is more performant is very application-dependent. With these very mixed results it is hard to pick a clear portability winner between Kokkos and RAJA, but we can observe that RAJA tends to perform more competitively for NVIDIA systems, and Kokkos tends to have an advantage on AMD systems.

Regarding RAJA's difficulty with su3\_bench, we observe for RAJA substantially lower arithmetic intensity in L1 and L2 cache compared to HIP, suggesting the RAJA port loads unnecessary data from memory more often. Additionally, in miniBUDE RAJA is not making use of shared memory, which we address in Sec. VIII.

Kokkos performance in CloverLeaf is a notable exception. We observe that the Kokkos port of CloverLeaf takes significantly more time in the calc\_dt reduction kernel relative to other ports. In Nsight Compute, we find that the Kokkos port achieves fewer eligible warps on average, mostly due to barrier warp stalls, which we do not observe in the other ports. In Sec. VIII we identify a fix for these issues in CloverLeaf Kokkos.

# E. Portability of directive-based models

**Observation 4:** OpenMP is often slower than other implementations, and OpenACC has greater affinity for NVIDIA systems.

OpenMP performance across systems and cases is often slower than the native baseline. In only one case, XSBench on Frontier, does OpenMP achieve significantly better performance than the baseline. OpenMP is able to achieve rough parity with the native baseline in exactly half the cases tested. CloverLeaf performance for OpenMP is a notable outlier; we find that compared to HIP the OpenMP port spends significantly more time in the PdV kernel, where OpenMP achieves less than half the L1 cache bandwidth, as well as a roughly 40% lower L2 cache hit rate and 30% higher rate of stalls on L2 cache data. Meanwhile, in miniBUDE, the OpenMP port appears to allocate an order of magnitude more Local Data Share (LDS) bytes than HIP does, limiting the number of active compute units.

On NVIDIA systems, OpenACC generally achieves more consistent performance with the baseline, but is consistently worse than OpenMP and further worse than HIP on AMD systems, likely because it is employing the same LLVM offloading runtime through the Clacc compiler that OpenMP is using. According to Clacc developers, there is some overhead due to suboptimal translation of OpenACC to OpenMP within Clacc which will be addressed in a future release. The OpenACC port for su3\_bench in particular suffers from insufficient exposed parallelism. This is caused by a small fixed number of iterations being distributed to a single block, resulting in only a few active threads per block. In Sec. VIII we redesign the existing su3\_bench port to improve its performance portability.

# F. Portability of SYCL

**Observation 5:** SYCL performance is very often competitive with native ports.

We observe that in many cases, SYCL performs as well or better than native programming models (CUDA and HIP). As a lower-level language extension, similar to CUDA or HIP, this is not necessarily surprising. In some cases, SYCL is able to improve on CUDA or HIP performance, and even where SYCL is more than 3% slower than a native port, is is never the worst-performing port except in XSBench on Perlmutter, where is is only 5.3% slower.

# G. Comparing individual observations to $\Phi$

Overall, the P results mostly conform with our observations from the raw data, although we cannot use them to draw conclusions about models' relative affinities to different systems. Inevitably, summarizing the performance results with one number for each application and programming model obscures some details, particularly exceptional cases where a model that usually does poorly is able to win out. The reverse, in which a model that usually does well does poorly, is less likely to be so obscured, due to P's bias towards low outliers arising from the behavior of the harmonic mean [9]. Compared to  $\overline{\Psi}$  [14],  $\Psi$ more strongly penalizes especially poor performance on a subset of systems, for instance assigning OpenMP and OpenACC scores of 0.58 and 0.53 on BabelStream Dot, respectively, compared to 0.65 and 0.67 for  $\overline{\Phi}$ , due to OpenACC's better performance on Perlmutter outweighing its poor performance on Frontier and Corona. This would reverse the two ports' relative rankings, but generally the insights from either metric are broadly similar.

In summary, we found that SYCL, as well as RAJA and Kokkos, show significant promise in their ability to enable performance portability, and are even able to outperform native ports written with a similar level of effort in some cases. SYCL's strong performance may be related to its lower-level nature, as a language extension, which results in code much more similar to CUDA or HIP. OpenMP and OpenACC, in contrast, may offer a less verbose and less intrusive porting experience, even if the performance portability achieved is more application-dependent.

# VIII. OPTIMIZATIONS

Having identified performance outliers in the previous section, we present performance optimizations for a few chosen case studies here. We note that for many of these optimizations we benefit from the programming models' capacities to allow multiple correct expressions of the algorithm that can be tuned for performance, such as by rearranging directives, changing the level of parallelism exposed, or improving use of hardware features.

#### A. su3\_bench

The su3\_bench OpenACC port originally generated code with only 36 threads per block, despite iterations being assigned to blocks of size 128. As a result, insufficient threads were active for the number of blocks launched. We addressed this issue by collapsing all four loops, thereby exposing more parallelism.

As for OpenMP and OpenACC, we found both generated twice as many global loads and stores as CUDA, due to a misaligned complex number struct. Note that OpenMP, OpenACC, and SYCL do not provide a native complex type suited for GPUs. We then replaced this struct with one properly aligned to sizeof(T) \* 2, resulting in a single load and store for each complex number in the array. On AMD this optimization has no effect.

# Runtimes (in seconds) After Optimizations by Application, Architecture, and Programming Model

Fig. 4. Average performance of all proxy applications across all platforms and programming models, after applying optimizations. Boxes indicates where our optimizations were applied. Lower is better.

As presented in Figure 4, OpenACC benefits strongly from this combination of optimizations, whereas OpenMP achieves more modest speedups.

# B. CloverLeaf

As mentioned previously, Kokkos CloverLeaf encounters a relatively high number of barrier stalls. Comparing the implementations of the calc\_dt between ports, we found that Kokkos was the only one to use a 2D reduction instead of collapsing the kernel into a 1D reduction. Once we updated the Kokkos port to use a 1D scheme we found that its performance on calc\_dt compared favorably with the native port on all studied systems, and no longer observed barrier warp stalls in the new profile.

Figure 4 displays how these speedups translate to the full application. On Perlmutter and Corona, where Kokkos's performance on the other three main kernels compares more favorably with the native ports, Kokkos has a greater overall speedup.

#### C. miniBUDE

In comparing the Kokkos, RAJA, SYCL, and CUDA versions of miniBUDE, we noticed that the RAJA version was not making use of shared memory, while the Kokkos, SYCL, and CUDA ports were. RAJA recently added features for dynamically allocating shared memory inside a kernel, a feature needed in miniBUDE since the forcefield data is input-dependent in size, so we modified RAJA miniBUDE to use shared memory for this data.

After this optimization, RAJA performance improves significantly on NVIDIA platforms, and stays about the same on AMD, leading to an overall increase in portability (see Fig. 4). After these changes the RAJA performance comes very close to the CUDA performance on Perlmutter, an impressive gain since other models already using shared memory do not get

this close on NVIDIA platforms. At the time of writing we were unable to add dynamic shared memory allocation inside the kernel for the OpenMP and OpenACC ports due to lack of support.

# IX. CONCLUSION

In this paper, we empirically evaluated seven GPU programming models and directly compared their capabilities for enabling performance portability. We performed this evaluation on some of the fastest supercomputers in the world using existing proxy application codes that represent real scientific workloads. We developed a Spack-based methodology to substantially lower the barrier to entry for similar portable programming model comparison experiments in the future. We invested significant effort in ensuring each proxy application's implementations in each model ports can be easily built and run on additional systems, and we plan to open-source the product of these efforts, sharing them with the broader HPC community.

For application, compiler, and programming model developers, we highlight several insights from our experiences:

- The process of successfully building all of these applications across systems was not trivial, especially for RAJA, a multi-library portability suite.

- Improving the quality of profiling tools for new programming models and hardware architectures will be critical to enabling performance portability, as our ability to identify bottlenecks depended heavily on such tooling.

- Reduction operations continued to be a major bottleneck, as observed in prior studies.

- The ability to separate correctness and performance concerns in these models was critical in identifying the optimizations we describe, as it allowed us to tune ports without invalidating scientific results.

#### ACKNOWLEDGMENTS

This material is based upon work supported in part by the National Science Foundation under Grant No. 2047120, and the National Science Foundation Graduate Research Fellowship Program under Grant No. DGE 2236417. This work was performed under the auspices of the U.S. Department of Energy (DOE) by Lawrence Livermore National Laboratory under Contract DE-AC52-07NA27344 (LLNL-CONF-855581).

This research used resources of the Oak Ridge Leadership Computing Facility at the Oak Ridge National Laboratory, which is supported by the Office of Science of the U.S. DOE under Contract No. DE-AC05-00OR22725. This research used resources of the National Energy Research Scientific Computing Center (NERSC), a U.S. DOE Office of Science User Facility located at Lawrence Berkeley National Laboratory, operated under Contract No. DE-AC02-05CH11231 using NERSC award DDR-ERCAP0025593.

#### REFERENCES

- [1] TOP500.org, "November 2023 top500," 2023. [Online]. Available: https://www.top500.org/lists/top500/2023/06/

- [2] "OpenMP Application Program Interface. Version 4.0. July 2013," 2013.

- [3] R. D. Hornung and J. A. Keasler, "The RAJA Portability Layer: Overview and Status," Lawrence Livermore National Laboratory, Tech. Rep. LLNL-TR-661403, Sep. 2014.

- [4] C. R. Trott, D. Lebrun-Grandié, D. Arndt, J. Ciesko, V. Dang, N. Ellingwood, R. Gayatri, E. Harvey, D. S. Hollman, D. Ibanez, N. Liber, J. Madsen, J. Miles, D. Poliakoff, A. Powell, S. Rajamanickam, M. Simberg, D. Sunderland, B. Turcksin, and J. Wilke, "Kokkos 3: Programming model extensions for the exascale era," *IEEE Transactions on Parallel and Distributed Systems*, vol. 33, no. 4, pp. 805–817, 2022.

- [5] T. Gamblin, M. LeGendre, M. R. Collette, G. L. Lee, A. Moody, B. R. de Supinski, and S. Futral, "The spack package manager: bringing order to hpc software chaos," in SC15: International Conference for High-Performance Computing, Networking, Storage and Analysis. Los Alamitos, CA, USA: IEEE Computer Society, nov 2015. [Online]. Available: https://doi.ieeecomputersociety.org/10.1145/2807591.2807623

- [6] S. J. Pennycook, J. D. Sewall, and V. W. Lee, "A metric for performance portability," in *Proceedings of the 7th International* Workshop in Performance Modeling, Benchmarking and Simulation of High Performance Computer Systems, 2016. [Online]. Available: https://arxiv.org/abs/1611.07409

- [7] A. Sabne, P. Sakdhnagool, S. Lee, and J. S. Vetter, "Evaluating performance portability of openacc," in *Languages and Compilers for Parallel Computing: 27th International Workshop, LCPC 2014, Hillsboro, OR, USA, September 15-17, 2014, Revised Selected Papers 27.* Springer, 2015, pp. 51–66.

- [8] T. Ben-Nun, J. de Fine Licht, A. N. Ziogas, T. Schneider, and T. Hoefler, "Stateful dataflow multigraphs: A data-centric model for performance portability on heterogeneous architectures," in *Proceedings of the International Conference for High Performance Computing, Networking, Storage and Analysis*, 2019, pp. 1–14.

- [9] S. J. Pennycook, J. D. Sewall, and V. W. Lee, "Implications of a metric for performance portability," *Future Generation Computer Systems*, vol. 92, pp. 947–958, 2019.

- [10] J. Sewall, S. J. Pennycook, D. Jacobsen, T. Deakin, and S. McIntosh-Smith, "Interpreting and visualizing performance portability metrics," in 2020 IEEE/ACM International Workshop on Performance, Portability and Productivity in HPC (P3HPC), 2020, pp. 14–24.

- [11] S. J. Pennycook, J. D. Sewall, D. W. Jacobsen, T. Deakin, and S. McIntosh-Smith, "Navigating performance, portability, and productivity," *Computing in Science & Engineering*, vol. 23, no. 5, pp. 28–38, 2021.

- [12] S. J. Pennycook and J. D. Sewall, "Revisiting a metric for performance portability," in 2021 International Workshop on Performance, Portability and Productivity in HPC (P3HPC), 2021, pp. 1–9.

- [13] D. F. Daniel and J. Panetta, "On applying performance portability metrics," in 2019 IEEE/ACM International Workshop on Performance, Portability and Productivity in HPC (P3HPC), 2019, pp. 50–59.

- [14] A. Marowka, "A comparison of two performance portability metrics," Concurrency and Computation: Practice and Experience, p. e7868, 2023

- [15] ——, "Toward a better performance portability metric," in 2021 29th Euromicro International Conference on Parallel, Distributed and Network-Based Processing (PDP). IEEE, 2021, pp. 181–184.

- [16] M. Martineau, S. McIntosh-Smith, and W. Gaudin, "Assessing the performance portability of modern parallel programming models using tealeaf," *Concurrency and Computation: Practice and Experience*, vol. 29, no. 15, p. e4117, 2017.

- [17] I. Z. Reguly and G. R. Mudalige, "Productivity, performance, and portability for computational fluid dynamics applications," *Computers & Fluids*, vol. 199, p. 104425, 2020.

- [18] I. Z. Reguly, "Performance portability of multi-material kernels," in 2019 IEEE/ACM International Workshop on Performance, Portability and Productivity in HPC (P3HPC). IEEE, 2019, pp. 26–35.

- [19] A. Sedova, J. D. Eblen, R. Budiardja, A. Tharrington, and J. C. Smith, "High-performance molecular dynamics simulation for biological and materials sciences: Challenges of performance portability," in 2018 IEEE/ACM International Workshop on Performance, Portability and Productivity in HPC (P3HPC). IEEE, 2018, pp. 1–13.

- [20] S. Boehm, S. Pophale, V. G. Vergara Larrea, and O. Hernandez, "Evaluating performance portability of accelerator programming models using spec accel 1.2 benchmarks," in *High Performance Computing:* ISC High Performance 2018 International Workshops, Frankfurt/Main, Germany, June 28, 2018, Revised Selected Papers 33. Springer, 2018, pp. 711–723.

- [21] A. S. Dufek, R. Gayatri, N. Mehta, D. Doerfler, B. Cook, Y. Ghadar, and C. DeTar, "Case study of using kokkos and sycl as performance-portable frameworks for mile-dslash benchmark on nvidia, amd and intel gpus," in 2021 International Workshop on Performance, Portability and Productivity in HPC (P3HPC). IEEE, 2021, pp. 57–67.

- [22] T. Deakin, J. Price, M. Martineau, and S. McIntosh-Smith, "Evaluating attainable memory bandwidth of parallel programming models via babelstream," *Int. J. Comput. Sci. Eng.*, vol. 17, no. 3, p. 247–262, jan 2018.

- [23] V. Artigues, K. Kormann, M. Rampp, and K. Reuter, "Evaluation of performance portability frameworks for the implementation of a particlein-cell code," *Concurrency and Computation: Practice and Experience*, vol. 32, no. 11, p. e5640, 2020.

- [24] E. M. Rangel, S. J. Pennycook, A. Pope, N. Frontiere, Z. Ma, and V. Madananth, "A performance-portable sycl implementation of crkhacc for exascale," in *Proceedings of the SC'23 Workshops of The International Conference on High Performance Computing, Network, Storage, and Analysis*, 2023, pp. 1114–1125.

- [25] R. Gayatri, C. Yang, T. Kurth, and J. Deslippe, "A case study for performance portability using openmp 4.5," in *Accelerator Programming Using Directives: 5th International Workshop, WACCPD 2018, Dallas, TX, USA, November 11-17, 2018, Proceedings 5.* Springer, 2019, pp. 75–95.

- [26] H. Brunst, S. Chandrasekaran, F. M. Ciorba, N. Hagerty, R. Henschel, G. Juckeland, J. Li, V. G. M. Vergara, S. Wienke, and M. Zavala, "First experiences in performance benchmarking with the new spechpe 2021 suites," in 2022 22nd IEEE International Symposium on Cluster, Cloud and Internet Computing (CCGrid). IEEE, 2022, pp. 675–684.

- [27] G. K. Reddy Kuncham, R. Vaidya, and M. Barve, "Performance study of gpu applications using sycl and cuda on tesla v100 gpu," in 2021 IEEE High Performance Extreme Computing Conference (HPEC), 2021, pp. 1–7

- [28] I. Karlin, A. Bhatele, J. Keasler, B. L. Chamberlain, J. Cohen, Z. DeVito, R. Haque, D. Laney, E. Luke, F. Wang, D. Richards, M. Schulz, and C. H. Still, "Exploring traditional and emerging parallel programming models using a proxy application," in *Proceedings of the IEEE Inter*national Parallel & Distributed Processing Symposium, ser. IPDPS '13. IEEE Computer Society, May 2013.

- [29] T. Deakin, S. McIntosh-Smith, J. Price, A. Poenaru, P. Atkinson, C. Popa, and J. Salmon, "Performance portability across diverse computer architectures," in 2019 IEEE/ACM International Workshop on Performance, Portability and Productivity in HPC (P3HPC), 2019, pp. 1–13.

- [30] T. Deakin, A. Poenaru, T. Lin, and S. McIntosh-Smith, "Tracking performance portability on the yellow brick road to exascale," in 2020 IEEE/ACM International Workshop on Performance, Portability and Productivity in HPC (P3HPC), 2020, pp. 1–13.

- [31] T. Deakin, S. McIntosh-Smith, S. J. Pennycook, and J. Sewall, "Analyzing reduction abstraction capabilities," in 2021 International Workshop on Performance, Portability and Productivity in HPC (P3HPC). IEEE, 2021, pp. 33–44.

- [32] T. Deakin, J. Cownie, W.-C. Lin, and S. McIntosh-Smith, "Heterogeneous programming for the homogeneous majority," in 2022 IEEE/ACM International Workshop on Performance, Portability and Productivity in HPC (P3HPC), 2022, pp. 1–13.

- [33] W.-C. Lin, S. McIntosh-Smith, and T. Deakin, "Preliminary report: Initial evaluation of stdpar implementations on amd gpus for hpc," arXiv preprint arXiv:2401.02680, 2024.

- [34] J. Kwack, J. Tramm, C. Bertoni, Y. Ghadar, B. Homerding, E. Rangel, C. Knight, and S. Parker, "Evaluation of performance portability of applications and mini-apps across amd, intel and nvidia gpus," in 2021 International Workshop on Performance, Portability and Productivity in HPC (P3HPC), 2021, pp. 45–56.

- [35] S. L. Harrell, J. Kitson, R. Bird, S. J. Pennycook, J. Sewall, D. Jacobsen, D. N. Asanza, A. Hsu, H. C. Carrillo, H. Kim et al., "Effective performance portability," in 2018 IEEE/ACM International Workshop on Performance, Portability and Productivity in HPC (P3HPC). IEEE, 2018, pp. 24–36.

- [36] T. Koskela, I. Christidi, M. Giordano, E. Dubrovska, J. Quinn, C. Maynard, D. Case, K. Olgu, and T. Deakin, "Principles for automated and reproducible benchmarking," in *Proceedings of the SC'23 Workshops of The International Conference on High Performance Computing, Network, Storage, and Analysis*, 2023, pp. 609–618.

- [37] J. R. Tramm, A. R. Siegel, T. Islam, and M. Schulz, "Xsbench-the development and verification of a performance abstraction for monte carlo reactor analysis," *The Role of Reactor Physics toward a Sustainable Future (PHYSOR)*, 2014.

- [38] J. Herdman, W. Gaudin, S. McIntosh-Smith, M. Boulton, D. A. Beckingsale, A. C. Mallinson, and S. A. Jarvis, "Accelerating hydrocodes with openacc, opencl and cuda," in 2012 SC Companion: High Performance Computing, Networking Storage and Analysis. IEEE, 2012, pp. 465–471.

- [39] D. Doerfler and C. Daley, "su3\_bench: Lattice qcd su (3) matrix-matrix multiply microbenchmark (su3\_bench) v1. 0," Lawrence Berkeley National Lab.(LBNL), Berkeley, CA (United States), Tech. Rep., 2020.

- [40] S. McIntosh-Smith, J. Price, R. B. Sessions, and A. A. Ibarra, "High performance in silico virtual drug screening on many-core processors," *The international journal of high performance computing applications*, vol. 29, no. 2, pp. 119–134, 2015.

- [41] "Ecp proxy applications," https://proxyapps.exascaleproject.org/, accessed: 2023-09-30.

- [42] "Nersc proxy suite," https://www.nersc.gov/research-and-development/nersc-proxy-suite/.

- [43] M. A. Heroux, R. F. Barrett, J. M. Willenbring, S. D. Hammond, D. Richards, J. Mohd-Yusof, and A. Herdman, "Mantevo suite 1.0." Sandia National Lab.(SNL-NM), Albuquerque, NM (United States), Tech. Rep., 2013.

- [44] J. H. Davis, C. Daley, S. Pophale, T. Huber, S. Chandrasekaran, and N. J. Wright, "Performance assessment of openmp compilers targeting nvidia v100 gpus," in *Accelerator Programming Using Directives*, S. Bhalachandra, S. Wienke, S. Chandrasekaran, and G. Juckeland, Eds. Cham: Springer International Publishing, 2021, pp. 25–44.

- [45] D. A. Beckingsale, M. J. McFadden, J. P. S. Dahm, R. Pankajakshan, and R. D. Hornung, "Umpire: Application-focused management and coordination of complex hierarchical memory," *IBM Journal of Research and Development*, vol. 64, no. 3/4, pp. 00:1–00:10, 2020.