# Makinote: An FPGA-Based HW/SW Platform for Pre-Silicon Emulation of RISC-V Designs

Elias Perdomo Barcelona Supercomputing Center Spain Universitat Politècnica de Catalunya Spain

Syed Zafar Barcelona Supercomputing Center Spain Alexander Kropotov Barcelona Supercomputing Center Spain

Teresa Cervero Barcelona Supercomputing Center Spain Francelly Cano Barcelona Supercomputing Center Spain

Xavier Martorell Barcelona Supercomputing Center Spain Universitat Politècnica de Catalunya Spain

Behzad Salami Barcelona Supercomputing Center Spain

# ABSTRACT

Emulating chip functionality before silicon production is crucial, especially with the increasing prevalence of RISC-V-based designs. FPGAs are promising candidates for such purposes due to their high-speed and reconfigurable architecture. In this paper, we introduce our Makinote, an FPGA-based Cluster platform, hosted at Barcelona Supercomputing Center (BSC-CNS), which is composed of a large number of FPGAs (in total 96 AMD/Xilinx Alveo U55c) to emulate massive size RTL designs (up to 750M ASIC cells)<sup>1</sup>. In addition, we introduce our FPGA shell as a powerful tool to facilitate the utilization of such a large FPGA cluster with minimal effort needed by the designers. The proposed FPGA shell provides an easy-to-use interface for the RTL developers to rapidly port such design into several FPGAs by automatically connecting to the necessary ports, e.g., PCIe Gen4, DRAM (DDR4 and HBM), ETH10g/100g. Moreover, specific drivers for exploiting RISC-V based architectures are provided within the set of tools associated with the FPGA shell. We release the tool online for further extensions.<sup>2</sup>

We validate the efficiency of our hardware platform (i.e., FPGA cluster) and the software tool (i.e., FPGA Shell) by emulating a RISC-V processor and experimenting HPC Challenge application running on 32 FPGAs. Our results demonstrate that the performance improves by 8 times over the single-FPGA case.

### **KEYWORDS**

FPGA, Ultrascale, Cluster, Software (SW), Hardware (HW), RISC-V

#### <sup>1</sup>Our hardware platform is initially targeted for research purpose and under collaboration agreements it can get available for external researchers <sup>2</sup>https://github.com/MEEPproject/fpga\_shell

# **1** INTRODUCTION

Recently, logic emulation emerged as the dominant approach addressing chip emulation challenges and its design explosion problems. These scalability problems arise from the increasing complexity of current processors and Systems-on-Chip (SoCs), which integrate hundreds of complex components, such as cores, accelerators, and memory hierarchies. Simulating such designs on conventional systems is notably time-consuming. Traditional simulation can be accelerated using emulation systems, where FPGAs on emulation boards replace a portion or the entire design, with the remaining simulation tasks handled by software on the host computer.

FPGA-based logic emulation foundational concept was described in [5]. A logic emulation system consists of one or more emulation boards with single or multiple FPGAs and other integrated circuits (ICs) such as memories [18, 27]. The notion of using multiple FPGAs for improving logic emulation was proposed in [16] as a reconfigurable computing application [10, 17]. To achieve high-speed emulation, a transaction-based approach is commonly employed, [7, 15] allowing emulation and computer software to execute independently, minimizing waiting times. The hardware for logic

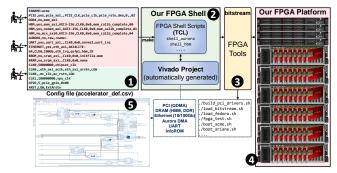

Figure 1: Our hardware/software FPGA-based platform including FPGA Shell and FPGA Cluster

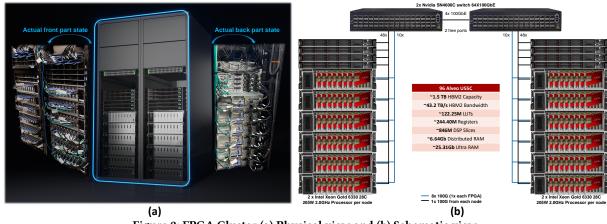

Figure 2: FPGA Cluster (a) Physical view and (b) Schematic view.

emulation involves three main types of chips[19]: (1) customized processor, (2) customized Field Programmable Gate Array (FPGA) and processor and (3) commercial FPGAs. Whereas (1) and (2) are application-specific integrated circuits (ASICs), (3) is not. Each has its advantages and drawbacks, as discussed in detail in [6, 24].

The growing capabilities of FPGAs introduce compelling emulation-based alternatives. Leveraging their inherently programmable architecture and hardware-speed executions enables combining fast simulation times with high accuracy and flexibility [12, 28]. FPGA emulation can significantly reduce the simulation time of large-scale design from years to days [13]. For one trillion cycles (-20 minutes) i.e., this extensive cycle count decreased from an estimated 3 years (1095 days) to a mere 8.7 days.

Reduced Instruction Set Computer (RISC-V) based processors and SoCs are current complex systems that benefit from FPGA emulation capabilities. RISC-V is an open standard for an instruction set architecture that has garnered substantial momentum over the past decade [23]. Industry benefits from this open and customizable architecture, promoting innovation, reducing vendor lock-in, and enabling cost-effective development of specialized processors. Additionally, it empowers academia to explore innovative computer architecture with a relevant, accessible standard, providing a pathway toward real-world commercial usage [11, 22].

Pre-silicon emulation using FPGAs has a long history, both academia (e.g., LiTEX[20], FireSim[14]) and industry (e.g., Synopsys HAPS[26], Cadence Palladium [8], Siemens Veloce[25]) have put significant effort into it. Although commercial platforms propose a complete hardware and software solution, they are not easily available for research purposes. On the other side, open-source platforms do not provide a complete hardware and software solution and have limited features. In contrast, we propose a complete hardware and software solution initially targeted for research purposes; our hardware platform is built based on commercial-off-the-shelf (COTS) FPGAs and our software platform is built on top of standard AMD/Xilinx IPs.

In this paper, we present an FPGA-Based Hardware/Software platform for pre-silicon emulation of RISC-V designs. *Our Hardware Platform* is a large-scale FPGA-based cluster comprising 96 AMD/Xilinx Alveo U55c boards and provides the capability of emulating large RISC-V designs, up to 730M ASIC cells. In addition, *Our Software Platform*, i.e., the FPGA shell, is a configurable, scalable, extensible, and easy-to-use tool to facilitate using the cluster by enabling the widely-used ports of FPGA (e.g., PCIe, Ethernet, Aurora, HBM).

Fig.1 shows the overall flow to work with our platforms. As a first step, through a configuration file, the users enable and configure the interfaces of the FPGA Shell need based on their design requirements **①**. Our FPGA Shell **②** depending on the file options, enables the desired macros and IPs and automatically generates a Vivado project connecting the user design to the desired interfaces **③** and generates a bitstream of the interfaced design. Once the bitstream is generated, by using our FPGA tools **④** all the needed drivers and the bitstream can be loaded in our cluster **⑤**.

# 2 MAKINOTE: A LARGE-SCALE FPGA-BASED CLUSTER

*Our HW Platform* is a large-scale multi-FPGA cluster designed to support hardware/software co-design activities and provides the capability of emulating large RISC-V designs, up to 730M ASIC cells. Our cluster empowers applications to run at a system level with multiple nodes and FPGAs per node. It also provides the foundational infrastructure for simulation, emulation, and software development to support the RISC-V ecosystem. In Fig.2(a) a Physical view of our cluster is illustrated.

*Our HW Platform* comprises 96 Xilinx Alveo U55C Data Center Accelerator Card, from AMD [1] targeting Virtex XCU55 Ultra-Scale+ HBM high-density FPGA modules. The designation of the FPGA used on the Alveo U55C board is the XCU55C, a multi-die FPGA made of XCVU33P + two XCVU11P die, which is rebadged XCVU37P [3]. The Alveo U55C has also various hard IP blocks, including HBM and memory controllers, PCIe controllers and drivers as well as QSFP and Ethernet functionality. These hard macros establish the primary functionalities required for numerous future designs to be emulated by an FPGA-based platform.

Our cluster is composed of 12 nodes, hosting 96 Alveo U55C cards (8 cards per node), and divided into two identical racks (6

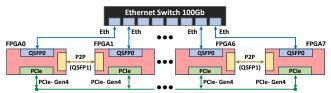

nodes per rack). In Fig.2(b) a detailed schematic view of the infrastructure is presented. The interconnection among FPGAs is based on QSFP+ ports of the FPGAs (two ports per card) as well as PCIe Gen4. The cluster is equipped with two 64-port 100gbs Ethernet switches, which are used to connect cards through QSFP1. As a soft configuration, we use the other QSFP0 port of the FPGA cards to establish a direct FPGA-to-FPGA connection among cards in pairs. Furthermore, within the nodes, all 8 FPGAs are connected through PCIe Gen4 for the host-FPGA communication. The all-to-all communication provides flexibility for interconnecting FPGAs together. Fig. 3 showcases these interface details within a node.

# 2.1 Makinote: access methodology

When accessing our FPGA-based cluster is crucial to know how it is organized as well as the methodology to be followed to be able to place our designs successfully. Currently, our cluster has distinct types of nodes, each serving a specific purpose:

- (1) Management nodes (4 nodes): One of these is the Login node which is the entry point for accessing the FPGA cluster and operating one or more FPGA cards using SLURM for resource allocation. The remaining 3 nodes are exclusively for overall rack operation control.

- (2) **Compute nodes (4 nodes):** General-purpose compute nodes that are not associated with FPGA usage.

- (3) FPGA node (12 nodes): Each has eight FPGAs. Users can allocate 1 or many FPGAs in a node or multiple nodes.

An overview of the large-scale FPGA machine's organization at the network level and the interactions amongst different components is illustrated in Fig. 4. This diagram represents the final system and the steps to access the numerous resources available:

• The first step is to stablish a connection to our large-scale FPGA cluster through the Login node via SSH **0**. Once logged, resources must be allocated and configured via SLURM.

• Then, if there is availability, the system : 1) allocates the requested resources, 2) configures the resources, and 3) deploys the system and provides access to the user **2**.

• A bitstream of the user design is "wrapped up" by our FPGA Shell (further explained in the following section) using the available repositories to get access to the different available interfaces (e.g., PCIe, Ethernet, Aurora, HBM).

• Finally, using a set of tools we developed the required drivers and the bitstream can be programmed on the cluster **④**.

• Once a user finishes, the session is guaranteed to be properly closed and user data is removed from the system **⑤**.

The current system configuration, demands users to specify two parameters as part of the connection process:

Figure 3: The interconnection network of FPGAs in the cluster (illustrated for a single node)

Figure 4: General schematic of the network designs and interactions.

• All FPGA cards are configured with a specified Ethernet speed: 10Gb Ethernet ("10g"), or 100Gb Ethernet ("100g"). The latter is also a default configuration ("auto").

• PCIe configuration for its Direct Memory Access (DMA) kernel module: "none", "xdma" or "qdma".

These constraints can be applied individually or in combination, depending on the specific user needs.

# 3 OUR SW PLATFORM: FPGA SHELL ENABLING SEAMLESS FPGA UTILIZATION

*Our SW platform* simplifies FPGAs usability, enabling expert and non-expert users to create, test, and validate IPs and designs effortlessly, and automatically, whenever possible. It includes our FPGA shell, several scripts and drivers to facilitate seamless, efficient, and flexible exploitation of the FPGA capabilities by all users, regardless of the specific characteristics of the designs.

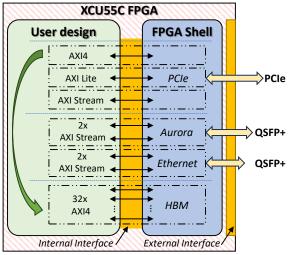

The FPGA Shell provides connectivity, through standard protocols, to memory and numerous interfaces allowing seamless communication to the host and other FPGAs. Ultimately, our FPGA Shell wrappers the user design by parsing the user-specified interfaces to the corresponding FPGA Shell interfaces. This guarantees that inner designs can be interchangeable while adhering to a defined I/O interface between the FPGA Shell and the design. Designs range from RISC-V-based implementations to IPs such as neural network implementations. The broad goal is that users focus only on their designs while abstracting away from issues of designing base components; instead, only well-known interfaces (mainly AXI) need to be provided Fig5. Meanwhile, our FPGA Shell takes responsibility for managing the interfaces and making user designs FPGA-agnostic.

Moreover, our FPGA shell is open-source licensed for users to take advantage of its features (if the targeted FPGAs are supported) or want to contribute to its development. This represents a paradigm shift in an industry predominantly monopolized by proprietary solutions. During project creation, our configuration file allows to "enable" and "configure" a combination of IPs including:

- Communication with the host CPU and/or other FPGAs via PCIe.

- Memory access through HBM.

• Communication with the host CPU and/or other FPGAs via 100 Gb Ethernet.

• Communication with other FPGAs using Quad Small Form-factor Pluggable (QFSP) and Aurora (Peer-to-Peer communication).

• Additional modules such as DDR4, UART, a custom BitInfo ROM, or JTAG, can also be provided per user requirements.

Figure 5: Diagram of the FGA Shell interfaces

Components shown in Table 1 are designed to operate at maximum capacity while incurring minimal resource costs insignificant in FPGAs with over a million LUTs. However, evaluating our FPGA Shell solely in terms of performance would be an incomplete assessment. Beyond this, our FPGA Shell brings substantial advantages in terms of usability, scalability, and time saved during project setup and debugging.

# 3.1 PCIe IP

Our FPGA Shell uses Peripheral Component Interconnect Express (PCIe) interface to establish communication between the FPGAs and the host server. PCIe offers advantages in terms of available OS drivers and integrated hard IPs within the FPGA. The Alveo U55C has PCIe Gen4 with 16x full duplex Lanes running at 8.0 GT/s for a peak bandwidth of 8 GT/s x2 (duplex) x16 lanes / 8 bits/byte = 32 GB/s. Setting up the PCIe link between the host and FPGA involves two key aspects: (1) Setting up the host by compiling and installing drivers, and (2) setting up the PCIE4C [4] hard block inside the FPGA using Vivado, including parameters like BAR options, number of lanes, physical functions, virtual functions, etc.

Xilinx supports two PCIe blocks: XDMA (External Direct Memory Access) and QDMA (Queue Direct Memory Access). Our FPGA Shell opts for the more flexible and powerful QDMA implementation, distinguishing itself from standard XDMA found in platforms like Xilinx Vivado. QDMA key differentiator is the concept of queues, individually configurable by interface type, offering a lowoverhead option for continuous update functionality. Although our

**Table 1: FPGA Shell IPs and Features**

| IPs         | Features                          |

|-------------|-----------------------------------|

| DRAM        | DDR4, HBM2 (DMA)                  |

| PCIe        | Gen4 (qdma)                       |

| Ethernet    | 10Gb/100Gb (over QSFP port)       |

| FPGA-2-FPGA | MAC-Layer Aurora (over QSFP port) |

| UART        | Debug, Bitstream Uploading        |

| Others      | JTAG, InfoROM                     |

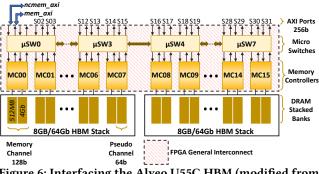

Figure 6: Interfacing the Alveo U55C HBM (modified from [29])

FPGA-Shell uses QDMA, our cluster supports PCIe functionalities for bitstreams programmed with QDMA or XDMA host drivers.

Our FPGA-Shell abstracts users from the PCIe IP configuration and setup complexity with this line in the configuration file:

PCIE,yes,pci\_axi,,PCIE\_CLK,pcie\_clk,pcie\_rstn,dma,0,,02

### **Code1: PCIe configuration**

The first value of this line, which is one of the many in **①** in Fig.1 configuration file, is always the name for the interface to be configured. The second is if the user wants to enable it [yes/no]. The third one is editable and is the name of the AXI interface to be connected to the IP followed by the protocol standard [AXI4-256/AXI4-256/AXI4-LITE-64] or blank (like in this PCIe case) for fixed interfaces. The clocks and reset are also editable and configured next and the last field is for the utilized HBM channel.

# 3.2 DRAM: HBM & DDR4

High Bandwidth Memory (HBM) is a pivotal component of our FPGA Shell because as the only memory available in the Alveo U55C plays the role of main memory and enables self-hosting capabilities for accelerators. HBM uses a 3D-stacked Dynamic Random Access Memory (DRAM) approach to significantly enhance system memory bandwidth through a system-in-package technology.

Our FPGA shell provides standard interfaces to the Alveo U555C HBM controller with two stacks of 64Gb density (8H stack / 8GB) (Fig.6). Each stack has 8 Memory Controllers (MC) and 8 channels divided into 16 pseudo-channels of 256MB. With a 256-bit AXI Port operating up to 450MHz for each 32 pseudo-channel for a 460.8GB/s bandwidth. Every 4 AXI Port enters a fully implemented microswitch providing the same behavior for any access inside the 4 pseudo-channels comprised. The two stacks involve 8 of these micro-switches connected adjacently allowing access to the whole memory. As HBM consists of multiple SDRAM cores, each controlled by its own MC, our FPGA Shell supports an arbitrary number of AXI-MM channels for connecting designs to multiple MCs. This feature enables high bandwidth due to the potential increase in concurrency of data exchange in multi-core systems through the distribution of concurrent memory accesses over multiple MCs.

Our FPGA Shell abstracts users from the HBM configuration and setup complexity with these lines in the configuration file:

| DDR,no, | mem_a  | xi     |          |      |      |     |       |          |     |

|---------|--------|--------|----------|------|------|-----|-------|----------|-----|

| HBM.ves | .mem a | axi.AX | (I3-256. | CLK0 | .0x0 | mem | calib | complete | .00 |

HBM,yes,ncmem\_axi,AXI3-256,CLK0,0x0,mem\_calib\_complete,01 HBM,no,mcx\_axi0,AXI3-256,CLK0,0x0,mem\_calib\_complete,04

#### **Code2: HBM configuration**

In Fig.6 we illustrated how pseudo channels *S00* and *S01* are connected using the AXI3-256 protocol to the defined signals *ncmem\_axi* and *mem\_axi* as explained before. *mcx\_axi0* has everything well configured but is set to **no** enable it.

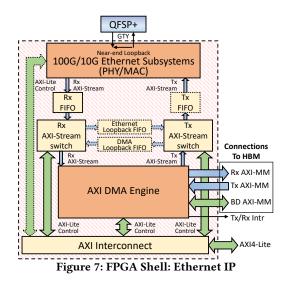

# 3.3 Ethernet IP

Our FPGA Shell Ethernet IP enhances user design capabilities with IP-based connections for user designs. This extends the concept of self-hosted designs, controlled by built-in CPU(s), which can be RISC-V-based with an OS running on top i.e. Our Ethernet IP solution satisfies the requirements for standard external connectivity based on CPU needs, mainly offering Ethernet over QSFP. For this, we used a set (4-lanes) of FPGA-level Ultrascale+ GTY transceivers providing a peak bandwidth of 32.75 Gb/s per external differential pins pair

This approach facilitates communications between the FPGAembedded OS and any other Ethernet system via QSFP. The main originator of Tx data and acceptor of Rx data present in the design is a DMA engine accompanied by its corresponding Tx and Rx memories. Xilinx AXI DMA core [2] converts AXI4-Stream input/output to AXI4-MM write/read accesses. *Loopback FIFOs* implements the feature of data loopback with bypass of the Ethernet core and serves the purpose of checking the test infrastructure itself and debugging the test software. Finally the design contains all kinds of connections for AXI4-Stream links allowing to debug and characterize data streaming separately for different units.

Our Ethernet-over-PCI driver solution shown in Fig.7, provides full connectivity to all 8 FPGA boards within the same node via PCIe, while Ethernet via QSFP establishes connectivity between FPGAs in different (or the same) nodes [9]. Additionally, the FPGA Shell provides a homogeneous and scalable communication infrastructure for all FPGAs, irrespective of their design architecture.

The Ethernet IP configuration and setup complexity, at the end, gets hidden from the user behind these lines in our configuration file:

ETHERNET,yes,eth\_axi,AXI4LITE-64,CLK0,100Gb,eth\_irq,qsfp1

,hbm,29

### **Code3: Ethernet configuration**

### 3.4 Aurora IP

Our FPGA Shell seamlessly integrates Xilinx's proprietary lightweight high-speed communication protocol, Aurora. Aurora is designed to accommodate higher-level protocols, such as TCP/IP, using one or more high-speed serial GT lanes. It can be referenced to a second or Data Link Layer of the OSI model (the layer where data packets are encoded and decoded into bits). The FPGA Shell's Aurora subsystem, based on the Aurora 64B/66B IP core, includes SerDes hard macros around FPGA GT differential pin pairs. The subsystem features receive and transmit 256-bit wide AXI4-Stream channels, along with logic for control, buffering, and diagnostics. The block diagram of our Aurora solution is quite similar to the Ethernet one in Fig.7 just replacing the Ethernet subsystems by the

Aurora 64B/66B IP because we use the AXI DMA for the same purposes, for providing communications over the IP by software. The *dotted* blocks are removed from our aurora solution because they are not needed due to a different clock synchronization strategy.

Configured by default to use all 4 GTY lanes connected to an optical QSFP+ connector of Alveo FPGA boards (10 Gb/s per lane), the Aurora subsystem achieves a bandwidth of around 3.5 Gb/s for data exchange between two boards using the Aurora DMA solution under Buildroot Linux with a non-cached region of HBM. The developed test application for the FPGA Shell's Aurora subsystem ensures data integrity checks, including ICMP packet exchanges, providing an example of running IP protocol packets over the Aurora link layer.

The Aurora IP configuration and setup complexity, gets hidden from the user behind these lines in our configuration file:

AURORA,no,eth\_axi,AXI4LITE-64,CLK0,dma,eth\_irq,qsfp1,hbm ,13

# **Code4: Aurora configuration**

### 4 EXPERIMENTAL RESULTS

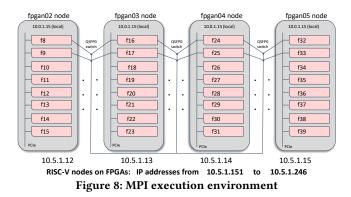

A comprehensive set of bring-up tests was conducted to validate the proper operation of *Our HW Platform* and *Our SW Platform*. In this section, we delve into a more extensive experiment involving MPI communication across many cores on many FPGAs, leveraging the capabilities of the FPGA Shell and the readiness of our multi-FPGA cluster. The baseline environment for these experiments is illustrated in Fig.8, utilizing four computing nodes in our cluster; from nodes 2 to 5.

For these experiments, all FPGAs were programmed with an identical bitstream, including a RISC-V microarchitecture with 4 Lagarto Hun CPUs [21], and the FPGA Shell facilitating interfaces to HBM, PCIe, and Ethernet. The RISC-V infrastructure on each FPGA is booted to execute Fedora Linux OS on the RISC-V cores. This provides 32 FPGAs able to run MPI applications using the QSFP0 connection to the switch.

The Fedora distribution image was updated to support booting on our cluster infrastructure in such a way that:

#### arXiv, January, 2024

• (*Ethernet-over-QSFP*): This Ethernet network is dynamically configured by starting the Network Manager service and the *dhclient* servers to get the DHCP configuration by contacting the DHCP server running on our cluster infrastructure. For this QSFP configuration through DHCP, we propagated the node MAC address from the boot sequence, including both the node and the FPGA numbers, within the binary boot file. In addition, OpenSBI inserts the proper MAC address into the device tree, for Linux to configure the eth0 device. We also support through this network the MPI communications being used in these experiments.

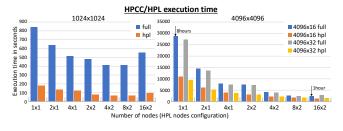

Fig. 9 shows the results obtained for the HPC Challenge application with a different set of FPGAs, increasing the number of FPGAs from 1 to 32, with the configuration of HPCC to be from 1x1 FPGA mesh to 16x2 FPGA mesh. Both graphics illustrate the Execution Time, showing satisfactory scalability for matrices of 1024x1024 and 4096x4096, even though the times are relatively high, as expected, due to the emulation of RISC-V cores over FPGAs. The left-side graphic reveals some degree of scalability for both the full application execution time and the particular High-Performance Linpack (HPL) execution time, even with a smaller matrix. On the right-side graphic, we utilized a larger matrix and tested different block sizes of 16x16 and 32x32, being the latter one faster for every configuration. In this case, the scalability exhibited is acceptable, decreasing execution time from 8 hours for a single FPGA to 1 hour for 32 FPGAs (configuration 16x2 of HPCC).

# 5 CONCLUSIONS

In this paper, we have shown our proposal for the emulation of chip functionality before reaching silicon production, for RISC-V-based designs using our large-scale multi-FPGA cluster. This platform supports the AMD/Xilinx Alveo U55c FPGA boards, installed on a system with 12 nodes and 8 FPGAs per node. Within the platform,

Figure 9: MPI execution results

we provide support for various common components, like HBM and DDR4 global memory, PCIe Gen4, and QSFP Ethernet connections (QSFP0 and QSFP1). We develop a specific set of common resources, which simplify and automate FPGA-based design generation. Moreover, they allow us to run full-fledged Linux distributions on the chips with the possibility to test parallel applications. As a proof of concept, we have run the HPC Challenge benchmark on a simple experiment with up to 32 FPGAs, showing that the performance of the execution of the application has an 8-fold improvement, as compared to the execution on a single node. These experiments not only validate the correct functioning of all FPGA Shell IPs and the cluster infrastructure but also showcase the potential of deploying multiple designs that can successfully communicate. This intercommunication can be used to exploit more logic resources and accommodate larger designs for enhancing overall performance.

### ACKNOWLEDGMENTS

This work has received funding from the MEEP project (European High-Performance Computing Joint Undertaking (JU) under grant agreement No 946002), from "Lenovo-BSC Contract-Framework (2022)", from the Spanish Government (PID2019-107255GB-C21/AEI /10.13039/501100011033, CEX2021-001148-S funded by MCIN/AEI / 10.13039/501100011033), and from Generalitat de Catalunya (contract 2021-SGR-01007).

The authors would like to thank John Davis, Luis Plana, Miquel Moretó, Daniel Jiménez Mazure and the Operations Team at BSC for their helpful support and collaboration.

### REFERENCES

- AMD Xilinx. 2022. Alveo U55C Data Center Accelerator Cards Data Sheet. Technical Report DS978.

- [2] AMD Xilinx. 2022. AXI DMA v7.1 LogiCORE IP Product Guide. Technical Report PG021.

- [3] AMD Xilinx. 2023. UltraScale Architecture and Product Data Sheet: Overview. Technical Report DS890 (v4.4.1).

- [4] AMD Xilinx. 2023. UltraScale+ Devices Integrated Block for PCI Express Product Guide. Technical Report PG213.

- [5] J. Babb and others. 1997. Logic emulation with virtual wires. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 16, 6 (1997), 609–626.

- [6] B. Bailey. 2010. Emulator, accelerator, prototype what's the difference? https: //www.eetimes.com/emulator-accelerator-prototype-whats-the-difference/

- T. Borgstrom. 2014. Transaction-Based Emulation Helps Tame SoC Verification. https://www.electronicdesign.com/technologies/eda/article/21800198/ transactionbased-emulation-helps-tame-soc-verification

- [8] Cadence Design Systems<sup>®</sup>. 2023. Palladium Emulation. https://www. cadence.com/en\_US/home/tools/system-design-and-verification/emulationand-prototyping/palladium.html

- [9] David Castells-Rufas, Xavier Martorell, Aleix Roca, Alexander Kropotov, Xavier Teruel, Teresa Cervero, and John D. Davis. 2023. Ethernet Emulation over PCIe for RISC-V Software Development Vehicles. In 2023 38th Conference on Design of Circuits and Integrated Systems (DCIS). 1–6. https://doi.org/10.1109/DCIS58620. 2023.10335994

- [10] K. Compton and S. Hauck. 2002. Reconfigurable computing: a survey of systems and software. ACM Computing Surveys (csuR) 34, 2 (2002), 171–210. Publisher: ACM New York, NY, USA.

- [11] E. Cui and others. 2023. RISC-V instruction set architecture extensions: A survey. IEEE Access 11 (2023), 24696–24711. Publisher: IEEE.

- [12] N. Dave and others. 2006. Implementing a functional/timing partitioned microprocessor simulator with an FPGA. In 2nd Workshop on Architecture Research using FPGA Platforms (WARFP 2006).

- [13] F. Elsabbagh and others. 2023. Accelerating RTL Simulation with Hardware-Software Co-Design. In Symposium on Microarchitecture (MICRO'23).

- [14] FireSim©. Powered by Jekyll & Minimal Mistakes. 2023. FireSim. https://fires.im/

[15] S. Hassoun and others. 2005. A Transaction-Based Unified Architecture for

- [15] S. Hadsoun and Omita's 2005. In Transaction back of omita's Reinfecture for Simulation and Emulation. Very Large Scale Integration (VLSI) Systems, IEEE Transactions on 13 (March 2005), 278 – 287.

- [16] S. Hauck and A. Agarwal. 1996. Software technologies for reconfigurable systems. Northwestern University, Dept. of ECE Technical Report (1996).

- [17] S. Hauck and A. DeHon. 2010. Reconfigurable computing: the theory and practice of FPGA-based computation. Elsevier.

- [18] K. Hosokawa and others. 2007. Efficient memory utilization for high-speed FPGAbased hardware emulators with SDRAMs. *IEICE transactions on fundamentals of electronics, communications and computer sciences* 90, 12 (2007), 2810–2817.

- [19] W. Hung and R. Sun. 2018. Challenges in large FPGA-based logic emulation systems. In Proceedings of the 2018 International Symposium on Physical Design. 26-33.

- [20] LiteX. 2023. Github:. https://github.com/enjoy-digital/litex (2023).

- [21] Marenostrum Experimental Exascale Platform (MEEP) & BSC. [n. d.]. Scalar core: Lagarto Hun improvements | MEEP. https://meep-project.eu/media/news/scalarcore-lagarto-hun-improvements

- [22] B. Mezger and others. 2022. A survey of the RISC-V architecture software support. IEEE Access 10 (2022), 51394–51411. Publisher: IEEE.

- [23] RISC-V International®. [n. d.]. Specification Status Home RISC-V International. https://wiki.riscv.org/display/HOME/Specification+Status

- [24] L. Rizzatti. 2014. What's The Difference Between FPGA And Custom Silicon Emulators? *Electronic Design* (2014).

- [25] Siemens®. 2023. Veloce Hardware-assisted Verification System. https://eda.sw. siemens.com/en-US/ic/veloce/

- [26] Synopsys<sup>®</sup>. 2023. HAPS-100 Prototyping | Synopsys Verification. https: //www.synopsys.com/verification/prototyping/haps-100.html

- [27] R. Tessier. 2008. Multi-FPGA systems: Logic emulation. In Reconfigurable Computing. 637–669.

- [28] J. Wawrzynek and others. 2007. RAMP: Research accelerator for multiple processors. *IEEE micro* 27, 2 (2007), 46–57. Publisher: IEEE.

- [29] Xilinx Inc. 2021. AXI High Bandwidth Memory Controller v1.0 LogiCORE IP Product Guide. Technical Report PG276 (v1.0). Xilinx Inc.