# Dynamic Electro-Optic Analog Memory for Neuromorphic Photonic Computing

Sean Lam<sup>1</sup>, Ahmed Khaled<sup>2</sup>, Simon Bilodeau<sup>3</sup>, Bicky A. Marquez<sup>2</sup>, Paul R. Prucnal<sup>3</sup>, Lukas Chrostowski<sup>1</sup>, Bhavin J. Shastri<sup>2,3,4</sup>, Sudip Shekhar<sup>1</sup>

<sup>1</sup>Electrical and Computer Engineering, University of British Columbia, 5500 – 2332 Main Mall, Vancouver, V6T 1Z4, British Columbia, Canada.

<sup>2</sup>Centre for Nanophotonics, Physics, Engineering Physics & Astronomy, Queen's University, 64 Bader Lane, Kingston, K7L 3N6, Ontario, Canada.

<sup>3</sup>Electrical and Computer Engineering, Princeton University, 41 Olden Street, Princeton, 08544, New Jersey, United States.

<sup>4</sup>Smith Engineering, Electrical and Computer Engineering, Queen's University, 19 Union Street, Kingston, K7L 3N6, Ontario, Canada.

Contributing authors: seanl@ece.ubc.ca; 20ak41@queensu.ca; sbilodeau@princeton.edu; bama@queensu.ca; prucnal@princeton.edu; lukasc@ece.ubc.ca; shastri@ieee.org; sudip@ece.ubc.ca;

#### Abstract

Artificial intelligence (AI) has seen remarkable advancements across various domains, including natural language processing, computer vision, autonomous vehicles, and biology. However, the rapid expansion of AI technologies has escalated the demand for more powerful computing resources. As digital computing approaches fundamental limits, neuromorphic photonics emerges as a promising platform to complement existing digital systems. In neuromorphic photonic computing, photonic devices are controlled using analog signals. This necessitates the use of digital-to-analog converters (DAC) and analog-to-digital converters (ADC) for interfacing with these devices during inference and training. However, data movement between memory and these converters in conventional von Neumann computing architectures consumes energy. To address this, analog memory co-located with photonic computing devices is proposed. This approach aims to reduce the reliance on DACs and minimize data movement to enhance compute efficiency. This paper demonstrates a monolithically integrated neuromorphic photonic circuit with co-located capacitive analog memory and compares various analog memory technologies for neuromorphic photonic computing using the MNIST dataset as a benchmark.

Keywords: Analog memory, neuromorphic photonic computing, DAC, ADC, online training

# 1 Introduction

#### 1.1 Motivation

Artificial intelligence (AI) has profoundly influenced society and technology with advancements ranging from ChatGPT's human-like dialogues (https://chat.openai.com/) to AlphaFold's protein structure predictions [1–3]. Historically, AI's progression has paralleled advances in CMOS electronics, driven by Moore's law and Dennard scaling [4]. While Moore's law has slowed down, AI's performance demands have surged, with computational needs doubling every two months [4]. In parallel, neuromorphic engineering has emerged as a field aiming to align AI algorithms to hardware architectures that mirror their inherently distributed nature, with demonstrated applications in particle physics, nonlinear programming, and signal processing [5]. Among these innovations, neuromorphic photonics promise high bandwidth and low latency, providing a complementary opportunity to extend the domain of AI [5–8]. However, most photonic processors have been limited to stationary weights, which are trained offline on digital computers and remain unchanged during inference, thus restricting their application potential. One reason this limitation arises is because analog photonic processors require analog-to-digital (ADC) and digital-to-analog (DAC) converters (Figure 1b), which become critical bottlenecks that affect bandwidth and energy efficiency as data transitions between digital memory and analog computation [5, 9–11]. During training, backpropagation requires computations (gradient and error calculations) and memory accesses (weight updates and temporary data storage for calculations), meaning that any part of the pipeline that requires data converters to compute or access memory can be a bottleneck. This work focuses on data conversion bottlenecks from memory and showcases energy savings and minimised latency from co-locating analog memory with analog optical computational units.

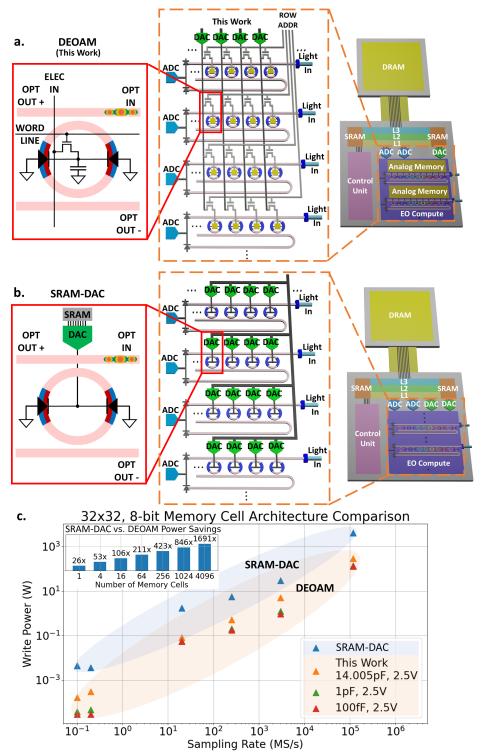

Fig. 1: Motivation for electro-optic processors with dynamic electro-optic analog memory (DEOAM). a) Dynamic electro-optic analog memory (DEOAM) consists of a capacitor connected to a PN junction microring resonator (MRR). The capacitor holds data on the MRR, thereby enacting a weight in the optical domain. Using DEOAM means DACs can be reused among rows of analog memory devices since the analog memory holds the signal on the MRR, which relaxes limitations on energy efficiency and bandwidth imposed by DACs. b) Conventional electro-optic processors require a dedicated SRAM-DAC for each PN junction MRR. The DAC needs to be constantly active to hold a signal on the MRR; therefore, implementing SRAM-DAC in a neuromorphic photonic processor requires a DAC for every MRR. c) If n represents the number of MRRs in the row and column of a neuromorphic photonic processor, scaling the conventional SRAM-DAC implementation incurs an n<sup>2</sup> DAC penalty, whereas DEOAM scales by n. Write power and sampling rate for 32x32, 8-bit memory cell architectures are compared using each memory device and DACs from literature [12–20]. As DEOAM scales, DEOAM saves more power compared to SRAM-DAC. Details on the power calculations are described in Appendix D.

Analog memory can reduce the number of DACs in neural network architectures (Figure 1a). While optical analog memories (OAM) have been explored as in-memory computing devices, they currently face challenges, such as low yield and endurance, incompatibility with standard foundry processes, and complex fabrication processes [21, 22]. In contrast, analog electronic memories, such as dynamic random-access memory (DRAM), metal-oxide-metal capacitors, metal-insulator-metal capacitors, or metal-on-semiconductor capacitors, are foundry-compatible and included in conventional CMOS technologies. This compatibility makes integrating analog electronic memories into neuromorphic photonic hardware a more

viable approach, potentially reducing the number of ADCs and DACs in applications, such as long-short term memory neural networks [23].

Here, we propose a neuromorphic photonic processor with dynamic electro-optic analog memory (DEOAM, Figure 1a). This processor leverages the monolithic integration of nanophotonic and CMOS devices on the same silicon substrate. The proposed architecture (Figure 1a) merges the parallel information processing capabilities of photonics using wavelength-division multiplexing (WDM) with the low control complexity of crossbar arrays offered by electronics. As a proof-of-concept, we demonstrate neurosynaptic photonic weights, realized through a WDM array of tunable PN junction microring resonators (MRR) within a photonic weightbank and integrated with an array of capacitive DEOAM on the 90 nm GF9WG monolithic process. We also evaluate and compare various analog memory technologies to enhance system performance. The MNIST dataset serves as a benchmark for training and inference in our comparative analysis of these analog memory technologies, along with a discussion on tradeoffs in neural network design [24]. Our approach to integrating analog memory in neuromorphic photonic processors aims to create a flexible processor with high bandwidth, efficient training capabilities, and the ability to adapt through on-chip, online learning.

#### 1.2 Dynamic Electro-Optic Analog Memory

DEOAM consists of a capacitor that holds charge on a reverse-biased PN junction MRR (Figure 1a). Data is stored on the capacitor as an electrical signal then the PN junction MRR converts the signal to the optical domain for processing. DEOAM can be integrated into an array of MRRs, functioning as an electronic crossbar array and photonic weight banks (Figure 1a) in a neuromorphic photonic processor. The conventional approach consists of several bits of static random access memory (SRAM) connected to a DAC that continuously drives a PN junction MRR (Figure 1b).

In a neuromorphic photonic processor with n rows and n columns of MRRs acting as weights, DEOAM reduces the number of DACs, thereby reducing power consumption. Since the conventional SRAM-DAC implementation requires each MRR to be paired with a DAC, scaling the implementation results in the number of DACs increasing by n² (Figure 1b). In contrast, using DEOAM reduces the number of DACs below n² (Figure 1a) because data is held directly on the photonic device via analog memory, eliminating the constant processing typically needed by DACs. This concept is similar to the functionality in modern liquid crystal active-matrix displays [25]. DACs are still required in the DEOAM architecture to load initial weights from non-volatile, digital memory before beginning inference or training and to refresh analog memory during inference. However, this approach not only simplifies control complexities by reducing the number of electrical lines needed for DAC operations but also, with longer retention times, diminishes the need for DACs to continuously drive the photonic devices, leading to further power savings as the processor scales (Figure 1c, inset). Hence, integrating DEOAM and reducing the reliance on DACs paves the way for more efficient computing.

In neuromorphic processors, analog memory is typically situated close to or directly integrated with the computing unit to minimize data movement, thereby reducing energy consumption and latency [26, 27]. Data movement in memory accesses can consume more than 10 times the energy of multiplication and addition operations [28]. Recent demonstrations of in-memory compute, such as Mythic's Analog Matrix Processor or NeuRRAM, achieve up to tens of TOPS/W in compute efficiency by co-locating the analog memory with the compute unit [29–32]. This highlights DEOAM's close integration with the MRR, which acts as the compute unit in the optical domain, thereby minimizing data movement and enhancing compute efficiency.

#### 2 Results

#### 2.1 Electro-Optic Characteristics

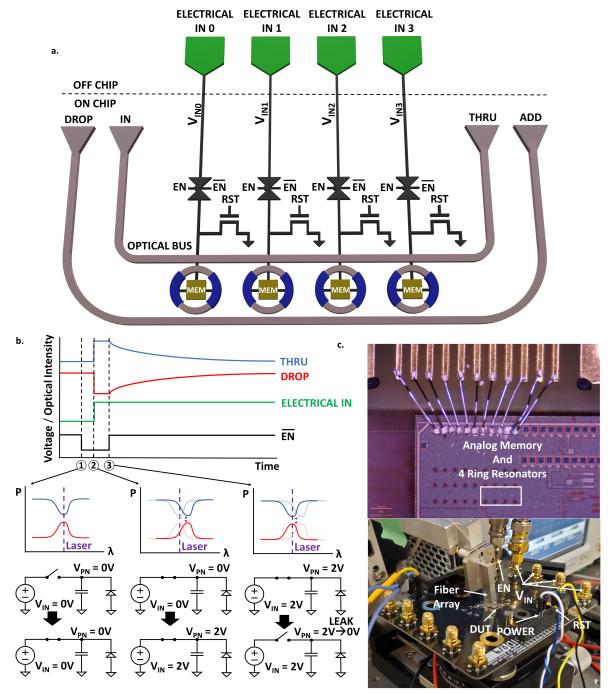

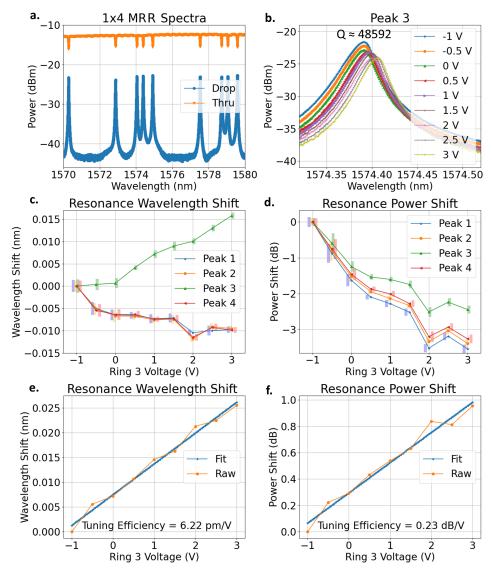

The neuromorphic photonic hardware with integrated DEOAM is shown in Figure 2. Key figures of merit for DEOAM are summarized in Table 1, and measurement results are shown in Figure 3. Figure 2a and b show the DEOAM circuit and its operation. Weights are loaded as voltages on the capacitive memory, affecting the MRR's resonance. The capacitive memory holds the voltage on the MRR until the charge leaks away, returning the MRR to its resonance. Figure 2c shows the chip and measurement setup for static optical and time domain measurements. Free spectral range, inter-channel spacing, Qfactor, and extinction ratio are crucial optical characteristics that determine the maximum number of MRRs and weights in a weight bank in a specific wavelength range. Therefore, if additional weights are needed in each row of a weight bank, solutions like adding more cores, reusing hardware, or employing time multiplexing may be needed for processing neural network data. In a neuromorphic photonic weight bank, light modulation is initiated at the input data modulators. The light then travels through the weight banks before being absorbed by photodetectors (PD) and amplified by transimpedance amplifiers (TIA). The group index helps characterize the group delay, which determines the overall compute time when combined with the delay from the PD and TIA. Since the delay from the PD and TIA depends on their design and technology, we report compute time based primarily on the group delay. State-of-theart demonstrations of PDs and TIAs yield latencies ranging in tens of ps [33-37]. The wavelength and modulation efficiencies are also important for characterizing the tunability and range of weights for the neural network.

Fig. 2: The architecture and operation of the neuromorphic photonic prototype with integrated DEOAM. a) The analog memory circuit consists of a 1x4 MRR weight bank with each MRR connected to a capacitive analog memory. Transmission gates are used to enable/disable (EN) writing and switches are used to reset (RST) the analog memories. Laser light is injected into grating couplers through the IN port and is measured at the THRU and DROP ports. b) The operation of the DEOAM circuit is shown. The PN junction MRR is modeled as a reversed biased diode, and the transmission gate is modeled as an ideal switch. At time 1, the laser has been tuned to the MRR's resonance, and the transmission gate is connected such that the voltage source ( $V_{\rm IN}$ ) can drive the analog memory. At time 2, voltage is driven onto the capacitor and MRR, causing the MRR's resonance to shift. At time 3, the transmission gate disconnects the voltage source from the capacitor, and the capacitor holds the charge on the MRR until it leaks away, returning the MRR resonance back to its original state. c) The chip is wire bonded to a custom printed circuit board with thermal control and high speed electrical lines. Details about the hardware operation and measurement setup are expanded in Appendix A.

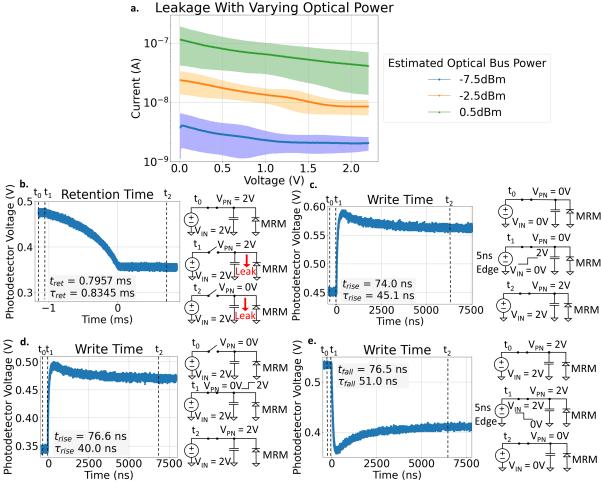

Key FoMs to characterize the capacitive analog memory are retention time, write time, read time, and power consumption. Since data written to DEOAM is immediately available in the optical domain, read time is effectively zero. Retention time is dependent on leakage, and leakage is dependent on optical power and photoresponse of the PN junction MRR [38]. Figures 3a and b reveal that the retention time of 0.8345 ms for one time constant can be extended if lower optical power is used since lower leakage is observed, but this involves a tradeoff between retention time and signal-to-noise ratio. Energy consumption, estimated to be 55.97 pJ/write, is linked to capacitor leakage and charge replenishment to maintain weight values. Figures 3c, d, and e show that the write time is about 40 to 50 ns for one time constant, enabling MHz write speeds. From Figure 3, the analog memory bit precision is about 5 bits and can be extracted from the time domain responses based on  $log_2(\frac{\overline{\mu}_{max} - \overline{\mu}_{min}}{\sigma}) = N_b$  where  $\overline{\mu}_{max}$  and  $\overline{\mu}_{min}$  are the mean values at the maximum and minimum range of the analog memory, respectively,  $\sigma$  is the standard deviation, and  $N_b$  is the bit precision of the analog memory [39].

Table 1: Experimental measurement results of the electro-optic analog memory circuit. Write time and retention time measured with 0.5 dBm optical bus power in the circuit. Details regarding measurement setup and optical characteristics can be found in Appendix A and B.

| Parameter                                     | Symbol                | Min. Value | Nom. Value | Max. Value | Unit       |

|-----------------------------------------------|-----------------------|------------|------------|------------|------------|

| Free Spectral Range                           | FSR                   | _          | 4.67       | -          | nm         |

| Full Width Half Max.                          | FWHM                  | -          | 0.019      | -          | nm         |

| Finesse                                       | F                     | -          | 245.79     | _          | -          |

| Inter-channel Spacing                         | $\Delta \lambda_0$    | 0.34       | -          | 2.61       | nm         |

| Group Index                                   | $n_{\mathbf{g}}$      | 3.70       | 3.70       | 3.71       | -          |

| Q-Factor                                      | Q                     | 46050      | 49234      | 51484      | -          |

| Extinction Ratio                              | m ER                  | 15.6       | -          | 19.9       | dB         |

| Wavelength Tuning Efficiency                  | -                     | -          | 6.22       | -          | pm/V       |

| Modulation Efficiency                         | _                     | -          | 0.23       |            | dB/V       |

| Retention Time (10-90% Level)                 | $t_{ m ret}$          | 0.3330     | 0.5735     | 0.7957     | $^{'}$     |

| Retention Time (One Time Constant)            | $	au_{ m ret}$        | 0.2590     | 0.5527     | 0.8345     | $_{ m ms}$ |

| Compute Time <sup>2</sup>                     | $	au_{\mathrm{read}}$ | 70.87      | -          | 79.51      | ps         |

| Write Time - Rising Edge (10-90% Level)       | $t_{ m rise}$         | 65.5       | 75.3       | 91.3       | ns         |

| Write Time - Falling Edge (10-90% Level)      | $t_{ m fall}$         | 76.2       | 89.4       | 121.2      | ns         |

| Write Time - Rising Edge (One Time Constant)  | $	au_{ m rise}$       | 35.5       | 43.8       | 52.0       | ns         |

| Write Time - Falling Edge (One Time Constant) | $	au_{ m fall}$       | 51.0       | 63.3       | 71.7       | ns         |

| Write Energy Consumption <sup>1</sup>         | $\eta$                | 26.82      | 55.97      | 80.97      | pJ/Write   |

| Bit Precision                                 | $N_b$                 | 5.33       | 5.65       | 5.97       | bits       |

| Capacitance                                   | $C_{MEM}$             | _          | 14.005     | _          | pF         |

$<sup>^1</sup>$ Write energy consumption derived from maximum, minimum, and nominal retention time curves with nominal leakage curve at 0.5 dBm optical bus power in the circuit.

<sup>&</sup>lt;sup>2</sup>Estimated by the group delay through the circuit and resonance build-up in the MRRs. The summation of path delay ( $\tau_{path} = Ln_g/c$  where  $\tau_{path}$  is the path delay, L is the path length, and c is the speed of light) and MRR resonance build-up time ( $\tau_{MRR} = FRn_g/c$  where R is the ring radius) defines compute time [40].

Fig. 3: Electro-optic characteristics of the DEOAM. a) Leakage shows a dependence on optical power incident on the doped MRR. Error bands represent the standard deviation in the leakage. b) Retention time from leakage is 0.835 ms for one time constant at 0.5 dBm optical bus power. The decay shows a nonlinear response from the ring's Lorentzian response. c) With the transmission gate on, 2 V is written to analog memory using a 5 ns edge rate, and the resulting write time is 45.1 ns for one time constant. d) With 2 V on  $V_{\rm IN}$  and toggling the transmission gate from off to on, write time is 40.0 ns. e) With the transmission gate on and writing 0 V to analog memory at an edge rate of 5 ns, write time is 51.0 ns for one time constant. Further discussions on the electro-optic results are expanded in Appendix C.

# 2.2 Device-Level Comparison of Analog Memory Technologies

Surveyed memory technologies are compared in Table 2, focusing on energy consumption, write time, endurance, physical area, and retention time. Among these, DRAM excels in endurance, PCM is optimal

in retention time and write time, OAMs have the lowest energy consumption, and floating gate memory requires the least physical space. Area is less critical since photonic devices can amortize memory area within the photonic device. To summarize, each analog memory technology has unique strengths and is suitable for specific applications; no single analog memory technology excels in all aspects.

#### 2.3 System-Level Comparison of Analog Memory Technologies

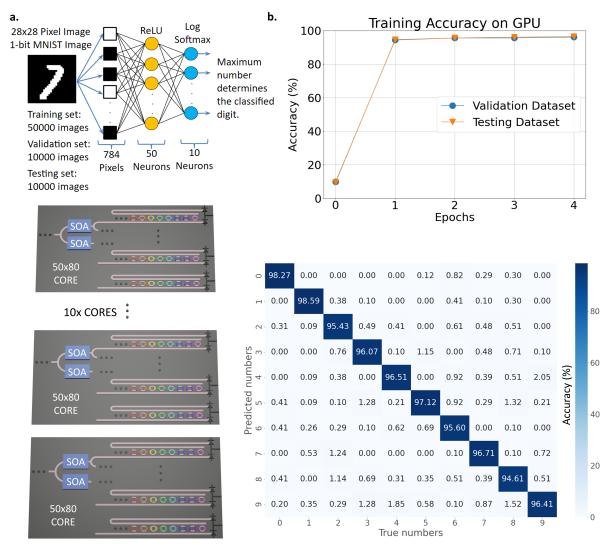

To evaluate the performance of different analog memory technologies within a neural network system, a weight bank architecture, depicted in Figure 4, is emulated to assess analog memory performance during inference and training using the MNIST dataset [24].

Fig. 4: The neural network emulation architecture and initial training. a) The feedforward neural network is trained using the MNIST dataset with 50000, 1-bit, 28x28 pixel images using a batch size of 64, then validated and tested using 10000 images [24]. The neural network is three layers with the input layer supporting 784 values for the 28x28 pixel images, the hidden layer supporting 50 neurons using a ReLU activation function, and the output layer supporting 10 neurons using a logarithmic softmax activation function to classify as a number. The neural network can map to the proposed neuromorphic photonic hardware that consists of 10 photonic cores with 50 rows of weight banks and 80 MRRs in each weight bank. Each core uses 80 wavelengths and 50 semiconductor optical amplifiers (SOA) to compensate for the splitting loss. b) The neural network achieves more than 95% inference accuracy after one epoch for all numbers. The specifics of the neural network architecture, performance, and modeling are detailed in Appendix E.

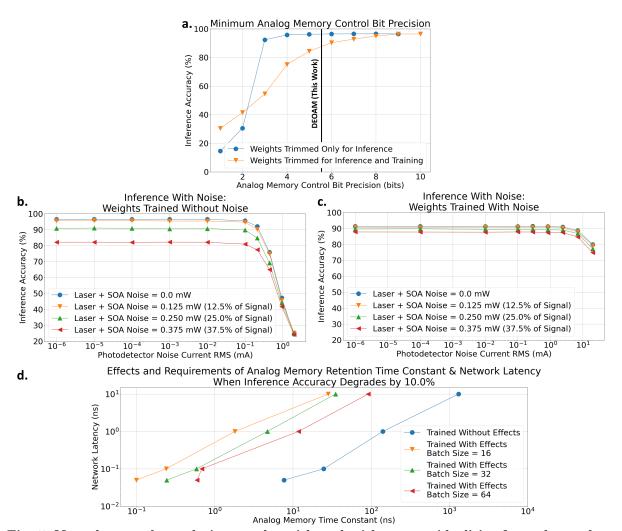

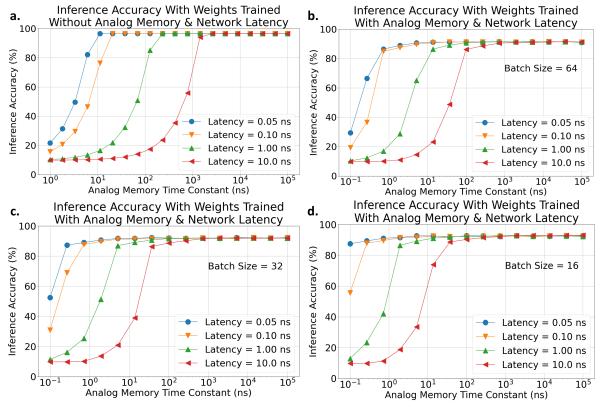

In Figure 5, the weight bank array is characterized for inference accuracy by comparing inference accuracy using weights trained on a GPU with full floating point accuracy and weights trained on emulated hardware with non-idealities in the analog memory and hardware. These non-idealities include analog memory control bit precision, noise, latency, and retention time, which can be generalized to any analog memory technology. These non-idealities are examined individually to assess their impact on inference accuracy. Figure 5a reveals that to achieve inference accuracies above 95%, more than 4 control bits are required for analog memory when weights are trimmed only in inference. The minimum control bit requirement increases to over 8 control bits when weights are adjusted in training and inference because lower control bit precision during training results in less accurate gradient calculations and weights, leading to reduced inference accuracy. For DEOAM, which achieves about 5 bits of precision, using 4 control bits results in an optical power change of about 383 nW and a delay of about 4  $\mu$ s before the weight is registered as a different value.

Figure 5b and 5c analyze the impact of noise sources on inference accuracy after training without noise and with noise, respectively. The main noise sources that have been taken into account come from

the laser, SOA, PD, and TIA. Results indicate that inference accuracy degrades with more than 12.5% optical power noise injected into the weight banks. Furthermore, networks trained with noise are more resilient to PD noise current during inference than networks trained without noise. Specifically, the network trained with noise maintains high inference accuracy until the PD noise current reaches about 2 mA RMS, whereas the network trained without noise only maintains high inference accuracy until about  $0.1~\mathrm{mA}$  RMS of PD noise current.

As weights decay due to the analog memory's leakage, the memory's retention time constant and the network latency determine the number of images that can be classified correctly or the number of useful computations before the weights become unusable. Network latency represents the time for an image to pass through the network. Within a retention time constant, k number of images can be passed through the network before weights are unusable, incurring k times the network latency. This indicates that the ratio of retention time constant to network latency is crucial for a network's inference performance.

Figure 5d examines the impact of analog memory retention time constant (weight decay) and network latency on inference accuracy when it degrades by 10%. The weight decay is modeled as an exponential decay based on the ratio of retention time constant to network latency. These experiments compare scenarios where weights are trained with and without considering retention time and network latency. The findings suggest that training with retention time constant and network latency relaxes the requirements for analog memory retention time, enabling the use of memories with shorter retention time. A ratio of retention time constant to network latency greater than 100 prevents inference accuracy from decaying by 10%. This implies that even with an analog memory retention time constant of 100  $\mu$ s, if the network latency is less than 1  $\mu$ s, the network can maintain high inference accuracy. The ratio of retention time constant to network latency can be scaled to any analog memory technology, giving either a minimum retention time constant for a given network latency or a maximum network latency for a given retention time constant. Although analog memory leakage may limit inference accuracy, controlled leakage can be employed as a regularization technique to avoid overfitting [55]. Furthermore, retention time constant and network latency are varied to evaluate training accuracy with different batch sizes, including 16, 32, and 64. The results show that larger batch sizes require longer retention times to achieve similar training accuracy as smaller batch sizes. With smaller batch sizes, weights are updated more frequently so the analog memory does not need to retain the data for a long time and can operate with shorter retention times.

Once weights become unusable due to leakage, dead-time is consumed to refresh the weight, which can be approximated by the analog memory's write time. When examining the ratio of retention time to write time for analog memories from Table 2, this ratio (10,000 for DEOAM) is a couple orders of magnitude greater than the retention time to network latency ratio (100) required to have high inference accuracy. This means the dead-time for refreshing can be much shorter than network latency. Therefore, refreshes can occur after each image classification, thereby maintaining accurate weights for high inference accuracy without adding significant latency but at the cost of refresh power.

Fig. 5: Neural network emulation results with and without non-idealities from the analog memory and system, such as control bit precision, noise, leakage, and latency. a) Minimum analog memory control bit precision to achieve more than 95% inference accuracy is 4 bits for weights trimmed only in inference and 8 bits for weights trimmed in inference and training. Inference accuracy degrades with increasing laser, SOA, PD, and TIA noise, but inference accuracy degrades b) earlier when weights are trained without noise and c) later when weights are trained with noise. d) The sweep of network latency and retention time characterizes inference accuracy for weights trained with and without leaky analog memory and network latency. Network latency and analog memory retention time constant at the point when inference accuracy degrades by 10% is plotted. When weights are trained with the effects of network latency and memory retention time, the network compensates for these effects and allows for a lower analog memory retention time constant requirement. Batch sizes of 64, 32, and 16 reveal that large batch sizes require longer retention times since weights are updated less frequently. Weights are updated more frequently in smaller batch sizes. Appendix E expands on results in d).

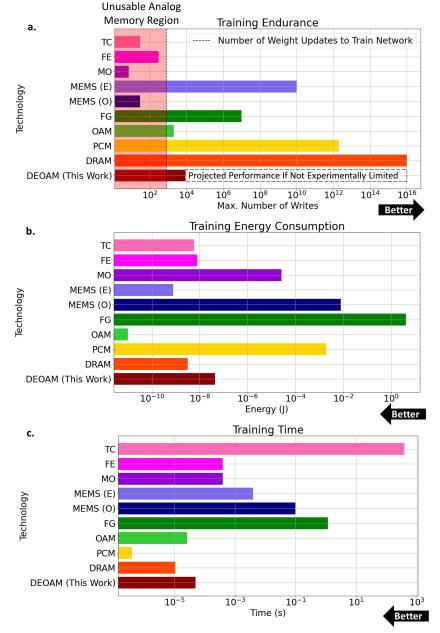

Analog memory technologies from Table 2 are used in the weight bank emulation to compare systemlevel performance metrics, including training energy consumption, training time, and analog memory endurance. These factors are directly impacted by the number of weight updates during training. Figure 6 compares analog memory technologies based on their characteristics from Table 2 and the number of weight updates (or writes to analog memory). Each analog memory technology exhibit strengths in different performance aspects. Reliability, for example, is a critical factor because even if an analog memory cell has a latency of 1 ns, its usefulness is limited if it can only endure 1 million writes or 1 ms before it requires recalibration. Therefore, any analog memory in the red zone in Figure 6a is deemed unsuitable. DRAM, PCM, and MEMS (E) demonstrate high endurance against numerous writes, making them superior candidates for reliability. Since DEOAM operates similarly to DRAM and MEMS (E), DEOAM's endurance is expected to reach similar endurance as DRAM and MEMS (E). Regarding energy consumption in Figure 6b, OAMs achieve the lowest energy consumption at  $12.5~\mathrm{fJ/bit}$  with MEMS (E) and DRAM following as the next most efficient technologies. In Figure 6c, training time is assumed to be limited by the write time of the analog memory and the number of weight updates. Here, PCMs are the optimal analog memory technology for minimal training time. Since different analog memory technologies excel in specific performance metrics, selecting the most suitable analog memory technology or combinations of technologies for a given neural network application is crucial to optimizing overall system performance [56].

Fig. 6: Emulated system comparison of various analog memory technologies and effects on training. a) Any analog memory in the red zone of the training endurance graph will fail or require recalibration before training completes. DRAM is optimal for endurance. b) Energy consumption of analog memories is governed by the write energy. OAMs show the least energy consumption in training. c) Training time for an analog memory is limited by its write time. PCM has the lowest training time.

# 3 Discussion

Training neuromorphic photonic processors presents several challenges related to energy efficiency, time, and execution. Analog-to-digital and digital-to-analog conversions along with memory access often become energy and latency bottlenecks. Additionally, since modeling hardware and environmental fluctuations are challenging, relying on offline-trained weights can degrade inference accuracy [9, 11, 57].

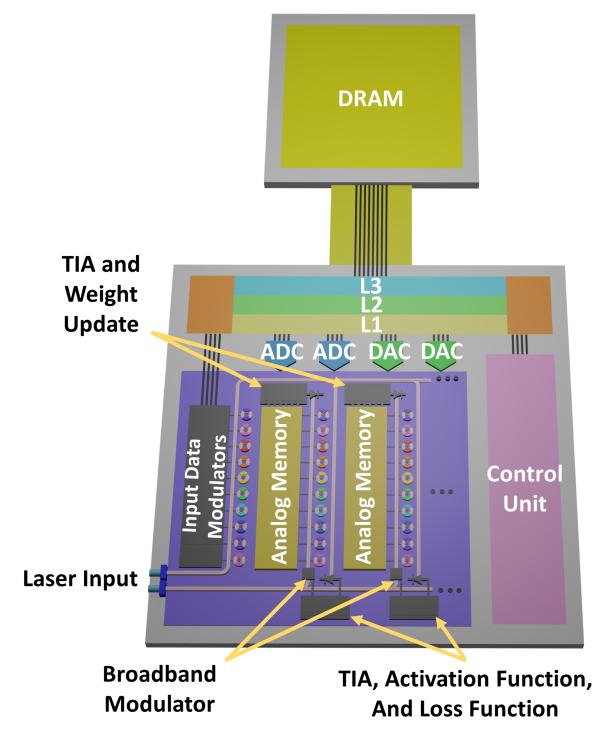

To address these challenges, co-locating analog memory with the compute unit can alleviate energy consumption and latency by reducing data movement and the need for ADCs and DACs. A promising outcome from integrating analog memory in neuromorphic photonic processors, as demonstrated in Figure 7, is the potential for fast, efficient, on-chip, online training. This training method uses backpropagation hardware and allows for immediate weight updates with each new input data, reducing the need for analog-to-digital and digital-to-analog conversions. As a result, the processor can adapt swiftly to changing environments and be more resilient to noise and hardware flaws while consuming less energy. Recurrent neural networks, in particular, can benefit from analog memory integration since retaining data in the analog domain reduces analog-to-digital and digital-to-analog conversions [23]. Furthermore, analog memory can enhance the effectiveness of other training algorithms, such as direct-feedback alignment and in-situ training, by improving training time and on-chip computations [11, 58]. Architecturally, incorporating analog memory into neuromorphic photonic processors facilitates system-level improvements, leading to improved energy efficiency, shorter training time, and a more adaptive neural network.

Fig. 7: A potential architecture for an fast, efficient neuromorphic photonic processor using analog memory and specialized on-chip, training hardware.

However, scaling the neuromorphic photonic processor with analog memory presents challenges in analog memory and MRR control. Depending on the analog memory requirements, specialized circuitry may be necessary for writing to or refreshing the memory. As the system scales, strategies like sharing drive lines (as illustrated in Figure 1a) where DACs are shared along columns, can be essential in reducing power consumption. Accurate resonance control in MRRs is vital for maintaining precise optical weight representation. As the processor scales, implementing thermal control and multi-MRR control algorithms becomes increasingly critical for system stability [39, 59–63].

While analog memory can provide system-level enhancements, analog memory specifications must be examined carefully to understand its limitations. Analog memory endurance is particularly critical, as it must endure numerous writes during training. Selecting training algorithms to minimize writes can enhance endurance, but choosing the right analog memory technology for the application is crucial for determining network endurance. Despite DEOAM's leakage, high inference accuracy can still be achieved if the ratio of retention time to network latency is 100 or higher. This and other charge-based or leaky analog memories can remain effective and maintain high inference accuracy despite inherent leakage.

Different analog memory technologies excel in specific performance metrics but also have certain drawbacks. According to Figure 6c, PCMs demonstrate the fastest training times due to their low write times; however, they consume significant power. On the other hand, OAMs, as shown in Figure 6b, are the most energy efficient because their write energy per bit is the lowest, but their endurance is marginally sufficient. By leveraging various analog memory technologies to exploit their specific strengths, it is possible to optimize neural network performance [56]. For example, DRAM or DEOAM can be used during training, owing to their predicted high endurance and relatively fast write times. During inference, non-volatile PCMs are suitable since no weight updates occur. While each type of analog memory may

excel in one metric, combining different analog memory technologies may complement each other, leading to improved overall system performance.

The modulator is another area for enhancement. Employing PN junctions with different doping levels and junction geometries, such as interleaved, U-shaped, or L-shaped designs, can improve tuning efficiency and speed [60, 64, 65]. However, as indicated in Figure 3a, the PN junction MRR exhibits leakage that is dependent on the incident optical power, suggesting that the photoresponsivity of the PN junction can limit analog memory performance. Reducing this leakage may involve removing contaminants and impurities, such as layering poly-silicon on the substrate or optimizing convection annealing [66, 67]. Alternatively, other modulators, such as MOS capacitor modulators, can be explored to potentially reduce leakage [68]. Pockels effect modulators might offer advantages over PN junctions, as they exhibit minimal leakage (less than 100 nA) and better tuning efficiency [69–71]. Further development in foundry processes is needed to better integrate these modulators into electro-optic platforms [72].

#### 4 Conclusion

We demonstrated a proof-of-concept neuromorphic photonic circuit with DEOAM and compared its capabilities with other analog memory technologies. DEOAM reduces DACs in a neuromorphic photonic processor from  $n^2$  to n, thereby alleviating bottlenecks in bandwidth and energy consumption. By integrating analog memory on chip, neuromorphic photonic processors have the potential to achieve fast and efficient training. Since the training process occurs on chip, the neural network can readily adapt to environmental fluctuations and noise by incorporating them during training. Moreover, analog memory with on-chip backpropagation hardware can enable online training, allowing weights to be updated after each new input data. This opens up possibilities for various applications requiring recurrent events, event-based decision-making, or adaptability, such as time series forecasting. As a result, the next generation of AI processors, equipped with integrated analog memory, can help sustain the continued growth of AI.

# Acknowledgments

We gratefully acknowledge the Natural Sciences and Engineering Research Council of Canada and CMC Microsystems for their support and design tools. We also acknowledge Omid Esmaeeli and Mohammed Al-Qadasi for helping with design reviews, design rule checks, and tapeout; Mustafa Hammood for helping with wirebonding; Jonathan Barnes and Madeline Mahanloo for helping with measurements; Avilash Mukherjee, Hassan Talaeian, Ata Khorami, Mohammed Al-Qadasi, and Ben Cohen for reviewing this paper.

#### **Declarations**

- Funding S.L, S.S, L.C, B.J.S acknowledge support from the Natural Sciences and Engineering Research Council of Canada (NSERC). B. J. S is supported by the Canada Research Chairs Program. S.S is supported by Schmidt Science Polymath Award. S.B. acknowledges funding from the Fonds de recherche du Québec—Nature et technologies.

- Conflict of interest/Competing interests B.J.S and B.M cofounded Milkshake Technology Inc.

- $\bullet\,$  Ethics approval Not applicable

- $\bullet\,$  Consent to participate Not applicable

- $\bullet$  Consent for publication Not applicable

- Availability of data and materials Data is available on reasonable request

- Code availability Available upon request

- Authors' contributions S.L, S.S, B.M, and B.J.S conceived the idea. S.L performed the experiments, led the manuscript writing. S.L, S.S, and S.B architected and S.L and S.B designed the chip. A.K and S.L developed and analyzed the simulation studies. All co-authors analyzed and discussed the data and contributed to revising the manuscript. S.S and B.J.S co-supervised this study.

# Appendix A Hardware Setup

To expand on the hardware setup, in Figure 2a, the silicon photonic electronic chip, fabricated in the 90 nm GF9WG monolithic process, consists of a 1x4 MRR circuit with C-band grating couplers to couple light to the chip and electronics to control when to load or reset voltages. The MRRs are PN junction doped modulators operating in depletion mode (reverse bias) and are connected to analog memory cells consisting of 100x100  $\mu$ m metal-oxide-metal capacitors that use interdigitated fingers to increase capacitance. The MRRs have different ring perimeters starting with 144.248  $\mu$ m and increasing by 50 nm to avoid resonance collision. The electronics consist of transmission gates and reset (RST) transistors. The transmission gates are controlled by an active low enable (EN) signal which connects (EN=0) or disconnects (EN=1) an external source measure unit (SMU) to the analog memory cells. The RST transistors reset the voltage on the analog memory cells before operation. From Figure 2c, the silicon photonic electronic chip is thermally glued and wirebonded to a custom printed circuit board (PCB) that breaks out connections to measurement equipment. The PCB has 50  $\Omega$  transmission lines that breakout to subminiature version A (SMA) connectors for high speed signals and 2.54 mm pitch headers for power and low speed signals. A 10k negative temperature coefficient (NTC) thermistor and peltier module are connected to the LDC501 for thermal control. An 8-degree, 8-channel fiber array is used to couple light to the chip.

Figure 2b shows the operation of the circuit. Initially, the laser is aligned with the MRR resonance while the MRR is voltage-biased at zero voltage. At time 1, the EN signal is active, allowing voltages from the SMU to propagate to the analog memory. At time 2, the SMU drives the capacitor with an analog voltage, which also drives the PN junction MRR. At time 3 when the EN signal is inactive, the capacitor holds the analog voltage on the PN junction MRR until the charge leaks away. As a result, the optical signals on the through (THRU) and drop (DROP) ports of the MRR circuit track the voltage on the capacitor and PN junction MRR.

As shown in Figure 2a, the optical characteristics are measured using a C-band tunable laser (HP81682A) and an array of photodetectors (N7744A) while the MRRs are voltage biased using a SMU (Keithley 2604B). Light is coupled through an 8-degree, 8-channel fiber array to C-band grating couplers on chip, and the SMU is sweeps voltage to observe MRR resonance changes with varying voltage biases.

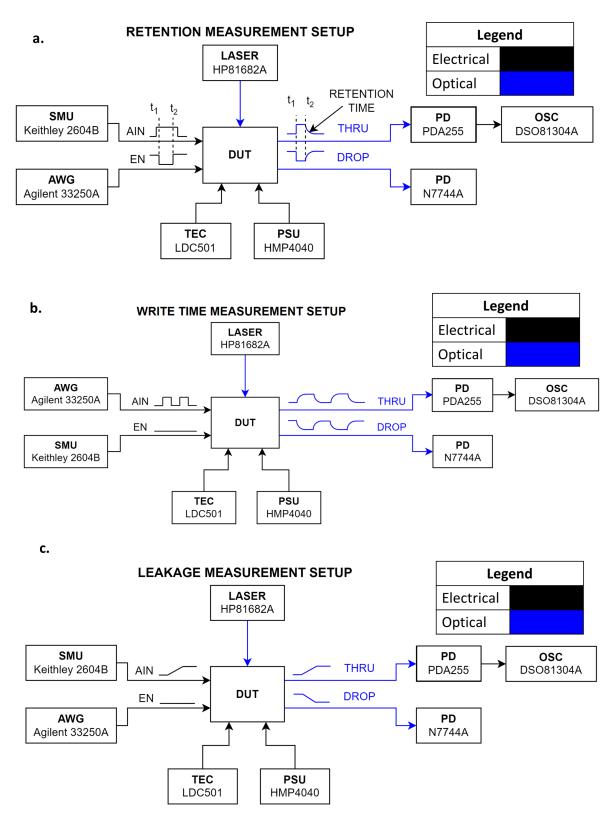

The retention time measurement setup is shown in Figure A1a. The HMP4040 power supply unit (PSU) powers the electronics, the LDC501 thermoelectric cooler (TEC) regulates the chip temperature, and the HP81682A tunable C-band laser provides optical power to the circuit for optical processing. To drive signals, the Keithley 2604B SMU is used to drive the analog memory and PN junction MRR and the Agilent 33250A arbitrary waveform generator (AWG) drives the EN signal with a 5 ns edge rate step to quickly connect and disconnect the SMU from the analog memory and PN junction MRR. The DROP port is connected to a PD on the N7744A to tune the laser wavelength to the MRR resonance, and the THRU port is connected to the high speed, amplified PDA255 and DSO81304A oscilloscope to measure the retention time of the circuit. The retention time measurement sequence is shown in Figure 3b. At t<sub>0</sub>, EN is active, and the SMU sets the desired voltage on the analog memory and PN junction MRR. At t<sub>1</sub>, EN becomes inactive and the analog memory retains the data on the PN junction MRR. After t<sub>1</sub>, charge leaks away from the analog memory, which returns the optical response on the THRU and DROP ports back to its original state (back to the MRR's resonance). At t<sub>2</sub>, all charge is depleted on the analog memory and the optical response returns to the MRR's resonance. The leakage measurement setup in Figure A1c is the same as the retention time setup in Figure A1c, except that the EN signal is constantly active and the SMU is sweeping voltage from 0 V to 2 V while measuring leakage current through the circuit.

Fig. A1: Measurement setup to characterize DEOAM. a) Retention time measurement setup, b) write time measurement setup, and c) leakage measurement setup.

The write time measurement setup is shown in Figure A1b and is similar to the retention time and leakage measurement setup in Figure A1a and A1c, respectively, except that the AWG is driving the analog memory and PN junction MRR while the SMU is holding the EN signal active. The write time measurement sequence is shown in Figure 3c and 3e. The AWG sends a pulse train with 5 ns edge rates to drive the analog memory and PN junction MRR, which modulates the optical response on the THRU and DROP port. The optical response is detected using the THRU port by the PD255 and measured by the DSO81304A oscilloscope. The write time measurement sequence shown in Figure 3d differs from Figure 3c and 3e because the rather than driving the analog memory and PN junction with the 5 ns edge rate pulse train, the transmission gate is driven with a pulse train that connects and disconnects the voltage source from the analog memory and PN junction. The rise time, fall time, and one time constant values are extracted from the oscilloscope time domain response.

# Appendix B Optical Characteristics

From the static optical characteristics of the MRRs in Figure C2a and C2b, the minimum wavelength spacing between different rings is 0.34 nm, the free spectral range (FSR) is 4.67 nm, the extinction ratio is between 15.6 dB and 19.6 dB, and the quality factor is about 50,000. From Figure C2a, optical bus

power is estimated to be -6 dBm. In Figure C2c and Figure C2d, to observe the tuning efficiency of the PN junction MRRs, one MRR is biased at various voltages from 0 to 3 V (3 V is the limit for the thick oxide transistors) while the other MRRs are biased at zero voltage. The resonance wavelength and optical power of each MRR are observed at each voltage bias point to track tuning. Figure C2c reveals that as peak 3 is biased, peaks 1, 2, and 4 track similar trajectories, meaning optical crosstalk between adjacent resonances is negligible. In Figure C2d, the resonance power shift is less apparent than the resonance wavelength shift because the power shift occurs near the resonance of the ring, where the ring response's slope is shallow. Looking at the tuning efficiency of the MRR in Figure C2e and C2f, the wavelength and power shifts are 6.22 pm/V and 0.23 dB/V, respectively.

# Appendix C Electro-Optic Characteristics

The leakage is measured with optical bus powers swept from -7.5 dBm to 0.5 dBm. Optical bus power represents the optical power in the bus waveguide that couples light into the MRRs. From Figure 3a, the leakage depends on the optical power in the circuit. At 0 V, the laser wavelength is biased on the MRR's resonance, meaning the highest optical power is incident on the PN junction in the MRR and the highest leakage is observed. As the SMU sweeps the voltage on the analog memory and PN junction MRR to 2 V, the MRR's resonance shifts away from the laser wavelength, meaning less optical power is circulating in the MRR, less optical power is incident on the PN junction, and less leakage is observed. At 0.5 dBm optical bus power in the circuit, leakage is as high as 200 nA, but at -7.5 dBm optical bus power in the circuit, the leakage is a few nanoamperes. With high optical power incident on the PN junction, additional carriers are generated and are measured as additional leakage. As the voltage bias increases, the MRR resonance strays away from the laser wavelength and less optical power is inside the MRR, meaning less carriers are generated and less leakage is measured. At lower optical powers, such as -7.5 dBm, a couple orders of magnitude reduction in leakage is attained in comparison to 0.5 dBm optical bus power, meaning the retention time can be improved by using lower optical power.

The maximum weight retention time is crucial to revealing the limit in multiply-accumulate (MAC) operations per second in a neural network. The amount of MAC operations per second is dependent on the input data modulation speed, compute time, and weight retention time. Increasing the input data modulation speed and decreasing compute time increases the amount of MAC operations per second, but if the weight retention time is short, inaccurate inferences can occur, meaning that the amount of useful MAC operations is limited by the weight retention time. As shown in Figure 3b, the maximum retention time is 0.8345 ms for one time constant with 0.5 dBm optical bus power.

Combining data from retention time and leakage in Figure 3b and 3a, the amount of energy stored in the analog memory capacitor can be estimated. Although the retention time measurement includes nonlinearity from the MRR Lorentzian response, an approximation of the energy consumed by the capacitors provides a baseline to compare with other analog memory technologies. To estimate the energy consumed from leakage, the maximum and minimum PD voltage in the retention time measurement correspond to the minimum and maximum leakage values at 2 V and 0 V on the capacitor, respectively. With the voltage and leakage current at each time step, power consumed due to leakage is extracted and integrated to obtain a nominal energy consumption of 55.97 pJ.

The analog memory and PN junction MRR introduce a bandwidth limitation, which is measured to extract the write time. From Table 1, the nominal write time is measured to be 75.3 ns to 89.4 ns (10-90%) for rise and fall times and 43.8 ns to 63.3 ns for one time constant. Overshoot is observed in the measurement, which is attributed to the lack of termination on chip and inductance in the PCB and wirebonds. The settling time for the circuit given this overshoot is around 3  $\mu$ s, meaning weights can be updated in 3  $\mu$ s intervals during training, although pre-emphasis pulse shaping has been shown to effectively deal with such dynamics [73].

Fig. C2: Measured optical characteristics of the neuromorphic photonic weight bank with 6 dBm optical bus power. a) 1x4 MRR spectra showing minimum and maximum drop port extinction ratios of 15.6 dB and 19.9 dB, respectively, and a minimum resonance spacing of 0.34 nm. b) Ring resonance Q factor measures around 50k and the static voltage tuning of resonance is shown. Resonance wavelength shift in c) and power shift in d) is tracked on ring 3 as its bias is swept from -1 V to 3 V, while the other rings remain biased at -1 V. Error bars represent the standard deviation in the wavelength shift and power shift. e) Resonance wavelength shift in e) and power shift in f) using the other three MRR responses to calibrate for effective shifts.

# Appendix D Comparing Static and Dynamic Electro-Optic Analog Memory

In electronics, static random access memory (SRAM) typically refers to memory implemented as bit cells with transistors, and dynamic random access memory (DRAM) refers to memory implemented as capacitors. Here, we detail the write power calculations for static and dynamic electro-optic analog memory, SRAM-DAC and DEOAM respectively, in a neuromorphic photonic processor with n columns of MRRs and n rows of photonic weight banks, totaling to n<sup>2</sup> MRRs and n<sup>2</sup> memory cells. SRAM-DAC is defined as consisting of SRAM and DACs, and DEOAM is defined as DACs connected to capacitors. The power consumed by SRAM-DAC is calculated as:

$$P_{SRAM-DAC} = n^2 P_{DAC} + P_{SRAM_{dynamic}} n + P_{SRAM_{static}} n^2$$

(D1)

where  $P_{SRAM-DAC}$  is the total SRAM-DAC array power consumption in W, and  $P_{SRAM}$  and  $P_{DAC}$  are the SRAM and DAC power consumption in W, respectively, which includes static and dynamic power consumption and accounts for varying bit precisions of the DAC. All surveyed DACs are demonstrated, and the SRAMs associated with each DAC are surveyed to be in the same process node [12–20]. The power consumed by DEOAM is calculated as:

$$P_{DEOAM} = (P_{DAC} + \alpha C f V^2) n \tag{D2}$$

where  $P_{DEOAM}$  is the total DEOAM array power consumption,  $\alpha$  is the activity factor (assumed to be 1), C is the load capacitance in F, f is the switching frequency in Hz and is half the sampling rate, and V is the switching voltage.

# Appendix E Emulation Modeling

#### E.1 Neural Network Architecture and Performance

The neural network architecture is configured as three layers with the input layer supporting 784 values for the 28x28 pixel image, the hidden layer supporting 50 neurons followed by a ReLU activation function, and the output layer supporting 10 neurons followed by a logarithmic softmax activation function to classify as a number. The neural network achieves more than 95% validation and testing accuracy within 1 epoch across all predicted numbers as shown in Figure 4b, which is comparable to the photonic neural network in [74]. Since MRR-based weight banks with finesse of 368 (≈55000 quality factor) are limited to 108 rings, 80 MRRs along with 80 analog memories are chosen to be in each weight bank to ensure they are supported in a weight bank system [75]. Each weight bank requires 2 PDs and 1 TIA to perform the summation and amplification. With 80 MRRs in each weight bank, 10 cores are required to sum each respective row of weight banks from each core to match the 784 pixels in each image, and 50 rows of weight banks are needed to match the number of neurons in the hidden layer. For the hidden layer calculation to the output layer, only one core is needed, which reduces overall core usage.

# E.2 Noise

Laser noise represents input data noise and can be related to relative intensity noise (RIN) from the laser as shown in the following equations [76]:

$$x = x_{avg}(1+dx) = P_{avg}(1+dP) = P_{avg}(1+(10^{RIN/10} \cdot f)^{1/2})$$

(E3)

where x is the input data,  $x_{avg}$  is the average value of the input data, dx is the random noise in the input data,  $P_{avg}$  is the average laser power, dP is the random noise in the laser power, RIN is the relative intensity noise in dB/Hz, and f is the bandwidth in Hz. As laser light splits to reach each weight bank, splitting loss is incurred. SOAs can amplify the signal to compensate for splitting loss but add noise to the input data. As a result, the input data to each weight can be described by:

$$x' = x + n_{SOA} \tag{E4}$$

where x' is the input data to each weight bank that includes SOA and laser noise and  $n_{SOA}$  is the SOA noise. As the input data is multiplied by weights, insertion loss from MRRs degrades the input data signal. Weight bank insertion loss ( $\beta$ ) is modeled by using an insertion loss of 0.125 dB/MRR, giving a total insertion loss of 10 dB in each weight bank. At the input of each weight bank, each wavelength has 1 mW of optical power and the noise ranges from 0% to 37.5% of 1 mW to mimic noise from the laser and SOAs. Furthermore, noise is applied to the data after the MAC operation and before the activation function to mimic the input referred noise current on the PD and TIA. The PD and TIA integrated noise current ranges from 1 nA to 2 mA based on current PD and TIA technology [33–37, 77–80]. The following equation summarizes the noise sources and the neural network equation:

$$y_j = \sigma_j(\beta \mathbf{x}' \cdot \mathbf{w_j} + n_j) \tag{E5}$$

where  $y_j$  is the  $j^{th}$  output data in a layer,  $\beta$  is the weight bank insertion loss,  $\sigma_j$  is the  $j^{th}$  activation function in a layer,  $\mathbf{x}'$  is the input data to the weight banks that includes SOA and laser noise,  $\mathbf{w_j}$  is the  $j^{th}$  set of weights in a layer, and  $n_j$  is the  $j^{th}$  input referred noise term. The dot product of  $\mathbf{x}$  and  $\mathbf{w_j}$  represents the photocurrent from the PD detecting laser wavelengths weighted by MRRs.

#### E.3 Weight Decay and Network Latency

Weight decay is modeled by using a ratio of retention time to network latency in an exponential decay model to determine inference accuracy from leaky weights:

$$w(k) = w_0 e^{-k\frac{t_{latency}}{\tau_{ret}}}$$

(E6)

where w(k) is the weight value for the  $k^{th}$  image,  $w_0$  is the initial weight,  $t_{latency}$  is the network latency or compute time,  $\tau_{ret}$  is the retention time constant. In inference, network latency is determined by group delay from photons propagating through the optical circuit and PD and TIA bandwidth, whereas training has additional latency from analog electronics used to update weights. Since the bandwidth of the PD and TIA and analog electronics can vary depending on design and technology nodes, the range of network latencies are assumed to be determined by the PD and TIA bandwidth, which translates to latencies ranging from 50 ps to 10 ns [33–37, 77–79].

# E.4 Effects of Retention Time Constant, Network Latency, and Batch Size on Inference Accuracy

The effects of retention time constant, network latency, and batch size on inference accuracy are shown in Figure E3. When weights are trained without accounting for analog memory retention time and network latency (Figure E3a), inference accuracy degrades at a ratio of analog memory retention time to network latency of about 200. Therefore, extending the ratio of retention time to network latency greater than 200 provides stable and high inference accuracy. Figures E3b-d show inference accuracy when weights are trained to account for analog memory retention time and network latency. Batch sizes of 64, 32, and

16 reveal that inference accuracy degrades at ratios of retention time to network latency of about 100, 40, and 30, respectively. This indicates that training with the effects of analog memory retention time and network latency along with smaller batch sizes relaxes the analog memory retention time constant requirement. One reason is that training with these effects allows the neural network to compensate for these faults. Another reason is that large batch sizes require longer retention times since weights are updated less frequently. Whereas, smaller batch sizes are updated more frequently, which relaxes the analog memory retention time constant requirement.

Fig. E3: The sweep of network latency and retention time characterizes inference accuracy for weights trained a) without leaky analog memory and network latency and b) with leaky analog memory and network latency. a) A ratio of latency to retention time of 100-300 is sufficient to achieve more than 95% inference accuracy. b) A ratio of latency to retention time of 100 is sufficient to achieve more than 90% inference accuracy. Batch size of b) 64, c) 32, and d) 16 reveal that large batch sizes require longer retention times since weights are updated less frequently. Weights are updated more frequently in smaller batch sizes.

#### E.5 Energy Consumption

Energy consumption is dependent on the neural network architecture and key devices that consume power, which include lasers, SOAs, DEOAM, PDs, TIAs, input data modulators, and thermal stabilizers. Table E1 summarizes the energy consumption of key devices in the neuromorphic photonic circuit from Figure 4 during training. Table E1 reveals that optical power delivery via lasers and SOAs and thermal stabilizers consume most of the energy during training followed by DEOAM. Thermal stabilizers using metallic heaters can be replaced by more efficient phase shifters, thereby reducing the energy consumption significantly [72, 81]. Future research for energy efficient neuromorphic photonic processors should, therefore, focus on improving optical power delivery (lasers and SOAs), photonic device stabilization (efficient phase shifters and circuits), and analog memory technology (materials and circuits).

# References

- [1] AlQuraishi, M. AlphaFold at CASP13. Bioinformatics 35, 4862–4865 (2019).

- [2] Merolla, P. A. et al. A million spiking-neuron integrated circuit with a scalable communication network and interface. Science **345**, 668–673 (2014).

- [3] Bannon, P., Venkataramanan, G., Sarma, D. D. & Talpes, E. Computer and Redundancy Solution for the Full Self-Driving Computer. 2019 IEEE Hot Chips 31 Symposium (HCS) 1–22 (2019). ISSN: 2573-2048.

- [4] Mehonic, A. & Kenyon, A. J. Brain-inspired computing needs a master plan. *Nature* **604**, 255–260 (2022). Number: 7905 Publisher: Nature Publishing Group.

- [5] Shastri, B. J. et al. Photonics for artificial intelligence and neuromorphic computing. Nature Photonics 15, 102–114 (2021).

- [6] Ferreira de Lima, T. et al. Primer on silicon neuromorphic photonic processors: architecture and compiler. Nanophotonics (Berlin, Germany) 9, 4055–4073 (2020). Publisher: De Gruyter.

- [7] de Lima, T. F. et al. Machine Learning With Neuromorphic Photonics. *Journal of Lightwave Technology* **37**, 1515–1534 (2019). Publisher: IEEE.

- [8] Tait, A. N. et al. Neuromorphic photonic networks using silicon photonic weight banks. Scientific Reports 7, 7430 (2017).

- [9] Sun, Z. et al. A full spectrum of computing-in-memory technologies. Nature Electronics 6, 823–835 (2023).

- [10] Antonik, P. in Online Training of a Photonic Reservoir Computer (ed.Antonik, P.) Application of FPGA to Real-Time Machine Learning: Hardware Reservoir Computers and Software Image Processing Springer Theses, 39–62 (Springer International Publishing, Cham, 2018).

- [11] Filipovich, M. J. et al. Silicon photonic architecture for training deep neural networks with direct feedback alignment. Optica 9, 1323–1332 (2022).

- [12] Ma, B., Huang, Q. & Yu, F. A 12-bit 1.74-mW 20-MS/s DAC with resistor-string and current-steering hybrid architecture. 2015 28th IEEE International System-on-Chip Conference (SOCC) 1–6 (2015). ISSN: 2164-1706.

- [13] Ansari, E. & Wentzloff, D. D. A 5mW 250MS/s 12-bit synthesized digital to analog converter. Proceedings of the IEEE 2014 Custom Integrated Circuits Conference 1–4 (2014). ISSN: 2152-3630.

- [14] Kumar, S., Chauhan, R. K., Kumar, M. & Gupta, M. D. Impact of Different Technology Node on the Delay and Power Dissipation of 6T SRAM Cell. 2021 7th International Conference on Signal Processing and Communication (ICSC) 337–342 (2021). ISSN: 2643-444X.

- [15] Wu, X., Palmers, P. & Steyaert, M. S. J. A 130 nm CMOS 6-bit Full Nyquist 3 GS/s DAC. IEEE Journal of Solid-State Circuits 43, 2396–2403 (2008).

- [16] Hong, C.-H. et al. A 28nm 36kb high speed 6T SRAM with source follower PMOS read and bitline under-drive. 2015 IEEE International Symposium on Circuits and Systems (ISCAS) 2549–2552 (2015). ISSN: 2158-1525.

- [17] Widmann, D. et al. A Time-Interleaved Digital-to-Analog Converter up to 118 GS/s With Integrated Analog Multiplexer in 28-nm FD-SOI CMOS Technology. *IEEE Journal of Solid-State Circuits* 1–15 (2023).

- [18] Zhang, H. et al. A 0.6-V 10-bit 200-kS/s SAR ADC With Higher Side-Reset-and-Set Switching Scheme and Hybrid CAP-MOS DAC. *IEEE Transactions on Circuits and Systems I: Regular Papers* 65, 3639–3650 (2018).

- [19] Kumar, M. & Ubhi, J. S. Performance evaluation of 6T, 7T & 8T SRAM at 180 nm technology. 2017 8th International Conference on Computing, Communication and Networking Technologies (ICCCNT) 1–6 (2017).

- [20] Rubino, R., Musolino, F., Chen, Y., Richelli, A. & Crovetti, P. A 880 nW, 100 kS/s, 13 bit Differential Relaxation-DAC in 180 nm. 2023 18th Conference on Ph.D Research in Microelectronics and Electronics (PRIME) 269–272 (2023).

- [21] Youngblood, N., Ríos Ocampo, C. A., Pernice, W. H. P. & Bhaskaran, H. Integrated optical memristors. *Nature Photonics* 17, 561–572 (2023).

- [22] Tossoun, B. et al. High-speed and energy-efficient non-volatile silicon photonic memory based on heterogeneously integrated memory memory. Nature Communications 15, 551 (2024).

- [23] Howard, E. R., Marquez, B. A. & Shastri, B. J. Photonic Long-Short Term Memory Neural Networks with Analog Memory. 2020 IEEE Photonics Conference (IPC) 1–2 (2020). ISSN: 2575-274X.

- [24] Lecun, Y., Bottou, L., Bengio, Y. & Haffner, P. Gradient-based learning applied to document recognition. *Proceedings of the IEEE* 86, 2278–2324 (1998). Conference Name: Proceedings of the IEEE.

- [25] den Boer, W. & Den Boer, W. Active Matrix Liquid Crystal Displays: Fundamentals and Applications (Elsevier Science & Technology, Oxford, UNITED STATES, 2005).

- [26] Sebastian, A., Le Gallo, M., Khaddam-Aljameh, R. & Eleftheriou, E. Memory devices and applications for in-memory computing. *Nature Nanotechnology* **15**, 529–544 (2020).

- [27] Tsai, H., Ambrogio, S., Narayanan, P., Shelby, R. M. & Burr, G. W. Recent progress in analog memory-based accelerators for deep learning. *Journal of Physics D: Applied Physics* **51**, 283001 (2018).

- [28] Horowitz, M. 1.1 Computing's energy problem (and what we can do about it). 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC) 10–14 (2014). ISSN: 2376-8606.

- [29] Fick, D. Mythic @ Hot Chips 2018 (2018). URL https://medium.com/mythic-ai/mythic-hot-chips-2018-637dfb9e38b7. Accessed on 2023-04-03.

- [30] Wan, W. et al. A compute-in-memory chip based on resistive random-access memory. Nature 608, 504–512 (2022).

- [31] Feldmann, J. et al. Parallel convolutional processing using an integrated photonic tensor core. Nature 589, 52–58 (2021).

- [32] Ambrogio, S. et al. An analog-AI chip for energy-efficient speech recognition and transcription. Nature 620, 768–775 (2023).

- [33] Atef, M. & Zimmermann, H. Optical Receiver Using Noise Cancelling With an Integrated Photodiode in 40 nm CMOS Technology. *IEEE Transactions on Circuits and Systems I: Regular Papers* **60**, 1929–1936 (2013).

- [34] Babar, M. B., Roberts, G. & Maram, R. A 83-GHz and 68-dBW TIA with 2.3 pA/√ Hz: Towards High Speed and Low Noise Optical Receivers. 2022 20th IEEE Interregional NEWCAS Conference (NEWCAS) 361–365 (2022).

- [35] Awny, A. et al. A 40 Gb/s Monolithically Integrated Linear Photonic Receiver in a 0.25 \mu \rm m BiCMOS SiGe:C Technology. *IEEE Microwave and Wireless Components Letters* **25**, 469–471 (2015).

- [36] Kudszus, S., Shahani, A., Pavan, S., Shaeffer, D. & Tarsia, M. A 46-GHz distributed transimpedance amplifier using SiGe bipolar technology. *IEEE MTT-S International Microwave Symposium Digest*, 2003 **2**, 1387–1390 vol.2 (2003). ISSN: 0149-645X.

- [37] Awny, A. et al. 23.5 A dual 64Gbaud 10kW 5% THD linear differential transimpedance amplifier with automatic gain control in 0.13µm BiCMOS technology for optical fiber coherent receivers. 2016 IEEE International Solid-State Circuits Conference (ISSCC) 406–407 (2016). ISSN: 2376-8606.

- [38] Yu, H. et al. Using carrier-depletion silicon modulators for optical power monitoring. Optics Letters 37, 4681–4683 (2012).

- [39] Tait, A. N. et al. Feedback control for microring weight banks. Optics Express 26, 26422–26443 (2018).

- [40] Geuzebroek, D. H. & Driessen, A. in *Ring-Resonator-Based Wavelength Filters* (ed. Venghaus, H.) *Wavelength Filters in Fibre Optics* Springer Series in Optical Sciences, 341–379 (Springer, Berlin, Heidelberg, 2006).

- [41] Kargar, S. & Nawab, F. Challenges and future directions for energy, latency, and lifetime improvements in NVMs. *Distributed and Parallel Databases* (2022).

- [42] Martin-Monier, L. et al. Endurance of chalcogenide optical phase change materials: a review. Optical Materials Express 12, 2145–2167 (2022).

- [43] Liu, Z. et al. Multilevel halide perovskite memristors based on optical & electrical resistive switching effects. Materials Chemistry and Physics 288, 126393 (2022).

- [44] Arai, F., Maruyama, T. & Shirota, R. Extended data retention process technology for highly reliable flash EEPROMs of 10/sup 6/ to 10/sup 7/ W/E cycles. 1998 IEEE International Reliability Physics Symposium Proceedings. 36th Annual (Cat. No.98CH36173) 378–382 (1998).

- [45] Abdollahramezani, S. et al. Tunable nanophotonics enabled by chalcogenide phase-change materials. Nanophotonics 9, 1189–1241 (2020).

- [46] Feng, X., Liu, X. & Ang, K.-W. 2D photonic memristor beyond graphene: progress and prospects. Nanophotonics 9, 1579–1599 (2020).

- [47] Liu, R., Yang, C.-L. & Wu, W. Optimizing NAND flash-based SSDs via retention relaxation | Proceedings of the 10th USENIX conference on File and Storage Technologies. FAST'12: Proceedings of the 10th USENIX conference on File and Storage Technologies (2012).

- [48] O'Connor, M. et al. Fine-Grained DRAM: Energy-Efficient DRAM for Extreme Bandwidth Systems. 2017 50th Annual IEEE/ACM International Symposium on Microarchitecture (MICRO) 41–54 (2017). ISSN: 2379-3155.

- [49] Koch, U., Hoessbacher, C., Emboras, A. & Leuthold, J. Optical memristive switches. *Journal of Electroceramics* **39**, 239–250 (2017).

- [50] Liang, S. et al. An Empirical Study of Quad-Level Cell (QLC) NAND Flash SSDs for Big Data Applications. 2019 IEEE International Conference on Big Data (Big Data) 3676–3685 (2019).

- [51] DDR5 SDRAM | JEDEC. URL https://www.jedec.org/standards-documents/docs/jesd79-5b. Accessed on 2023-10-28.

- [52] Miller, K. J., Haglund, R. F. & Weiss, S. M. Optical phase change materials in integrated silicon photonic devices: review. *Optical Materials Express* 8, 2415–2429 (2018).

- [53] Choe, J. Memory technology: process and cell architecture. *Optical and EUV Nanolithography XXXVI* **12494**, 1249402 (2023).

- [54] Yuh, J. et al. A 1-Tb 4b/Cell 4-Plane 162-Layer 3D Flash Memory With a 2.4-Gb/s I/O Speed Interface. 2022 IEEE International Solid- State Circuits Conference (ISSCC) 65, 130–132 (2022). ISSN: 2376-8606.

- [55] Singhal, R. et al. Enhanced regularization for on-chip training using analog and temporary memory weights. Neural Networks 165, 1050–1057 (2023).

- [56] Mukherjee, A., Saurav, K., Nair, P., Shekhar, S. & Lis, M. A Case for Emerging Memories in DNN Accelerators. 2021 Design, Automation & Test in Europe Conference & Exhibition (DATE) 938–941 (2021). Conference Proceedings.

- [57] Buckley, S. M., Tait, A. N., McCaughan, A. N. & Shastri, B. J. Photonic online learning: a perspective. *Nanophotonics* **12**, 833–845 (2023).

- [58] Hughes, T. W., Minkov, M., Shi, Y. & Fan, S. Training of photonic neural networks through in situ backpropagation and gradient measurement. *Optica* 5, 864–871 (2018).

- [59] DeRose, C. T. et al. Thermal crosstalk limits for silicon photonic DWDM interconnects. 2014 Optical Interconnects Conference 125–126 (2014). ISSN: 2376-8665.

- [60] Moazeni, S. et al. A 40-Gb/s PAM-4 Transmitter Based on a Ring-Resonator Optical DAC in 45-nm SOI CMOS. *IEEE Journal of Solid-State Circuits* **52**, 3503–3516 (2017). Publisher: IEEE.

- [61] Ren, Y. et al. A Continuously Tunable Silicon Double-Microring Filter With Precise Temperature Tracking. *IEEE Photonics Journal* **10**, 1–10 (2018).

- [62] Li, H. et al. A 3-D-Integrated Silicon Photonic Microring-Based 112-Gb/s PAM-4 Transmitter With Nonlinear Equalization and Thermal Control. *IEEE Journal of Solid-State Circuits* **56**, 19–29 (2021). Publisher: IEEE.

- [63] Zhang, Y., Li, Y., Feng, S. & Poon, A. W. Towards Adaptively Tuned Silicon Microring Resonators for Optical Networks-on-Chip Applications. *IEEE Journal of Selected Topics in Quantum Electronics* **20**, 136–149 (2014).

- [64] Liu, J. et al. Silicon mode-loop Mach-Zehnder modulator with L-shaped PN junction for 0.37 V·cm  $V_{\pi}L$  high-efficiency modulation. Photonics Research 10, 214–221 (2022).

- [65] Yong, Z. et al. U-shaped PN junctions for efficient silicon Mach-Zehnder and microring modulators in the O-band. Optics Express 25, 8425–8439 (2017).

- [66] Itokawa, H., Ohno, H., Iinuma, T. & Suguro, K. Reduction in pn Junction Leakage for Ni-Silicided Small Si Islands by Using Improved Convection Annealing. *Japanese Journal of Applied Physics* 48, 076503 (2009).

- [67] Horiuchi, M. & Ohoyu, K. Reduction of PN junction leakage current by using poly-Si interlayered SOI wafers. IEEE Transactions on Electron Devices 42, 876–882 (1995).

- [68] Hsu, W.-C., Zhou, B. & Wang, A. X. MOS Capacitor-Driven Silicon Modulators: A Mini Review and Comparative Analysis of Modulation Efficiency and Optical Loss. *IEEE Journal of Selected Topics in Quantum Electronics* 28, 1–11 (2022).

- [69] Chmielak, B. et al. Pockels effect based fully integrated, strained silicon electro-optic modulator. Optics Express 19, 17212–17219 (2011).

- [70] Azadeh, S. S., Merget, F., Nezhad, M. P. & Witzens, J. On the measurement of the Pockels effect in strained silicon. *Optics Letters* **40**, 1877–1880 (2015).

- [71] Eltes, F. et al. A BaTiO3-Based Electro-Optic Pockels Modulator Monolithically Integrated on an Advanced Silicon Photonics Platform. *Journal of Lightwave Technology* 37, 1456–1462 (2019).

- [72] Shekhar, S. et al. Roadmapping the Next Generation of Silicon Photonics. Nature Communications (2024).

- [73] Geis, M., Spector, S., Williamson, R. & Lyszczarz, T. Submicrosecond submilliwatt silicon-on-insulator thermooptic switch. *IEEE Photonics Technology Letters* **16**, 2514–2516 (2004).

- [74] Ma, X. et al. High-density Integrated Photonic Tensor Processing Unit with a Matrix Multiply Compiler (2022). URL https://doi.org/10.21203/rs.3.rs-1833027/v1. Accessed on 2023-09-19.

- [75] Tait, A. N. Silicon Photonic Neural Networks. Ph.D. thesis, Princeton University (2018).

- [76] Hui, R. & O'sullivan, M. in Chapter 3 Characterization of optical devices (eds Hui, R. & O'sullivan, M.) Fiber-Optic Measurement Techniques (Second Edition) 297–446 (Academic Press, 2023).

- [77] Di Patrizio Stanchieri, G. et al. A 1.8 V Low-Power Low-Noise High Tunable Gain TIA for CMOS Integrated Optoelectronic Biomedical Applications. *Electronics* 11, 1271 (2022).

- [78] Chuah, J. H. & Holburn, D. Design of Low-Noise High-Gain CMOS Transimpedance Amplifier for Intelligent Sensing of Secondary Electrons. *IEEE Sensors Journal* 15, 5997–6004 (2015).

- [79] Wang, P. et al. A Multi-Channel Low-Noise Analog Front End Circuit for Linear LADAR. *IEEE Transactions on Circuits and Systems II: Express Briefs* **67**, 1209–1213 (2020).

- [80] Li, H., Balamurugan, G., Jaussi, J. & Casper, B. A 112 Gb/s PAM4 Linear TIA with 0.96 pJ/bit Energy Efficiency in 28 nm CMOS | IEEE Conference Publication | IEEE Xplore. ESSCIRC 2018 IEEE 44th European Solid State Circuits Conference (ESSCIRC) (2018).

- [81] Taghavi, I. et al. Polymer modulators in silicon photonics: review and projections. Nanophotonics 11, 3855–3871 (2022).

- [82] Chang, L., Liu, S. & Bowers, J. E. Integrated optical frequency comb technologies. *Nature Photonics* **16**, 95–108 (2022).

- [83] Cheung, S., Kawakita, Y., Shang, K. & Yoo, S. J. B. Highly efficient chip-scale III-V/silicon hybrid optical amplifiers. *Optics Express* 23, 22431–22443 (2015).

- [84] Rahim, A. et al. Taking silicon photonics modulators to a higher performance level: state-of-the-art and a review of new technologies. Advanced Photonics 3, 024003 (2021).

- [85] Liu, S. et al. Thermo-optic phase shifters based on silicon-on-insulator platform: state-of-the-art and a review. Frontiers of Optoelectronics 15, 9 (2022).

| Figure of Merit                  | DEOAM (This Work) DRAM <sup>3</sup> | $\mathrm{DRAM}^3$         | PCM (E)                   | OAM         | FG                      | MEMS (O)                 | MEMS (E)             | MO                     | 표                                | $^{ m LC}$               |

|----------------------------------|-------------------------------------|---------------------------|---------------------------|-------------|-------------------------|--------------------------|----------------------|------------------------|----------------------------------|--------------------------|

| Endurance (cycles)               | 86981                               | 10P[41]                   | $2T^{[42]}$               | $2k^{[43]}$ | $10\mathrm{M}^{[44]}$   | 30[21]                   | $10G^{[21]}$         | 7[21]                  | 300[21]                          | 30[21]                   |

| Retention Time                   | $573.53 \ \mu s$                    | $64 \text{ ms}^{[21]}$    | $10 \text{ years}^{[45]}$ |             | $1 \text{ year}^{[47]}$ | 1                        |                      | 1                      | ,                                |                          |

| Write Energy Consumption (J/bit) | 55.97p                              | $3.97 \mathrm{p}^{[48]}$  | $2.5\mu^{[21]}$           |             | $5.4 \mathrm{m}^{[50]}$ | $10\mu^{[21]}$           | $1\mathrm{p}^{[21]}$ | $33.3n[^{21}]$         | $10\mathrm{p}^{[21]}$            | 7.5p[21]                 |

| Write Time                       | 63.3 ns                             | $13.75 \text{ ns}^{[51]}$ | 500  ps[52]               | •           | $1.5 \text{ ms}^{[50]}$ | $125 \ \mu s^{[21]}^{2}$ | $5 \ \mu s^{[21]2}$  | $500 \text{ ns}[21]^2$ | $500 \text{ ns}[\frac{21}{2}]^2$ | $500 \text{ ms}^{[21]2}$ |

| Area $(\mu m^2)$                 | 10000                               | $0.0023^{[53]}$           | $0.001^{[42]}$            |             | $0.00027^{[54]}$        | $400^{[21]}$             | 10000[21]            | 8000[21]               | $20000^{[21]}$                   | $315^{[21]}$             |

Table 2: Key FoMs for state-of-the-art analog memory technologies, which include phase change materials (PCM), optical analog memories (OAM), floating gate (FG) memories, DRAM, micro-electromechanical systems (MEMS), magneto-optic (MO) memories, ferro-electric (FE) memories, and trapped charge (TC) memories. Some analog memory technologies are denoted with electrical (E) or optical (O) for its switching ability.

<sup>1</sup>Write cycles measured until now and can be extended given time for measurement.

<sup>2</sup>Write time is calculated from frequency  $(t_{wr}=1/(2f)$  where  $t_{wr}$  is the write time in seconds and f is the frequency in Hz).

<sup>3</sup>Reported DRAM characteristics are for isolated DRAM memory chips that are not monolithically integrated with the CMOS computing chip and does not account for leakage in the PN junction MRR and its dependence on optical power.

| Specification                                        | Laser $[82]$ | SOA [83]             | DEOAM (This Work) PD and TIA [79] | PD and TIA [79]      | Input Data Modulators [84] | Thermal Stabilizers [85] |

|------------------------------------------------------|--------------|----------------------|-----------------------------------|----------------------|----------------------------|--------------------------|

| Average Power Consumption Per Device (mW) 100 - 1000 | 100 - 1000   | 300 - 1000           | $1^{1}$                           | 37                   | 1                          | <30                      |

| Energy Consumption Per Device $(\mu J)$              | 5 - 50       | 15 - 50              | 0.05                              | 1.85                 | 40E-9 - 1E-6               | <1.5                     |

| Required Number of Devices                           | 10           | $50 \times 10 = 500$ | $50 \times 80 \times 10 = 40000$  | $50 \times 10 = 500$ | 80x10 = 800                | 50x80x10 + 10 = 40010    |

| Total Energy Consumption $(\mu J)$                   | 50 - 500     | 7500 - 25000         | 2000                              | 925                  | 32E-6 - 800E-6             | <60015                   |

|                                                      |              |                      |                                   |                      |                            |                          |

Table E1: Training energy consumption analysis for the neuromorphic photonic circuit in Figure 4 using DEOAM. Total energy consumption for each device group is calculated from average power consumption, training time (for DEOAM which is 50  $\mu$ s from Figure 6), and number of devices required for the neural network. Results show that optical power delivery (lasers and SOAs), thermal stabilization, and DEOAM consume the most amount of energy.

$^{1}$ Calculated based on nominal write energy and write time.