# RESURF Ga<sub>2</sub>O<sub>3</sub>-on-SiC Field Effect Transistors for Enhanced Breakdown Voltage

Junting Chen, Graduate Student Member, IEEE, Junlei Zhao, Jin Wei, and Mengyuan Hua, Member, IEEE

Abstract—Heterosubstrates have been extensively studied as a method to improve the heat dissipation of Ga2O3 devices. In this simulation work, we propose a novel role for p-type available heterosubstrates, as a component of a reduced surface field (RESURF) structure in Ga2O3 lateral field-effect transistors (FETs). The RESURF structure can eliminate the electric field crowding and contribute to higher breakdown voltage. Using SiC as an example, the designing strategy for doping concentration and dimensions of the p-type region is systematically studied using TCAD modeling. To mimic realistic devices, the impacts of interface charge and binding interlayer at the Ga<sub>2</sub>O<sub>3</sub>/SiC interface are also explored. Additionally, the feasibility of the RESURF structure for high-frequency switching operation is supported by the short time constant ( $\sim$ 0.5 ns) of charging/discharging the p-SiC depletion region. This study demonstrates the great potential of utilizing the electrical properties of heat-dissipating heterosubstrates to achieve a uniform electric field distribution in Ga<sub>2</sub>O<sub>3</sub> FETs.

Index Terms—Ga<sub>2</sub>O<sub>3</sub>, heterosubstrate, SiC, RESURF, field effect transistors

#### I. INTRODUCTION

**G** ALLIUM oxide (Ga<sub>2</sub>O<sub>3</sub>) has attracted intensive research interests in deep-ultraviolet photodetectors [1], power electronics [2], [3], and radio-frequency applications [4] in recent years. With the merit of intrinsic material properties of Ga<sub>2</sub>O<sub>3</sub>, such as ultrawide bandgap ( $E_g \simeq 4.8 \text{ eV}$ ), high critical electric field ( $E_{\text{crit.}} \simeq 8 \text{ MV} \cdot \text{cm}$ ), and decent electron mobility ( $\mu_n \simeq 200 \text{ cm}^2 \cdot \text{V}^{-1} \cdot \text{s}^{-1}$ ), the Ga<sub>2</sub>O<sub>3</sub>-based power electronics have much higher Baliga's figure of merit (BFOM) compared to Si and other wide-bandgap semiconductors [3]. However, the intrinsically low thermal conductivity of Ga<sub>2</sub>O<sub>3</sub> ( $\kappa_T \simeq 0.1$ -0.3 W·m<sup>-1</sup>·K<sup>-1</sup> [5]) becomes a major obstacle in the design of power electronics, because the resultant high thermal resistance and self-heating effects seriously hamper the efficiency,

Manuscript received xx Month 2023; revised xx Month 2023; accepted xx Month 2023. Date of publication xx Month 2023; date of current version xx Month 2023. The review of this article was arranged by Editor Xxxx. Yyyyy. (Corresponding author: Mengyuan Hua.)

Junting Chen is with the Department of Electrical and Electronic Engineering, Southern University of Science and Technology, Shenzhen 518055, China, and also with the Department of Electronic and Computer Engineering, The Hong Kong University of Science and Technology, Hong Kong, China.

Junlei Zhao, and Mengyuan Hua is with the Department of Electrical and Electronic Engineering, Southern University of Science and Technology, Shenzhen 518055, China (e-mail: huamy@sustech.edu.cn).

Jin Wei is with the Department of Electrical and Electronic Engineering, Peking University, Beijing 100871, China. reliability, and scalability of the Ga<sub>2</sub>O<sub>3</sub> power devices [6], and hence their competitiveness in power applications.

As a remedy for this thermal management challenge, heat dissipation of Ga<sub>2</sub>O<sub>3</sub>-based devices can be improved by utilizing heterogeneous semiconductor substrates with higher thermal conductivity, such as sapphire [7], [8], diamond [9]-[11], GaN, and SiC. Among these heterosubstrates, SiC is an attractive choice owing to its high thermal conductivity and low cost. The thermal conductivity of SiC is 490 W·m<sup>-1</sup>·K<sup>-1</sup>, better than most typical semiconductor substrates (e.g., 150  $W \cdot m^{-1} \cdot K^{-1}$  for Si, 46  $W \cdot m^{-1} \cdot K^{-1}$  for sapphire, and 130 W·m<sup>-1</sup>·K<sup>-1</sup> for GaN [12]). Compared with diamond, large-diameter SiC wafers can be produced at a much lower cost which can be further reduced with polycrystalline samples [13]. Heterogeneous binding of Ga<sub>2</sub>O<sub>3</sub> on SiC substrate has been demonstrated through surface activation bonding [13], fusion bonding [12], and direct growth [14], [15]. Moreover, wafer-scale integration of hundreds-nm  $Ga_2O_3$ thin film on SiC can be achieved with the ion-cutting technique [16].

As a result of the effectively promoted heat dissipation,  $Ga_2O_3$  field-effect transistors (FETs) based on such heterosubstrates deliver improved thermal stability and suppressed selfheating effects [17], [18]. Currently, overcoming the interfacial thermal impediments of the heterogeneous integration is still an active area of research. However, the investigations are mainly focused on the thermal properties and heat dissipation, whereas the electrical properties of the heterosubstrates and their potential benefits for the power electronics have not been extensively explored.

In this work, we demonstrate the utilization of *p*-type doping of SiC heterosubstrate as a component of a reduced surface field (RESURF) structure to suppress electric field (E-field) crowding in lateral  $Ga_2O_3$  FETs. The *E*-field crowding is one of the major issues that limit the breakdown voltages (BVs) of lateral high-voltage devices. The RESURF technology is firstly developed to address this issue in silicon devices [19], and is later implemented in SiC [20], [21], and GaN devices [22], showing remarkable benefits in terms of more evenly-distributed E-field, and thus higher BVs. As for  $Ga_2O_3$ , the lack of *p*-type doping techniques poses a fundamental challenge to realizing the RESURF structures. In contrast, ptype doping is readily available for SiC substrates. The upper limit of the acceptor doping concentration in SiC is as high as  $10^{20}$  cm<sup>-3</sup>, with the feasibility of selective-area doping. Therefore, in addition to improving the thermal dissipation,

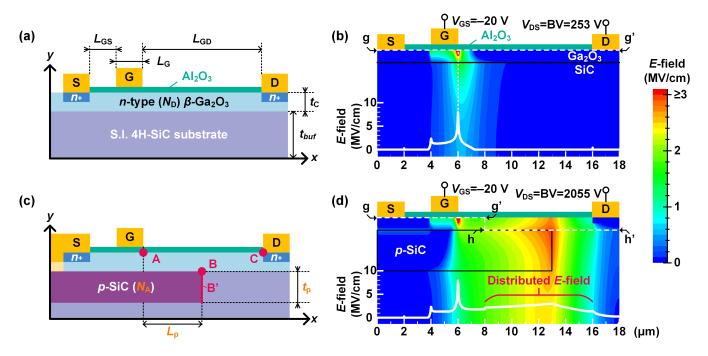

Fig. 1. Schematic structures and *E*-field strengths at breakdown voltages of (a,b) conventional Ga<sub>2</sub>O<sub>3</sub>/SiC FET; and (c,d) FET with the *n*-Ga<sub>2</sub>O<sub>3</sub>/*p*-SiC RESURF structures. The device with RESURF structures withstands much higher  $V_{DS}$ . In (b), the *E*-field along cutline g-g' is shown in the inset. In (d), the *E*-field along cutline g-g' and h-h' is shown in the inset. The red dots (A, B, and C) and red line (B') in (c) are potential breakdown positions, and are critical in the following discussion. The values of key simulation parameters in (a):  $L_{GS}$ ,  $L_G$ ,  $L_{GD}$ ,  $t_c$ ,  $t_{buf}$ ,  $N_D$  are 2 µm, 2 µm, 10 µm, 0.2 µm, 1.5 µm, and  $3 \times 10^{17}$  cm<sup>-3</sup>, respectively. One of the optimal values of  $N_A$ ,  $L_p$ ,  $t_p$  that used in (d) is  $0.6 \times 10^{17}$  cm<sup>-3</sup>, 7 µm, 0.65 µm, respectively. The breakdown is defined as the *E*-field in the Ga<sub>2</sub>O<sub>3</sub> reaches 8 MV·cm<sup>-1</sup>, or the *E*-field in the SiC reaches 3 MV·cm<sup>-1</sup>.

the  $Ga_2O_3$ -on-SiC heterosubstrate also offers an excellent platform to construct RESURF structures with *n*-type  $Ga_2O_3$ to achieve a more evenly distributed *E*-field, and thus higher BV. To guide the experimental demonstration of the RESURF structures, the impact of key parameters, such as acceptor concentration ( $N_A$ ) and dimensions of the *p*-SiC region are studied. To mimic the realistic devices, the influences of  $Al_2O_3$ binding interlayer and charges at the  $Ga_2O_3/SiC$  interface are investigated. In final, the charging/discharging rates of the *p*-SiC region during the fast switching transient are also investigated.

## II. PROPOSAL OF RESURF STRUCTURES AND FABRICATING FEASIBILITY

As shown in Fig. 1, the device structure (Fig. 1 (a)) and the E-field distribution (Fig. 1 (b)) of the conventional heterosubstrate Ga<sub>2</sub>O<sub>3</sub>-on-SiC FET is compared with that of a proposed selective-area *p*-SiC RESURF FET (Fig. 1 (c) and (d)). In the conventional FET, the *E*-field crowds at the drain-side gate corner, and the BV of the device is 253 V. By introducing a selective-area *p*-SiC with optimal parameters (Fig. 1 (d)), the *E*-field is distributed over a larger area instead of crowding at the gate corner, benefiting to a higher BV of 2055 V. It is noticed that, the RESURF structures can be combined with other techniques (e.g., field plates [23], and *p*-NiO [24] on the top surface) to further increase the BV of devices.

The fabrication of the proposed RESURF  $Ga_2O_3$ -on-SiC FETs is feasible based on existing techniques. The conventional  $Ga_2O_3$ -on-SiC FETs have been successfully fabricated [16], [25], [26]. Based on the existing devices, the fabri-

cation of the proposed RESURF FETs requires two additional steps: (i) the selective area *p*-doping of the SiC substrate, and (ii) the Ohmic contact of the p-SiC. The selective-area *p*-doping technique is well-established and commonly used in SiC devices [27]. Moreover, the doping of the SiC substrate can be done before integrated to the Ga<sub>2</sub>O<sub>3</sub> layer, so the engineering of p-SiC region is rather independent from the following fabrication of Ga<sub>2</sub>O<sub>3</sub> devices. As for the Ohmic contact, forming Ohmic contact to the p-SiC needs high temperature (600-1100 °C) annealing process [28], whereas forming Ohmic contact to the n-Ga2O3 needs low temperature (400-600 °C) annealing process [29]. As a result, the Ohmic contact to the p-SiC should be formed before the formation of the Ohmic contact to the n-Ga<sub>2</sub>O<sub>3</sub>. Overall, utilizing the electrical properties of the heterosubstrate by the proposed RESURF structures would not add too much complexity to the device fabrication process.

## **III.** E-FIELD REGULATION IN RESURF STRUCTURES

In this section, the impacts of the three key parameters, including the acceptor concentration  $(N_A)$ , the thickness  $(t_p)$ , and the length  $(L_p)$  of the *p*-SiC region (as illustrated in Fig. 1 (c)) are systemically studied. Meanwhile, the influence of the interface charges and the Al<sub>2</sub>O<sub>3</sub> interlayer at the Ga<sub>2</sub>O<sub>3</sub>/SiC interface in practical devices are also discussed. In the following discussions, as labeled in Fig. 1 (c), three critical potential breakdown positions are: (i) the gate corner at drain side (point A), (ii) the *p*-SiC edge at drain side (line B'), and (iii) the corner of the drain-side  $n^+$ -Ga<sub>2</sub>O<sub>3</sub> (point C). We note that the *E*-field at point B is very close or equal (97-100% at

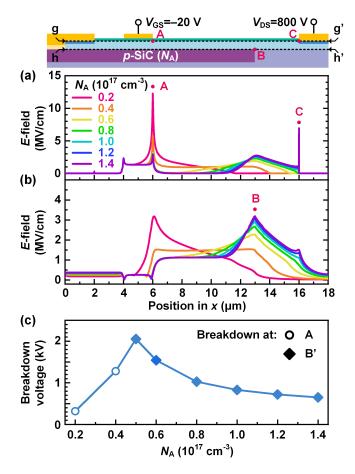

Fig. 2. *E*-field strength along cutline (a) g-g' and (b) h-h' of FET with the n-Ga<sub>2</sub>O<sub>3</sub>/p-SiC RESURF structure with increasing  $N_A$  at  $V_{DS}$  = 800 V. Fixed  $L_p$  = 7 µm and  $t_p$  = 0.8 µm (c) Overall BVs depending on the  $N_A$ .

$V_{\rm DS}$ =800 V) to the peak value of the *E*-field along line B'. Therefore, for simplicity, the *E*-field at point B will be used to represent that along line B'.

### A. Acceptor Concentration of the p-SiC

Fig. 2 (a) and (b) show the E-field distribution along the cutlines g-g' and h-h', respectively, with the different  $N_{\rm A}$ in the p-SiC at a  $V_{\rm DS}$  of 800 V. Without the RESURF structures, the E-field tends to crowd at point A, leading to low-voltage device breakdown. Low-level p-doping ( $N_{\rm A}$ in range of  $0.2-0.6 \times 10^{17}$  cm<sup>-3</sup>) contributes negative space charge in the p-SiC to terminate a part of the E-field that originally directs to point A, and results in a fast reduction of the *E*-field at point A from 12.2 MV·cm<sup>-1</sup> to 3.1 MV·cm<sup>-1</sup>. However, as a compensation, the E-field at point B increases from 0.4 MV·cm<sup>-1</sup> to 2.3 MV·cm<sup>-1</sup>. With the  $N_A$  further increasing to  $1.4 \times 10^{17}$  cm<sup>-3</sup>, more holes in the *p*-SiC can further deplete the Ga<sub>2</sub>O<sub>3</sub> channel. Consequently, the depletion region in the Ga<sub>2</sub>O<sub>3</sub> extends toward drain terminal, leading to the E-field at point C increases from 0.4 MV·cm<sup>-1</sup> to 6.9 MV  $\cdot$  cm<sup>-1</sup>, and that at point B further increases to 3.2 MV·cm<sup>-1</sup>. Meanwhile, the *E*-field at point A shows less significant decrease (2.7 MV·cm<sup>-1</sup> at  $N_A$  of 1.4×10<sup>17</sup> cm<sup>-3</sup>). Since line B' (p-SiC) has a lower critical E-field

Since line B' (*p*-SiC) has a lower critical *E*-field (3 MV·cm<sup>-1</sup>) compared to point A (Ga<sub>2</sub>O<sub>3</sub>, 8 MV·cm<sup>-1</sup>), the

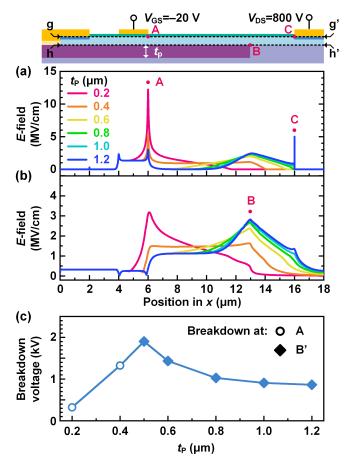

Fig. 3. *E*-field strength along cutline (a) g-g' and (b) h-h' of FET with the *n*-Ga<sub>2</sub>O<sub>3</sub>/*p*-SiC RESURF structure with changing  $t_p$  at  $V_{DS}$  = 800 V. Fixed  $N_A$  = 0.8×10<sup>17</sup> cm<sup>-3</sup> and  $L_p$  = 7 µm. (c) Overall breakdown voltages depending on the  $t_p$ .

breakdown point can easily transfer from point A to line B' when the *p*-SiC starts to terminate the *E*-field. Fig. 2 (c) shows the relationship between the overall BV and  $N_A$ . When the  $N_A$  increases from  $0.2 \times 10^{17}$  to  $0.5 \times 10^{17}$  cm<sup>-3</sup>, the BV increases because the *E*-field at point A is reduced. Starting from the  $N_A$  of  $0.5 \times 10^{17}$  cm<sup>-3</sup>, the breakdown at line B' dominates the breakdown of the devices. The BV decreases with the further increasing of  $N_A$  due to the increase of the *E*-field along line B'. Overall, the  $N_A$  of  $0.5 \times 10^{17}$  cm<sup>-3</sup> is the nearly balanced value for the *E*-field at points A and B to simultaneously reach their critical *E*-fields.

#### B. Thickness of the p-SiC

As shown in the Fig. 3 (a) and (b), the effect of  $t_p$  on the *E*-field distribution is similar to that of  $N_A$ . As expected, the increase of  $t_p$  firstly redirects a portion of the *E*-field from point A to point B, indicated as a fast reduction of *E*field at point A. Moreover, the further increase of  $t_p$  extends the depletion region of the *n*-Ga<sub>2</sub>O<sub>3</sub> channel toward drain terminal, resulting in the larger *E*-field from point C to point B. Similar to the overall trend in Fig. 2 (c), the BV increases with  $t_p$  increasing from 0.2 µm to 0.5 µm (Fig. 3 (c)), owning to the reduction of *E*-field peak at point A. Then, the

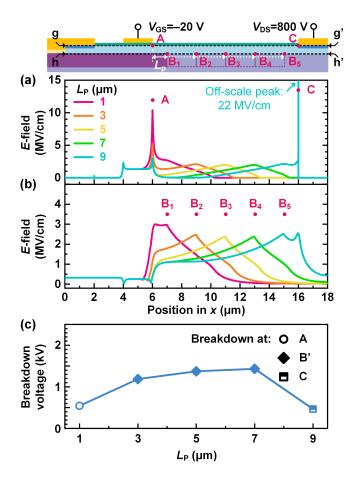

Fig. 4. *E*-field strength along cutline (a) g-g' and (b) h-h' of FET with the n-Ga<sub>2</sub>O<sub>3</sub>/p-SiC RESURF structure with changing  $L_p$  at  $V_{DS}$  = 800 V. Fixed  $N_A$  = 0.8×10<sup>17</sup> cm<sup>-3</sup> and  $t_p$  = 0.6 µm. (c) Overall BVs depending on the  $L_p$ .

BV decreases with the  $t_p$  further increasing from 0.5 µm to 1.2 µm owing to the increase of the *E*-field peak at point B.

Based on the analyses shown in Figs. 2 and 3, we conclude that an optimal overall BV of the device can be reached by carefully engineering the  $N_A$  and  $t_p$  in the *p*-SiC region with respect to a balanced *E*-field distribution simultaneously close to the critical points of the *E*-field at point A in Ga<sub>2</sub>O<sub>3</sub> and point B in SiC. It is worth noting that, in both Fig. 2 (a) and Fig. 3 (a), *E*-field peaks appear at point C when the  $N_A$  and  $t_p$  is very large (at  $N_A$  of  $1.4 \times 10^{17}$  cm<sup>-3</sup> and  $t_p$  of 1.2  $\mu$ m, respectively). However, in those cases, the line B' in the SiC breakdowns before the *E*-field at point C would not be a critical value. As a result, the *E*-field at point C would not be a critical concern as long as  $N_A$  and  $t_p$  is not aggressively large.

## C. Length of the p-SiC

Fig. 4 (a) and (b) show the *E*-field distribution with different  $L_{\rm p}$ . The *p*-SiC region with too short  $L_{\rm p}$  can not sufficiently block the *E*-field from crowding at point A. An *E*-field peak of 8.5 MV·cm<sup>-1</sup> can be seen at the  $L_{\rm p}$  of 1 µm. On the other hand, the *p*-SiC should not be too close to the drain terminal, otherwise it will cause the *E*-field to crowd at point C. A sudden increase of the *E*-field peak at point C (22 MV·cm<sup>-1</sup>) can be found when the  $L_{\rm p}$  reaches 9 µm (Fig. 4 (a)). When

Fig. 5. Effects of the different types of charge at the  $Ga_2O_3/SiC$  interfaces on the BVs. Fixed  $N_A = 0.6 \times 10^{17}$  cm<sup>-3</sup>,  $t_p = 0.6 \mu$ m, and  $L_p = 7 \mu$ m.

the  $L_{\rm p}$  is in a proper range (3-7 µm in this simulation), the *E*-field at point A and point B decreases monotonically with  $L_{\rm p}$  increase (Fig. 4 (b)), because a longer *p*-SiC benefits to a longer depletion region in the Ga<sub>2</sub>O<sub>3</sub> channel, and thus a smaller *E*-field at a same  $V_{\rm DS}$  bias. To sum up, an  $L_{\rm p}$  of 7 µm is the optimal  $L_{\rm p}$  in this simulation, which provides a wide depletion region in Ga<sub>2</sub>O<sub>3</sub> channel, but does not lead to *E*-field crowing at point C.

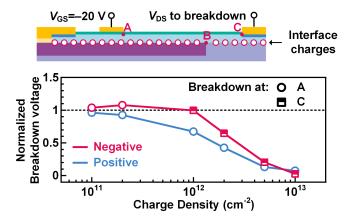

#### D. Interface Charge

To mimic the realistic condition of device, the impact of net charges at the Ga<sub>2</sub>O<sub>3</sub>/SiC interface is studied. In Fig. 5, the BV with respect to the interface charge density is plotted. The BV is normalized to that of the device without interface charge. A small amount of negative charge  $(2 \times 10^{11} \text{ cm}^{-2})$ can act as field plates, which help blocking the point A from high *E*-field, thus slightly improve the breakdown voltage. As for the case where there is a large amount of negative interface charge, it is similar to the case where the  $L_p$  is very long (9 µm in Fig. 4). Excessive negative interface charge will cause the *E*-field to crowd at point C, lowering the breakdown voltage.

Positive interface charge has monotonic impact on the breakdown voltage. The positive interface charge compensates the negative space charge in the *p*-SiC region, and thus eliminates the improvement brought by the RESURF structures, causing the *E*-field to crowd at point A again. Moreover, the excessive positive interface charge can emit *E*-field to point A, further enhancing the *E*-field at point A. As a result, the BV decreases monotonically with positive interface charge. In practical applications, the interface charge at the Ga<sub>2</sub>O<sub>3</sub>/SiC interface should be carefully controlled.

## E. $Al_2O_3$ Interlayer

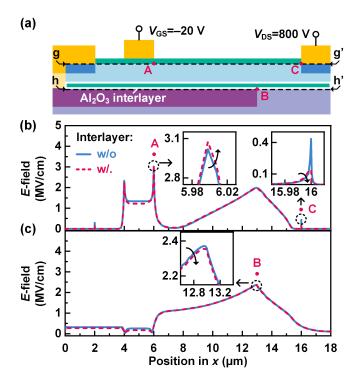

An additional  $Al_2O_3$  interlayer at the  $Ga_2O_3/SiC$  interface (Fig. 6 (a)) is often adopted to improve the interface binding quality and hence the thermal dissipation [16], [26]. The *E*-field distribution with and without the 20-nm  $Al_2O_3$  interlayer is compared in Fig. 6 (b) (cutline g-g') and Fig. 6 (c) (cutline h-h'). The  $Al_2O_3$  interlayer slightly weakens the impact of the

Fig. 6. (a) Schematic illustration of  $Al_2O_3$  interlayer. *E*-field strength along the cutlines (b) g-g' and (c) h-h' of the device with and without the 20-nm  $Al_2O_3$  interlayer. Fixed  $N_A = 0.8 \times 10^{17}$  cm<sup>-3</sup>,  $t_p = 0.8 \mu$ m, and  $L_p = 7 \mu$ m.  $V_{DS} = 800$  V.

RESURF structure, leading to a 1.7% increase of peak *E*-field at point A, a 0.4% decrease of peak *E*-field at point B, and a 67% decrease of peak *E*-field at point C. As points A and B are the dominate breakdown points in proper designed devices, and the influence of the  $Al_2O_3$  interlayer at points A and B is quite small, the  $Al_2O_3$  interlayer in the practical devices will not limit the adoption of the proposed RESURF structures.

In summary, with the preset dimensions and doping concentration of the *n*-Ga<sub>2</sub>O<sub>3</sub> channel epilayers, the optimal BV can be obtained when the point A and the line B' reach their critical *E*-field simultaneously. In the example shown in Fig. 1 (d), by carefully engineering the  $N_A$  and the dimensions of *p*-SiC, at  $V_{\rm DS}$ =BV=2055 V, the *E*-field at point A is 7.91 MV·cm<sup>-1</sup>, and that at point B is 2.99 MV·cm<sup>-1</sup>, indicating that point A and point B breakdown almost at the same time. Meanwhile, the interface charges should be minimized in practical fabrication process, and the binding interlayer has less impact on the BV.

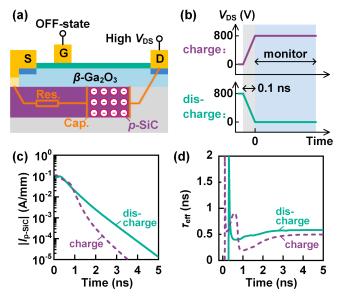

## IV. SWITCHING SPEED OF RESURF DEVICES

During practical switching process,  $V_{\rm DS}$  switches between high and low values. When the  $V_{\rm DS}$  switches to high values, holes will leave the *p*-SiC to establish a depletion region (Fig. 7 (a)). When the  $V_{\rm DS}$  switches to low values, holes will flow back to the *p*-SiC. The charging/discharging rate of the depletion region is limited by the contact resistance and sheet resistance of the *p*-SiC, and should be fast enough for high frequency applications. To estimate the (dis)charging time of the *p*-SiC's depletion region, the simulation in Fig. 7 (b) is

Fig. 7. (a) Schematic illustration of the depletion region in the *p*-SiC at high  $V_{\rm DS}$  bias, and its charging/discharging path. "Cap." represents the capacitor formed by the depletion region. "Res." is the equivalent resistance when charging/discharging the depletion region. (b) Illustration of the  $V_{\rm DS}$  waveform applied in the simulation. (c) Absolute current passing through the *p*-SiC region after a sudden rise/drop of  $V_{\rm DS}$ . (d) Extrapolated effective time constant ( $\tau_{\rm eff}$ ) of (dis)charging the *p*-SiC region. Fixed  $N_{\rm A} = 0.6 \times 10^{17}$  cm<sup>-3</sup>,  $t_p = 0.6 \ \mu m$ , and  $L_p = 7 \ \mu m$ . The contact resistance of the Ohmic contact to the *p*-SiC is calibrated to  $10^{-4} \ \Omega \cdot \text{cm}^{-2}$  [28]. The hole mobility in SiC is estimated to be  $100 \ \text{cm}^2 \cdot \text{V}^{-1} \cdot \text{s}^{-1}$  according to the  $N_{\rm A}$  [30].  $V_{\rm GS} = -20 \ \text{V}$ .

conducted. First,  $V_{\rm DS}$  is suddenly (within 0.1 ns) increased from 0 to 800 V (charging), or decreased from 800 to 0 V (discharging). Then, the current through the *p*-SiC is monitored (Fig. 7 (c)), from which the effective time constant ( $\tau_{\rm eff}$ ) for charging/discharging are both estimated to be ~0.5 ns after a ~0.5 ns of oscillation (Fig. 7 (d)). Therefore, the (dis)charging time (usually defined at  $5\tau_{\rm eff}$ ) for the *p*-SiC's depletion region is ~2.5 ns. The fast (dis)charging rate demonstrates the feasibility of such *p*-SiC RESURF structures in high frequency (MHz level) switching applications.

#### V. CONCLUSION

In this work, the electrical properties of heat-dissipating  $Ga_2O_3$ -on-SiC heterosubstrate have been utilized to construct RESURF structures in  $Ga_2O_3$  FETs. The proposed RESURF structures can evenly distribute the *E*-field to achieve higher BVs. With careful design of the  $N_A$  and dimensions of *p*-SiC, as well as eliminating the interface charges, the BV can be improved from 253 V to 2055 V with the RESURF structures. The  $Al_2O_3$  interlayer in the existing heterosubstrate devices has minimal influence on the RESURF structures. Additionally, RESURF  $Ga_2O_3$ -on-SiC FETs shows a fast (dis)charging rate for high-frequency switching applications. This study provides a demonstration of unlocking the full potential of heat-dissipating heterosubstrates by leveraging their electrical properties.

#### REFERENCES

- [1] S. J. Pearton, J. Yang, P. H. Cary, F. Ren, J. H.Kim, M. J. Tadjer, and M. A. Mastro, "A review of Ga<sub>2</sub>O<sub>3</sub> materials, processing, and devices," *Appl. Phys. Rev.*, vol. 5, no. 1, p. 011301, Jan. 2018, doi:10.1063/1.5006941.

- [2] J. Zhang, P. Dong, K. Dang, Y. Zhang, Q. Yan, H. Xiang, J. Su, Z. Liu, M. Si, J. Gao, M. Kong, H. Zhou, and Y. Hao, "Ultra-wide bandgap semiconductor Ga<sub>2</sub>O<sub>3</sub> power diodes," *Nat. Commun.*, vol. 13, no. 1, p. 3900, Jul. 2022, doi:10.1038/s41467-022-31664-y.

- [3] A. J. Green, J. Speck, G. Xing, P. Moens, F. Allerstam, K. Gumaelius, T. Neyer, Arias-PurdueAndrea, V. Mehrotra, A. Kuramata, K. Sasaki, S. Watanabe, K. Koshi, J. Blevins, O. Bierwagen, S. Krishnamoorthy, K. Leedy, A. R. Arehart, A. T. Neal, S. Mou, S. A. Ringel, A. Kumar, A. Sharma, K. Ghosh, U. Singisetti, W. Li, K. Chabak, K. Liddy, A. Islam, S. Rajan, S. Graham, S. Choi, Z. Cheng, and M. Higashiwaki, "β-gallium oxide power electronics," *APL Mater.*, vol. 10, no. 2, p. 029201, Feb. 2022, doi:10.1063/5.0060327.

- [4] M. Singh, M. A. Casbon, M. J. Uren, J. W. Pomeroy, S. Dalcanale, S. Karboyan, P. J. Tasker, M. H. Wong, K. Sasaki, A. Kuramata, S. Yamakoshi, M. Higashiwaki, and M. Kuball, "Pulsed large signal RF performance of field-plated Ga<sub>2</sub>O<sub>3</sub> MOSFETs," *IEEE Electron Device Lett.*, vol. 39, no. 10, pp. 1572–1575, Aug. 2018, doi:10.1109/LED.2018.2865832.

- [5] M. D. Santia, N. Tandon, and J. D. Albrecht, "Lattice thermal conductivity in β-Ga<sub>2</sub>O<sub>3</sub> from first principles," *Appl. Phys. Lett.*, vol. 107, no. 4, p. 041907, Jul. 2015, doi:10.1063/1.4927742.

- [6] Y. Zhang, B. Wang, M. Xiao, J. Spencer, R. Zhang, J. Knoll, C. Di-Marino, G.-Q. Lu, K. Sasaki, and C. Buttay, "(Invited) How to achieve low thermal resistance and high electrothermal ruggedness in Ga<sub>2</sub>O<sub>3</sub> devices?" *ECS Trans.*, vol. 104, no. 5, p. 21, Oct. 2021, doi:10.1149/10405.0021ecst.

- [7] Z. Hu, H. Zhou, K. Dang, Y. Cai, Z. Feng, Y. Gao, Q. Feng, J. Zhang, and Y. Hao, "Lateral β-Ga<sub>2</sub>O<sub>3</sub> Schottky barrier diode on sapphire substrate with reverse blocking voltage of 1.7 kV," *IEEE J. Electron Devices Soc.*, vol. 6, pp. 815–820, Jul. 2018, doi:10.1109/JEDS.2018.2853615.

- [8] A. Y. Polyakov, N. B. Smirnov, I. V. Shchemerov, E. B. Yakimov, V. I. Nikolaev, S. I. Stepanov, A. I. Pechnikov, A. V. Chernykh, K. D. Shcherbachev, A. S. Shikoh, A. Kochkova, A. A. Vasilev, and S. J. Pearton, "Deep trap spectra of Sn-doped α-Ga<sub>2</sub>O<sub>3</sub> grown by halide vapor phase epitaxy on sapphire," *APL Mater.*, vol. 7, no. 5, p. 051103, May 2019, doi:10.1063/1.5094787.

- [9] W. Wang, Q. Yuan, D. Han, J. Sun, N. Liu, S. Hu, C. Liu, W. Zhang, and J. Ye, "High-temperature deep ultraviolet photodetector based on a crystalline Ga<sub>2</sub>O<sub>3</sub>-diamond heterostructure," *IEEE Electron Device Lett.*, vol. 43, no. 12, pp. 2121–2124, Oct. 2022, doi:10.1109/LED.2022.3214981.

- [10] Z. Cheng, V. D. Wheeler, T. Bai, J. Shi, M. J. Tadjer, T. Feygelson, K. D. Hobart, M. S. Goorsky, and S. Graham, "Integration of polycrystalline Ga<sub>2</sub>O<sub>3</sub> on diamond for thermal management," *Appl. Phys. Lett.*, vol. 116, no. 6, p. 062105, Feb. 2020, doi:10.1063/1.5125637.

- [11] Z. Cheng, L. Yates, J. Shi, M. J. Tadjer, K. D. Hobart, and S. Graham, "Thermal conductance across β-Ga<sub>2</sub>O<sub>3</sub>-diamond van der Waals heterogeneous interfaces," *APL Mater.*, vol. 7, no. 3, p. 031118, Mar. 2019, doi:10.1063/1.5089559.

- [12] Y. Song, D. Shoemaker, J. H. Leach, C. McGray, H.-L. Huang, A. Bhattacharyya, Y. Zhang, C. U. Gonzalez-Valle, T. Hess, S. Zhukovsky, K. Ferri, R. M. Lavelle, C. Perez, D. W. Snyder, J.-P. Maria, B. Ramos-Alvarado, X. Wang, S. Krishnamoorthy, J. Hwang, B. M. Foley, and S. Choi, "Ga<sub>2</sub>O<sub>3</sub>-on-SiC composite wafer for thermal management of ultrawide bandgap electronics," *ACS Appl. Mater. Interfaces*, vol. 13, no. 34, pp. 40817–40829, Aug. 2021, doi:10.1021/acsami.1c09736.

- [13] C.-H. Lin, N. Hatta, K. Konishi, S. Watanabe, A. Kuramata, K. Yagi, and M. Higashiwaki, "Single-crystal-Ga<sub>2</sub>O<sub>3</sub>/polycrystalline-SiC bonded substrate with low thermal and electrical resistances at the heterointerface," *Appl. Phys. Lett.*, vol. 114, no. 3, p. 032103, Jan. 2019, doi:10.1063/1.5051720.

- [14] F. Hrubišák, K. Hušeková, X. Zheng, A. Rosová, E. Dobročka, M. Ťapajna, M. Mičušík, P. Nádaždy, F. Egyenes, J. Keshtkar, E. Kováčová, J. W. Pomeroy, M. Kuball, and F. Gucmann, "Heteroepitaxial growth of Ga<sub>2</sub>O<sub>3</sub> on 4H-SiC by liquid-injection MOCVD for improved thermal management of Ga<sub>2</sub>O<sub>3</sub> power devices," J. Vac. Sci. Technol. A, vol. 41, no. 4, p. 042708, Jun. 2023, doi:10.1116/6.0002649.

- [15] N. Nepal, D. S. Katzer, B. P. Downey, V. D. Wheeler, L. O. Nyakiti, D. F. Storm, M. T. Hardy, J. A. Freitas, E. N. Jin, D. Vaca, L. Yates, S. Graham, S. Kumar, and D. J. Meyer, "Heteroepitaxial growth of β-

Ga<sub>2</sub>O<sub>3</sub> films on SiC via molecular beam epitaxy," *J. Vac. Sci. Technol. A*, vol. 38, no. 6, p. 063406, Oct. 2020, doi:10.1116/6.0000452.

- [16] W. Xu, Y. Wang, T. You, X. Ou, G. Han, H. Hu, S. Zhang, F. Mu, T. Suga, Y. Zhang, Y. Hao, and X. Wang, "First demonstration of waferscale heterogeneous integration of Ga<sub>2</sub>O<sub>3</sub> MOSFETs on SiC and Si substrates by ion-cutting process," in 2019 IEEE International Electron Devices Meeting (IEDM), Dec. 2019, pp. 12.5.1–12.5.4, doi:10.1109/IEDM19573.2019.8993501.

- [17] B. K. Mahajan, Y.-P. Chen, J. Noh, P. D. Ye, and M. A. Alam, "Electrothermal performance limit of β-Ga<sub>2</sub>O<sub>3</sub> field-effect transistors," *Appl. Phys. Lett.*, vol. 115, no. 17, p. 173508, Oct. 2019, doi:10.1063/1.5116828.

- [18] S. A. O. Russell, A. Pérez-Tomás, C. F. McConville, C. A. Fisher, D. P. Hamilton, P. A. Mawby, and M. R. Jennings, "Heteroepitaxial β-Ga<sub>2</sub>O<sub>3</sub> on 4H-SiC for an FET with reduced self heating," *IEEE J. Electron Devices Soc.*, vol. 5, no. 4, pp. 256–261, May 2017, doi:10.1109/JEDS.2017.2706321.

- [19] J. Appels and H. Vaes, "High voltage thin layer devices (RESURF devices)," in 1979 IEEE International Electron Devices Meeting (IEDM), Dec. 1979, pp. 238–241, doi:10.1109/IEDM.1979.189589.

- [20] N. Saks, S. Mani, A. Agarwal, and M. Ancona, "A 475-V high-voltage 6H-SiC lateral MOSFET," *IEEE Electron Device Lett.*, vol. 20, no. 8, pp. 431–433, Aug. 1999, doi:10.1109/55.778167.

- [21] K. Chatty, S. Banerjee, T. Chow, and R. Gutmann, "High-voltage lateral RESURF MOSFETs on 4H-SiC," *IEEE Electron Device Lett.*, vol. 21, no. 7, pp. 356–358, Jul. 2000, doi:10.1109/55.847379.

- [22] S. Karmalkar, J. Deng, and M. Shur, "Resurf AlGaN/GaN HEMT for high voltage power switching," *IEEE Electron Device Lett.*, vol. 22, no. 8, pp. 373–375, Aug. 2001, doi:10.1109/55.936347.

- [23] S. Sharma, K. Zeng, S. Saha, and U. Singisetti "Field-plated lateral Ga<sub>2</sub>O<sub>3</sub> MOSFETs with polymer passivation and 8.03 kV breakdown voltage," *IEEE Electron Device Lett.*, vol. 41, no. 6, pp. 836–839, Apr. 2020, doi:10.1109/LED.2020.2991146.

- [24] Y. Wang, H. Gong, X. Jia, G. Han, J. Ye, Y. Liu, H. Hu, X. Ou, X. Ma, and Y. Hao, "First Demonstration of RESURF and Superjunction β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs with *p*-NiO/*n*-Ga<sub>2</sub>O<sub>3</sub> Junctions," in 2021 IEEE International Electron Devices Meeting (IEDM), Dec. 2021, pp. 36.6.1– 36.6.4, doi:10.1109/IEDM19574.2021.9720500.

- [25] Y. Song, A. Bhattacharyya, A. Karim, D. Shoemaker, H.-L. Huang, S. Roy, C. McGray, J. H. Leach, J. Hwang, S. Krishnamoorthy, and S. Choi, "Ultra-wide band gap Ga<sub>2</sub>O<sub>3</sub>-on-SiC MOSFETs," ACS Appl. Mater. Interfaces, vol. 15, no. 5, pp. 7137–7147, Jan. 2023, doi:10.1021/acsami.2c21048.

- [26] Y. Wang, W. Xu, G. Han, T. You, F. Mu, H. Hu, Y. Liu, X. Zhang, H. Huang, T. Suga, X. Ou, X. Ma, and Y. Hao, "Channel properties of Ga<sub>2</sub>O<sub>3</sub>-on-SiC MOSFETs," *IEEE Trans. Electron Devices*, vol. 68, no. 3, pp. 1185–1189, Jan. 2021, doi:10.1109/TED.2021.3051135.

- [27] P. Godignon, F. Torregrosa, and K. Zekentes, "Chapter 3–Silicon Carbide Doping by Ion Implantation," in *Advancing Silicon Carbide Electronics Technology II*, Millersville, PA, USA: Materials Research Forum LLC, 2020, pp. 107–174, doi:10.21741/9781644900673.

- [28] L. Huang, M. Xia, and X. Gu, "A critical review of theory and progress in Ohmic contacts to *p*-type SiC," *J. Cryst. Growth*, vol. 531, p. 125353, Feb. 2020, doi:10.1016/j.jcrysgro.2019.125353.

- [29] M.-H. Lee and R. L. Peterson, "Process and characterization of Ohmic contacts for beta-phase gallium oxide," *J. Mater. Res.*, vol. 36, no. 23, pp. 4771–4789, Aug. 2021, doi:10.1557/s43578-021-00334-y.

- [30] H. Matsuura, M. Komeda, S. Kagamihara, H. Iwata, R. Ishihara, T. Hatakeyama, T. Watanabe, K. Kojima, T. Shinohe, and K. Arai, "Dependence of acceptor levels and hole mobility on acceptor density and temperature in Al-doped *p*-type 4H-SiC epilayers," *J. Appl. Phys.*, vol. 96, no. 5, pp. 2708–2715, Sep. 2004, doi:10.1063/1.1775298.