## Institute of Theoretical and Applied Informatics, Polish Academy of Sciences

# VALIDATION AND BENCHMARKING OF QUANTUM ANNEALING TECHNOLOGY

DOCTORAL DISSERTATION

mgr Konrad Jałowiecki

Supervisor: dr hab. Bartłomiej Gardas

Co-supervisor: dr hab. inż. Łukasz Pawela

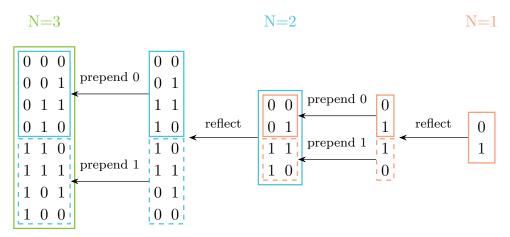

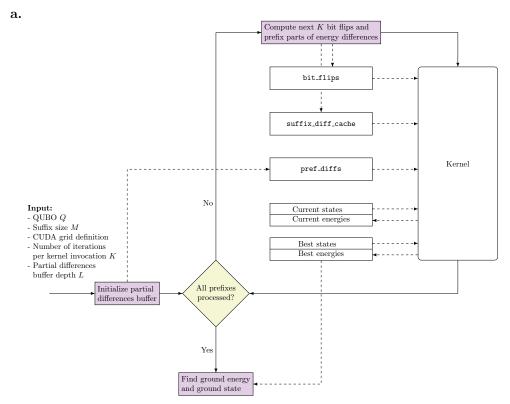

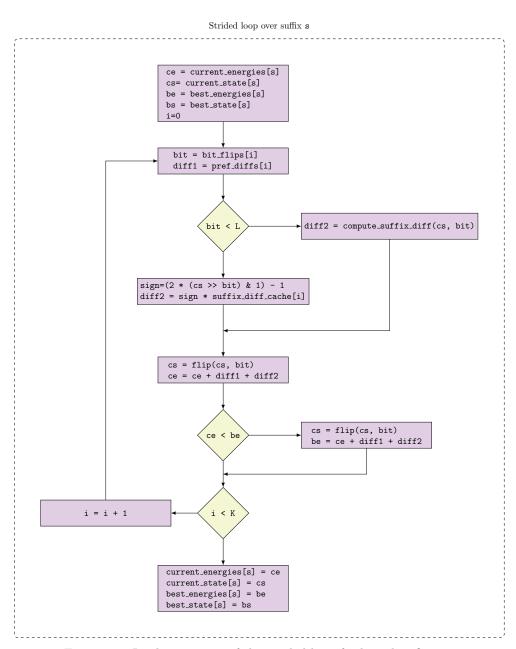

Katowice, November 24, 2023

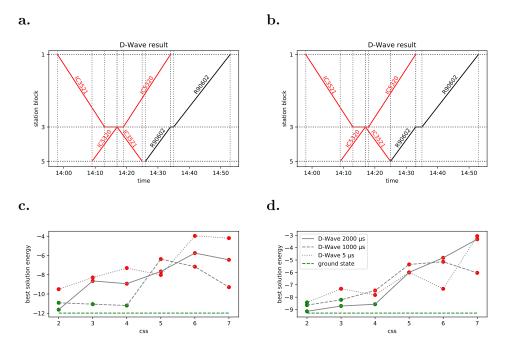

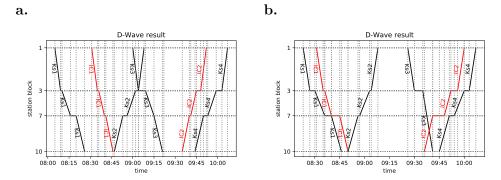

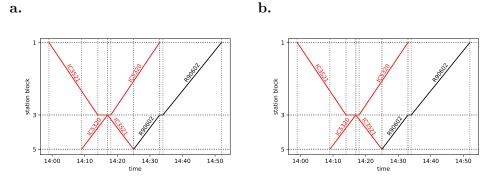

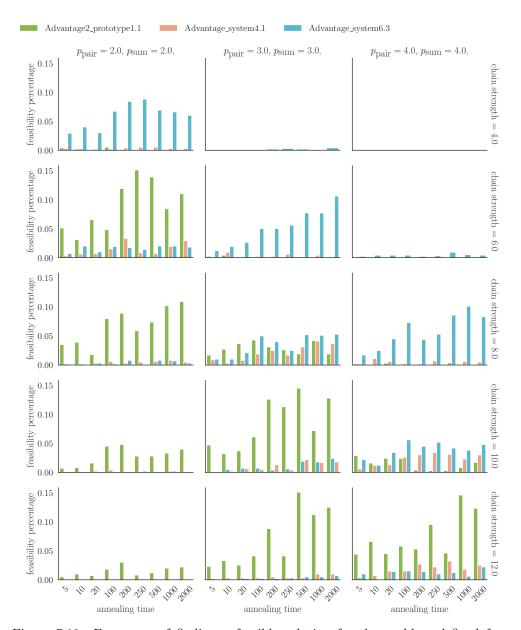

#### Instytut Informatyki Teoretycznej i Stosowanej Polskiej Akademii Nauk

#### Walidacja i testowanie porównawcze technologii kwantowego wyżarzania

#### Rozprawa doktorska

mgr Konrad JAŁOWIECKI

Promotor: dr hab. Bartłomiej Gardas

Promotor pomocniczy: dr hab. inż. Łukasz Pawela

Katowice, 24 listopada 2023

## Contents

| A  | ckno  | wledgements                                                    | iii          |

|----|-------|----------------------------------------------------------------|--------------|

| P  | ublis | hed work                                                       | $\mathbf{v}$ |

| A  | bstra | act                                                            | vii          |

| St | resz  | czenie                                                         | ix           |

| 1  | Int   | roduction                                                      | 1            |

| 2  | Isin  | ng model and QUBO problem                                      | 5            |

|    | 2.1   | Ising model                                                    | 6            |

|    | 2.2   | Algorithms and complexity                                      | 8            |

|    | 2.3   | Complexity classes                                             | 9            |

|    | 2.4   | Ising model and complexity                                     | 10           |

|    | 2.5   | Algorithms for solving Ising model                             | 11           |

|    | 2.6   | Quadratic Unconstrained Binary Optimization                    | 13           |

| 3  | Qua   | antum annealing and GPU computing                              | 17           |

|    | 3.1   | Adiabatic quantum computation and quantum annealing            | 17           |

|    | 3.2   | Nvidia CUDA                                                    | 28           |

| 4  | Sim   | nulating dynamics of quantum systems using quantum             |              |

|    | ann   | ealing                                                         | 39           |

|    | 4.1   | Parallel in time simulation of dynamical systems               | 40           |

|    | 4.2   | Solving systems of linear equations as an optimization problem | 42           |

|    | 4.3   | Discretizing variables                                         | 42           |

ii CONTENTS

|              | 4.4   | Parallel-in-time simulations with quantum annealer          | 44  |

|--------------|-------|-------------------------------------------------------------|-----|

| 5            | Sol   | ving spin-glass problems using tensor networks              | 49  |

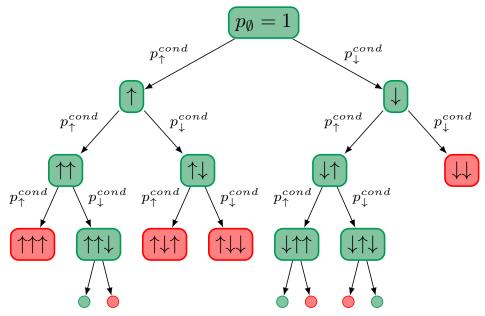

|              | 5.1   | Exploring the probability space                             | 49  |

|              | 5.2   | Branch and bound                                            | 50  |

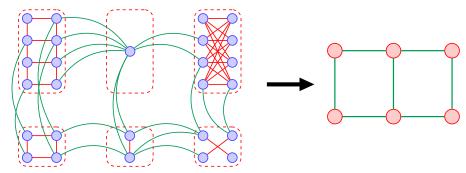

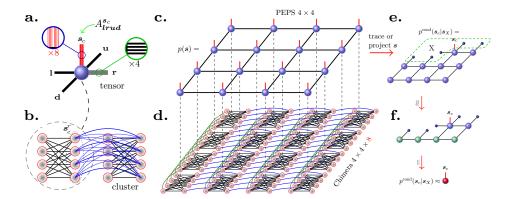

|              | 5.3   | PEPS network construction                                   | 52  |

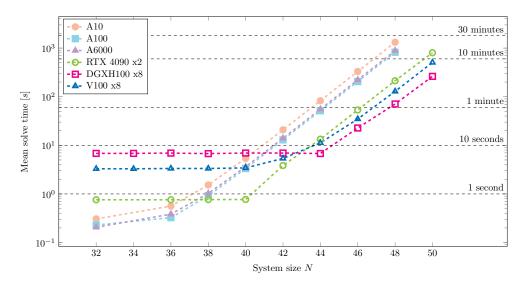

|              | 5.4   | Benchmarks                                                  | 53  |

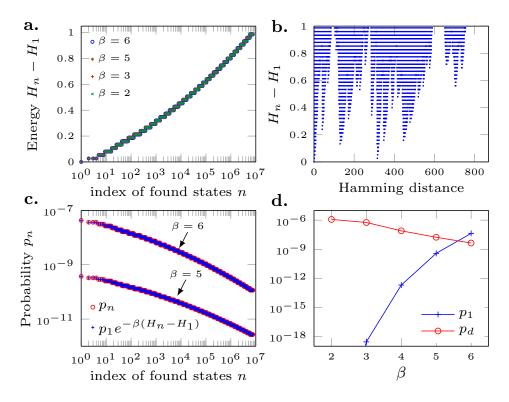

| 6            | Bru   | te-forcing spin-glass problems with CUDA                    | 59  |

|              | 6.1   | Finding low–energy spectrum with CUDA                       | 60  |

|              | 6.2   | Example application: verifying MPS-based optimization algo- |     |

|              |       | rithm                                                       | 65  |

|              | 6.3   | Improving the algorithm using Gray Code                     | 67  |

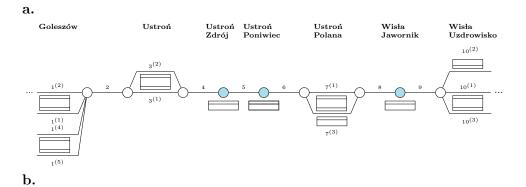

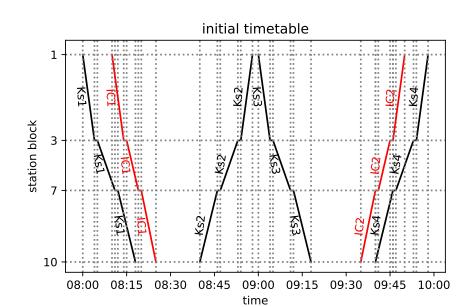

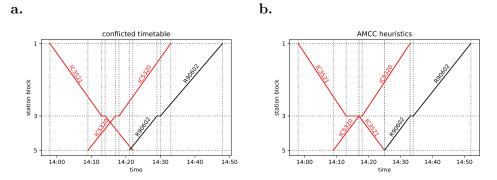

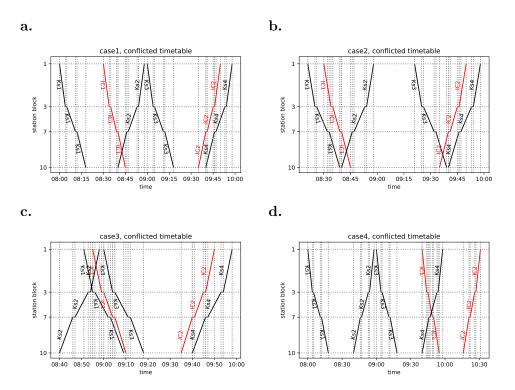

| 7            | Rai   | lway conflict management                                    | 79  |

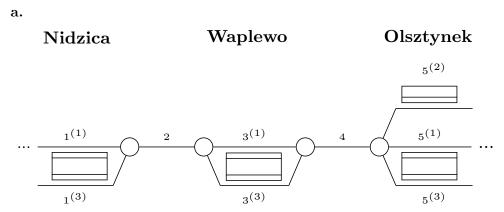

|              | 7.1   | Overview of the problem                                     | 79  |

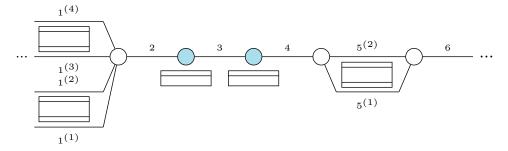

|              | 7.2   | The mathematical model                                      | 81  |

|              | 7.3   | Discretizing delays                                         | 84  |

|              | 7.4   | Dispatching conditions and the penalties                    | 85  |

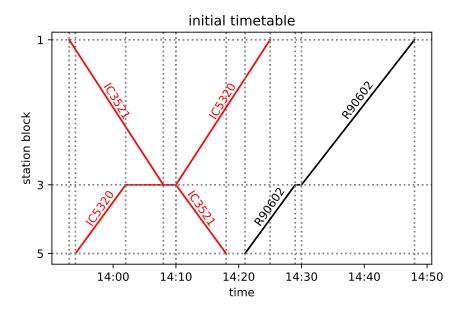

|              | 7.5   | Results                                                     | 87  |

| Bi           | bliog | graphy                                                      | 103 |

| A            | Asy   | emptotic notation                                           | 111 |

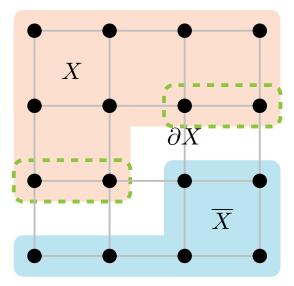

| В            | Cor   | nditional probability on square lattice                     | 113 |

| $\mathbf{C}$ | Dis   | patching conditions                                         | 115 |

| ~            | C.1   | The minimum passing time condition                          |     |

|              | C.2   | The single block occupation condition                       |     |

|              | C.3   | The deadlock condition                                      |     |

|              | C.4   | The rolling stock circulation condition                     |     |

|              | C.5   | The capacity condition                                      |     |

## Acknowledgements

I am deeply grateful to my supervisor, dr hab. Bartłomiej Gardas, whose unwavering support and insightful guidance have been instrumental in shaping this doctoral thesis. His expertise, encouragement, and mentorship have been invaluable, and I am truly fortunate to have had the opportunity to work under his supervision.

I would also like to express my sincere appreciation to my co-supervisor, dr hab. inż. Łukasz Pawela, for his constructive feedback, especially in the field of software engineering. His expertise and willingness to share knowledge have significantly enriched the quality of this thesis.

I would also like to express my gratitude to all my colleagues from the Institute who contributed to this thesis via many fruitful conversations I had with them. In particular, I would like to thank Krzysztof Domino for sharing his knowledge and expertise in the railway dispatching field.

Additionally, I extend my deepest gratitude to my friends, Alexander Juda, Michał Stęchły, and Paweł Grzybek, for taking the time to read parts of this thesis. Their valuable feedback contributed greatly to improving the readability and overall quality of this work.

This project was partially supported by the National Science Center (NCN), Poland, under Projects: Sonata Bis 10, No. 2020/38/E/ST3/00269 and the National Centre for Research and Development (NCBR), Poland, under Project No. POIR.01.01.01-00-0061/2. I would also like to thank The Quantum Data Center Corporation for providing me with access to several GPUs used for benchmarks presented in this thesis.

## Published work

#### Publications relevant for this dissertation

- [1] K. Jałowiecki, A. Więckowski, P. Gawron, and B. Gardas, *Parallel in time dynamics with quantum annealers*, Sci. Rep. **10** (2020).

- [2] M. M. Rams, M. Mohseni, D. Eppens, K. Jałowiecki, and B. Gardas, Approximate optimization, sampling, and spin-glass droplet discovery with tensor networks, Phys. Rev. E 104 (2021).

- [3] K. Jałowiecki, M. M. Rams, and B. Gardas, *Brute-forcing spin-glass problems with CUDA*, Comput. Phys. Commun. **260**, 107728 (2021).

- [4] K. Domino, M. Koniorczyk, K. Krawiec, K. Jałowiecki, S. Deffner, and B. Gardas, Quantum annealing in the NISQ era: railway conflict management, Entropy 25 (2023).

- [5] K. Jałowiecki and Ł. Pawela, Omnisolver: An extensible interface to Ising spin-glass and QUBO solvers, SoftwareX 24, 101559 (2023).

#### Other publications

[6] K. Jałowiecki, P. Lewandowska, and Ł. Pawela, PyQBench: A Python library for benchmarking gate-based quantum computers, SoftwareX 24, 101558 (2023).

## Abstract

In this thesis, we focus on the problem of validating and benchmarking quantum annealers in a practical context. To this end, we propose two algorithms for solving real-world problems and test how well they perform on the current generation of quantum annealers. The first algorithm allows for solving the dynamics of quantum systems (or, in fact, any dynamical systems). The second of the proposed algorithms is suitable for solving a particular family of railway dispatching problems: the delay and conflict management on single-track railway lines. We assess the performance of those algorithms on the current generation of D-Wave quantum annealers with the assistance of two novel, classical strategies for solving an Ising model also presented in the thesis. The first, tensor network-based approach is a heuristic algorithm specifically tailored for solving instances defined on Chimera-like graphs, thus making it ideal for providing a baseline with which the results from physical annealers can be compared. The other presented approach is a massively parallel implementation of the exhaustive search through the whole solution space, also known as the brute-force approach. Although the brute-force approach is limited to moderate instance sizes, it has the advantage of being able to compute the low energy spectrum and certify the solutions. Thus, it can be used to obtain additional insight into the solution space structure. The results obtained in our experiments suggest that already present-day quantum annealers are capable of solving a subset of the aforementioned optimization problems. In particular, we show that the D-Wave annealers are capable of capturing the dynamics of a simple two-level quantum system in a specific regime of parameters, and can be used to obtain good-quality solutions for instances of railway conflict management problems. Finally, our findings make it clear that the current viii ABSTRACT

generation of the D-Wave annealers is far from perfect. We discuss problem instances for which the annealers failed to find a good or even feasible solution. We also provide, where possible, a plausible explanation of why some of the presented problems might be hard for the annealers.

### Streszczenie

W niniejszej pracy skupiamy się na problemie walidowania i benchmarkowania wyżaraczy kwantowych w praktycznym kontekście. W tym celu, przedstawiamy dwa algorytmy służące do rozwiązywania rzeczywistych problemów, oraz sprawdzamy, jak dobrze sprawdzają się na obecnej generacji wyżaraczy kwantowych. Pierwszy z algorytmów pozwala na rozwiązywanie dynamiki kwantowych układów (lub, w gruncie rzeczy, dowolnych układów dynamicznych). Drugi z przedstawianych algorytmów może z kolei zostać użyty do rozwiązywania pewnego podzbioru kolejowych problemów dyspozytorski: zarzadania opóźnieniami i konfliktami w sieciach kolejowych o jednej linii. Oceny działania obu w.w. algorytmów na bieżącej generacji wyżaraczy D-Wave dokonujemy z pomoca dwóch, nowatorskich, klasycznych strategii rozwiazywania szkieł spinowych Isinga, które również prezentujemy w niniejszej rozprawie. Pierwszym z nich jest opierający się na sieciach tensorowych heurystyczny algorytm stworzony specjalnie do rozwiązywania szkieł spinowych zdefiniowanych na grafach przypominających topologie Chimera, co sprawia, że idealnie nadaje sie do wyznaczania referencyjnych rozwiazań, do których można porównać wyniki z fizycznych wyżarzaczy. Drugim z prezentowanych podejść jest masywnie równoległa implementacja wyczerpującego przeszukiwania całej przestrzeni rozwiązań, tzw. brute-force. Mimo, że użycie algorytmu bruteforce jest ograniczone do instancji o niewielkich rozmiarach, posiada on te zaletę, że może wyznaczać niskoenergetyczne spektrum, oraz certyfikować rozwiązania. W związku z tym, algorytm przeszukiwania wyczerpującego może slużyć do uzyskania dodatkowego wgladu w strukture przestrzeni rozwiazań. Wyniki otrzymane w naszych eksperymentach sugerują, że już współczesne wyżarzacze są w stanie uchwycić dynamikę prostych, dwupoziomowych układów x STRESZCZENIE

kwantowych w specyficznym reżimie parametrów, oraz mogą znaleźć dobrej jakości rozwiązania instancji kolejowych problemów dyspozytorskich. Wreszcie, nasze eksperymenty pokazują jasno, że obecna generacja wyżaraczy D-Wave nie jest idealna. Wymieniamy instancje problemów, dla których wyżarzanie nie potrafily znaleźść wysokojakościowych, lub nawet dopuszczalnych rozwiązań. Tam gdzie to możliwe, omawiamy również możliwe wyjaśnienie dlaczego niektóre z prezentowanych instancji mogą być dla wyżaraczy wymagające.

## Chapter 1

## Introduction

The previous century has witnessed what is now called the digital revolution. The introduction of digital computers dramatically altered multiple aspects of our lives. In particular, almost every area of science benefitted hugely from the increasingly available computational power [7]. Physics was no exception, and numerical simulations now commonly assist experiments.

Simulating quantum systems – a holy grail of modern computational physics – is a highly challenging task for classical computers [8]. The difficulties can be blamed on the enormous number of possible configurations of such systems. Direct, naive simulations would require solving systems of differential equations with the number of variables exponential in the number of particles. But what about using more sophisticated algorithms? Surprisingly, it is commonly believed that a sufficiently efficient classical algorithm for simulating quantum systems does not exist [8, 9]. Matters seem even worse when one considers that the increase in the classical devices' computational power cannot accelerate infinitely. Moore's law [10], which so far well predicted this growth, is expected to slow down in the years to come [11, 12].

If classical computers cannot simulate quantum physics efficiently, what device can? In the 1980s, Richard Feynman and Paul Benioff put forward the idea that quantum devices can be used to carry simulations of quantum systems [8, 13]. This idea led to the development of several quantum computation models. In 1985 David Deutsch described a universal, gate-based quantum computer [14], a device capable of simulating any other quantum computer with at most

polynomial slowdown. The 1990s and the early 2000s saw the emergence of another model of quantum computation, Adiabatic Quantum Computing (AQC) [15, 16]. Interestingly, AQC was later proven to be equivalent to the standard gate-based model [17].

Just like a classical computer, a quantum computer needs software to run, and software is based on algorithms, describing how the computation should be performed. It is not a surprise that quantum computers operate in a very different way than classical ones, and require different, specialized algorithms. What is surprising is that several notable quantum algorithms were developed even before the first quantum computers were constructed. In 1994 Peter Shor published his, now famous, algorithm for integer factorization [18]. Shor's algorithm demonstrated that quantum computers are (in principle) capable of solving problems intractable by the classical ones [19]. It was also shown that quantum computers could offer a significant performance boost for easier problems. For instance, in 1996 Grover presented a quantum algorithm for unstructured database search [20], offering a quadratic speed-up over classical algorithms solving the same problem.

The invention of specialized quantum algorithms further fuelled interest in the field. In recent years, we observed the development of hardware that brings us closer to the quantum revolution. Several implementations of gate—based quantum computers [21, 22] and quantum annealers [23, 24] were constructed and made publicly available. This allowed scientists to benchmark them and further research their possible applications.

However promising, current quantum computers are far from perfect [25, 26]. Can those noisy devices already be used to solve some real-world problems? And how does one approach validating if this is the case? In this thesis, we try to answer these questions, focusing solely on a specific type of quantum computer – namely, the D-Wave quantum annealers.

#### Layout of the thesis

We begin the thesis with an introduction to Ising and QUBO models (collectively known as Binary Quadratic Models) in Chapter 2. This chapter's purpose is to lay the necessary foundations for understanding optimization problems that can be, at least in principle, solved using quantum annealers.

In Chapter 3 we introduce technologies and devices used for conducting research presented in this thesis. Quite naturally, the first of those devices are quantum annealers. We briefly describe the principle of operation of these devices and then move on to discuss currently available models. We also describe NVIDIA CUDA, another technology that we used for implementing the brute-force algorithm presented in Chapter 6.

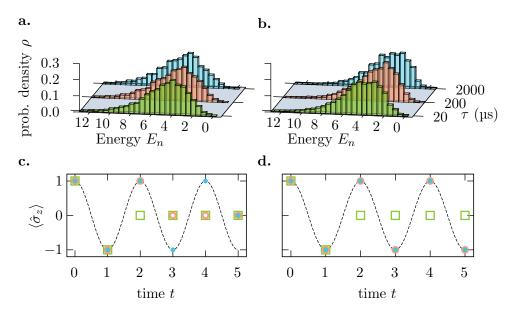

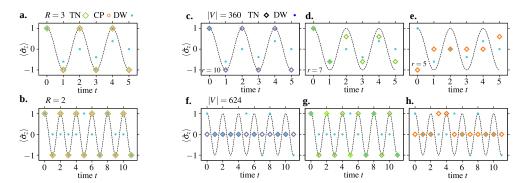

It is widely believed that a noiseless universal quantum computer would be capable of simulating quantum systems. But what about the near-term quantum devices? In Chapter 4 we explore the idea of simulating the evolution of dynamical (not necessarily quantum) systems using quantum annealers. We describe how to represent the task of simulating the dynamics as a static optimization problem and then present experimental results obtained from the D-Wave annealer. We find out that for small systems, the annealer is able to faithfully capture the dynamics. We also discuss possible sources of errors for the problem instances that the annealers failed to solve. While our algorithm is only a proof of concept, it exemplifies possible directions of future research.

A key component in assessing the performance of current quantum annealers is comparing them to the classical algorithms solving the same problems. While there exists a plethora of general heuristic methods for finding a ground state of Ising spin-glass, one can ask if it is possible to construct a better algorithm tailored for problems defined on the same graph as the physical device. In Chapter 5, we present a recent, heuristic algorithm for finding the low-energy spectrum of an Ising spin-glass based on tensor networks, specifically suited for problems defined on Chimera-like graphs.

Chapter 6 describes a fast, parallel approach to exhaustively searching for a low-energy spectrum of Ising spin-glass problems. Our method is suitable for solving small (less than 54 spins), but otherwise arbitrary instances. The presented approach can be used for benchmarking other algorithms that cannot certify their solution. Moreover, the possibility of finding a low-energy spectrum (instead of a single solution) is extremely useful for analyzing the structure of the energy landscape of the problem. We exemplify the usage of our algorithm by conducting benchmarks of a recent MPS-based algorithm on a set of random spin-glass problems. Compared to the original algorithm presented in [3], the algorithm described in Chapter 6 contains several new,

non-trivial optimizations further increasing the problem sizes that it can tackle. To the best of our knowledge, those optimizations make our implementation the fastest brute-force solver for Ising problems available on the market.

Lastly, in Chapter 7, we present the application of quantum annealing to solving certain railway dispatching problems. We discuss how such problems can be converted to QUBO problems suitable for running on the annealer. We then report the performance of the current generation of quantum annealers on a set of dispatching problems constructed for real Polish railway networks. Presented benchmarks extend results presented in [4] to the newer generation of quantum annealers. Compared to [4], we also include a more detailed discussion on the influence of penalty terms on the quality of results.

## Chapter 2

## Ising model and QUBO problem

Quantum annealers are fundamentally different from classical computers. For one, they don't execute programs written as a sequence of instructions in their memory. Instead, they are single-purpose devices capable (in principle) of solving a specific optimization problem. Namely, annealers are designed to find the lowest energy configuration (called *ground state*) of instances of the Ising spin–glass model, which we introduce in this chapter.

The potential usefulness of quantum annealers stems from the fact that the optimization problem they are supposed to solve is hard for classical computers. But what does it formally mean for a problem to be hard? To answer this question, we will need a brief recap of complexity theory, which is a second point of this chapter.

Finding a ground state of the Ising spin–glass model may be hard for classical computers, but there exists a plethora of heuristic, classical algorithms capable of finding solutions that are at least "good enough". As the next point in this chapter, we provide a brief overview of the most popular classical algorithms for solving the Ising spin-glass problems. These algorithms will serve as a baseline for comparison with quantum annealing and a recent tensor network-based approach discussed later in the thesis.

As the last point in the chapter, we define the Quadratic Unconstrained Binary Optimization (QUBO) problem, which is equivalent to the problem of finding the ground state of the Ising model. We will use the QUBO formulation on several occasions in the thesis, as it oftentimes results in a more natural phrasing of the problem, or leads to a surprising performance improvement when implementing software solvers.

#### 2.1 Ising model

The Ising spin–glass model was introduced in 1920 by Wilhelm Lenz [27] as a description of ferromagnetism in solids but is named after his student Ernst Ising, who studied and solved it in the one-dimensional case [28]. For purposes of this thesis, however, we will forget about the physical interpretation of the model, treating it merely as a description of a particular optimization problem.

Consider a simple<sup>1</sup>, undirected graph G = (V, E) with N nodes labeled by consecutive natural numbers. With each node  $i \in V$  we associate a spin variable  $s_i \in \{-1, 1\}$ . To each edge  $\{i, j\} \in E$  we assign an interaction strength  $J_{ij}$  and to each node  $i \in V$  we assign a local magnetic field  $h_i$ . Here, all  $J_{ij}$  and  $h_i$  are real numbers. For such a system, one can define the following energy function (Hamiltonian):

$$H(\mathbf{s}) = \sum_{\langle i,j \rangle} J_{ij} s_i s_j + \sum_{i=1}^{N} h_i s_i, \tag{2.1}$$

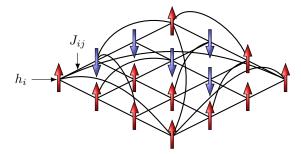

where  $\mathbf{s} = (s_i, \dots, s_N)$  and the first sum runs over all edges exactly once<sup>2</sup>. In this thesis, we will call the instances of the Ising model *Ising spin-glasses*. An illustrative representation of a spin-glass is depicted in Fig. 2.1.

For fixed model coefficients, one is typically interested in finding its *ground* state, a configuration s that minimizes H. More generally, it might be desirable to search for  $k \ll 2^N$  configurations with the lowest energy, a so-called *low-energy spectrum of size* k.

<sup>&</sup>lt;sup>1</sup>That is, one that does not contain duplicate edges or loops.

<sup>&</sup>lt;sup>2</sup>In the literature, the Ising Hamiltonian (2.1) is often negated. However, the definition provided here is consistent with the one used by D-Wave, and thus more suitable for use in this thesis.

Figure 2.1: Symbolic representation of Ising spin–glass defined on the graph with N=16 nodes. Here,  $h_i$  is a real number associated with *i*-th node, and  $J_{ij}$  denotes coupling strength associated with an edge between *i*-th and *j*-th node. The configuration of each spin is marked by a red arrow pointing upwards (+1) or a blue arrow pointing downwards (-1).

**Example 2.1.** Consider an Ising model instance with 3 spins given by the Hamiltonian H:

$$H(s_1, s_2, s_3) = s_1 - s_2 + 2s_3 - 2s_2s_3 + 3s_1s_2$$

(2.2)

This instance has 8 possible states:

| $\mathbf{s} = (s_1, s_2, s_3)$ | $H(\mathbf{s})$ | $\mathbf{s} = (s_1, s_2, s_3)$ | $H(\mathbf{s})$ |

|--------------------------------|-----------------|--------------------------------|-----------------|

| (-1, -1, -1)                   | -1              | (1, -1, -1)                    | -5              |

| (-1, -1, 1)                    | 7               | (1, -1, 1)                     | 3               |

| (-1, 1, -1)                    | -5              | (1, 1, -1)                     | 3               |

| (-1, 1, 1)                     | -5              | (1, 1, 1)                      | 3               |

Table 2.1: All possible configurations for the Ising Hamiltonian in the equation (2.2).

Observe that the lowest attainable energy is -5 and there are 3 states with exactly this energy. Hence, all the configurations (-1,1,-1), (-1,1,1), (1,-1,-1) are ground states. This situation, i.e. when two or more states share the same energy, is called *degeneracy* and the states in question are called *degenerate*. For this instance, a low energy spectrum of size k=5 comprises all ground states, the (-1,-1,-1) state with H(-1,-1,-1)=-1 and any of the states with  $H(\mathbf{s})=3$ .

Despite the simple formulation, the problem of finding a ground state of Ising spin–glass is computationally hard [29]. Before expanding on this idea, let us first introduce the hierarchy of complexity classes.

#### 2.2 Algorithms and complexity

Solving the computational problem requires a suitable algorithm, a description of steps to be performed by a computer to obtain a solution. It is hardly surprising that some problems might be solved in more than one way, i.e. there might exist different algorithms performing essentially the same task. Different algorithms solving the same problems might vastly differ in their demand on various resources, like memory or time needed to execute them. In practice, the execution time (and usage of other resources) of a given algorithm might also vary between its implementations, depending on factors like programming language or libraries used and the hardware it is executed on. Moreover, measuring execution time can only tell us how the given implementation performs on a specific problem. But if we increase the problem size tenfold, will the execution time be 10 times slower? Or maybe 100 times slower? Or maybe it will remain unchanged? Clearly, measuring execution times is useful, but cannot be used for comparing algorithms (instead of their implementations). Instead, it is more informative to characterize algorithms based on how their execution time scales asymptotically with increasing problem size [30]. For instance, given an algorithm with execution time roughly proportional to the input size N, one might suspect that for problem instances large enough, it will perform better than the one with execution time proportional to  $N^2$ . This characteristic, known as computational complexity<sup>3</sup>, can be formalized by a big-O notation (see appendix for a more detailed description). Using this notation, the algorithms from the above example would be classified as O(N)and  $O(N^2)$  respectively.

$<sup>^3</sup>$ Note that here we focus only on  $time\ complexity$ , but other notions like memory complexity can be defined similarly

#### 2.3 Complexity classes

Although there might exist more than one algorithm for solving a particular problem, one might consider the smallest time complexity needed to do so. Consequently, one might group computational problems based on their demand on resources. In this view, sets of similar problems are called *complexity classes* [30]. The definition of some complexity classes might also be restricted to specific types of problems. For instance, one might consider only decision problems, i.e. problems to which the answer is yes or no [30]. Finally, to define any complexity class one has to assume some model of computation. In many cases, this model is assumed to be a Turing Machine [30], a theoretical device manipulating symbols on a tape using some table of rules, or its non-deterministic variant.

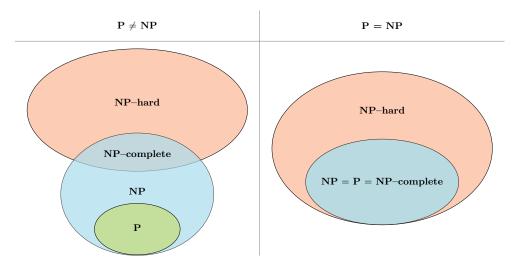

One of the fundamental complexity classes is  $\mathbf{P}$ , a class of decision problems solvable in polynomial time on a deterministic Turing Machine [30]. Another class,  $\mathbf{NP}$ , comprises all decision problems whose solution can be verified in polynomial time using a deterministic Turing Machine [30]. Immediately, one can see that  $\mathbf{P} \subset \mathbf{NP}$ . Indeed, if a problem is solvable in polynomial time, then it is also trivially verifiable in polynomial time. However, it is not immediately obvious if the inclusion is strict, and the question of whether  $\mathbf{P} \neq \mathbf{NP}$  is one of the most important, yet unsolved problems in theoretical computer science [31]. The class of  $\mathbf{NP}$ —hard problems comprises all the problems that are at least as hard as every problem in  $\mathbf{NP}$ . More formally, a decision problem S is  $\mathbf{NP}$ —hard if and only if solving every problem in  $\mathbf{NP}$  can be reduced to solving S a polynomial number of times [30]. A particular subclass of  $\mathbf{NP}$ —hard problems,  $\mathbf{NP}$ —complete, is an intersection of  $\mathbf{NP}$  and  $\mathbf{NP}$ —hard [30]. Figure 2.2 shows the relationship between the discussed complexity classes, both under assumptions  $\mathbf{P} = \mathbf{NP}$  and  $\mathbf{P} \neq \mathbf{NP}$ .

Problems in the complexity class  $\mathbf{P}$  are often considered tractable, or efficiently solvable, whereas problems not in  $\mathbf{P}$  are perceived as hard and computationally demanding, a statement known as the Cobham's thesis [30, 32]. At first, one might find it strange and unintuitive - a decision problem for which the best-known algorithm runs in  $O(N^{10^5})$  time is definitely in  $\mathbf{P}$ , but can hardly be called efficiently solvable. However, such large polynomial complexities are rarely encountered in practice. Furthermore, even in such cases, it is

Figure 2.2: Hierarchy of basic complexity classes. Under the assumption of  $P \neq NP$  (left), the hierarchy is richer and there exist problems in NP that are not NP-complete. Under the opposite assumption (right), the hierarchy collapses. Notice that in both cases there exist NP-hard problems that are not in NP

not uncommon that a better algorithm is found shortly after the original one is discovered [30].

#### 2.4 Ising model and complexity

Thus far, we only discussed classes of decision problems. How do they relate to the problem of finding a ground state of the Ising model? Suppose we are given an Ising model instance with hamiltonian H and let  $x \in \mathbb{R}$  be some fixed number. Consider the problem of deciding whether there exists  $\mathbf{s}$  such that  $H(\mathbf{s}) < x$ . We will call this problem a decision version of the Ising problem.

If we can minimize H, we can also solve the decision problem by simply finding a ground state and checking if its energy exceeds threshold x. On the other hand, the sole capability of solving the decision version of a problem does not give us an algorithm for solving an original optimization problem. Therefore, one can see that the optimization problem is at least as hard as the corresponding decision problem. Of course, the same reasoning applies for other optimization problems. Hence, if the decision version of an optimization problem is  $\mathbf{NP}$ —hard, the optimization problem is sometimes also called  $\mathbf{NP}$ —

hard, even if it slightly abuses the terminology. For simplifying the vocabulary, in what follows we will use this slightly imprecise but more concise convention.

It was shown that finding a ground state of the Ising spin-glass in the case of three-dimensional lattices, as well as for some planar graphs, is **NP-hard** [29]. The decision version of the problem is **NP-complete**. Multiple known **NP-hard** problems, such as Travelling Salesman Problem, Hamiltonian Cycles Problem or Set Cover Problem are reducible to finding the ground state of Ising spin-glass [33].

As a side note, one might be tempted to think that the **NP-hard**ness of finding Ising model's ground state is trivial, because its enormous state space comprises  $2^N$  states. However, it is important to remember that the size of the solution space itself is not enough to reason about the problem's hardness. For instance, the number of possible spanning trees in the complete graph of N vertices is  $N^{(N-2)}$ , yet the minimum spanning tree problem is solvable in polynomial time via several algorithms [34].

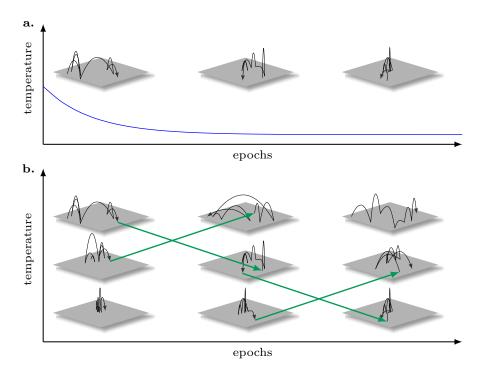

#### 2.5 Algorithms for solving Ising model

As is the case with many NP-hard optimization problems, there are many heuristic approaches for solving the Ising model. One family of such algorithms relies on the Metropolis-Hastings [35] algorithm for sampling configurations from the underlying Boltzmann distribution. In simulated annealing [36, 37], one samples states from the system while lowering the temperature over time. Thus, the chance of accepting a locally worse solution is greater at the start of the algorithm, which helps avoid getting stuck in a local minimum, and decreases with each iteration. In another approach from the same family, parallel tempering, one simulates several replicas of the system, each of them in a different temperature. Neighboring replicas are allowed to exchange states, with exchange probability depending on their energy and temperature difference [38]. Replicas with higher temperatures explore state space rapidly (thus reseeding the algorithm), while ones with lower temperatures refine the best solutions found so far. Various modifications of the aforementioned algorithms exist. For instance, one could employ isoenergetic cluster moves [39] or adaptive choosing of the number of sweeps performed between replica exchanges [40]. Population annealing is yet another Monte Carlo method, sharing similarities with simulated annealing and parallel tempering [41]. Other approaches for solving Ising spin–glasses include methods involving branch–and–bound framework [42], its chordal extensions [43] or methods based on simulating dynamical systems [44].

Figure 2.3: a. Schematic representation of the simulated annealing algorithm. b. Schematic representation of the Parallel tempering algorithms. In simulated annealing, a single copy of the system is simulated. The temperature of the system is decreased with each epoch, thus reducing movement through the state space. In parallel tempering, several copies (replicas) of the system are simulated, each with a fixed temperature. Hotter replicas move through the state space rapidly and less predictably, while colder replicas move conservatively. Between epochs, replicas can exchange states, which helps avoid being stuck at local minima. Exchanging replicas can also be viewed as reseeding of the colder replicas by randomized solutions provided by hotter replicas.

#### 2.6 Quadratic Unconstrained Binary Optimization

Let us now shift our attention to QUBO – the Quadratic Unconstrained Binary Optimization problem. QUBO is essentially the same as the problem of finding the ground state of Ising spin–glass, except that in QUBO one uses binary variables  $q_i \in \{0,1\}$  instead of  $\pm 1$  spin variables. To distinguish between the two problems, we will use symbols  $a_{ij}$  and  $b_i$  to denote respectively quadratic and linear coefficients in QUBO, so the energy function to be minimized can be written as:

$$F(q_1, \dots, q_N) = \sum_{\langle i, j \rangle} a_{ij} q_i q_j + \sum_{i=1}^N b_i q_i,$$

(2.3)

where, as in the Ising model, the first sum runs through all the edges of the graph on which the problem is defined.

The QUBO and Ising formulations are essentially equivalent. Indeed, it is always possible to transform the Ising Hamiltonian (2.1) into the QUBO cost function by a linear substitution of variables  $s_i \mapsto 2q_i - 1$ . Then, one obtains function F like in the equation (2.3), with the following values for  $a_{ij}$  and  $b_i$ :

$$a_{ij} = 4J_{ij}, \quad b_i = 2h_i - 2\sum_{\langle i,j\rangle} J_{ij},$$

(2.4)

where the last sum runs over all neighbors of node i. The obtained function F differs from the original H by the constant offset:

$$F(\mathbf{q}) - H(\mathbf{s}) = \sum_{i=1}^{N} h_i - \sum_{\langle i,j \rangle} J_{ij}, \qquad (2.5)$$

which is irrelevant to the optimization process.

**Example 2.2.** Let us go back to the previous example and convert the Ising Hamiltonian from the equation (2.2) to an equivalent QUBO. We compute the coefficients using formulas from the equation (2.4) to obtain:

$$b_1 = 2h_1 - 2J_{12} = -4 a_{12} = 4J_{12} = 12$$

$$b_2 = 2h_2 - 2(J_{12} + J_{23}) = -4 a_{23} = 4J_{23} = -8 (2.6)$$

$$b_3 = 2h_3 - 2J_{23} = 8.$$

This gives the following energy function:

$$F(q_1, q_2, q_3) = -4q_1 - 4q_2 + 8q_3 + 12q_1q_2 - 8q_2q_3.$$

(2.7)

The possible system configurations and their energies are listed in the table 2.7 below. Observe that the difference between QUBO and Ising energies for corresponding configurations is always 1, which is exactly what we get if we computed the offset explicitly:

offset =

$$h_1 + h_2 + h_3 - J_{12} - J_{23} = 1$$

. (2.8)

| $\mathbf{q} = (q_1, q_2, q_3)$ | $F(\mathbf{q})$ | $\mathbf{q} = (q_1, q_2, q_3)$ | $F(\mathbf{q})$ |

|--------------------------------|-----------------|--------------------------------|-----------------|

| (0, 0, 0)                      | 0               | (1, 0, 0)                      | -4              |

| (0, 0, 1)                      | 8               | (1, 0, 1)                      | 4               |

| (0, 1, 0)                      | -4              | (1, 1, 0)                      | 4               |

| (0, 1, 1)                      | -4              | (1, 1, 1)                      | 4               |

Table 2.2: All configurations for example QUBO from the equation (2.7).

We will conclude this chapter by discussing alternative notation for QUBO problems when the problem is defined on a complete graph. In such a case, the first sum in the equation (2.3) runs through all the possible pairs i, j, and thus F can be written as:

$$F(q_1, \dots, q_N) = \sum_{i=1}^{N} \sum_{j=i+1}^{N} a_{ij} q_i q_j + \sum_{i=1}^{N} b_i q_i,$$

(2.9)

One can now define a  $n \times n$  real symmetric matrix Q with coefficients:

$$Q_{ij} = \begin{cases} b_i & i = j \\ a_{ij} & i < j \\ a_{ji} & j < i \end{cases}$$

$$(2.10)$$

Having in mind that squaring a binary variable does not change its value, we can again rewrite F as:

$$F(q_i, \dots, q_N) = \sum_{i < j} Q_{ij} q_i q_j = \sum_{j < i} Q_{ij} q_i q_j.$$

(2.11)

Moreover, since it is always possible to view any given QUBO as a one defined on a complete graph (by introducing artificial edges with weights 0), the equation (2.11) provides a one–to–one correspondence between real symmetric matrices and QUBO problems. We will see the benefits of this correspondence when discussing the brute-force algorithm in Chapter 6.

## Chapter 3

# Quantum annealing and GPU computing

After introducing the Ising model, our next task is to present the technologies used in the research conducted for this thesis. Since the main point of this thesis is benchmarking quantum annealers, it is only natural that we start by introducing the reader to the concepts of adiabatic quantum computations and quantum annealing. The second part of the chapter is devoted to Nvidia CUDA, a technology allowing massively parallel computations on general-purpose graphics processing units (GPUs).

## 3.1 Adiabatic quantum computation and quantum annealing

#### Adiabatic Quantum Computation

One of the possible models of quantum computing is Adiabatic Quantum Computation (AQC) [16]. AQC ties closely with quantum annealing, and hence we will shortly discuss how it works in general. Before we describe how the computations are performed in this model, we will take a closer look at the underlying adiabatic theorem, which can be stated as follows [16, 45]:

**Theorem 1** (Adiabatic theorem). Suppose we are give a time-dependent Hamiltonian  $\tilde{H}(t)$  with eigenenergies  $E_1(t) \leq E_2(t) \leq \ldots \leq E_i(t) \leq \ldots$  and

corresponding eigenstates  $|\psi_i(t)\rangle$ . Further, suppose we are given a physical system  $\mathcal{S}$  evolving according to  $H(t) = \tilde{H}(t/T)$  and let  $|\psi(t)\rangle$  denote the state of  $\mathcal{S}$  at time t. If  $|\psi(0)\rangle = |\psi_n(0)\rangle$ , then also  $|\psi(t)\rangle = |\psi_n(t)\rangle$  for all time t, provided that T is large enough and for all t there exists a non-zero difference between  $E_n(t)$  and the rest of the H(t)'s spectrum.

One conclusion to the adiabatic theorem is of particular importance to quantum computation. If the system is prepared in a ground state, has a non-zero gap between its ground energy and the energy of the first excited state, and is evolved slowly enough, it will stay in the ground state during the whole evolution. Knowing this we can finally discuss how AQC works. First, an optimization problem to be solved is encoded as a ground state of some Hamiltonian  $\mathcal{H}_{\text{target}}$ . Then, a physical system is prepared in a ground state of some simpler Hamiltonian,  $\mathcal{H}_{\text{initial}}$ . After that, the system is driven slowly from  $\mathcal{H}_{\text{initial}}$  to  $\mathcal{H}_{\text{target}}$ . By adiabatic theorem, the system ends up in a ground state of  $\mathcal{H}_{\text{target}}$ , and after the measurement is performed the solution to the original problem can be decoded.

In Quantum Annealing (QA), one follows essentially the same procedure as in Adiabatic Quantum Computing. What is different, is that the evolution of the system in QA does not have to be adiabatic [46]. We will describe in more detail how Quantum Annealing works on a concrete example later in this chapter when we discuss D-Wave annealers.

#### D-Wave quantum annealers

The first commercially available quantum annealer was D-Wave One, which was introduced by D-Wave company in 2011 [23], featuring 128 qubits. Since then, multiple improved generations of D-Wave annealers have been released. At the time of writing, the newest series of D-Wave annealers is called the Advantage system. Devices in this series utilize a chip with at least 5000 qubits. Table 3.1 summarizes the release history of D-Wave annealers and highlights the differences between their generations.

As already mentioned in the introduction, D-Wave annealers are built to find the ground states of the classical Ising spin–glasses. In these devices, the spin variables correspond to physical two-level systems, called qubits, which are implemented using Josephson junctions [47, 48]. At the end of the annealing

process, the (quantum) Hamiltonian of the annealer has to correspond to the classical Ising Hamiltonian of the spin-glass instance being solved, i.e.:

$$\mathcal{H}_{\text{target}} = \sum_{i=1}^{N} h_i \hat{\sigma}_z^{(i)} + \sum_{\langle i,j \rangle} J_{ij} \hat{\sigma}_z^{(i)} \hat{\sigma}_z^{(j)},$$

(3.1)

where N, as previously, is the number of spins,  $\hat{\sigma}_x^{(i)}$ ,  $\hat{\sigma}_z^{(i)}$  denote Pauli operators acting on i-th qubit, and  $h_i, J_{ij} \in \mathbb{R}$  are coefficients of the instance. Note that finding the ground state of such Hamiltonian is equivalent to finding the ground state of its classical counterpart (c.f. eq. (2.1)). For small system sizes, this can be accomplished by listing all possible configurations and sorting them with respect to their energies.

More precisely, the time-dependent Hamiltonian implemented by the D-Wave devices is of the form:

$$\mathcal{H}(t) = -\frac{A(t)}{2} \sum_{i=1}^{N} \hat{\sigma}_x^{(i)} + \frac{B(t)}{2} \left( \sum_{i=1}^{N} h_i \hat{\sigma}_z^{(i)} + \sum_{\langle i,j \rangle} J_{ij} \hat{\sigma}_z^{(i)} \hat{\sigma}_z^{(j)} \right). \tag{3.2}$$

where  $t \in [0, \tau]$  [49]. The tunneling energy curve A(t) is monotonically decreasing and it vanishes as t approaches  $\tau$ . Similarly B(t) is monotonically increasing, and the functions satisfy  $A(0) \gg B(0)$  and  $B(\tau) \gg A(\tau)$ . Illustrative plots of the functions A and B are presented in Fig. 3.1.

Since the variables in the spin–glass being solved have to correspond to the physical qubits, it is clear that the number of qubits of the device limits the size of the input problem. However, it is not the only factor restricting problems that can be directly submitted to the annealer. To implement quadratic terms in the Ising hamiltonian, the qubits have to be physically connected via a coupler. The available connectivity on the device depends on two factors. The first one is the topology of the chip, i.e. graph describing its qubits layout. The topology is the same for all devices in the same generation. However, due to manufacturing errors and calibration problems, some qubits and/or couplers might be unavailable to the end user. The graph describing qubits' connectivity of an actual device is called its working graph. Understanding annealer topologies is crucial for understanding how to program these devices. Hence, in the next section, we will describe topologies of all currently available D-Wave annealers

Figure 3.1: A typical shape of the A and B curves defining the annealing protocol on D-Wave annealers. Here,  $\tau$  denotes the annealing time. Actual values of the functions vary between the devices.

| Series       | Release year | Topology | Num. qubits | Num. couplers |

|--------------|--------------|----------|-------------|---------------|

| D-Wave One   | 2011         | $C_4$    | 128         | 352           |

| D-Wave Two   | 2013         | $C_8$    | 512         | 1472          |

| D-Wave 2X    | 2015         | $C_{12}$ | 1152        | 3360          |

| D-Wave 2000Q | 2017         | $C_{16}$ | 2048        | 6016          |

| Advantage    | 2020         | $P_{16}$ | 5640        | 40484         |

| Advantage 2  | 2023-2024    | $Z_{15}$ | 7440        | 71736         |

Table 3.1: Comparison of different generations of D-Wave annealers. For topologies,  $C_n$ ,  $P_n$  and  $Z_n$  refers to Chimera, Pegasus and Zephyr of size n respectively. The numbers of qubits and couplers are given for a perfectly manufactured chip with full yield. Actual devices typically have a lower number of qubits or couplers.

•

#### Annealer topologies

The first topology that we will discuss in this chapter is the *Chimera* topology, used for all generations of D-Wave devices up to D-Wave 2000Q series. We decided to describe the Chimera before moving towards newer topologies because it serves as a building block for its successors.

While discussing the topologies of the D-Wave annealers, we will not discuss the physical structure of the chip. We decided to do so because, for this thesis, the *logical* structure of the chip is far more important than the underlying physical one. However, one consequence of this choice is that the distinction between two types of couplers (external and internal) will become less intuitive once we reach beyond the Chimera topology. Nevertheless, we believe that this will not impair the reader's ability to understand the layout of qubits in the newer devices. For the description of the physical chip layouts, we refer the reader to [49].

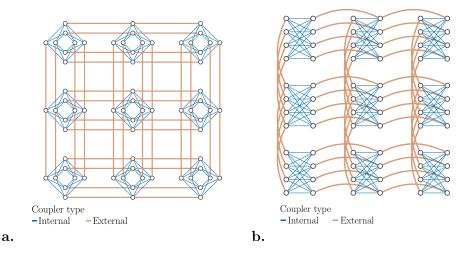

#### The Chimera topology

In Chimera topology, depicted in Fig. 3.2, the qubits are placed on a rectangular grid of unit cells. Every unit cell is a complete bipartite graph  $K_{t,t}$ . Each group in the bipartition is called shore, and hence the parameter t is called the shore size. Each qubit in the unit cell (except the ones in the cells on the border) connects to two qubits on the same shore in the neighboring cells. Hence, the whole Chimera graph is also bipartite, and the maximum degree of a node is t+2. The couplers connecting qubits in the same unit cell are called internal and the couplers connecting qubits belonging to different cells are called external.

Typically, the devices using Chimera topology utilize a square grid with a shore size of 4. Such layouts are denoted by  $C_n$ , where n is the width (and the height) of the grid. In such devices, each qubit is connected to a maximum of 6 qubits, the total number of qubits is  $8n^2$  and the total number of couplers is  $16n^2 + 8(n-1)n$ .

The Chimera topology is often visualized using two distinct layouts, both of which are exemplified in Fig. 3.2. In the cross layout, the shores of the unit cell form a cross, with one shore being placed vertically and the second shore being placed horizontally. In the grid layout, each unit cell is depicted as two

Figure 3.2: Chimera  $C_3$  topology drawn using different layouts. **a.** The cross layout. **b.** The grid layout. The internal couplers are marked with blue, and the external couplers are marked with bold orange.

columns of qubits, corresponding to both shores of the cell. While the grid layout might be more intuitive in some applications, cross layouts are in turn convenient when presenting the Pegasus topology, which we will discuss next.

#### The Pegasus topology

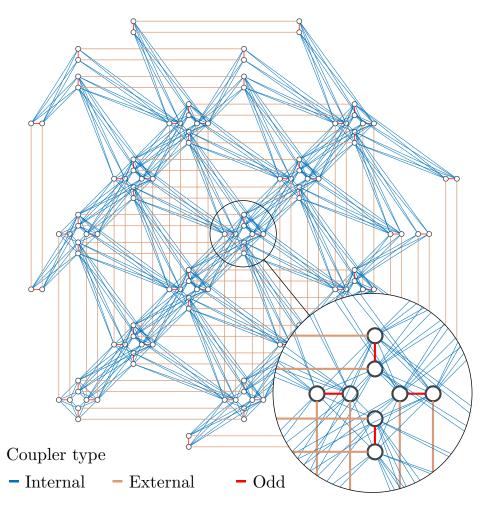

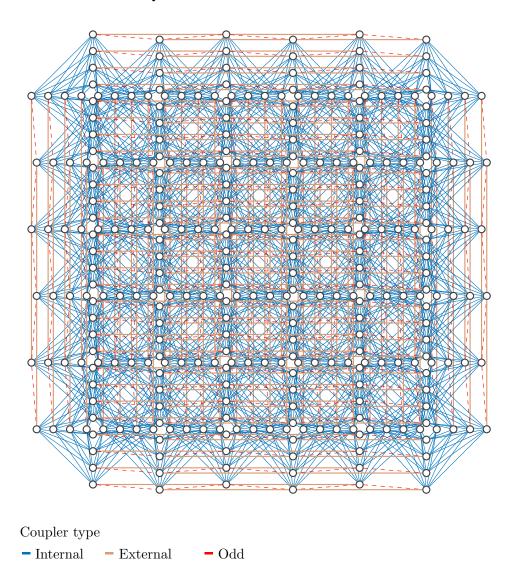

The current generation of D-Wave devices, dubbed the Advantage System, uses a topology called Pegasus [50]. An example of this topology is presented in Fig. 3.3. The unit cell of Pegasus comprises 24 qubits grouped into the 3 Chimera unit cells. The topology features several improvements regarding the qubit connectivity. Firstly, the internal couplers connect not only the qubits in the same Chimera unit cell but also connect some neighboring Chimera unit cells. Secondly, inside the Chimera unit cells new type of connection, called the odd couplers, is introduced. Interestingly, those modifications mean that the Pegasus graph is no longer bipartite. The Pegasus topology having n rows and n columns of unit cells is denoted by  $P_n$  and contains 24n(n-1) qubits.

Observe that a graph in Pegasus topology features subgraphs isomorphic to Chimera graphs. This fact is important for the annealer users, as all problems instances compatible with a device using the Chimera topology are automati-

Figure 3.3: The  $P_3$  graph, an example of the Pegasus topology. The magnified portion of the image shows a part of the graph containing a Chimera unit cell. Observe the odd couplers, marked in red, connecting qubits that are not connected in a unit cell of Chimera topology.

cally compatible with annealers using a sufficiently large Pegasus topology.

### The Zephyr topology

The upcoming generation of D-Wave annealers, called Advantage 2 System, will use the Zephyr topology [51]. This topology utilizes Chimera unit cells with a shore size of 8 and, compared to the Pegasus topology, contains more

Figure 3.4: The  $Z_3$  graph, an example of the Zephyr topology. Different types of couplers are color–coded. Observe that, similarly to Pegasus, the Zephyr topology contains Chimera subgraphs. However, the shore size of the Chimera unit cells in Zephyr is 8 instead of 4.

odd couplers. Overall, the maximum degree of a qubit in Zephyr topology is 20. The Zephyr topology containing n unit cells is denoted  $Z_n$  and contains 16n(2n+1) qubits.

### Minor embeddings

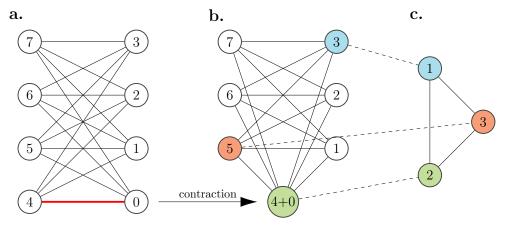

Oftentimes, even small (relatively to the available number of qubits) instances are not compatible with the annealer because of its restricted connectivity. This issue can sometimes be mitigated using a procedure called the *minor embedding*, in which the number of qubits is sacrificed for an improvement in connectivity. Informally, the minor embedding relies on constructing a new *logical* graph with which the Ising instance to be solved is compatible. This, in turn, is achieved by introducing *logical* qubits built from several physical qubits (a process called *contraction*). For the reasons explained later in this section, we will require all qubits forming the logical qubit to be connected in a chain. The logical qubit constructed this way inherits all the neighbors of its physical qubits, and thus one ends up with a more densely connected graph, albeit with a lower number of qubits. Before formalizing this idea, let us first present an example of minor embedding.

**Example 3.1** (Minor embedding). Consider an annealer with  $C_1$  topology and an (arbitrary) Ising spin–glass instance defined on a triangular graph G as depicted in Fig. 3.5. No such instance is compatible with  $C_1$ , because graph G is not bipartite. Combining qubits 0 and 4 into a single logical qubit yields a

Figure 3.5: Example of minor embedding. Spin-glasses defined on the graph G (c.) cannot be directly solved on an annealer with  $C_1$  topology (a.). By contracting neighboring vertices 4 and 0 one obtains a new logical graph  $C'_1$  (b.), which contains problem graph G as a subgraph.

graph depicted in Fig. 3.5b., with which G is compatible. If one could use an annealer with this logical graph, then instances defined on G could be solved directly. Note that vertices 0 and 4 are not the only choice in this case. Indeed, every contraction of two vertices in  $C_1$  would be sufficient to embed G.

As demonstrated in the example, contracting vertices in the annealer's working graph can make it compatible with an Ising instance otherwise unsolvable by the annealer. It only remains to explain how this new logical graph can be used with the actual device.

The idea is to make all the physical qubits in the chain behave like a single qubit. Since the qubits are connected, one can couple them, including a penalty large enough that violating qubits' alignment would prohibitively increase the energy of the solution. The next example presents this idea.

**Example 3.2** (Minor embedding, continued). Consider an Ising spin–glass instance with Hamiltonian:

$$H(s_1, s_2, s_3) = s_1 + s_2 + s_3 - s_1 s_2 - s_2 s_3$$

(3.3)

with an unique optimal solution  $\mathbf{s} = (-1, -1, -1)$ . Suppose we want to solve it on annealer with  $C_1$  topology, using the minor embedding presented in Example 3.1. The problem submitted to the annealer will have the following Hamiltonian:

$$H'(z_0, z_3, z_4, z_5) = \underbrace{z_3 + z_5}_{s_1 + s_3} + \underbrace{0.5(z_0 + z_4)}_{s_2} - \underbrace{z_3 z_4}_{s_2 s_1} - \underbrace{z_0 z_5}_{s_2 s_3} + \underbrace{P(z_0, z_4)}_{\text{penalty}}, \quad (3.4)$$

where  $z_i$  is a spin variable associated to *i*-th qubit and  $P(z_0, z_4)$  is a *penalty* term for chain comprising qubits 0 and 4. The penalty is of the form:

$$P(z_0, z_4) = -\alpha z_0 z_4 \tag{3.5}$$

where *alpha* is a positive constant. Let us examine all possible configurations of  $(z_0, z_3, z_4, z_5)$  and observe how the penalty term influences their energy:

If  $\alpha$  is large enough, e.g.  $\alpha = 2$ , all feasible solutions (left part of the table) have energy lower than any solution in which qubits  $z_0$  and  $z_4$  are misaligned (right part of the table), which increases a chance of sampling them on a physical device. On the other hand, if  $\alpha = 1$ , the feasible solution (1, 1, 1, 1) has higher energy than the infeasible solution (1, -1, -1, -1).

| feasible solutions   |                | infeasible solutions |                 |  |

|----------------------|----------------|----------------------|-----------------|--|

| $z_0, z_3, z_4, z_5$ | energy         | $z_0, z_3, z_4, z_5$ | energy          |  |

| -1, -1,-1, -1        | $-5.0-\alpha$  | 1, 1,1, -1           | $1.0 + \alpha$  |  |

| -1, 1,1, -1          | $-2.0-\alpha$  | 1, -1,1, -1          | $1.0 + \alpha$  |  |

| -1, -1,1, -1         | $-2.0-\alpha$  | -1, -1,-1, 1         | $-1.0 + \alpha$ |  |

| 1, 1,-1, 1           | $2.0-\alpha$   | 1, 1,-1, -1          | $2.0 + \alpha$  |  |

| 1, -1,-1, 1          | $-2.0-\alpha$  | 1, -1,-1, -1         | $-2.0 + \alpha$ |  |

| -1, 1,-1, -1         | $-1.0-\alpha$  | -1, -1,1, 1          | $2.0 + \alpha$  |  |

| 1, -1,1, 1           | $1.0 - \alpha$ | -1, 1,1, 1           | $2.0 + \alpha$  |  |

| 1, 1,1, 1            | $1.0 - \alpha$ | -1, 1,-1, 1          | $3.0 + \alpha$  |  |

Table 3.2: All possible configurations for the instance from the equation (3.4).

As demonstrated in the example above, when performing minor embedding it is important to correctly choose the chain strengths. Typically, it is not possible to choose a correct  $\alpha$  with certainty. In practice, one typically tries different chain strengths and tests how well they perform for the given problem.

Since the annealers are inherently heuristic devices, even with carefully chosen chain strength one might obtain solutions that cannot be decoded into feasible solutions to the original problem because the qubits forming chains are misaligned. This situation is known as a *chain break*, and there are two most commonly used strategies for dealing with it:

- discarding the incorrect samples. This is the simplest method, but it reduces the total number of samples. Hence, the experiments needing some fixed number of samples have to adapt and e.g. sample from the annealer multiple times until the desired number of feasible samples is collected.

- majority voting: whenever the chain of qubits is misaligned, choose the most common value among the chain and use it as a value of the logical qubit. In case of a tie, choose -1 or 1 with equal probability.

Having presented all the necessary information about quantum annealers, we can conclude this section with a discussion on how quantum annealing differs from the classical model of computation.

### Comparison to the classical model of computation

It is clear that quantum annealing is different from classical computations. One of the most obvious differences is the computational model. On classical computers, one essentially writes programs as a series of instructions to be executed by the CPU. On typical machines, the CPU is capable of performing arithmetic operations, computing values of some special functions, managing execution flow, controlling I/O and much more. In comparison, chips in quantum annealers are capable of executing a single operation: annealing a given optimization problem. Therefore, programming these devices boils down to defining an optimization problem and tuning the annealing parameters.

Another difference between classical computers and quantum annealers is the lack of working memory in the former. Classical computers use working memory (typically in the form of RAM) to store machine code and data. However, quantum annealers do not need to store neither code nor data, and hence they do not feature an analogous component. Similarly, quantum annealers, being purely computationally oriented devices, do not have mass storage.

A slightly less obvious difference between classical computers and quantum annealers is their model of parallelism. Classical computers are capable of running several threads of execution at the same time. However, every non-trivial classical algorithm involving parallelism must necessarily also include a serial part which limits speedup gained for introducing more execution units (CPU cores or CPUs). In contrast, quantum annealers are capable of annealing multiple qubits at the same time, making their operation inherently parallel.

### 3.2 Nvidia CUDA

Quantum annealing, introduced in the previous section, is a heuristic process. Like many heuristic algorithms, it cannot certify that the solution it found is optimal. One way to assess the performance of such algorithms is to compare their results with known low-energy spectra of some test instances. Another viable approach is to compute the exact low energy spectra of some test instances, which in turn requires an exact solver. In particular, one might perform an exhaustive search over all possible states and extract only the selected number of the ones with the lowest energy, the approach also known

as the brute-force approach. In Chapter 6 we demonstrate a massively parallel implementation of the brute-force algorithm using Nvidia CUDA, but before we do this, in this section we will introduce the basic principles of using CUDA-enabled graphic processing units.

### Brief history of Graphics Processing Units

The history of specialized hardware for manipulating graphics ranges as far as the 1970s [52]. Initially, these devices, which later became known as Graphics Processing Units (GPUs), offered limited functionalities. Increasing demand for performance in the gaming industry and professional graphics processing drove the evolution of GPUs, which eventually became highly sophisticated devices supporting advanced 2D and 3D image manipulation. Performing such arithmetically intensive operations requires enormous computational power, and it was only a matter of time until it was realized that the power of these devices could be harnessed for the general purpose computations (so-called GPGPU - General Purpose computing on GPU).

The early forms of GPGPU required framing of computational problems in terms of operations performed on graphical primitives, as this was the only way for using specialized API of GPUs [53, 54]. This changed with the development of devices, toolkits and frameworks that supported operations needed for the general-purpose computations out of the box. Notable examples of such computational frameworks include Nvidia CUDA [55–57] (released in 2007), ATI/AMD FireStream [58, 59] (2006) and ROCm [60–62] (2016) or OpenCL [56] (2009). The research presented in this thesis was conducted using Nvidia CUDA-capable devices, which is why in the rest of this chapter we focus solely on CUDA framework.

#### Differences between CPU and GPU

The principles behind the operation of CUDA-enabled GPUs are fundamentally different from the ones governing the execution of a program on traditional CPU-only architecture. In current x86—based computers, the CPU runs a given sequence of instructions (so-called thread of execution) using one of its cores. Such a processor is the "brain" of a computer, and it can perform a wide variety of tasks ranging from arithmetic operations, through accessing

the system's RAM, to performing IO operations and controlling other components of the system. Typical CPUs are optimized for sequential execution, and as such are usually equipped with moderate (as compared to the GPUs) number of high-performance cores.

On the other hand, GPUs are more specialized. They are well suited for performing numerous arithmetic operations and accessing memory in parallel. They typically have more cores than a traditional CPU (with even modern commodity GPUs boasting thousands of them). Although those cores are less performant than their CPU counterparts and support a much narrower set of operations, their large number combined with fast memory access gives modern GPUs an advantage over CPUs in multiple areas.

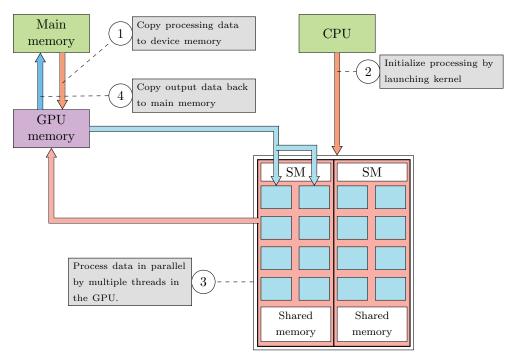

### Processing flow on CUDA

Considering the architectural differences between CPUs and GPUs, it is hardly surprising that both of these types of devices are programmed quite differently. The first major difference is that GPUs cannot operate on their own and are themselves controlled by the CPU. This is why CUDA is a type of *heterogenous* architecture as opposed to CPU-only *homogenous* architecture. The processing flow on CUDA is summarized in Figure 3.6.

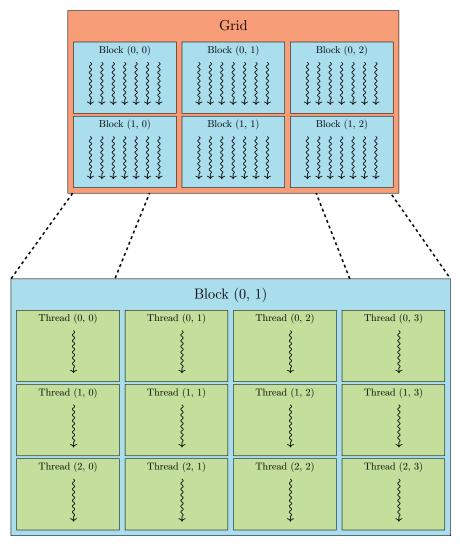

Programs run on GPU are organized in kernels. For the most part, kernels might be viewed as functions or subroutines (which is indeed how they are implemented) that don't have a return value. On a CPU, such a function would be executed by some core as a part of a thread. In CUDA however, the very same kernel is executed by multiple threads. Executing a kernel requires specifying a grid that will be used for running it. A grid can be 1, 2– or 3–dimensional and is itself divided into blocks. Each block is in turn also organized in 1, 2–, or 3-dimensional structure of threads, which has to be the same for every block in the grid. A schematic view of a two-dimensional grid is presented in Fig. 3.7.

As already mentioned, each thread in the grid executes *precisely the same* kernel with *precisely the same* parameters. It might therefore seem surprising that, nevertheless, they can access different parts of memory or otherwise handle a different part of the computational task. This is possible because each thread is identified by its indices in both the grid and the block. Those indices

Figure 3.6: Processing flow on CUDA. The CPU sends input data to the GPU memory and launches the computational kernel. The kernel's code is executed, in parallel, using multiple threads on the GPU. Once the execution is done, results are copied from the GPU memory to the system's RAM.

can be used for computing offsets in arrays that are being processed or (as we will demonstrate in Chapter 6) otherwise used for performing computations.

#### SIMT architecture

CUDA-enabled GPUs employ an architecture called SIMT (Single Instruction, Multiple Threads)<sup>1</sup>. As implied by the name, in SIMT architecture, multiple threads execute the same instruction. Threads are executed in blocks by computational units called Streaming Multiprocessors (SMs), and blocks are distributed to multiprocessors on kernel launch. When a block is distributed to SM, it is further partitioned into warps, groups of 32 threads each. All threads in a warp are scheduled for execution together. Nevertheless, each of

<sup>&</sup>lt;sup>1</sup>One can contrast SIMT architecture used by CUDA with SIMD instructions (Single Instruction, Multiple Data) available on modern CPUs.

Figure 3.7: A schematic view of an example two-dimensional CUDA grid. Presented here is a  $2 \times 3$  grid of  $3 \times 4$  blocks.

them has a separate program counter and thus their execution flow can diverge. At any given time, a thread in a warp can be either active (executing the same instruction as the rest of the active threads in a warp) or inactive (not executing any instruction at all). A thread may be inactive because its execution diverged from the rest of the warp or because it terminated earlier. It is interesting to note that starting from the Volta architecture, threads can

be scheduled on a finer level of granularity, allowing them to diverge and reconverge on the sub-warp level. Each multiprocessor manages a set of 32-bit registers and a parallel data cache, called *shared memory*, distributed among the thread blocks. Since those resources are limited, the number of warps that can run in parallel on any SM is heavily dependent on the resource usage of the kernel being executed.

### Memory hierarchy

On CUDA-enabled devices, threads can access several memory types during kernel execution, including global memory, local memory, constant and texture memory and shared memory [55]. Physically, those different memory types can be divided into device memory (global memory, local memory, constant memory) and on-chip memory (shared memory). SM's on-chip memory also serves as the L1 cache.

Global memory is a device memory available to all threads. All accesses to global memory are serviced in 32-, 64-, or 128- bytes memory transactions. Accesses made from a single warp are coalesced into as many such transactions as necessary, depending on the device's architecture and access pattern. Reads and writes targeting global memory are always cached in L2 and (depending on configuration, compute capability and access pattern) may also be cached in L1 cache.

Local memory in CUDA is only a logical concept. Physically, it resides in the off-chip memory just like global memory and thus offers the same bandwidth and latency. Just like global memory, it is always cached in L2 cache. This type of memory is never used directly by the programmer. Instead, the compiler might decide to use it for local variables of a thread in case there is not enough register (so-called register spilling) or for dynamically indexed local arrays. Local memory is arranged in such a way, that accesses are always fully coalesced as long as all threads access the same relative address (e.g. the same local variable, the same position of a local array etc.).

Constant and texture memory are two types of read-only memory<sup>2</sup> residing in global memory. Accesses to constant memory are cached in constant cache and serialized. Therefore, each request is split into as many transactions as

<sup>&</sup>lt;sup>2</sup>Read-only here means "Not writeable from inside the kernel".

there are different memory addresses in the original request. Texture memory is cached in the texture cache, which is optimized for accessing spatial data. Hence, the best performance is achieved if threads in a warp read or write to the addresses that are placed closely on 2D tiles.

Threads can cooperate and share data through the use of the on-chip *shared memory*. The amount of allocated shared memory is directly controlled by the programmer either on the kernel definition level or during its launch. Shared memory is organized in banks that can be accessed simultaneously, and the best performance is achieved if each thread in a warp accesses memory in a different bank. Otherwise, a *bank conflict occurs*, and the request is split into as few conflict-free requests as possible.

### Programming environment

CUDA devices can be programmed directly using either C/C++ or Fortran. For both languages a Nvidia compiler is required to compile the CUDA program, as CUDA extends C/C++ and Fortran languages with a syntax for defining and launching kernels. The C/C++ CUDA code can be compiled using Nvidia's nvcc compiler, shipped out of the box with the CUDA toolkit. For CUDA Fortran code, the Nvidia High-Performance Computing (HPC) suite contains nvfortran compiler<sup>3</sup>. Giving a comprehensive walkthrough of using either C/C++ or Fortran with CUDA is well beyond the scope of this thesis, but for the sake of completeness, below we present a short example of the CUDA C/C++ and CUDA Fortran code.

Example 3.3 (Implementing parallel vector addition with CUDA). Listings 3.1 and 3.2 below present an example implementation of a parallel vector addition using CUDA. The addVec defined with global attribute is a kernel and accepts two input vectors x, y (in the form of arrays) and their length n. Since CUDA kernels cannot return a value, both versions of the code accept an additional argument res designating where the result will be stored. The addVec kernel can be launched on any one-dimensional grid of one-dimensional blocks. Hence, some threads may need to handle more than one position in the

$<sup>^3</sup>$ The nvfortran compiler was previously a third–party program called pgfortran, developed by PGI [63]

```

def find_bit_to_flip(i): # i starts from 0

return ffs(gray(i) ^ gray(i+1))

```

Listing 3.1: Example code in CUDA Fortran implementing parallel addition of vectors on GPU.

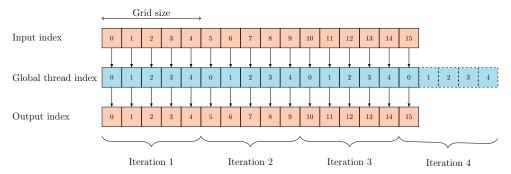

Figure 3.8: A schematic representation of a GPU kernel transforming an input array into an output array of the same size using a grid-stride loop pattern. Here, both arrays are of size k=16 and the hypothetical grid comprises l=5 threads (the exact grid configuration is irrelevant). During the first iteration, the i-th thread accesses i-th input element, transforms it and stores the new value in i-th element of the output array. In subsequent iterations, each thread advances the index it processes by the stride equal to the total grid size. Observe that for the last iteration only the first thread needs to do processing and remaining 4 threads, marked with dashed line, remain inactive.

input arrays. The pattern presented here, where i-th thread handles positions  $i, i+N, i+2N, \ldots$  with N equal total number of blocks is called a *grid-stride* loop and is illustrated in Fig. 3.8.

There are several differences between the two code examples stemming from the languages used. In CUDA Fortran we can copy data from the host to the GPU using array assignment. On the other hand, the equivalent code in C++ requires manually calling cudaMemcpy function. Similarly, the GPU arrays in C++ are declared as pointers, for which the memory has to be manually allocated and later deallocated using the combination of cudaMalloc and cudaFree. Lastly, C/C++ uses zero-based indexing, whereas Fortran uses one-based indexing. This affects how the global thread index, stored in tid variable, is computed.

```

module addVec

contains

attributes(global) subroutine addVec(x, y, res, n)

real, dimension(*) :: x, y, res

integer, value :: n, i, tid, gridsize

tid = (blockidx%x - 1) * blockdim%x + threadidx%x

gridsize = blockdim%x * griddim%x

do i = tid, n, gridsize

res(i) = x(i) + y(i)

end do

end subroutine

end module

program testAddVec

use addVec

use cudafor

implicit none

integer, parameter :: N = 100000

real :: x(N), y(N), res(N)

integer :: i, nBlocks=256, nThreads=128

real, device :: x_d(N), y_d(N), res_d(N)

do i = 1,N

call random_number(x(i))

call random_number(y(i))

end do

x_d = x

y_d = y

call addVec<<<nBlocks, nThreads>>>(x_d, y_d, res_d, N)

res = res_d

write(*,*) 'Max error: ', maxval(abs(res - (x + y)))

end program testAddVec

```

Listing 3.2: Example code in CUDA C/C++ implementing parallel addition of vectors on GPU.

37

### Software ecosystem

Along with the nvcc compiler, the CUDA toolkit contains several, more specialized libraries. Among others, those include:

- cuBLAS [64] CUDA Basic Linear Algebra Subroutines library,

- cuFFT [65] CUDA Fast Fourier Transform library,

- cuRAND [66] CUDA Random Number Generation library,

- cusparse [67] Cuda library for manipulating sparse matrices,

- thrust [68] parallel algorithms library. Thrust also provides parallel implementations of its algorithms that can be run on traditional CPU, making it usable even without CUDA.

For some high-level languages, there exist third-party libraries enabling the usage of CUDA. For Python, one could mention e.g. PyCUDA [69], CuPy [70] or recently introduced setuptools\_cuda [71] created by the author of this thesis. In Julia, integration with CUDA can be achieved with CUDA.jl [72] package.

### Chapter 4

### Simulating dynamics of quantum systems using quantum annealing

One of the leading motivations behind the development of quantum computing devices is simulating quantum systems intractable by classical computers. But how far are we from this goal? To answer this question, one might design an algorithm for conducting such a simulation of a physical system and then test how it performs on the current generation of quantum computers. In this chapter, we follow this idea and present a possible approach for simulating quantum systems (or any time-dependent dynamical system) that can be used with annealing devices such as D-Wave quantum annealers and similar devices. To illustrate the working of our algorithm, we simulate the simplest single-qubit system and demonstrate that already near-term annealing devices are capable of capturing its dynamics in a narrow regime of parameters. Furthermore, the class of physics-inspired problem instances proposed in this chapter can be valuable in benchmarking other (not necessarily quantum) solvers.

# 4.1 Parallel in time simulation of dynamical systems

Optimization problems that can be solved using quantum annealers exhibit no time–dependence. Therefore, simulating any time-dependent phenomena using those devices requires reformulating the problem as one that is static in nature. In our case, it is possible by enlarging the Hilbert space of the system under consideration, so that the states of this larger space encode also temporal information [73].

Let us start by precisely defining the problem we want to address. Consider an L-dimensional real or complex system, whose state at time t is described by the vector  $|\psi(t)\rangle$  evolving according to a differential equation of the form:

$$\frac{\partial |\psi(t)\rangle}{\partial t} = K(t) |\psi(t)\rangle. \tag{4.1}$$

Here, K is the so-called Kamiltonian [74] and can be any linear operator acting on  $\mathbb{R}^L$  or resp.  $\mathbb{C}^L$ . Observe that any isolated quantum system can be described by equation (4.1), as putting  $K = -\frac{i}{\hbar}H$ , where H is its Hamiltonian, transforms the equation (4.1) into Schrödinger equation.

Given an initial state,  $|\psi(t_0)\rangle$  the equation (4.1) admits a unique solution:

$$|\psi(t)\rangle := U(t, t_0) |\psi(t_0)\rangle,$$

(4.2)

where operator  $U(t,t_0)$  is a propagator transforming the initial state of the system into its state at time t and is given by:

$$U(t, t_0) = \mathcal{T} \exp\left(\int_{t_0}^t K(\tau)d\tau\right). \tag{4.3}$$

Here,  $\mathcal{T}$  denotes the time-ordering operation [75]. Note that in the case when K(t) commutes with K(t') for every  $t' \neq t$ , the time-ordering can be omitted. In particular, this is the case if K is time-independent.

Given the initial state, we are interested in finding the state of the system at some time  $t > t_0$ . Numerical methods for solving this problem usually start by partitioning the interval  $[t_0, t]$  into N distinct time points  $t_0 < t_1 < \ldots < t_{N-1} = t$ . Then, the desired state  $|\psi(t)\rangle$  can be computed as:

$$|\psi(t)\rangle = U_{N-1} \cdots U_1 |\psi(t_0)\rangle, \qquad (4.4)$$

#### 4.1. PARALLEL IN TIME SIMULATION OF DYNAMICAL SYSTEMS 41

where  $U_i$  is a shorthand notation for  $U(t_i, t_{i-1})$ . This is purely a rearrangement of computations, which by itself gives no benefit over applying  $U(t, t_0)$  directly. However, shortening the interval allows for a more efficient approximation of propagators, which can be done using a variety of methods, including Suzuki-Trotter approximation [76], commutator-free expansion [77] or tensor-networks based approaches [78].