# Towards Optimizations of Quantum Circuit Simulation for Solving Max-Cut Problems with QAOA

Yu-Cheng Lin National Taiwan University Taipei, Taiwan r11922015@csie.ntu.edu.tw Chuan-Chi Wang National Taiwan University Taipei, Taiwan d10922012@ntu.edu.tw Chia-Heng Tu National Cheng Kung University Tainan, Taiwan chiaheng@ncku.edu.tw Shih-Hao Hung National Taiwan University Taipei, Taiwan hungsh@csie.ntu.edu.tw

# ABSTRACT

Quantum approximate optimization algorithm (QAOA) is one of the popular quantum algorithms that are used to solve combinatorial optimization problems via approximations. QAOA is able to be evaluated on both physical and virtual quantum computers simulated by classical computers, with virtual ones being favored for their noise-free feature and availability. Nevertheless, performing QAOA on virtual quantum computers suffers from a slow simulation speed for solving combinatorial optimization problems which require large-scale quantum circuit simulation (QCS). In this paper, we propose techniques to accelerate QCS for QAOA using mathematical optimizations to compress quantum operations, incorporating efficient bitwise operations to further lower the computational complexity, and leveraging different levels of parallelisms from modern multi-core processors, with a study case to show the effectiveness on solving max-cut problems. The experimental results reveal substantial performance improvements, surpassing a state-of-the-art simulator, QuEST, by a factor of 17 on a virtual quantum computer running on a 16-core, 32-thread AMD Ryzen 9 5950X processor. We believe that this work opens up new possibilities for accelerating various QAOA applications.

### **1** INTRODUCTION

Combinatorial optimization searches for an optimal solution from a finite set of feasible solutions, where an objective function is used to calculate and explore the possible solutions under given constraints. Examples of combinatorial optimization problems include maximum cut problem [2], portfolio optimization [3], and route planning [7]. Combinatorial optimization has important applications in different fields, such as auction theory, IC design, and software engineering. Many combinatorial optimization problems (e.g., the max-cut problem) cannot be solved in polynomial time. In such a case, it is a common method to resort to approximation algorithms (e.g., genetic algorithm [13], Monte Carlo simulation [10], and simulated annealing [17]) to generate good solutions for such problems in polynomial time.

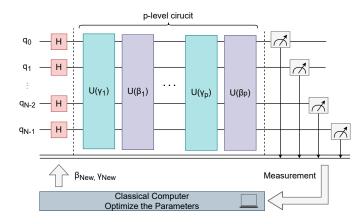

With the advancements in quantum computing, quantum algorithms offer promising alternatives for solving combinatorial optimization problems, where a target problem can be mapped onto a quantum circuit model to be run on a quantum computer to solve the problem. Popular quantum algorithms includes quantum annealing [1], quantum approximate optimization algorithm (QAOA) [5], quantum adiabatic algorithm [6], Shor's algorithm [14], and variational quantum eigensolver [12]. QAOA belongs to the class of quantum-classical algorithms, and this algorithm can exploit classical optimization on quantum operations to tweak an objective function. As illustrated in Fig. 1, a problem is mapped to the quantum circuit (e.g., the *unitary operations*,  $U(\gamma)$  and  $U(\beta)$ ) that adjusts the angles of parameterized quantum gate operations to optimize the expected value of the problem, and the relevant parameter optimization is performed on classical computers. As the updating process iterates, the solution is expected to progressively improve.

A QAOA algorithm can be adopted to solve a max-cut problem either on a physical or virtual quantum computer. As a physical quantum computer has a relatively higher cost and is susceptible to noise (leading to errors in the obtained results), a virtual counterpart established by computer simulations is a more preferable alternative, especially for the early stage of the algorithm development because it is free from the noise, if desired. Unfortunately, while a quantum circuit simulator (e.g., QuEST [9], Quantum++ [8], qHiPSTER [15], projectQ [16], and Cirq [4]) can serve as the platform to evaluate the QAOA algorithm (e.g., to approximate the result for a max-cut problem), its simulation speed is slow and the simulation time grows almost linearly when a more accurate result is desired (refer to Section ?? for theoretical background and Section 3.4 for experimental results).

This work aims to accelerate the simulations of the QAOA circuit for solving a max-cut problem. Our proposal is a comprehensive approach as it covers the optimizations on both quantum and classical computing. That is, we propose the mathematical analysis to compress the quantum operations of the standard QAOA algorithm (Section 2.2), adopting the bitwise operations to further lower the computation complexity (Section 2.3), and exploiting different levels of parallelisms to unlash the computing power of multicore/manycore processors (Section 2.4). The experimental results show that our work outperforms the standard QAOA algorithm running with the state-of-the-art simulator (QuEST [9]) by a factor of 17.1 and 8.3 on the multicore processor and the manycore processor, respectively. We believe this work can be further generalized to support the acceleration of QAOA algorithms targeting various problems.

The contributions made by this work are summarized as follows.

- (1) A comprehensive approach is proposed to optimize the QAOA simulation for a max-cut problem from both quantum and classical computing perspectives as described above. To the best of our knowledge, we are unaware of any other work that serves such a purpose with data analysis.

- (2) An open-source implementation of the proposed optimizations is online available<sup>1</sup> and there are two versions, one

<sup>&</sup>lt;sup>1</sup>https://anonymous.4open.science/r/QAOA\_simulator-8FF3

Fig. 1: A general architecture of the QAOA circuit for a maxcut problem.

for the x86-based multicore processor and the other for the NVIDIA GPU-based manycore processor.

(3) A series of experiments is conducted to demonstrate the efficiency of our proposed optimizations, in terms of simulation speed. Our optimizations achieve a significant improvement of up to two orders of magnitude over the state-of-the-art simulator.

The rest of this paper is organized as follows. Section ?? gives the background and the existing works for the QAOA simulation for a max-cut problem. Section 2 offers the standard QAOA simulation algorithm and the proposed optimization techniques. Section 3 presents the preliminary results. Section 4 concludes this work.

#### 2 METHODOLOGY

The QAOA simulation methodologies and the proposed optimization techniques are presented. Section 2.1 elaborates the baseline methodology for the QAOA simulation and introduces the required parameters. Section 2.2 presents the developed mathematical optimizations to accelerate the QAOA simulation. Section 2.3 offers the optimization that can be used when the max-cut problem can be modelled as an unweighted graph. In addition to the algorithmic optimizations, Section 2.4 introduces the parallelization methodology that utilizes the single-instruction-multiple-data scheme for the developed algorithms to boost simulation performance.

#### 2.1 The QAOA Simulation

The QAOA simulation is performed through the state vector-based scheme on the three-layer quantum gates illustrated in Fig. ??. The important parameters involved with the quantum circuit simulation for QAOA are listed in Table 1. The simulation flow, especially for the max-cut problem, is presented in Algorithm 1.

Given a quantum system with N qubits, the state vector-based simulation scheme requires  $2^N$  complex numbers, each of which represents the amplitude of a specific possible quantum state. The index to the state vector (*stateVector*) is denoted as b, where b is usually represented as binary numbers to better correlate to the qubits, and thereby,  $b_i$  represents the *i*-th bit of b in binary representation. P defines the termination criterion of QAOA, and a larger

Table 1: The parameters required by the QAOA simulation.

| Name        | Description                                                   |

|-------------|---------------------------------------------------------------|

| N           | The total number of qubits simulated                          |

| stateVector | The state composed of $2^N$ amplitude                         |

| b           | The index of the <i>stateVector</i>                           |

| Р           | The number of layers in QAOA circuit                          |

| Yi          | The rotation angle of cost layer in the <i>i</i> -th level    |

| $\beta_i$   | The rotation angle of mixer layer in the <i>i</i> -th level   |

| graph       | The upper triangular matrix used to determine the             |

|             | connectivity of each node                                     |

| w           | The upper triangular matrix used to determine the             |

|             | weight of each node                                           |

| $b_I$       | The integer where each bit is $b_i$                           |

| $graph_I$   | The integer to represent the connectivity of the <i>i</i> -th |

|             | node                                                          |

*P* value would ordinarily lead to a better approximation ratio.  $\gamma_i$  and  $\beta_i$  correspond to the rotation angles and the cost of the mixer layer in *i*-th level, respectively. These angles are essential in modifying the quantum states during the optimization process. The data structure *graph* is used to represent the node connectivity of the graph for the max-cut problem, and *w* is the weight of each graph node. For instance, *graph*<sub>*i*,*j*</sub> indicates the connectivity between node<sub>*i*</sub> and node<sub>*j*</sub> of *graph*, and *w*<sub>*i*,*j*</sub> is the corresponding weight. The integers *b*<sub>*I*</sub> and *graph*<sub>*I*</sub> are used to accelerate the performance of the unweighted graph problem, which will be described later.

Algorithm 1 provides the pseudocode of the quantum circuit simulation for the single-level QAOA, consisting of three essential layer types, *Initial Layer, Cost Layer*, and *Mixer Layer*, as illustrated in Fig. ??. The algorithm follows a standard QAOA that starts with Hadamard gates to all qubits for initialization (*initial layer*). It then explores the solutions via applying *p*-levels of updating layers (*P-level QAOA*, including cost and mixer layers). Through iterative searching for the required parameters at the updating layers, QAOA is able to deliver a viable approximated solution to the given optimization problem.

# 2.2 Mathematical Optimizations

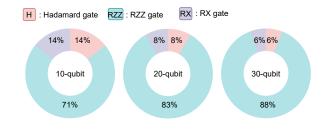

In a quantum circuit simulation, when the simulation time of one quantum gate is similar to that of another gate, the overall simulation time is proportional to the number of gates to be simulated. In Fig. ??, it is obvious that the simulation of the RZZ gates dominates the overall performance. The charts shown in Fig. 2 display the ratios of the three types of gates when the qubits to be simulated increase from 10 to 30, where the percentages of the RZZ gates grow from 71% to 88%. The ratio of the three gate types (H, RZZ, and RX gates) for the single-level QAOA is 2:N-1:2 (derived from  $N:\frac{N(N-1)}{2}:N$ ). With the gate ratio in mind, the optimization of RZZ gates becomes the first target for the mathematical optimization, *rotation compression*, which is followed by the optimization for the Hadamard gates, *launch control*.

**Rotation compression**. This optimization is driven by the inherent diagonal property demonstrated by RZZ gates. It can transform

| Algorithm 1 A typical methodology for the QAOA simulation. |

|------------------------------------------------------------|

|------------------------------------------------------------|

| 1: $stateVector \leftarrow initZeroState()$ 2: $for \ 0 < i < N \ do$ 3: $stateVector \leftarrow HGate(stateVector, i)$ 4: end for5: $for \ 0 6: for \ 0 \le i < N \ doP-level QAOe: for \ 0 \le i < N \ do$ |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3: $stateVector \leftarrow HGate(stateVector, i)$ 4:end for5:for $0  do> P-level QAO$                                                                                                                        |

| 4: end for<br>5: for $0  do \triangleright P-level QAO$                                                                                                                                                      |

| 5: <b>for</b> $0  do \triangleright P-level QAO$                                                                                                                                                             |

|                                                                                                                                                                                                              |

|                                                                                                                                                                                                              |

|                                                                                                                                                                                                              |

| 7: for $i < j < N$ do                                                                                                                                                                                        |

| 8: <b>if</b> graph <sub>i,j</sub> <b>then</b>                                                                                                                                                                |

| 9: $\theta = w_{i,j} * \gamma_p$                                                                                                                                                                             |

| 10: $stateVector \leftarrow RZZGate(stateVector, i, j, \theta)$                                                                                                                                              |

| 11: <b>end if</b>                                                                                                                                                                                            |

| 12: end for                                                                                                                                                                                                  |

| 13: end for                                                                                                                                                                                                  |

| 14: <b>for</b> $0 < i < N$ <b>do</b> $\triangleright$ Mixer Lay                                                                                                                                              |

| 15: $stateVector \leftarrow RXGate(stateVector, i, \beta_p)$                                                                                                                                                 |

| 16: end for                                                                                                                                                                                                  |

| 17: <b>end for</b>                                                                                                                                                                                           |

Fig. 2: The proportions of the three gate types for a singlelevel of QAOA.

the gate-by-gate accesses into state-by-state accesses. As a result, the cache miss ratio during the QAOA simulation can be greatly reduced. This optimization is presented with the following equations, starting from the rewriting of the expression of the cost unitary from Equation ?? into Equation 1.

$$U(\hat{H}_{C}, \gamma) = e^{-\frac{1}{2}i\gamma \sum_{\{i,j\} \in E} w_{i,j} Z_{i} Z_{j}}$$

(1)

Furthermore, based on the definition of a Pauli-Z gate  $(Z_i = \sum_{b \in \{0,1\}^N} (-1)^{b_i} |b\rangle \langle b|)$  that represents the unitary as the summation of matrics in the bra-ket notation, Equation 1 can be derived to Equation 2.

$$U(\hat{H}_{C},\gamma) = e^{-\frac{1}{2}i\gamma \sum_{\{i,j\}\in E} w_{i,j} \left(\sum_{b\in\{0,1\}^{N}} (-1)^{b_{i}} |b\rangle\langle b|\right) \left(\sum_{b\in\{0,1\}^{N}} (-1)^{b_{j}} |b\rangle\langle b|\right)}$$

(2)

In accordance with the definition, the inner product of a bra  $\langle b |$  and a ket  $|b\rangle$  has the following property.

$$\langle b | | b' \rangle = \begin{cases} 1, & \text{if } b = b' \\ 0, & \text{otherwise} \end{cases}$$

(3)

Algorithm 2 The optimized simulation method of the cost layer.

| 1: <b>f</b>  | <b>Function</b> rotationCompression(st     | ateVector, graph, w, y)                           |

|--------------|--------------------------------------------|---------------------------------------------------|

| 2:           | for $0 \le b < 2^N$ do                     | ▷ Scan $2^{N}$ state                              |

| 3:           | $totRotation \leftarrow 0$                 |                                                   |

| 4:           | for $0 \le i < N$ do                       |                                                   |

| 5:           | for $i < j < N$ do                         |                                                   |

| 6:           | if graph <sub>i,j</sub> then               |                                                   |

| 7:           | <b>if</b> $(b_i \oplus b_j) == 1$          | 1 then                                            |

| 8:           | totRotation                                | $\leftarrow$ totRotation – $w_{i,j}$              |

| 9:           | else                                       |                                                   |

| 10:          | totRotation                                | $\leftarrow$ totRotation + $w_{i,j}$              |

| 11:          | end if                                     |                                                   |

| 12:          | end if                                     |                                                   |

| 13:          | end for                                    |                                                   |

| 14:          | end for                                    |                                                   |

| 15:          | $stateVector[b] \leftarrow stateVector[b]$ | $ctor[b] * e^{-\frac{1}{2}i\gamma \ totRotation}$ |

| 16:          | end for                                    |                                                   |

| 17: <b>e</b> | end function                               |                                                   |

Thanks to the bra-ket property in Equation 3, the multiplication is reduced from  $2^{2N}$  to  $2^N$ . The rewritten form is shown in Equation 4, where a ket-gra formalism is used to simplify the calculation, and the sign term is intuitively replaced with the XOR operator.

$$U(\hat{H_C},\gamma) = \sum_{b \in \{0,1\}^N} e^{-\frac{1}{2}i\gamma \sum_{\{i,j\} \in E} w_{i,j}(-1)^{b_i \oplus b_j}} |b\rangle \langle b| \qquad (4)$$

Given the rotation compression optimization in Equation 4, Algorithm 1 (line  $6 \sim 13$ ) can be replaced by Algorithm 2, where the outer loop iterates over for updating the  $2^N$  amplitudes of the quantum state while the inner loop evaluates multiple RZZ gates (through subtraction or addition operations at line 8 and 10). In order words, thanks to the diagonal property of RZZ gates, the tweaked algorithm performs the rotations of RZZ gates first before the corresponding results are deposited into the stateVector at line 15. On the contrary, the ordinary simulation method shown in Algorithm 1 requires a state content update (a memory access) for each simulated RZZ gate, incurring a potentially higher number of memory accesses and hence, a higher cache miss rate. To be exact, the number of memory accesses required for updating the entire stateVector in Algorithm 1 is  $O(N^2)$ , whereas in Algorithm 2, it is reduced to O(1). In summary, this optimization 1) performs consecutive operations on a single quantum state enhancing cache efficiency and 2) converts all multiplications into additions, each quantum state requires only one single rotation.

**Launch control.** In Algorithm 1, the Hadamard gates should be applied to all the qubits for the state initialization, where each amplitude is set to  $(1/\sqrt{2})^N$ . Based on this observation, the simulation can all  $2^N$  amplitudes to  $(1/\sqrt{2})^N$ , so as to avoid the simulation of N Hadamard gates. Together with the rotation compression optimization, the simulation speed of the single-level of QAOA can be further reduced. The impact of this optimization is further discussed in Section 3.

**Algorithm 3** The optimized codes used to accumulate the number of cut/uncut edges in the unweighted graph.

| 1: $c_{neg} \leftarrow 0$                     | ▶ Count the cut edges                  |

|-----------------------------------------------|----------------------------------------|

| 2: for $0 \leq i < N$ do                      |                                        |

|                                               | Expand a bit $b_i$ to an integer $b_I$ |

| 4: $c_{neg} \leftarrow c_{neg} + popCount(g$  | $raph_I \land (b_I \oplus b))$         |

| 5: end for                                    |                                        |

| 6: $c_{pos} \leftarrow totEdge - c_{neg}$     | Count the uncut edges                  |

| 7: $totRotation \leftarrow c_{pos} - c_{neg}$ |                                        |

## 2.3 Unweighted Graph Optimization

Algorithm 2 is developed to deal with the max-cut problem that can be modelled as a weighted graph, where each edge has its own weight/cost value. If the max-cut problem can be modelled as an unweighted graph, where every edge has the same weight/cost of one (i.e.,  $w_{i,j} = 1$ ), Algorithm 2 can be further optimized via bitwise instructions rather than addition and subtraction operations. In particular, the rotations can be computed by bitwise operations and the number of '1' bits corresponds to the number of rotations (which can be obtained by a special operation, called population count *popcount*).

The parameters used in this unweighted graph optimization include *totEdge*,  $b_I$ , and *graph\_I*. *totEdge* is a variable representing the total number of edges in a given graph.  $b_I$  is an *N*-bit integer  $b_I = (b_i, b_i, ..., b_i)$ , where  $b_i$  is the *i*-th bit of the integer *b* repeating *N* times. Similarly, *graph\_I* is also an *N*-bit integer, revealing the connectivity of the *i*-th node of the given graph. Note that the entries of the *i*-th row of *graph* matrix are sequentially arranged into a one-dimensional array in *graph\_I* = (*graph\_{i,N-1}, graph\_{i,N-2}, ..., graph\_{i,0}*) in binary representation.

Algorithm 3 provides the optimized version to replace the pseudocode (line  $5 \sim 13$ ) in Algorithm 2. The XOR operation between b and  $b_I$  is used as a replacement for the XOR operation performed individually on each element in the *i*-th row of *graph*, based on the concept specified in Equation 4. *graph*<sub>I</sub> serves as a bitmask for assessing the connectivity of individual nodes while eliminating redundant bits of the leading *i* bits. The summation of the '1' bits is accomplished by a *popcount* operation. The final result *totRotation* can be obtained with the arithmetic operations on *totEdge*.

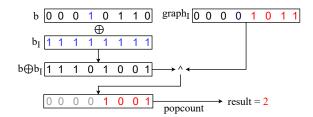

Fig. 3 provides an example of Algorithm 3, where the given values include an 8-bit integer  $b = (00010110)_2$ , an 8-bit integer  $graph_I = (00001011)_2$ , and the indexing value i = 3. After the XOR operation of b and  $b_I$ , the resulting value is  $(11101001)_2$ , which can be further processed by *anding* with  $graph_I$  to obtain  $(00001001)_2$ . The *popcount* operation is applied on the result value to obtain the *count*, which is two in this case. By applying these bitwise operations, a loop layer (located at line 5 of Algorithm 2) can be removed to lower the computation complexity.

#### 2.4 Parallel Optimization

The QAOA simulation takes advantage of both thread- and instructionlevel parallelisms that can be applied on a multicore processor (CPU) and a manycore processor (GPU). The thread-level parallelism exists at the outermost loop (line 2 of Algorithm 2). The OpenMP library is used to parallelize the outermost loop, where parallel

Fig. 3: An example of unweighted graph optimization to count the cut edges, where all parameters are 8-bit integers.

threads are running to process the loop body of different loop iterations on a CPU. A similar parallel execution is also available on a GPU, which can be done with the CUDA library support.

The single-instruction-multiple-data (SIMD) support on a processor can take advantage of the instruction-level parallelism. Modern compilers support the auto-vectorization optimization to transform an input code segment into a parallel version utilizing the SIMD instructions of an underlying processor. Nevertheless, the autovectorization optimization cannot directly apply to Algorithm 2 and Algorithm 3 because 1) the conditional statements (i.e., *if-else* statement) within the loops and the unsupported functions (i.e., the exponential function) in Algorithm 2, and 2) the unsupported function (i.e., the *popcount* operation) on the experimental hardware processor in Algorithm 3. Therefore, the algorithms are manually converted into the style accepted by compilers to take advantage of the underlying parallel hardware with the Advanced Vector Extensions (AVX) instruction set support to accelerate the computations.

The innermost loop is partitioned into sections by using the strip-mining technique, where the length of a strip (or a loop section) is less than or equal to the maximum vector length of the underlying processor. For example, AVX-512 represents a vector operation that can handle a 512-bit number at a time. Furthermore, the loop iteration numbers are defined as *constant* variables, so that compilers can partition the loop iterations at the program compile time. In addition, the statements in the loop body are converted into AVX intrinsic functions to perform the parallel computations. Lastly, the unsupported operations should be replaced with alternative implementations. For example, a lookup table approach is used to handle the *popcount* operations [11]. The performance results of the SIMD optimization are provided in Section 3.2.

## **3 EVALUATION**

The experimental environment is introduced in Section 3.1. The performance improvements achieved by the multicore processor and the manycore processor (using the optimizations described in Section 2)are presented in Sections 3.2 and 3.3, respectively. These performance data are compared against the state-of-the-art work, QuEST. The quality of the approximation results under different *p* values (*p*-level QAOA circuits) is discussed in Section 3.4.

#### 3.1 Experimental Setup

The hardware and software configurations that are used for the QAOA simulation are listed in Table 2. The multicore processor (AMD Ryzen 9) and the manycore processor (NVIDIA RTX 4090)

Table 2: The hardware and software platforms.

| Name     | Attribute                                           |

|----------|-----------------------------------------------------|

| CPU      | AMD Ryzen 9 5950X Processor (w/ 32 threads & AVX2)  |

| GPU      | NVIDIA GeForce RTX 4090 (16,3884 cores, 24 GB mem.) |

| RAM      | Kingston 128 GB (=4 * 32GB) DDR4 2400MHz            |

| OS       | Ubuntu 22.04 LTS (kernel version 5.19.0-43-generic) |

| CUDA     | CUDA Toolkit version 12.1.105                       |

| Compiler | GCC version 12.2.1                                  |

| OpenMP   | OpenMP version 4.5                                  |

are used for the QAOA simulation, and the delivered performance results are compared against those data obtained by the state-of-theart simulator QuEST [9], referred to as baseline that implements the pseudocode in Algorithm 1. Different experimental configurations are represented by the variables, Opt for the adoption of an optimization technique introduced in Section 2 and SU for the speedup compared to the baseline. Specifically,  $Opt_w$  and  $Opt_u$  denote the optimizations for the weighted and unweighted graph, respectively, where the optimizations are run with parallel threads. Furthermore,  $Opt_{uAVX}$  means that the AVX instructions are further used for the computation acceleration, as introduced in Section 2.4. By default, a five-level QAOA is used as the target quantum circuit for our QAOA simulation and for the QuEST simulation. The five-level QAOA is chosen since it would provide superior approximation ratios than traditional approximation algorithms for the benchmark of the u3R and w3R graph [18].

## 3.2 Multicore Processor

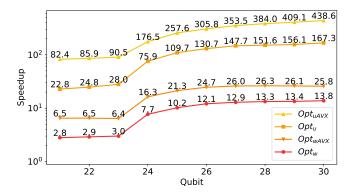

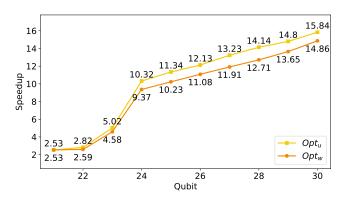

The five-level QAOA is used as the input to QuEST and our simulator with the qubit size ranging from 21 to 30, where the state vectors are kept in 128 GB of the main memory. Table 3 lists the overall performance data delivered by QuEST with parallel threads (*Baseline*), our simulator with parallel threads ( $Opt_w$ ), and with parallel threads plus AVX support ( $Opt_{wAVX}$ ) for a weighted graph. In order to observe the performance improvements achieved by the proposed optimizations elaborated in Sections 2.2 and 2.3 on the cost layer, Fig. 4 plots their speedups to show the performance trends of the optimizations under a different number of qubits.

**Overall performance**. The speedups  $SU_w$  and  $SU_u$  in Table 3 indicate that the optimized Algorithm 2 and Algorithm 3 can reduce the computational complexity (turning the rotations into additions/subtractions in Algorithm 2 and using the bitwise operations in Algorithm 3), resulting in up to 7.5x and 14.2x speedups against the parallel version of QuEST (*Baseline*), respectively. The AVX support can further improve the performance by a factor of 2.1 (for  $SU_{wAVX}$ ) and 2.7 (for  $SU_{uAVX}$ ) on average. It is important to note that when the qubit size is larger than 24, the quantum states cannot be accommodated by the L3 cache of the processor (64 MB). In this case, the vectorized bitwise operations slightly outweigh the overhead of the data movements to pack and unpack the data, and the performance improvements achieved by the AVX feature ( $SU_{uAVX}$ ) drop from 3.1x (23 qubits) to 0.2x (24 qubits).

Fig. 4: The speedup of the cost layer on the multicore processor.

**Speedups of the cost layer**. The performance enhancements achieved by the cost layer are plotted in Fig. 4 to observe the performance-dominant layer behaviors under different qubit sizes. It is obvious that the optimizations presented in Sections 2.3 and 2.4 have a significant impact on the simulation performance. Furthermore, the performance improvements achieved by the AVX feature are significant, where the ideal performance speedup contributed by the AVX feature is four for using four 64-bit integers to handle the four concurrent operations at a time. It is worth noting that if the max-cut problem can be modelled as an unweighted graph, the speed of the QAOA simulation delivered by our tool is 400x faster than that of the state-of-the-art simulator for the cost layer.

#### 3.3 Manycore Processor

The performance speedups  $SU_w$  and  $SU_u$  achieved by the GPU are presented in Table 4. It is important to note that the  $SU_w$  achieved by the GPU is similar to that delivered by the CPU, and this demonstrates that our proposed mathematical optimizations in Section 2.2 have substantial performance improvements across different computer architectures. On the contrary, the  $SU_u$  in Table 3 is larger than the  $SU_u$  in Table 4, which reflects the architectural difference between CPU and GPU. Note that the *popcount* operation is implemented by the GCC library for the CPU version and by the CUDA library for the GPU version.

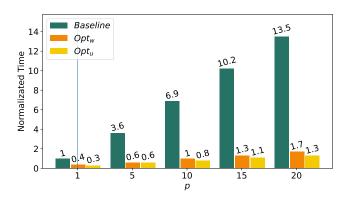

Considering the speedups of the cost layer for the GPU, the simulation time can achieve up to 9.3x speedup  $(SU_w)$  for the 24qubit configuration against Baseline, and the unweighted graph configuration can have an additional 10% improvement  $(SU_u)$ . The detailed performance data are plotted in Fig. 5. It is important to note that the GPU simulation time (e.g.,  $Opt_w$  and  $Opt_u$  in Table 4) is up to two orders of magnitude less than the CPU time (in Table 3). It shows that our proposed methods can provide a better performance boost when a GPU is available. Also note that when the qubit size is larger than 23, the simulation time increases significantly because the L2 cache size of the GPU (72 MB) cannot keep all the states.

| Qubit | Baseline  | <i>Opt</i> <sub>w</sub> | $SU_w$ | <i>Opt<sub>wAVX</sub></i> | $SU_{wAVX}$        | <i>Opt</i> <sub>u</sub> | $SU_u$ | $Opt_{uAVX}$ | $SU_{uAVX}$         |

|-------|-----------|-------------------------|--------|---------------------------|--------------------|-------------------------|--------|--------------|---------------------|

| 21    | 325       | 124                     | 2.6x   | 63                        | <b>5.2x</b> (+2.6) | 30                      | 10.9x  | 21           | <b>15.5x</b> (+4.6) |

| 22    | 710       | 264                     | 2.7x   | 135                       | <b>5.2x</b> (+2.5) | 61                      | 11.6x  | 42           | 17.1x (+5.5)        |

| 23    | 1,940     | 575                     | 3.4x   | 308                       | 6.3x (+2.9)        | 145                     | 13.4x  | 118          | <b>16.5x</b> (+3.1) |

| 24    | 8,418     | 1,762                   | 4.8x   | 1,164                     | 7.2x (+2.4)        | 798                     | 10.5x  | 790          | <b>10.7x</b> (+0.2) |

| 25    | 24,333    | 4,159                   | 5.8x   | 3,020                     | 8.1x (+2.3)        | 2,100                   | 11.6x  | 1,967        | <b>12.4x</b> (+0.8) |

| 26    | 60,794    | 9,257                   | 6.6x   | 6,856                     | 8.9x (+2.3)        | 4,962                   | 12.3x  | 4,693        | <b>13.0x</b> (+0.7) |

| 27    | 138,475   | 20,137                  | 6.9x   | 15,126                    | <b>9.2x</b> (+2.3) | 10,957                  | 12.6x  | 10,410       | <b>13.3x</b> (+0.7) |

| 28    | 302,501   | 42,128                  | 7.2x   | 31,898                    | 9.5x (+2.3)        | 22,885                  | 13.2x  | 21,653       | <b>14.0x</b> (+0.8) |

| 29    | 647,955   | 88,188                  | 7.3x   | 66,667                    | 9.7x (+2.4)        | 47,221                  | 13.7x  | 44,724       | 14.5x (+0.8)        |

| 30    | 1,385,228 | 185,209                 | 7.5x   | 139,663                   | 9.9x (+2.4)        | 97,482                  | 14.2x  | 92,291       | 15.0x (+0.8)        |

Table 3: The elapsed time of 5-level QAOA on the multicore processor with different optimizations (unit: milliseconds).

Table 4: The elapsed time of 5-level QAOA on the manycore processor with different optimizations (unit: milliseconds).

| Qubit | Baseline | Opt <sub>w</sub> | $SU_w$ | $Opt_u$ | $SU_u$ |

|-------|----------|------------------|--------|---------|--------|

| 21    | 17       | 8                | 2.1x   | 7       | 2.4x   |

| 22    | 34       | 17               | 2.0x   | 14      | 2.4x   |

| 23    | 121      | 38               | 3.1x   | 31      | 3.9x   |

| 24    | 488      | 96               | 5.1x   | 81      | 6.0x   |

| 25    | 1,050    | 196              | 5.4x   | 168     | 6.2x   |

| 26    | 2,247    | 398              | 5.7x   | 331     | 6.8x   |

| 27    | 4,809    | 811              | 5.9x   | 676     | 7.1x   |

| 28    | 10,268   | 1,676            | 6.1x   | 1,383   | 7.4x   |

| 29    | 21,877   | 3,407            | 6.4x   | 2,790   | 7.8x   |

| 30    | 46,548   | 6,957            | 6.7x   | 5,640   | 8.3x   |

Fig. 5: The speedup of the cost layer on the manycore processor.

## 3.4 Approximation Result Quality

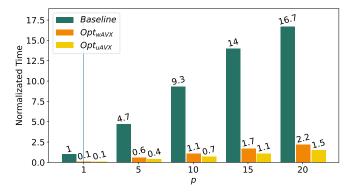

The level of QAOA circuits p relates to the quality of the approximation result as introduced in Section ??, and a larger p value leads to a longer simulation time. If an application developer desires a better result, she/he should wait for a longer time. To analyze how the simulation time scales with the increasing of the p value, a 30-qubit circuit is constructed with the p value ranging from 1 to 20. Figs. 6 and 7 plot the normalized time (normalized to the baseline with

Fig. 6: The CPU simulation times vary with different the values of p for three distinct techniques.

p = 1) when the simulations are performed on the CPU and the GPU, respectively.

Both figures show that the simulation time grows almost linearly with the increasing p value (e.g., approaching the slope of one for the CPU simulation time). On the contrary, our proposed optimization approaches have a relatively shorter simulation time. With ultrafast simulation speed, our methods are able to deliver far better approximation results (e.g., p = 15), but only require 20% more time than the p = 1 configuration running with the state-of-theart simulator on the multicore processor. These results evidently indicate that our methods are able to deliver a higher-quality result at a lower cost (simulation time).

#### 4 CONCLUSION

This work aims to boost the performance of the QAOA simulations for the max-cut problem. Different levels of optimizations have been proposed for the simulation acceleration, in terms of mathematical forms (Section 2.2), bitwise implementation scheme (Section 2.3), and parallelization techniques (Section 2.4). Compared with the state-of-the-art simulator QuEST, our work achieves up to 438x speedups for the cost layer of a single-level QAOA circuit and up to 17x speedups for the five-level QAOA circuit on the multicore processor. A significant performance acceleration is also observed

# Fig. 7: The GPU simulation times vary with different the values of p for three distinct techniques.

on the manycore processor. We believe that our work paves the way toward efficient QAOA simulations for the max-cut problem.

#### REFERENCES

- [1] 1994. Quantum annealing: A new method for minimizing multidimensional functions. *Chemical Physics Letters* 219, 5 (1994), 343–348. https://doi.org/10. 1016/0009-2614(94)00117-0

- [2] Giorgio Ausiello, Alberto Marchetti-Spaccamela, Pierluigi Crescenzi, Giorgio Gambosi, Marco Protasi, and Viggo Kann. 1999. Complexity and Approximation. Springer.

- [3] Fischer Black and Robert Litterman. 1992. Global portfolio optimization. Financial analysts journal 48, 5 (1992), 28–43.

- [4] Cirq 2022. Cirq is a Python library for writing, manipulating, and optimizing quantum circuits and running them against quantum computers and simulators. https://github.com/quantumlib/Cirq

- [5] Edward Farhi, Jeffrey Goldstone, and Sam Gutmann. 2014. A Quantum Approximate Optimization Algorithm. arXiv:1411.4028

- [6] Edward Farhi, Jeffrey Goldstone, Sam Gutmann, Joshua Lapan, Andrew Lundgren, and Daniel Preda. 2001. A quantum adiabatic evolution algorithm applied to random instances of an NP-complete problem. *Science* 292, 5516 (2001), 472–475.

- [7] Merrill M Flood. 1956. The traveling-salesman problem. Operations research 4, 1 (1956), 61–75.

- [8] Vlad Gheorghiu. 2018. Quantum++: A modern C++ quantum computing library. PLOS ONE 13, 12 (dec 2018), e0208073.

- [9] Tyson Jones, Anna Brown, Ian Bush, and Simon C. Benjamin. 2019. QuEST and High Performance Simulation of Quantum Computers. *Scientific Reports* 9, 1 (jul 2019). https://doi.org/10.1038/s41598-019-47174-9

- [10] Christopher Z Mooney. 1997. Monte carlo simulation. Number 116. Sage.

- [11] Wojciech Mula, Nathan Kurz, and Daniel Lemire. 2016. Faster Population Counts using AVX2 Instructions. CoRR abs/1611.07612 (2016). arXiv:1611.07612 http: //arxiv.org/abs/1611.07612

- [12] Alberto Peruzzo, Jarrod McClean, Peter Shadbolt, Man-Hong Yung, Xiao-Qi Zhou, Peter J. Love, Alán Aspuru-Guzik, and Jeremy L. O'Brien. 2014. A variational eigenvalue solver on a photonic quantum processor. *Nature Communications* 5, 1 (jul 2014). https://doi.org/10.1038/ncomms5213

- [13] Colin Reeves. 2003. Genetic algorithms. Springer. 55-82 pages.

- [14] P.W. Shor. 1994. Algorithms for quantum computation: discrete logarithms and factoring. In Proceedings 35th Annual Symposium on Foundations of Computer Science. 124–134. https://doi.org/10.1109/SFCS.1994.365700

- [15] Mikhail Smelyanskiy, Nicolas P. D. Sawaya, and Alán Aspuru-Guzik. 2016. qHiPSTER: The Quantum High Performance Software Testing Environment. arXiv:1601.07195

- [16] Damian S. Steiger, Thomas Häner, and Matthias Troyer. 2018. ProjectQ: an open source software framework for quantum computing. *Quantum* 2 (jan 2018), 49. https://doi.org/10.22331/q-2018-01-31-49

- [17] Peter JM Van Laarhoven, Emile HL Aarts, Peter JM van Laarhoven, and Emile HL Aarts. 1987. Simulated annealing. Springer.

- [18] Leo Zhou, Sheng-Tao Wang, Soonwon Choi, Hannes Pichler, and Mikhail D. Lukin. 2020. Quantum Approximate Optimization Algorithm: Performance, Mechanism, and Implementation on Near-Term Devices. *Phys. Rev. X* 10 (Jun 2020), 021067. Issue 2. https://doi.org/10.1103/PhysRevX.10.021067