# Deep Reinforcement Learning for Energy-Efficient on the Heterogeneous Computing Architecture

Zheqi Yu<sup>®</sup>, Chao Zhang<sup>®</sup>, Pedro Machado<sup>®</sup>, *Member, IEEE*, Adnan Zahid<sup>®</sup>, *Member, IEEE*, Tim. Fernandez-Hart<sup>®</sup>, Muhammad A. Imran<sup>®</sup>, *Fellow, IEEE*, and Qammer H. Abbasi<sup>®</sup>, *Senior Member, IEEE*

Abstract—The growing demand for optimal and low-power energy consumption paradigms for Internet of Things (IoT) devices has garnered significant attention due to their costeffectiveness, simplicity, and intelligibility. In this article, an Artificial Intelligence (AI) hardware energy-efficient framework to achieve optimal energy savings in heterogeneous computing through appropriate power consumption management is proposed. The deep reinforcement learning framework is employed, utilising the Actor-Critic architecture to provide a simple and precise method for power saving. The results of the study demonstrate the proposed approach's suitability for different hardware configurations, achieving notable energy consumption control while adhering to strict performance requirements. The evaluation of the proposed power-saving framework shows that it is more stable, and has achieved more than 34.6% efficiency improvement, outperforming other methods by more than 16%.

*Index Terms*—Deep reinforcement learning, Actor-Critic architecture, Power efficiency, Performance optimisation, Heterogeneous computing.

# I. INTRODUCTION

RADITIONAL power management techniques rely on pre-trained AI algorithms and specialised energy-saving settings for different hardware. Such traditional techniques typically follow predefined energy-saving rules, such as those used in Dynamic Voltage Frequency Scaling (DVFS) [1], where the algorithm is based on feedback control energy-saving actions to optimise voltage and frequency by modelling the power and performance of the system. This approach is limited in its application and effectiveness, as it strongly depends on the construction and preprocessing of the data model. An important area of research is focused on developing methods to maximise power usage while ensuring performance without the need for predefined energy-saving methods and data pre-processing.

In our previous research [2], Yu et al. utilised a reinforcement learning algorithm [3] to observe the states of different

Manuscript created June, 2024; The authors are with the James Watt School of Engineering, University of Glasgow, Glasgow G12 8QQ, U.K. (e-mail: muhammad.imran@glasgow.ac.uk; Qammer.Abbasi@glasgow.ac.uk) Zheqi Yu with Opteran Ltd, Sheffield, UK. (e-mail: zheqiyu@hotmail.com;) Chao Zhang with LAN-XEN, Technology, INC., Shanghai, China. (e-mail: ChaoZhang.z@outlook.com;) Pedro Machado with the Computation Intelligence and Applications Group, Department of Computer Science, Nottingham Trent University, Nottingham, U.K. (e-mail: pedro.machado@ntu.ac.uk;) Adnan Zahid with the School of Engineering & Physical Sciences, Heriot Watt University, Edinburgh, EH14 4AS, U.K. (e-mail: a.zahid@hw.ac.uk;) Tim Fernandez-Hart with Brunel University, CEDPS, Department of Electronic and Computer Engineering, UB8 3PH, Uxbridge, UK. (e-mail:Tim.Fernandez-Hart@brunel.ac.uk)

hardware modules, and subsequently take actions to achieve energy savings. The algorithm's agent improves continuously through a specified learning method, ultimately learning the targeted optimal decisions for energy-saving actions. To enhance the performance of this method, Yu et al. have now combined Deep Learning (DL) [4] with reinforcement learning, making use of the ability of neural networks to fit data [5] and the decision-making capability of reinforcement learning [6]. The results shown a more robust deep reinforcement learning algorithm, which performs better in energy-saving tasks. Yu et al. build upon our prior research by seamlessly integrating DL into an existing reinforcement learning approach. The fusion of DL with reinforcement learning not only enhances the performance of our energy-saving method but also leverages the data-fitting capabilities of neural networks and the decisionmaking prowess of reinforcement learning. The result is a more robust deep reinforcement learning algorithm that excels in energy-saving tasks. Additionally, we introduce the Power Measurement Utility Deep Reinforcement Learning (PMU-DRL) model for controlling hardware power consumption. marking a significant advancement from our earlier work.

In today's computational environments, heterogeneous computing systems, which combine various types of processors (such as Central Processor Unitss (CPUs), Graphics Processor Units (GPU), etc.) for enhanced performance and efficiency, have become the norm. However, managing the energy consumption of these systems presents a significant challenge. DVFS technology is widely regarded as an effective method to enhance the energy efficiency of heterogeneous computing hardware nodes and embedded systems. By dynamically adjusting the operating voltage and frequency of each processor, DVFS optimises energy consumption based on actual performance demands.

Wang *et al.* [7] investigate energy savings in emerging CPU-GPU hybrid clusters through DVFS. They derive a rapid and precise analytical model to calculate the appropriate voltage and frequency settings for each task and employ heuristic scheduling algorithms to allocate multiple tasks to the cluster. The model underscores the nonlinear relationship between task execution time and processor speed in GPU-accelerated applications to capture real-world GPU energy consumption more accurately.

Nabavinejad *et al* [8] introduce a fast and lightweight runtime system: BatchDVFS, that dynamically adjusts input batch processing to adaptively change batch sizes, thereby balancing throughput with power consumption. Utilising a binary search-based method to find the optimal batch size quickly, this

system combines dynamic batching with DVFS technology to control power consumption over a broader range, thus achieving higher throughput under power constraints.

Zamani *et al* [9] designed an energy-saving framework: GreenMD, for an LU decomposition heterogeneous system utilising multiple GPUs. The predicted redundancy applies DVFS to heterogeneous systems by intelligently leveraging slack on CPUs and multiple GPUs. Accurate performance models for CPU and GPU are developed based on algorithmic knowledge and manufacturer's specifications to predict slack time, achieving improved energy consumption for LU decomposition on heterogeneous multi-GPU systems.

However, the implementation of DVFS also faces challenges, including complex control logic and potential performance loss. These case studies also highlight potential drawbacks, such as the complexity of implementing DVFS and the need for careful tuning to balance power consumption with performance requirements. Complex control mechanisms are required to dynamically adjust voltage and frequency based on workload, which could introduce additional overheads, potentially impacting the system's responsiveness and performance.

In this article, we propose a new approach that can achieve more efficient energy management without the need for predefined energy-saving rules and data preprocessing. Deep Reinforcement Learning (DRL), with its self-learning and decision-making capabilities, provides a potential solution. DRL can learn and improve its actions through constant observation and interaction, leading to more efficient energy management.

Wu *et al.* proposes a power-saving framework: a PMU-DRL [10] model for controlling hardware power consumption. The proposed PMU-DRL power-saving framework is implemented on a LynSyn Lite Board (LSLB) [11], and is connected to the heterogeneous computing platform of NVIDIA Jetson TX2 (NJT2) [12] for implementation and evaluation. The results clearly demonstrate that excellent energy consumption control is achieved while meeting stringent performance requirements. The main contributions of this work are as follows:

- Application of DRL for Energy Optimisation: Proposing a novel energy optimisation framework that utilises DRL to achieve significant energy savings in heterogeneous computing. This is accomplished by leveraging the datafitting capabilities of deep learning and the decisionmaking proficiency of reinforcement learning, resulting in an enhanced deep reinforcement learning algorithm for superior performance in energy-saving tasks.

- Novel Power Management Technique: Employing a pioneering PMU-DRL model for controlling hardware power consumption. In contrast to conventional power management techniques like DVFS, which rely on predefined energy-saving rules, the PMU-DRL model eliminates the need for data pre-processing. It utilises self-adaptive feedback through the Actor-Critic architecture, simplifying and refining power-saving strategies.

- Empirical Evaluation: Implementing and evaluating the PMU-DRL framework on the heterogeneous computing platform of NVIDIA Jetson TX2 (NJTX2). The framework exhibited enhanced stability and achieved over a

- 34.6% improvement in efficiency, surpassing the performance of alternative methods.

- Adaptive Energy Optimisation: Developing a DRL framework, an updated iteration of a previously employed reinforcement learning algorithm. It's self-balancing of module working states delivers an optimal energy-saving scheme for the entire system. The approach diverges from traditional handcrafted states, such as using a Q-table for reinforcement learning, and yields more substantial energy-saving effects.

The proposed method study not only offers a new energy optimisation framework, but also that this framework exhibits higher efficiency and stability, leading to significant energy savings in real-world heterogeneous computing environments.

The article's structure is organised as follows: In Section II, the power-saving framework's operation on the heterogeneous computing platform is elucidated, along with details on the signal processing and algorithm calculation workflow. Section III presents a quantitative evaluation of the DRL algorithm, showcasing the achieved power-saving effects. Section IV engages in a discussion of the power-saving results, drawing comparisons with relevant research to highlight contributions. Lastly, Section V delivers a conclusion and suggests potential avenues for future research.

#### II. MATERIALS AND METHODS

The PMU-DRL framework represents a noteworthy enhancement over the reinforcement learning algorithm applied in the prior study. Avoiding the need for data pre-processing, it utilises self-adaptive feedback via the Actor-Critic architecture. This simplification of power-saving strategies enhances precision. The framework's self-balancing of module working states delivers an optimal energy-saving scheme for the entire system, deviating significantly from traditional handcrafted states in reinforcement learning and yielding more substantial energy-saving effects.

In the proposed PMU-DRL framework, we innovatively balance the trade-off between energy and computational performance by using power consumption information to control the working state of the GPU [13]. The proposed algorithm uniquely assesses and predicts the optimal GPU operational states by analysing the overall topological structure and estimating the optimal working state using power consumption data.

The PMU-DRL algorithm balances the trade-off between energy and computational performance by using power consumption information to make decisions and control the working state of the GPU. The algorithm assesses and predicts the optimal GPU operational states by analysing the overall topological structure and estimating the optimal working state using power consumption data. We evaluate the performance of the PMU-DRL by running You Only Look Once (YOLO)v4 [14] on the NJTX2, measuring the power consumption of the on-chip CPU and GPU. YOLO is a state-of-the-art Convolutional Neural Network (CNN) that is able to accurately classify objects in real-time [14]. The algorithm processes the entire image using a single neural network, then divides the

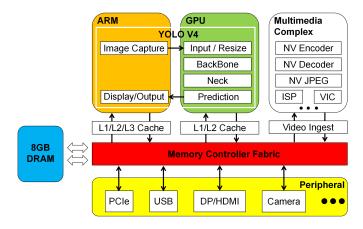

image into parts and forecasts bounding boxes and probabilities for each object [15]. The predicted probability weighs these bounding boxes. The technique "only looks once" at the image, since it only does one forward propagation loop through the neural network before making predictions [16]. Figure 1 has shown the demonstrated YOLOv4 algorithm workflow on the hardware.

Fig. 1. Distributed computation stages of the YOLOv4 neural network inference on the NJTX2

#### A. PMU-DRL Framework

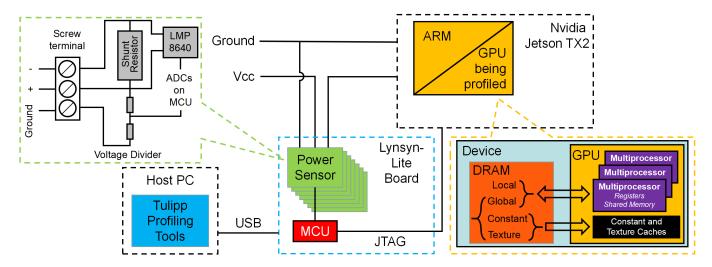

In this section, we present the architecture of the proposed PMU-DRL framework, which is unique in its use of a deep reinforcement learning algorithm to process power information and provide feedback for optimisation actions. Our framework makes innovative decisions to control the scheduling of the GPU based on the energy-saving analysis of the entire system. The setup used to evaluate the power consumption and computational performance of the NJTX2 is illustrated in Figure 2.

Figure 2 illustrates the system architecture used for evaluating the performance of the proposed PMU-DRL framework. The setup comprises the NJTX2 as the host hardware, and a Sundance Lynsyn Lite (SLL). for monitoring the hardware.

The SLL is equipped with a Microcontroller Unit (MCU) [17] and power consumption sensors that are used to operate the PMU-DRL framework. The SLL [18] captures voltage and current information of the NJTX2 at a rate of 1 kilo samples per second (kS/s) and sends it to the PMU-DRL framework for analysis. The framework, based on a deep reinforcement learning algorithm, processes the power information and provides feedback for optimisation actions. Finally, the PMU-DRL framework makes decisions to control the scheduling of the GPU based on the energy-saving analysis of the entire system.

In our PMU-DRL framework, we define the following elements to formalise our problem. First, we define a state s as the current power consumption of the system, as well as the current working state of the GPU. Second, we define an action a as the next operating state of the GPU. Finally, we define a reward function r(s, a) as the amount of electrical energy saved by the system upon taking action a and transitioning to a new state, relative to the previous state. Our goal is to find a policy  $\pi$  that selects an action a for each state s to maximise the expected cumulative reward. A DRL was used to find the best policy.

In the description of the PMU-DRL framework, it is important to note that computing performance does impact the working states of the CPU and GPU. As computing task demand fluctuates, the CPU and GPU may necessitate higher frequencies during periods of increased demand to meet performance requirements, resulting in heightened power consumption. Conversely, during decreased computing task demand, the CPU and GPU can operate at lower frequencies, thereby mitigating power consumption. Consequently, our PMU-DRL framework dynamically adjusts the states of the CPU and GPU to optimise energy usage by analysing data on power consumption and computing performance.

Fig. 2. Setup used to assess the power consumption and computational performance of PMU-DRL. The NJTX2 monitored by SLL.

# B. Power Measurement Unit

The SLL¹ (see Figure 3) Power Measurement Utility (PMU), detailed in [2], is purpose-built for analysing power consumption in embedded systems. While primarily optimised for Field Programmable Gate Arrays (FPGAs), it can be adapted for deployment with the NJTX2. The SLL is equipped with three power sensors for monitoring the power consumption of the unit under test. Furthermore, it incorporates a series design featuring two USARTs (universal synchronous/asynchronous receiver/transmitter) synchronised through the EFM32 PRS trigger system [19]. This configuration enables precise and efficient monitoring of power consumption in the NJTX2.

Fig. 3. SLL Hardware Platform.

In addition, when the board connects to the host workstation via Joint Test Action Group (JTAG). The power measurements can be read directly from the SLL Program Counter (PC) [18]. It can be configured to sample the target signals with frequencies up to 10kHz, and can be used as a generic remotely as an amperimeter or voltmeter. The PMU visualisation tool can be configured to run on a host workstation to display and control the NJTX2 via JTAG.

The SLL delivers efficient power measurement tools ideal to perform power analysis on embedded systems and can be used as a general power analysis tool. Therefore, the SLL is fully compatible with major development platforms including Xilinx ZynqMP [20], NJTX2 [21], Raspberry Pi 4 [22], and Sundance VCS-1 [23].

1) Power Saving Concept for GPU: Context switching is the process of switching between different tasks or threads by the processor. This is done to ensure that the maximum number of tasks are executed in the shortest possible time. When a context switch occurs, the processor saves the current task's kernel context, including the processor registers and program counter, in a Process Control Block [24] (Switch Frame). This information is then used to load the context of the new task and jump to its location in memory, allowing it to run.

The cost of context switching in a CPU is high, as it requires saving and restoring the data from the registers to Random Access Memory (RAM) [25], which takes time. In contrast, the context switch of a GPU uses the CPU resources in a time-sharing manner, and is designed to process parallelisable data, which is less efficient for a CPU to compute sequentially. A GPU utilises an efficient work pool to ensure continuous task execution without idle hardware resources, and when a task encounters a pipeline stall, other tasks can run in parallel and utilise the idle pipelines. This is called a latency hiding work model, where the latency of one task is hidden by the progress of other tasks.

Context switching in a GPU is very fast, as it does not need to save the value of the register to memory as in a CPU. The GPU uses the Single Instruction, Multiple Data (SIMD) mode [26], which means that one instruction can process multiple different data, and has many cores built-in that can simultaneously process multiple threads. Additionally, the GPU can schedule threads at the hardware level, making context switching particularly fast with low overhead.

Overall, the GPU enables significantly reducing the contextswitching in parallelisable tasks, which releases the CPU to process sequential tasks. This improves the overall performance of the system by utilising the resources of both the CPU and GPU effectively.

#### C. Deep Reinforcement Learning

DRL is a type of machine learning that involves an agent learning to interact with an environment in order to achieve a specific goal. There are two main types of algorithms in DRL, namely, 1) Behaviour policy: This is the strategy that the agent uses to interact with the environment in order to produce data; 2) Target policy: This is the strategy that the agent learns to accurately evaluate the Q value, which is the strategy that needs to be optimised.

When the two policies are the same strategy, the method is referred to as an on-policy method. When the policies are different, the method is referred to as an off-policy method. In this project, the Proximal Policy Optimization (PPO) algorithm [27] was used to make smart scheduling of hardware for power optimisation. PPO is an on-policy DRL, and the data used in the buffer is obtained by the target policy. This means that the Replay Buffer stores the data collected by the same policy for updating the network.

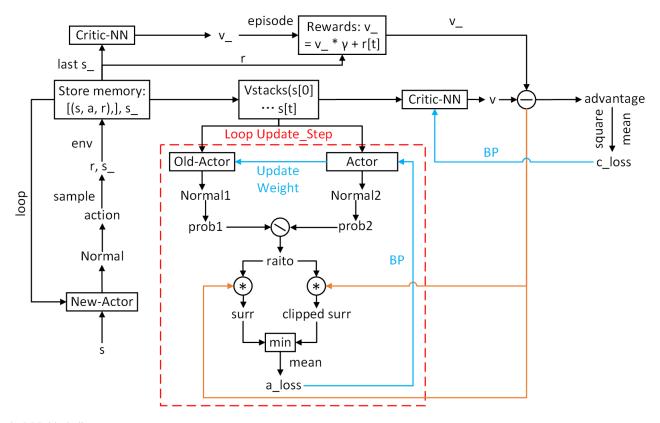

The PPO algorithm includes two network structures: the Actor Network [28] and the Critic Network [29]. The Actor Network takes the state as input and outputs either the action probability for discrete action spaces or the action probability distribution parameters for continuous action spaces [28]. The Critic Network takes the state as input and outputs the state values [29]. The output of the algorithm is considered better if the action output by the actor network can make the advantage larger, and if the value of the state output by the critic network is more accurate. The pseudocode is described in Algorithm 1 and depicted in Figure 4. The PPO agent consists of two parts: interaction with the environment to collect samples, and decision-making of the actions quality. One advantage of the Actor-Critic (AC) network architecture used in PPO is that it can solve DRL problems related to continuous action

<sup>&</sup>lt;sup>1</sup>Available online, https://store.sundance.com/product/lynsyn-lite/, last accessed 27/01/2023

Fig. 4. DRL block diagram.

spaces. Unlike discrete action spaces, it does not require dictionaries or storing value functions as tables or matrices. Instead, the AC network architecture directly uses the Policy-Based method, which uses various policy gradient methods to directly optimise the deep neural network parameterisation's policy. This allows the deep neural network to directly output the action. Additionally, the noise variance of the action can be represented as a trainable vector, rather than being output by the network. This helps prevent overlarge noise variance from generating numerous boundary actions, which can negatively affect the performance of the agent and make the algorithm difficult to explore certain states. PPO is also well-suited for modelling continuous data of GPU energy consumption, which can be used as input for the deep reinforcement learning algorithm. The algorithm's output is the action with energy saving effect.

Figure 4 shows the deep reinforcement learning algorithm architecture. The algorithm's algorithm is illustrated in Algorithm 1 and represented in Figure 4.

The parameters for DRL are detailed in Table I. Leveraging power consumption information from the environment, the algorithm tailors scheduling strategies for both CPU and GPU. In the environment, we define a continuous action space that represents the control strategy for power allocation to the CPU and GPU. This action space has two dimensions, corresponding to the power adjustments for the CPU and GPU, respectively. The range of the action space is [-1.0, 1.0], and then map it into power control. Within this interval, -1.0 signifies a decrease in power by the maximum amount,

TABLE I PPO ALGORITHM HYPER-PARAMETERS.

| Hyper-parameter              | Value        |

|------------------------------|--------------|

| Sample_Step                  | 7000         |

| Reuse_Times (epochs)         | 100          |

| Gamma                        | 0.99         |

| Lambda_Entropy               | 0.95         |

| Clip Epsilon                 | 0.2          |

| Policy_Learning_Rate         | 2e-4         |

| Value_Function_Learning_Rate | 1e-4         |

| Train_Policy_Iterations      | 32 (2048/64) |

| Train_Value_Iterations       | 32 (2048/64) |

| PPO_Update_Times             | 1            |

| Target_kl                    | 2e-4         |

| Hidden_Sizes                 | (8, 64)      |

while 1.0 indicates an increase by the maximum amount. The description can be shown as follows:

- CPU Range: The interval [-1.0, 1.0] maps to [-2, 2], representing a maximum increase of 2 watts or a decrease of 2 watts.

- GPU Range: The interval [-1.0, 1.0] maps to [-3, 3], representing a maximum increase of 3 watts or a decrease of 3 watts.

#### D. Simulation Environment: YOLOv4 and NJTX2

To evaluate the performance of our deep reinforcement learning-based PMU-DRL framework, we set up a simulated environment for an energy-saving algorithm using the NJTX2 hardware platform. This platform is known for its

# Algorithm 1 Proposed PMU-DRL Algorithm

- 1: Input *s* (environmental information) into the *Actor-New* network, and get two values representing the distribution of action. One is *mu* (mean of Normal distribution), the other is *sigma* (variance of Normal distribution).

- 2: Following the Normal distribution to sample an action a.

- 3: Input *s*\_ into the *Actor-New* network to Loop steps 1 and 2 until stored a certain amount of [(s, a, r), ...]. The *Actor-New* network is not updated during this process.

- 4: Input the s\_ obtained in the last step of the loops into the *Critic-NN* to get the v\_ value of the state.

- 5: Calculate discount rewards:  $R[t] = r[t] + \gamma * r[t+1] + \gamma^2 * r[t+1] + \dots + \gamma^{T-t+1} * r[T-1] + \gamma^{T-t} * v_{-}$ , and then achieve  $R = [R[0], R[1], \dots, R[t], \dots, R[T]]$ . (T is the last time step)

- 6: Input all stored s combinations into Critic-NN, get  $V_{-}$  values for all states, and then calculate  $A_t = R V_{-}$

- 7: c\_loss = mean(square( $A_t$ )), and then backpropagation updates the Critic-NN

- 8: Input all stored *s* combinations into the *Actor-Old* and *Actor-New* networks (there are two network structure are the same), and get the Normal distribution of *Normal 1* and *Normal 2*.

- 9: Input all stored action combinations as actions into the Normal distribution of *Normal 1* and *Normal 2* that achieves the corresponding probability of *prob 1* and *prob 2* for each action.

- 10: Divide *prob 2* by *prob 1* to get the important weight, which is *ratio*

- 11: Following equation a\_loss = mean(min((ration \*  $A_t$ , clip(ratio, 1- $\xi$ , 1+ $\xi$ ) \*  $A_t$ ))) to update *Critic-NN* by backpropagation

- Following some Loops by steps 8 11 to update Actor-Old network from Actor-New network's weight.

- 13: Looping all above steps to achieve the finally output.

low power consumption of 15 watts [30] and is designed to run efficient state-of-the-art AI applications. The NJTX2 is a heterogeneous platform that includes the NVIDIA Jetpack Software Developer Kit (SDK) which provides libraries for GPU-accelerated computing, Linux drivers, and the Ubuntu operating system. The on-chip GPU can be programmed using NVIDIA's Compute Unified Device Architecture (CUDA) [31] for accelerating parallelisable algorithms and the CUDA Deep Neural Network (cuDNN) library, which is optimised for Deep Neural Network (DNN), is also installed to ensure maximum computational performance. Additionally, popular AI frameworks such as PyTorch and TensorFlow are integrated with the NVIDIA libraries to simplify the use of the GPU for AI developers. The NJTX2 is widely used in fields such as computer vision, data classification, deep learning and other areas that require intensive computing. It has a wide range of applications, including Intelligent Video Analysis (IVA), drones, robots, gaming devices, virtual reality (vr), augmented reality (ar) and portable medical devices.

The hardware specifications for the NJTX2 system, delineated in Table II, provide crucial information for configuring

the simulation environment in this study. Demonstrating the computational requirements of large-scale deep neural network applications, the YOLOv4 algorithm, detailed in [14], was employed. Furthermore, the YOLOv4 algorithm stands out due to its C++ implementation, yielding lower latency compared to Python-based implementations of other CNNs. This independence from third-party libraries like PyTorch or TensorFlow streamlines AI computing. The C++ implementation of YOLOv4 directly leverages the CUDA instruction set, optimising GPU RAM utilisation efficiency over Python implementations. Consequently, the algorithm is widely adopted in computing resource-constrained embedded environments. In contrast, Python, being a scripting language, requires an interpreter to interpret the code line by line, converting it into machine instructions each time the project is called, allowing the processor to execute the program. In contrast, C/C++ undergoes pre-compilation with gcc, resulting in a one-time compilation into a machine code file executed by the system. The approach enables multiple executions without compromising efficiency. The difference in underlying logic within the hardware system underscores that Python's execution efficiency is not on par with that of the C/C++ language. C/C++ language projects can also leverage the CUDA library for accelerated computation, extending its utility beyond Python project development.

The devised hardware/software configuration effectively simulates the typical workloads imposed by cutting-edge CNNs running on edge devices. It authentically replicates human-like tasks, including detection, observation, recognition, and object identification—tasks commonly performed by individuals monitoring Closed-Circuit Television (CCTV) systems. The application is executed on the hardware platform, capturing real-time power consumption data through the SLL sensors. Subsequently, a simulation environment is constructed using this acquired information. Operating within this simulated setting, the PMU-DRL framework learns and comprehends the hardware requirements for power consumption and performance of the application. Consequently, the PMU-DRL framework optimises GPU scheduling to conserve power on the hardware platform.

In the DRL framework, the assumption is made that the environment is Markov. Thereforem, the system's next state is presumed to depend solely on the current state and the action taken in the current state, excluding past states and actions. The DRL model is trained and makes predictions based on this assumption. Nonetheless, recognition is given to the possibility that, in real-world heterogeneous computing environments, certain state variables or actions might have effects that persist into future time steps. Further exploration of this aspect is planned for future research.

# III. EXPERIMENTAL EVALUATION

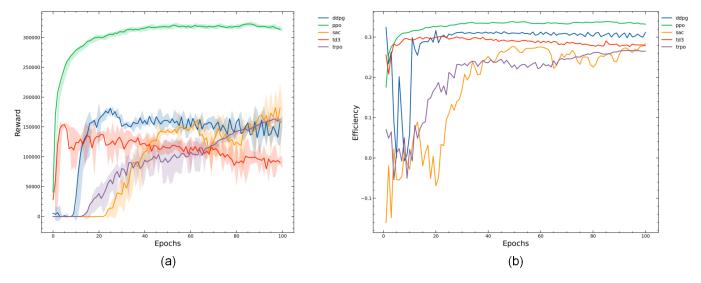

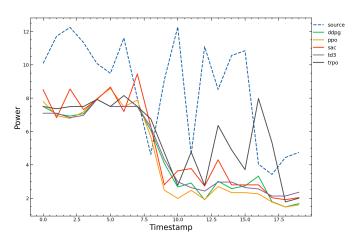

Figure 5 portrays the performance of the DRL algorithm within the PMU-DRL framework, revealing our method's primary learning and performance curves, and comparing with other popular deep reinforcement learning algorithms. All algorithms have been trained with the same epochs that are

Fig. 5. Deep Reinforcement Learning Training Results.

# TABLE II NJTX2 SPECIFICATIONS

| NJTX2                                                                                                   |

|---------------------------------------------------------------------------------------------------------|

| Dual-Core for NVIDIA Denver 2 and<br>Quad-Core for Application Response<br>Measurement (ARM) Cortex A57 |

| 256-core NVIDIA Pascal with CUDA                                                                        |

| 18-Stages, Out-of-Order, 3-way Issue                                                                    |

| 48kB L1-I, 32kB L1-D, 2 MB L2                                                                           |

| 8 GB LPDDR4                                                                                             |

| Ubuntu 20.04 LTS                                                                                        |

|                                                                                                         |

trained 100 epochs on each algorithm to make sure algorithms achieve stable learning output. Figure 5.a provides insights into the agent's training process. It has shown the trend of the rewards' sum during algorithm learning. It is evident from the chart that the PPO algorithm exhibits the quickest increase in reward value during training and achieves the highest final reward compared to the other algorithms. Initially, all algorithms start with low rewards, but the PPO algorithm shows a sharp increase in rewards after approximately 5 epochs, rapidly surpassing the others. After around 25 epochs, the reward curve of PPO stabilizes, maintaining around 300,000, indicating good consistency and the highest performance. In contrast, the training reward curves of the other algorithms either increase more slowly (as with Trust Region Policy Optimization (TRPO) and Twin Delayed Deep Deterministic policy gradient algorithm (TD3)) or rise rapidly but result in lower final rewards (as with Deep Deterministic Policy Gradient (DDPG) and Soft Actor-Critic (SAC)). Not only does the PPO algorithm achieve the highest final reward, but its reward curve also exhibits smaller fluctuations, indicating better stability compared to the others.

For figure 5.b, all algorithms experience fluctuations in efficiency, which is a common occurrence as the algorithms are still adapting to the environment. Over time of training, the PPO algorithm demonstrates higher and more stable efficiency. After an initial period of fluctuation, PPO's efficiency quickly

stabilizes and remains more than 0.34 (34%), the highest among all algorithms. The other algorithms, such as TD3, eventually reach a stable efficiency but at lower levels than PPO, and stabilising slower in the training process. SAC, DDPG and TRPO show lower efficiency for most of the training period, even exhibiting negative efficiency at certain points, indicating that the algorithms may misunderstand the power-saving experience rather than improve efficiency during those epochs. Overall, throughout the training period, PPO not only quickly achieves a high level of efficiency but also maintains it, indicating the best overall performance during the training process. This suggests that in a reinforcement learning framework, when efficiency is considered a key performance metric, the PPO algorithm may be the optimal choice.

The DRL algorithm introduces a delay in assessing the impact of the current decision, necessitating additional time to ascertain if the intended outcome is achieved. Consequently, the adverse effects of decisions are not solely attributable to recent actions, but may also be influenced by errors that occurred in the previous period. The foundational principle of DRL is to swiftly navigate away from the current state in the event of an error and judiciously adjust to facilitate convergence when executing correct actions.

In our experiment, power consumption is derived from sampled voltage and current data. Specifically, at each time point i, denoted as (V[i]) and I[i], the voltage and current are captured by a sensor at a rate of 1 kHz. Consequently, the power at time point i, P[i], is computed as the product of V[i] and I[i]. With a sampling rate f of 1 kHz, the duration of each time point  $\Delta t$  is I/f. Accordingly, the energy consumption E, representing the integral of power over time (as per Equation 1), can be approximated as the sum of the product of power and the duration at each time point:

$$E = \sum P[i] * \Delta t = \sum (V[i] * I[i] * (1/f))$$

(1)

For discrete time systems or simulations, this can be approx-

imated as equation:

$$E = \sum P[t] * \Delta t \tag{2}$$

where:  $\Delta t$  is the time step. Given the context of the paper, the power consumption P(t) could be the power consumed by the CPU and GPU at a given time, which the proposed PMU-DRL system is designed to minimise. The equation provides a precise method to quantify the energy consumption of the system, facilitating a fair and accurate comparison of the energy efficiency among different configurations and algorithms.

Figure 6 illustrates the learning output of the PMU-DRL framework and other algorithms for the effect of energy-saving power consumption. The source curve shows the normal power consumption of the system, and it is compared with all implemented Deep Reinforcement Learning algorithms. Following the power curve trend, which produces our designed PMU-DRL framework of the PPO algorithm is the best power consumption control effect. According to the simulation environment settings, the PMU-DRL algorithm can improve the energy efficiency of the system by understanding the appropriate time for GPU context switching scheduling rules for different processing conditions required by hardware computing.

Fig. 6. Comparison of power consumption effects with and without PMU-DRL framework.

The DRL agent is based on on-policy learning, which avoids the difference between the effect of the optimisation result and the theoretical value affecting the output of the decision. The simulation environment test reflects the different simulations of the running time of the popular program to achieve the overall reaction energy-saving effect. The ablation study of deep reinforcement algorithms for hardware power control resulting data, there are presented in Table III and Table IV.

Table III of algorithm complexity lists five deep reinforcement learning algorithms under the same network architecture that unifies layers and deep reinforcement algorithms setting, the compared results including two metrics: the number of floating-point operations (FLOPs) and the number of parameters (Parameters). Among these five algorithms, it can be seen that under the same deep reinforcement architecture, the PPO algorithm has the smallest computational complexity and

requires the least number of parameters, which means it has the highest computational efficiency, the shortest training time, and the least storage space and memory resources required.

Table IV shows the power consumption and energy efficiency improvement comparison results for normal work mode and five deep reinforcement learning algorithms for hardware control over different time intervals (1s, 10s, 30s, 60s, and 90s). The influence of different time periods on energy consumption is examined through the continuous multiobject detection of the YOLOv4 deep neural network algorithm in the test. All five deep reinforcement learning algorithms demonstrate significant energy savings compared to the normal work mode. The DRL algorithm achieves the highest energy efficiency, reducing energy consumption by more than 34.6% across all time intervals. Therefore, the algorithm can save power without compromising performance requirements, which depends on the algorithm to output more efficient scheduling rules for GPU context switching.

TABLE III

ALGORITHMS' COMPLEXITY

| Energy Complexity Algs | FLOPs | Parameters |

|------------------------|-------|------------|

| DRL(PPO)               | 9536  | 9797       |

| DDPG                   | 14336 | 14724      |

| SAC                    | 24064 | 24712      |

| TD3                    | 28672 | 29448      |

| TRPO                   | 17600 | 17987      |

# IV. DISCUSSION

The article introduces an energy-efficient framework tailored for edge AI hardware platforms, striking a balance between performance and power consumption. The framework simulates the real program's operational environment, showcasing the utilisation of the LSLB sensors for capturing power consumption information. Hardware control is then facilitated through the DRL algorithm, ultimately achieving energy-saving effects. The proposed approach diverges from conventional techniques like DVFS [1] and Adaptive Voltage Scaling (AVS) [35], which necessitate data pre-processing of frequency and voltage information. Furthermore, compared to the DRL algorithm employed in our earlier work [2], the PMU-DRL framework, employing self-adaptive feedback via the AC architecture, offers enhanced accuracy and stability. Operating solely on top-level system power consumption information, the PMU-DRL framework orchestrates optimal energy-saving schemes for the entire system.

Table V provides a comprehensive comparison of results obtained in this work with other similar projects from various sources, showcasing the superior efficiency and energy consumption performance of our proposed framework. The devised method builds upon a previously researched reinforcement learning architecture [2], elevating it to a deep reinforcement learning algorithm. This upgrade not only enhances efficiency by over 16% but also ensures a more stable output. In contrast, traditional methods relying on voltage and frequency control technologies, such as DVFS and AVS,

TABLE IV ENERGY EFFICIENCY EVALUATION

| Energy & Times Efficiency Algs | 1s                              | 10s                             | 30s                              | 60s                              | 90s                               |

|--------------------------------|---------------------------------|---------------------------------|----------------------------------|----------------------------------|-----------------------------------|

| Normal Work Mode               | 8.3623 mWh                      | 83.9054 mWh                     | 254.4317 mWh                     | 510.7967 mWh                     | 771.8151 mWh                      |

| DRL for Hardware Control       | 5.5356 mWh ( <b>33.8028</b> % ) | 54.9101 mWh ( <b>34.5572%</b> ) | 166.6102 mWh ( <b>34.5167%</b> ) | 333.7791 mWh ( <b>34.6552%</b> ) | 504.4102 mWh ( <b>34.6462</b> % ) |

| DDPG for Hardware Control      | 5.5917 mWh                      | 55.2472 mWh                     | 167.6610 mWh                     | 336.0514 mWh                     | 508.2106 mWh                      |

|                                | (33.1321%)                      | ( 34.1554% )                    | ( 34.1037% )                     | ( 34.2103% )                     | ( 34.1538% )                      |

| SAC for Hardware Control       | 5.9427 mWh                      | 58.8223 mWh                     | 177.9094 mWh                     | 356.5327 mWh                     | 537.8799 mWh                      |

|                                | ( 28.9345% )                    | ( 29.8946% )                    | ( 30.0758% )                     | (30.2007%)                       | ( 30.3097% )                      |

| TD3 for Hardware Control       | 5.6252 mWh                      | 55.7439 mWh                     | 169.1433 mWh                     | 339.0435 mWh                     | 512.4474 mWh                      |

|                                | ( 32.7312% )                    | (33.5633%)                      | (33.5211%)                       | (33.6246%)                       | (33.6049%)                        |

| TRPO for Hardware Control      | 6.0435 mWh                      | 60.3145 mWh                     | 182.4971 mWh                     | 365.5448 mWh                     | 551.5803 mWh                      |

|                                | ( 27.7291% )                    | ( 28.1161% )                    | ( 28.2727% )                     | ( 28.4363% )                     | ( 28.5347% )                      |

TABLE V

COMPARISON ENERGY EFFICIENCY WITH OTHERS WORK

| Project       | Hardware                                 | Method                                                    | Energy Efficiency Improved |

|---------------|------------------------------------------|-----------------------------------------------------------|----------------------------|

| Our work      | NJTX2 and SLL                            | Deep Reinforcement Learning algorithm to hardware         | More than 34.6% average    |

|               |                                          | control with GPU context switch rule                      | energy efficiency improved |

|               |                                          |                                                           | with the normal model      |

| Yu et al. [2] | VCS-1 board based on Xilinx ZYNQ Ul-     | DRL on the MCU to control and stop the clocks when        | Up to 18% power reduction  |

|               | traScale+ Multi-Processor system-on-Chip | no data are being exchanged via the I/Os                  | compared with the original |

|               | (MPSoC) Chip and Sundance Lynsyn board   |                                                           | model                      |

| Saroj et. al  | NVIDIA Jetson Nano                       | An application-deadline-aware data offloading scheme      | The most energy reduction  |

| [32]          |                                          | using deep reinforcement learning and DVFS                | ranging between 9.68 and   |

|               |                                          |                                                           | 10.35%                     |

| Jose Nunez-   | ZYNQ Z7020 and Zynq Ultrascale+ ZU9      | The extension and application of an adaptive volt-        | Energy efficiency between  |

| Yanez [33]    |                                          | age scaling framework called Elongate to a high-          | 5%-23% via a +/-1% accu-   |

|               |                                          | performance and reconfigurable binarised neural network   | racy variation.            |

| Sadrosadati   | NVIDIA Tesla P100                        | A idle-time-aware power management technique, which       | Improves the static energy |

| et al [34]    |                                          | use finite state machine to effectively reduce the static | savings by an average of   |

|               |                                          | energy consumption of GPU execution units by exploit-     | 16.9%                      |

|               |                                          | ing their idleness                                        |                            |

depend on data pre-processing for extensive data source analysis. Our method, in comparison, excels in achieving energy efficiency without compromising performance requirements and exhibits adaptability across different hardware platforms. The research underscores the adaptability of our proposed method across various platforms, evident in both theoretical considerations and algorithmic feasibility reflected in the test results. The deep reinforcement learning algorithm at the core of our adaptive architecture allows seamless matching with different hardware configurations without necessitating modifications to the decision-making environment. Furthermore, the algorithm's self-feedback adjustment through the AC architecture enables adaptive matching with unknown hardware parameters, effectively handling changes in hardware. It's essential to note that while a DRL application optimises power consumption management in a heterogeneous computing environment, the energy consumption of the DRL program itself was not measured in this research. The focus was primarily on leveraging the DRL application to achieve optimal energy savings in a simulated environment, and future studies could explore and measure the energy consumption of the DRL program for a more comprehensive analysis.

#### V. CONCLUSION

This research proposed an energy-efficient framework for edge AI hardware platforms that balances performance and power consumption through the use of a deep reinforcement learning algorithm. The results demonstrate that this method is highly effective, achieving a 34.6% improvement in energy efficiency for sustainable system operation. Additionally, the proposed approach is based on self-adaption feedback by the AC architecture and does not require data pre-processing. This makes it a significant improvement over traditional methods such as DVFS and AVS, which rely on data pre-processing of frequency and voltage information to achieve optimal performance.

The results of this study provide strong theoretical support and algorithmic feasibility for extending this method to different platforms and hardware configurations in the future. One possible direction would be to investigate the scalability of the proposed method to larger and more complex edge AI systems. Additionally, further experimentation and testing could be conducted on different types of hardware platforms to validate the universality of the method. Another area for future research could be to explore the integration of other AI algorithms, such as neural networks or evolutionary algorithms, to enhance the performance and energy efficiency of the proposed method. Finally, it would be desirable to apply

the proposed method to other types of systems, such as data centres or cloud computing environments, to further reduce energy consumption and without detorating the computational performance.

# VI. ACKNOWLEDGMENTS

This research project has been made possible with the support of Sundance Multiprocessor Technology Ltd, through the European Union's Horizon 2020 research and innovation program projects: Optimisation for Energy Consumption and Performance Trade-off, under grant agreement No. 779656 and VineScout, under grant agreement No. 737669. The hardware support power monitor system used in this research was provided by Sundance Multiprocessor Technology Ltd. We would like to express our gratitude for their invaluable assistance and support. (Figure 3 illustrates the hardware support provided by Sundance Multiprocessor Technology Ltd.).

#### REFERENCES

- Q. Zhang, M. Lin, L. T. Yang, Z. Chen, S. U. Khan, and P. Li, "A double deep q-learning model for energy-efficient edge scheduling," *IEEE Transactions on Services Computing*, vol. 12, no. 5, pp. 739–749, 2018.

- [2] Z. Yu, P. Machado, A. Zahid, A. M. Abdulghani, K. Dashtipour, H. Heidari, M. A. Imran, and Q. H. Abbasi, "Energy and performance trade-off optimization in heterogeneous computing via reinforcement learning," *Electronics*, vol. 9, no. 11, p. 1812, 2020.

- [3] A. Kumar, A. Zhou, G. Tucker, and S. Levine, "Conservative q-learning for offline reinforcement learning," Advances in Neural Information Processing Systems, vol. 33, pp. 1179–1191, 2020.

- [4] Z. Yu, A. Taha, W. Taylor, A. Zahid, K. Rajab, H. Heidari, M. A. Imran, and Q. H. Abbasi, "A radar-based human activity recognition using a novel 3d point cloud classifier," *IEEE Sensors Journal*, 2022.

- [5] Z. Yu, A. Zahid, A. Taha, W. Taylor, J. L. Kernec, H. Heidari, M. A. Imran, and Q. H. Abbasi, "An intelligent implementation of multisensing data fusion with neuromorphic computing for human activity recognition," *IEEE Internet of Things Journal*, pp. 1–1, 2022.

- [6] X. Wang, S. Wang, X. Liang, D. Zhao, J. Huang, X. Xu, B. Dai, and Q. Miao, "Deep reinforcement learning: a survey," *IEEE Transactions on Neural Networks and Learning Systems*, 2022.

- [7] Q. Wang, X. Mei, H. Liu, Y.-W. Leung, Z. Li, and X. Chu, "Energy-aware non-preemptive task scheduling with deadline constraint in dvfs-enabled heterogeneous clusters," *IEEE Transactions on Parallel and Distributed Systems*, vol. 33, no. 12, pp. 4083–4099, 2022.

- [8] S. M. Nabavinejad, S. Reda, and M. Ebrahimi, "Coordinated batching and dvfs for dnn inference on gpu accelerators," *IEEE transactions on* parallel and distributed systems, vol. 33, no. 10, pp. 2496–2508, 2022.

- [9] H. Zamani, L. Bhuyan, J. Chen, and Z. Chen, "Greenmd: Energy-efficient matrix decomposition on heterogeneous multi-gpu systems," ACM Transactions on Parallel Computing, vol. 10, no. 2, pp. 1–23, 2023.

- [10] C. Wulf, M. Willig, and D. Göhringer, "Low power scheduling of periodic hardware tasks in flash-based fpgas," in 2020 IEEE Nordic Circuits and Systems Conference (NorCAS). IEEE, 2020, pp. 1–7.

- [11] C. Wulf, M. Willig, and D. Goehringer, "Rtos-supported low power scheduling of periodic hardware tasks in flash-based fpgas," *Micropro*cessors and Microsystems, p. 104566, 2022.

- [12] A. Wilson, A. Kumar, A. Jha, and L. R. Cenkeramaddi, "Embedded sensors, communication technologies, computing platforms and machine learning for uavs: A review," *IEEE Sensors Journal*, vol. 22, no. 3, pp. 1807–1826, 2021.

- [13] A. C. Elster and T. A. Haugdahl, "Nvidia hopper gpu and grace cpu highlights," *Computing in Science & Engineering*, vol. 24, no. 2, pp. 95–100, 2022.

- [14] A. Bochkovskiy, C.-Y. Wang, and H.-Y. M. Liao, "Yolov4: Optimal speed and accuracy of object detection," arXiv preprint arXiv:2004.10934, 2020.

- [15] J. Redmon, S. Divvala, R. Girshick, and A. Farhadi, "You only look once: Unified, real-time object detection," in *Proceedings of the IEEE* conference on computer vision and pattern recognition, 2016, pp. 779– 788

- [16] K. R. B. Legaspi, N. W. S. Sison, and J. F. Villaverde, "Detection and classification of whiteflies and fruit flies using yolo," in 2021 13th International Conference on Computer and Automation Engineering (ICCAE). IEEE, 2021, pp. 1–4.

- [17] F. Santoni, A. De Angelis, A. Moschitta, and P. Carbone, "A traveling standard for calibration of battery impedance measurement systems," *IEEE Transactions on Instrumentation and Measurement*, vol. 71, pp. 1–8, 2022.

- [18] A. Djupdal, B. Gottschall, F. Ghasemi, and M. Jahre, "Lynsyn and lynsynlite: The sthem power measurement units," in *Towards Ubiquitous Low-power Image Processing Platforms*. Springer, 2021, pp. 93–114.

- [19] G. Callebaut, G. Leenders, J. Van Mulders, G. Ottoy, L. De Strycker, and L. Van der Perre, "The art of designing remote iot devices—technologies and strategies for a long battery life," *Sensors*, vol. 21, no. 3, p. 913, 2021.

- [20] S. Sabogal, A. George, and G. Crum, "Recon: A reconfigurable cnn acceleration framework for hybrid semantic segmentation on hybrid socs for space applications," in 2019 IEEE Space Computing Conference (SCC). IEEE, 2019, pp. 41–52.

- [21] T. Ye, W. Qin, Z. Zhao, X. Gao, X. Deng, and Y. Ouyang, "Real-time object detection network in uav-vision based on cnn and transformer," *IEEE Transactions on Instrumentation and Measurement*, vol. 72, pp. 1–13, 2023.

- [22] V. Brunacci and A. De Angelis, "Fusion of uwb and magnetic ranging systems for robust positioning," *IEEE Transactions on Instrumentation* and Measurement, 2023.

- [23] B. G. Oliveira and J. Lobo, "Interactive demonstration of an energy efficient yolov3 implementation in reconfigurable logic," in 2019 5th Experiment International Conference (exp. at'19). IEEE, 2019, pp. 235–236.

- [24] Z. M. Khaing, Y. Naung, and P. H. Htut, "Development of control system for fruit classification based on convolutional neural network," in 2018 IEEE conference of russian young researchers in electrical and electronic engineering (EIConRus). IEEE, 2018, pp. 1805–1807.

- [25] L. Yu, E. Yang, B. Yang, Z. Fei, and C. Niu, "A robust learned feature-based visual odometry system for uav pose estimation in challenging indoor environments," *IEEE Transactions on Instrumentation and Measurement*, 2023.

- [26] A. Tino, C. Collange, and A. Seznec, "Simt-x: Extending single-instruction multi-threading to out-of-order cores," ACM Transactions on Architecture and Code Optimization (TACO), vol. 17, no. 2, pp. 1–23, 2020.

- [27] J. Schulman, F. Wolski, P. Dhariwal, A. Radford, and O. Klimov, "Proximal policy optimization algorithms," arXiv preprint arXiv:1707.06347, 2017.

- [28] B. Huang and J. Wang, "Deep-reinforcement-learning-based capacity scheduling for pv-battery storage system," *IEEE Transactions on Smart Grid*, vol. 12, no. 3, pp. 2272–2283, 2020.

- [29] J. Su, S. Adams, and P. Beling, "Value-decomposition multi-agent actorcritics," in *Proceedings of the AAAI conference on artificial intelligence*, vol. 35, no. 13, 2021, pp. 11352–11360.

- [30] H. Cui and N. Dahnoun, "Real-time stereo vision implementation on nvidia jetson tx2," in 2019 8th Mediterranean Conference on Embedded Computing (MECO). IEEE, 2019, pp. 1–5.

- [31] S. Paul, S. Mulani, N. Daimary, and M. S. Singh, "Simplified-delay-multiply-and-sum-based promising beamformer for real-time photoa-coustic imaging," *IEEE Transactions on Instrumentation and Measure-ment*, vol. 71, pp. 1–9, 2022.

- [32] S. K. Panda, M. Lin, and T. Zhou, "Energy efficient computation offloading with dvfs using deep reinforcement learning for time-critical iot applications in edge computing," *IEEE Internet of Things Journal*, 2022.

- [33] J. Nunez-Yanez, "Energy proportional neural network inference with adaptive voltage and frequency scaling," *IEEE Transactions on Com*puters, vol. 68, no. 5, pp. 676–687, 2018.

- [34] M. Sadrosadati, S. B. Ehsani, H. Falahati, R. Ausavarungnirun, A. Tavakkol, M. Abaee, L. Orosa, Y. Wang, H. Sarbazi-Azad, and O. Mutlu, "Itap: Idle-time-aware power management for gpu execution units," ACM Transactions on Architecture and Code Optimization (TACO), vol. 16, no. 1, pp. 1–26, 2019.

- [35] M.-A. LaCroix, H. Wong, Y. H. Liu, H. Ho, S. Lebedev, P. Krotnev, D. A. Nicolescu, D. Petrov, C. Carvalho, S. Alie *et al.*, "6.2 a 60gb/s pam-4 adc-dsp transceiver in 7nm cmos with snr-based adaptive power

scaling achieving 6.9 pj/b at 32db loss," in 2019 IEEE International Solid-State Circuits Conference-(ISSCC). IEEE, 2019, pp. 114–116.

Zheqi Yu received a Bachelor degree in electronic information engineering in 2014, and a Master degree in Information Technology in 2015 from the University of Wolverhampton. He received his Ph.D. degree in Electronic and Electrical engineering from University of Glasgow, U.K., in 2022. Currently, he is Research Engineer at Opteran Ltd, UK, which works on Neuromorphic Hardware design. His other research interests include Neuromorphic computing, hardware design, embedded systems, signal processing, power efficiency, and programmable devices.

Chao Zhang received a Bachelor's degree in Computer Science and Technology in 2019 from the Shanghai Institute of Technology. He is currently working as a research engineer at LAN-XEN, Technology, INC., where his work is focused on research and software development in the area of artificial intelligence penetration testing. In addition to his primary job, he is also deeply passionate about researching the fields of cybersecurity and reinforcement learning.

Pedro Machado received his MSc in Electrical and Computers Engineering from the University of Coimbra (2012) and his PhD in Computer Science from Nottingham Trent University (2022). Dr Machado is a Senior Lecturer in Computer Science, Course Leader for MSc Artificial Intelligence and the secretary for the IEEE Systemic Innovation Special Interest Group (SISIG) Dr Machado's research interests includes neuromorphic engineering, edge computer vision, bio-inspired computing, robotics and intelligent sensors, retinal cell understanding,

biological nervous system modelling, spiking neural networks, robotics and autonomous systems, and neuromorphic hardware, aquaculture, endangered/invasive underwater species.

Adnan Zahid received the B.Sc. (Hons.) degree in electronics and communications engineering from Glasgow Caledonian University and the M.Sc. degree in electronics and electrical engineering from the University of Strathclyde in 2016. He is currently pursuing the Ph.D. Research degree with the University of Glasgow. His current research interests encompasses machine learning to monitor plant's health for precision agriculture applications, and detection of water stress in leaves by integrating deep learning and terahertz sensing.

Tim Fernandez-Hart Tim Fernandez-Hart has a B.Sc. (Hons) in Genetics, an M.Sc. in Industrial Biotechnolgy, a M.Sc. in Medical Ultrasound and received a B.Sc. with first-class honours in Mathematics and Statistics from The Open University, UK in 2021. He is currently working towards a Ph.D. in Computer Systems Research at Brunel University, London, UK. His research interests include AI, neuromorphic engineering, spiking neural networks, event-based sensors and computer arithmetic.

Muhammad Ali Imran (IEEE Follow 2023) received his M.Sc. (Distinction) and Ph.D. degrees from Imperial College London, UK, in 2002 and 2007, respectively. He is a Professor in Communication Systems in the University of Glasgow, Dean University of Glasgow UESTC, Head of Autonomous Systems and Connectivity research division, Head of Communications Sensing and Imaging (CSI) research group and Director of Glasgow UESTC Centre of Educational Development and Innovation. He also serves as an affiliate Professor at

the University of Oklahoma, USA; Adjunct Research Professor AIRC, Ajman University UAE and a visiting Professor at 5G Innovation centre, University of Surrey, UK. He has led a number of multimillion-funded international research projects and the "new physical layer" work area for 5G innovation centre at Surrey. He has a global collaborative research network spanning both academia and key industrial players in the field of wireless communications. He has supervised 50+ successful PhD graduates and published over 600 peerreviewed research papers including more than 100 IEEE Transaction papers. He has an award of excellence in recognition of his academic achievements, conferred by the President of Pakistan. He was also awarded the IEEE Comsoc's Fred Ellersick Award 2014, the FEPS Learning and Teaching Award 2014, and the Sentinel of Science Award 2016. He was twice nominated for the Tony Jean's Inspirational Teaching Award. He is a shortlisted finalist for The Wharton-QS Stars Awards 2014, the QS Stars Reimagine Education Award 2016 for innovative teaching, and VC's Learning and Teaching Award from the University of Surrey. He is a Senior Fellow of the Higher Education Academy, U.K. He is the editor/co-editor of 8 books. Prof. Imran is a Fellow of IEEE.

Qammer H. Abbasi (SM'16) received his BSc and MSc degree in electronics and telecommunication engineering from University of Engineering and Technology (UET), Lahore, Pakistan (with distinction). He received his Ph.D. degree in Electronic and Electrical engineering from Queen Mary University of London (QMUL), U.K., in Jan., 2012. Currently, he is Professor of Applied Electromagnetics & Sensing and theme lead for connecting people with the James Watt School of Engineering, University of Glasgow, U.K., deputy head for Communication

Sensing and Imaging group, past Program Director for Dual PhD Degree, deputy theme lead for Quantum in the University's Advance Research Centre, Co-Manager for RF and terahertz laboratory, lead for healthcare and Internet of things use cases with 5G Center Urban testbed and Project Manager for EON XR Centre. He has grant portfolio of £9M and contributed to more than 450+ leading international technical journal (including nature portfolio) and peer reviewed conference papers and 11 books. Prof. Abbasi is an IEEE senior member and is chair of IEEE AP/MTT UK, Ireland and Scotland joint chapter and was chair of IEEE young professional affinity group. He is an Associate editor for IEEE Journal of Electromagnetics, RF, and Microwaves in Medicine and Biology, IEEE Sensors, IEEE Internet of Things, IEEE open access Antenna and Propagation, senior editor for Frontiers IoT and Sensors Networks section, and acted as a guest editor for numerous special issues in top notch journals. He has been a member of the technical program committees of several IEEE flagship conferences and acted as TPC chair and executive chair for 4th, 5th and 6th international UCET conference 2019, 2020, 2021 in addition to EAI Bodynets 2021 General Co-Chair.