# Scalable on-chip multiplexing of low-noise silicon electron and hole quantum dots

Heorhii Bohuslavskyi<sup>#</sup>, Alberto Ronzani, Joel Hätinen, Arto Rantala, Andrey Shchepetov, Panu Koppinen,

Mika Prunnila<sup>#</sup>, and Janne S. Lehtinen<sup>#</sup>

VTT Technical Research Centre of Finland, Tietotie 3, 02150 Espoo, Finland

<sup>#</sup>Corresponding authors: heorhii.bohuslavskyi@vtt.fi, mika.prunnila@vtt.fi, and janne.lehtinen@vtt.fi

The scalability of the quantum processor technology is elemental in reaching fault-tolerant quantum computing. Owing to the maturity of silicon microelectronics, quantum bits (qubits) realized with spins in silicon quantum dots are considered among the most promising technologies for building scalable quantum computers. However, to realize quantum-dot-based high-fidelity quantum processing units several challenges need to be solved. In this respect, improving the charge noise environment of silicon quantum dot-based qubits and the development of ultra-low-power on-chip cryogenic classical complementary metal oxide semiconductor (CMOS) electronics for the manipulation and interfacing of the qubits are important milestones. We report scalable interfacing of highly tunable and ultra-low charge noise electron and hole quantum dots embedded in a 64-channel cryogenic CMOS multiplexer, which has less-thandetectable static power dissipation (< 1 pW) even at sub-1 K temperatures. Our integrated hybrid quantum-dot CMOS technology provides a route to scalable interfacing of up to millions of high-quality quantum dots enabling, for example, straightforward variability analysis and qubit geometry optimization, which are essential prerequisites for building fault-tolerant large-scale silicon-based quantum computers. At 5.6 K temperature, we find unprecedentedly low charge noise of 22 and 28  $\mu eV/\sqrt{Hz}$  at 1 Hz in the electrostatically defined few-electron and few-hole quantum dots, respectively. The low-noise quantum dots are realized by harnessing a custom CMOS process that utilizes a conventional doped-Poly-Si/SiO<sub>2</sub>/Si MOS stack. This approach provides lower charge noise background than high-k metal gate solutions and translates into higher spin qubit fidelities.

#### Introduction

To fully unlock the potential of quantum computers and run a large spectrum of computations that are uncrackable by classical supercomputers [1], millions of physical quantum bits (qubits) will be required [2,3]. Solid-state qubits based on electron and hole spins in semiconductor quantum dots (QDs) [4-6] are considered to provide one of the most scalable quantum computing platforms [7]. Historically, the first semiconductor spin qubits were demonstrated in GaAs in 2005 [8]. More recently, the progress in manufacturing commercial silicon transistors and CMOS circuitry - accumulated since the 1960s - has been harnessed for the fabrication of silicon QD spin qubit devices [9-11]. However, the demonstration of the coherent control of spins in silicon QDs hosted in advanced complementary metal oxide semiconductor (CMOS) silicon transistors [9,10] does not directly solve the challenge of the spin-based quantum information being extremely sensitive to background charge and (nuclear) spin environment [7]. Luckily, standard Si component processing can also accommodate isotopically purified silicon (<sup>28</sup>Si), which leads to a reduction of the nuclear spin originated noise and, thereby, higher-fidelity Si-based spin qubits can be achieved using either planar SiMOS- or FinFET-based geometries [11-13]. Furthermore, given the prospects of direct integration with on-chip classical cryogenic electronics used to initialize, drive, read out qubits, and perform quantum error

correction [14-17], silicon-based platforms have become one of the most studied routes for building large-scale quantum computers [16].

Among challenges to be solved towards realizing large-scale Si quantum computers, quantum dot charge noise and its increase at "hot" temperatures (above 1 K), where spin qubits would be ideally operated [10,18-19], is of great importance. Large-scale analysis of mesoscopic spin qubit devices is required to engineer better qubits. In this respect, cryogenic signal multiplexing is considered extremely important for large-throughput characterization and, at the same time, interfacing layer of quantum processors [20-25]. Therefore, integrated and scalable low-power cryogenic CMOS auxiliary circuitry (cryo-CMOS) interfacing quantum dot-based qubits is another crucial challenge to be solved to build large-scale silicon quantum computers [14-16].

In this article, we report on scalable interfacing of an array of electron and hole quantum dots with monolithically integrated on-chip ultra-low power 64-channel cryo-CMOS multiplexer (MUX). Using a custom silicon-on-insulator (SOI) fabrication process with the all-silicon gate stack, we demonstrate a high degree of tunability of electron and hole double SiMOS quantum dots with large addition energies and gate lever arm parameter, measure extremely low charge noise at 5.6 K (approaching the best values reported for Si/SiGe and Ge/SiGe quantum dots) and demonstrate scalable characterization of several dozens of quantum dot devices measured in the same cooldown. Our hybrid quantum-dot CMOS technology development was focused on improving the quality of quantum dots by using an older, all-silicon CMOS process successfully used in semiconductor manufacturing in the past, unlike the more advanced CMOS processes featuring high-k (e.g. HfO<sub>2</sub>) oxide and metal gate (e.g. TiN) in the MOS stack, which were recently applied to make wafer-scale qubits [9-11]. Using the same process, we also realized excellent metal oxide semiconductor field effect transistors (MOSFETs) and cryo-CMOS circuits on the same chip as quantum dot devices.

We correlate the low charge noise in electron and hole quantum dots with the record cryogenic turn-on sharpness of our MOSFETs in the weak inversion regime (described by subthreshold swing). The n- and p-type MOSFETs were fabricated using the same "all-silicon" process. We demonstrated that our cryogenic multiplexing based on a decoder and analog switches is quasi-dissipationless from 5.6 K down to 300 mK and thus, holds excellent potential for very large-scale characterization of silicon quantum dots and spin qubits.

## Multiplexer, device selectivity, and cryo-CMOS

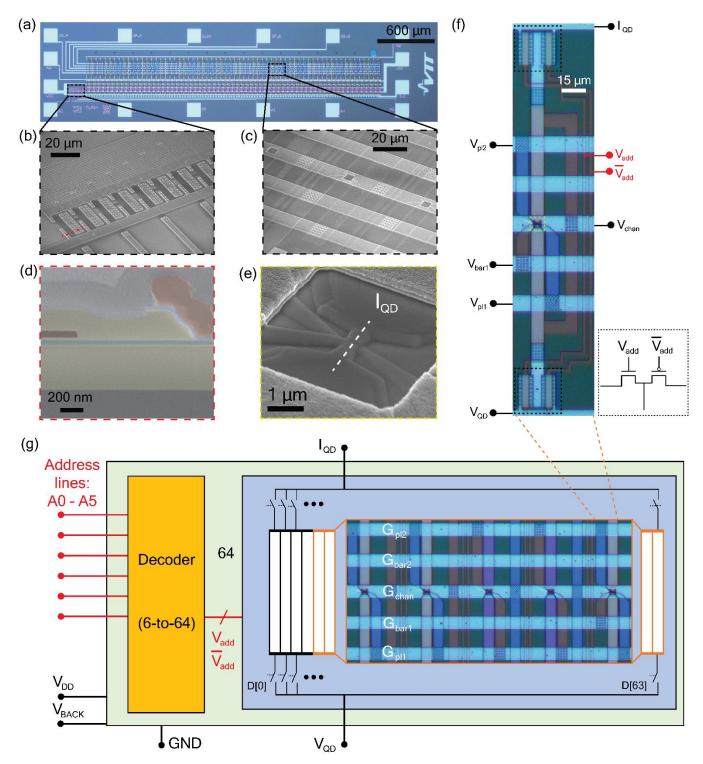

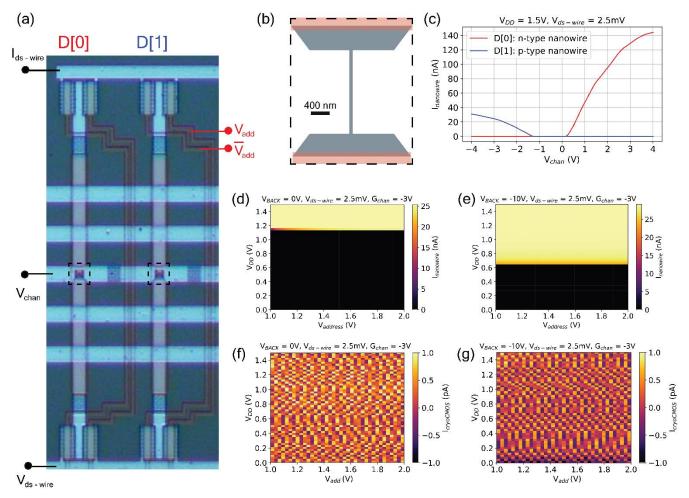

Figures 1 (a)-(f) show micrographs of the monolithically integrated cryo-CMOS MUX - quantum dot device. An optical micrograph of the 64-channel multiplexer is shown in Fig. 1(a). A block of cryogenic conventional logic featuring standard CMOS NAND3 logic gates is shown in Fig. 1(b) and three parallel DQD devices are shown in Fig. 1(c). A cross-section of the MOSFET used for the cryo-CMOS logic is shown in Fig. 1(d). MUX-quantum dot components were realized on SOI wafers with a custom fabrication process involving an undoped channel, n++ doped Poly-Si/SiO<sub>2</sub>/Si front-end-of-line, and TiW + A1 for the backend metallization. The tilted scanning electron microscopy (SEM) micrograph of a DQD device taken after the final passivation step of the back-end-of-line process is shown in Fig. 1 (e). The same process was used in the fabrication of recently reported ambipolar double quantum dot devices [26]. Here, the gate length and gate pitch for all the quantum dot devices is 50 nm and the SOI channel thickness is 70 nm.

The cryo-MUX is composed of a 6-to-64 decoder, made of standard CMOS NAND3, NOR, and NOT gates, and analog switches using a transmission gate design featuring a pair of n- and p-MOSFETs. An optical micrograph of an electron double

quantum dot is shown in Fig. 1 (f). The inset shows a circuit topology of the analog switch. The simplified schematic of the MUX is shown in Fig. 1(g). The MUX logic part features a supply power line  $V_{DD}$ , ground contact, and the 6 address line voltages A0 – A5. To select one of the devices under test among 24 single electron and hole QDs, 24 electron and hole DQDs, and 16 test nanowires, a combination of the A0 – A5 voltages is supplied to the decoder while having  $V_{DD}$  applied. For example, to select the second device D[1] (counting starts from D[0]),  $V_{add} = \{A0 = "0", A1 = "0", A2 = "0", A3 = "0", A4 = "0", A5 = "1"\}$  is applied. Here, "0" and "1" are the logic zero and one. Then, for example, the electron DQD dev#1 (D[42]) introduced in Fig. 2 was selected by applying  $V_{add} = \{"0", "1", "1", "0", "0", "1"\}$ .

The role of  $V_{add}$  can be understood as follows: it corresponds to the direct and inverted gate voltages applied to the n- and p-MOSFET of the analog switch, to have the switch transistors fully open (saturation regime). By measuring the source-drain current as a function of gate voltage  $I_{DS}(V_{GS})$  of individual transistors, we estimated the pair of analog switches to add approximately a few k $\Omega$  of resistance in series with the M $\Omega$ -impedance QD device. The quantum dot experimental data presented in this article were acquired using  $V_{add} = V_{DD} = 1.5$  V. However, the MUX can operate at lower  $V_{DD}$  as shown in Extended Data Fig. 1. Furthermore, we envision lowering  $V_{DD}$  even further either by having two global independent back gates for n- and p-MOSFETs as it was done in some commercial low-power silicon-on-insulator technologies characterized at low temperatures [27].

All 64 devices share the 5 chip terminals to drive the voltages applied to two plunger gates  $G_{pl1}$  &  $G_{pl2}$ , two barrier gates  $G_{bar1}$  &  $G_{bar2}$ , and one accumulation gate  $G_{chan}$ . Depending on the selected device, a given gate electrode can be either at gate-1 or gate-2 level. The difference between the two gate layers is the gate oxide thickness, which is 20 nm and 55 nm, respectively. Moreover, depending on the layout of the selected device, plunger gates can become barrier gates and vice versa, thus offering possibilities for large-scale characterization of quantum dot devices with different geometry. The device selectivity using D[0] and D[1] which are n- and p-type gated nanowires is demonstrated in Extended Data Fig. 1. There, to confirm that the MUX decoder and switches function as designed, FET transfer characteristic of devices D[0] and D[1] are shown, featuring the accumulation of electrons and holes in the nanowire D[0] and D[1], respectively. The cryo-CMOS logic leakage current was found to be  $I_{cryoCMOS} < 1$  pA which was the noise floor of the used setup corresponding to the sub-pW cryo-CMOS power dissipation level. We confirmed the static power dissipation of < 1 pW and correct device selectivity for 64 devices measured in two different 64-channel MUXes at 5.6 K. Several dozens of coarse-resolution stability diagrams for n-type and p-type single and double quantum dots and test nanowires from the two different MUX devices are shown in Supplementary Figures 1-9.

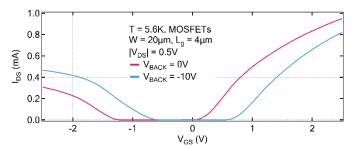

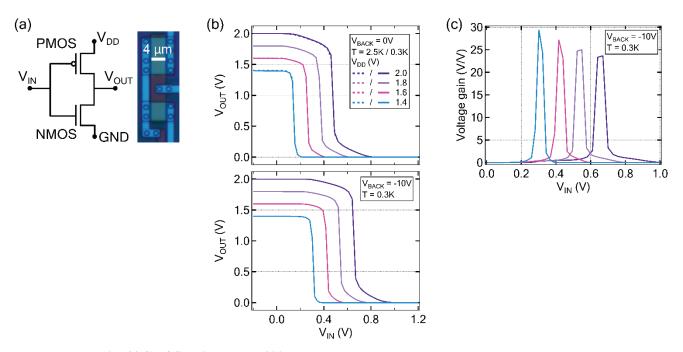

The transfer characteristics  $I_{DS}(V_{GS})$  of individual n- and p-MOSFET measured at 5.6 K are shown in Extended Data Fig. 2. Since the same n++ Poly-Si was used in the gate stack of both n- and p-type transistors, the threshold voltages are different. Upon applying global back-biasing  $V_{BACK} = -10$  V, close matching of cryogenic threshold voltages of n- and p-MOSFETs is demonstrated. The subthreshold swing  $SS = \partial V_{GS}/\partial \log (I_{DS})$  as a function of source-drain current for n- and p-MOSFETs and quantum dot devices configured as FETs in the linear source-drain bias regime is shown in Extended Data Fig. 3. The temperature dependence of SS is given by  $SS = m \ln 10 k_B T/e$ , where T is the temperature,  $k_B$  is the Boltzmann constant, e is the elementary charge, and m is a technological parameter related to the fabrication process and mainly results from a finite density of interface traps and disorder at the channel/gate oxide interface [28]. The lowest possible value of SS in conventional MOSFETs at 300 K is 60 mV/decade, which corresponds to m = 1. In our case, we measured m(300 K) = 1.33 based on the SS(300 K) = 80 mV/dec measured for n- and p-MOSFETs. The measured SS at 5.6 K however does not follow the linear scaling with temperature. In Ref. [29] the underlying physics of the weak inversion operation of MOSFETs (below threshold voltage) where the diffusive transport of charge carriers results in  $I_{DS}$  was explained. It was shown that applying the concept of band broadening introduced by Lifshitz in the 1960s [30] explains the saturation of *SS* in cryogenic MOSFETs below a certain critical temperature  $T_c$ , given by a few-meV ( $k_BT_c$ ) disorder-induced tail [31] in the density of states (DoS) below the edge of conduction and valence bands,  $E_c$  and  $E_v$  respectively.

The previous record values of *SS* at low temperatures below  $T_c$  using commercial SOI technology planar transistors were of the order of 7-8 mV/dec down to mK temperatures [29]. It should be noted that several recent wafer-scale silicon spin qubits [9-11], as well as low-power cryo-CMOS circuits [32], used the so-called high-k metal gate process or featured metal gate which is characterized by larger disorder and noise in both conventional transistors [33] and quantum-dot-based spin qubits [34]. On the other hand, we fabricated quantum dot devices and cryo-CMOS circuits on the same wafer using the same Poly-Si/SiO<sub>2</sub>/Si process. In the linear  $V_{DS}$ -regime, by measuring  $I_{DS}(V_{GS})$  of individual MOSFETs and quantum dot devices configured as field-effect transistors (FETs), we obtained the world's sharpest to-date SS values of 4 mV/dec in the weak inversion regime. The 4 mV/dec value corresponds to 1.5 meV band tails below  $E_c$  and  $E_{\nu}$ . In the absence of SS-saturation, we would expect SS(5.6 K) = 1.5 meV/dec. Based on the measured 4 mV/dec, we estimate the critical temperature, below which the *SS* is saturated to be ~ 15 K (=  $k_BT_c$ ). This finding is extremely promising for building both ultra-low-power cryo-CMOS (due to very sharp turning on and adjustable  $V_{TH}$  via back-biasing) and making low-disorder silicon quantum-dot-based spin qubits.

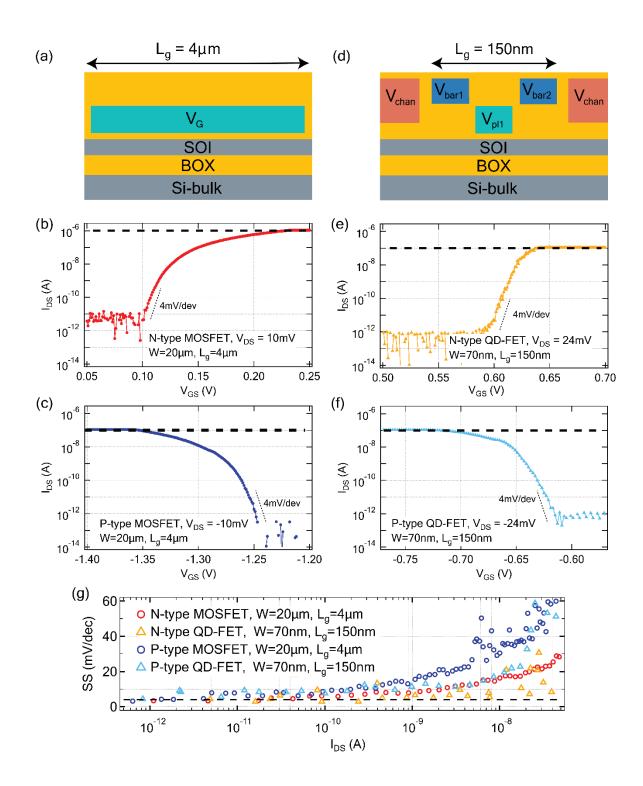

Now, let us consider the most basic CMOS logic gate which is the inverter (NOT-gate). We measured the single inverter at both 2.5 K and 300 mK and an almost identical operation for cryo-CMOS logic at both temperatures were found. Moreover, we confirmed the advantageous effect of negative back-gate biasing, the MOSFET threshold voltage tunability with back-biasing is shown in Extended Data Fig. 2. The latter makes the  $V_{\text{TH}}$  of p- and n-MOSFET more symmetrical and the transistors are thus better matched. Nevertheless, the CMOS logic is also fully operational in the absence of back-gate biasing. Finally, we illustrated the potential of our cryo-CMOS logic for analog circuitry applications by analyzing the CMOS inverter's voltage gain. Using the negative back-gate biasing with  $V_{\text{BACK}} = -10$  V, we demonstrated close matching of n- and p-MOSFETs [35] despite using n++ Poly-gate for both transistors. The measured voltage gain of a single inverter reaches  $dV_{\text{OUT}}/dV_{\text{IN}}$  of ~ 25 - 30 at both 2.5 K and 300 mK, which is comparable to the performance of commercial advanced analog CMOS circuitry [35]. The inverter datasets are shown in Extended Data Fig. 4.

#### Tunable low-noise electron and hole double quantum dots

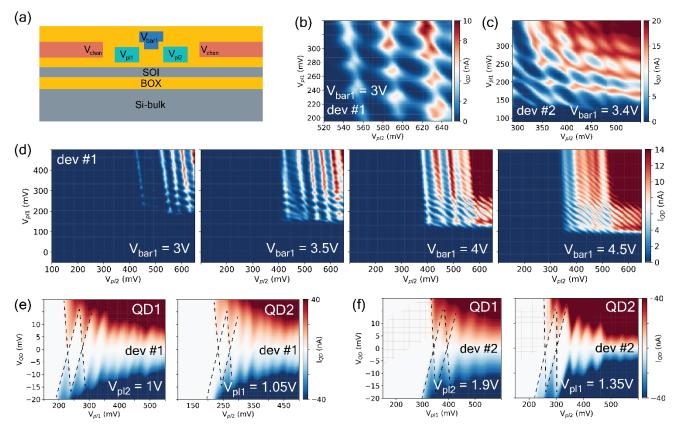

The schematic cross-section of a DQD device (inside the MUX) whose SEM image was presented in Fig. 1 (e), is shown in Fig. 2(a). The electron and hole DQDs reported in this Article did not feature dedicated access tunnel barriers. Thus, to facilitate the electron DQD formation and to make the access tunnel barriers connecting QDs to the reservoirs more opaque, back-gate biasing with  $V_{BACK} = -10$  V was used to characterize two nominally identical electron DQDs. We find almost the same charge noise, lever arm, and charging energy at  $V_{BACK} = 0$  V and -10 V (applied through  $t_{BOX} = 400$  nm), verified for QD2 of dev#1 described in Fig. 2 ( $V_{BACK} = -10$  V), see Supplementary Fig. 10 for the data on the same device measured at  $V_{BACK} =$ 0 V. In Fig. 2 (b) and (c), the DQD stability diagrams obtained by sweeping two plunger gates with  $V_{pl1}$  and  $V_{pl2}$  while fixing the inner barrier gate voltage  $V_{bar1}$  are shown. The quantum dot source-drain bias was fixed to  $V_{QD} = 2.2$  mV and 1.8 mV and barrier gate voltage was set to  $V_{bar1} = 3$  V and 3.4 V for dev#1 (D[42]) and dev#2 (D[58]), respectively. The accumulation gate voltage  $V_{chan} = 3$  V was used for both devices. A typical honeycomb pattern – the signature of two coupled quantum dots [36] was obtained for dev#1 and dev#2 by measuring source-drain current  $I_{OD}$  through the device as a function of two plunger gate voltages ( $V_{pl1}$ ,  $V_{pl2}$ ). The evolution of two weakly coupled QDs into strongly coupled almost merged quantum dots as a function of  $V_{bar1}$  is shown in Fig. 2(d).

Next, we focus on the Coulomb diamond measurements for which weakly coupled DQDs were configured with  $V_{bar1} = 2.1$  V and -1.5 V for dev#1 and #2 respectively. To probe Coulomb diamonds of QD1 (QD2), we filled the adjacent QD2 (QD1) with a dozen electrons and used the latter as an extended electron reservoir, see Fig. 2(e) and (f). While the current QD devices did not feature a charge sensor to ensure that the 1<sup>st</sup> electron was detected, judging by the gradually decreasing addition energy  $E_{add}$  (energy required to load an additional electron onto a QD, see [36]) as the QD is filled up, and no interruption of the opening edges of the first diamond, we assume that the few-electron regime has been reached. It should be noted that the similar addition energy  $E_{add}$  for the first detected electrons was measured in dev#1 and dev#2, and similar plunger and barrier voltages were used to tune up both devices. We also tested that upon applying  $|V_{DS}| > 20$  mV, the QD devices with similar geometry as the DQDs described above become field-effect transistors (see Extended Data Fig. 3). This is another experimental result toward the conclusion that the few-electron regime was reached.

Charge noise in silicon spin qubits is one of the limiting factors for improving qubit performance [9-11, 34, 37-41]. The spin qubit's charge noise background couples to the spin via spin-orbit coupling (SOC) but can also affect spin coherence through other mechanisms [42]. Unlike *III–V* nanowire-based spin-orbit qubits [43,44], SOC is weak in silicon, but its impact on spin coherence of SiMOS QDs accumulated at the interface between Si and gate oxide is not negligible. The role of charge-noise-induced spin decoherence in silicon qubits is extensively discussed in [42]. In the recently reported foundry-grade electron spin qubits [11], the charge noise was found to be limiting the spin coherence: charge noise at 1 Hz,  $S_e(1 \text{ Hz}) = 2 - 10 \, \mu eV/\sqrt{Hz}$  was measured in the many-electron regime, and  $S_e(1 \text{ Hz}) = 29 \pm 27 \, \mu eV/\sqrt{Hz}$  estimated in the few-electron regime were reported for FinFET-like spin qubits in isotopically purified <sup>28</sup>Si measured at a base temperature of 10 mK. The state-of-the-art  $T_1 > 1$  s (longitudinal relaxation time) and  $T_{2,CPMG} > 3$  ms (spin coherence time measured with dynamical decoupling technique using the Carr-Purcell-Meiboom-Gill (CPMG) sequence [45] with 30- $\pi$  pulses) were reported in Ref. [11], where the estimated low-frequency charge noise  $S_e(1 \text{ Hz})$  was  $\sim 30 - 60 \, \mu eV/\sqrt{Hz}$ . These results are comparable to the state-of-the-art <sup>28</sup>Si/SiGe quantum dots and single spin qubits with fidelities exceeding 99.9% reported in [37,38]. Thus, we can consider a quantum-dot-based spin qubit defined in <sup>28</sup>Si with low-frequency charge noise in the few-electron or hole regime of a few tens of  $\mu eV/\sqrt{Hz}$  at 1 Hz to be at the threshold for fault-tolerant quantum computing enabled by quantum error correction [46-48], provided the charge noise is the main spin coherence limitation mechanism [37].

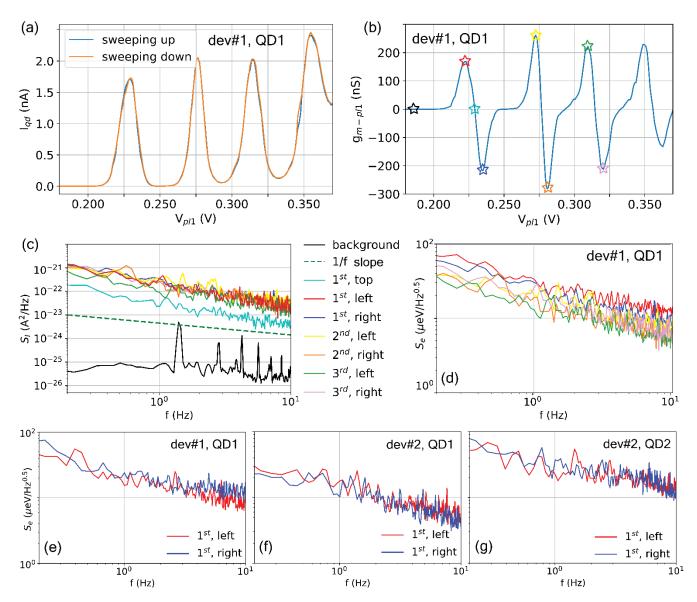

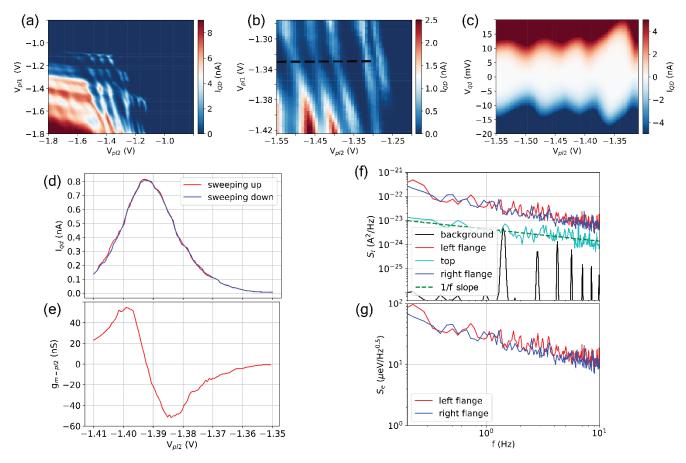

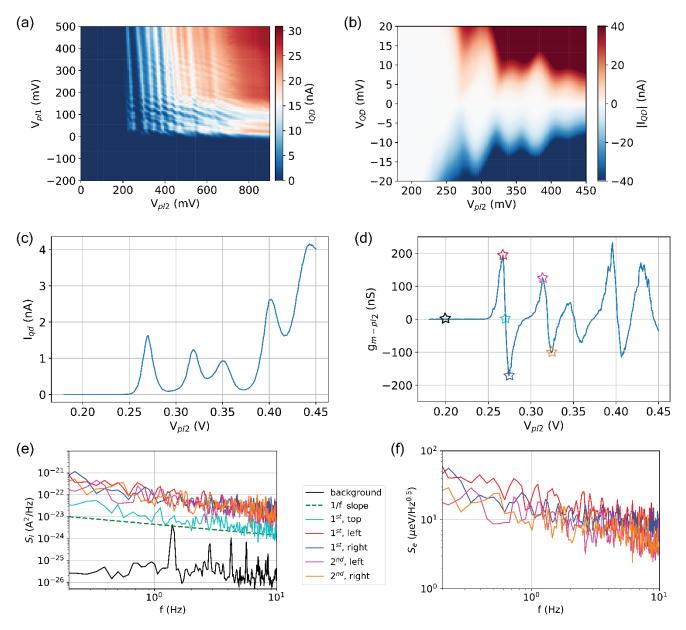

At the same time, the holy grail of silicon quantum computing is the integration of silicon spin qubits together with onchip cryo-CMOS auxiliary electronics used to initialize, operate, read out qubits and perform quantum error correction at > 1 K where the thermal budget is much more relaxed (few W at the 4 K plate) compared to the cooling power available in the standard commercial dilution refrigerators at mK-temperatures (few tens of  $\mu$ W). Following the development of the so-called hot spin qubits **[15,16]**, several demonstrations of electron and hole Si spin qubits above 1 K were reported **[10,18,19]**. However, the reported hot qubit fidelities above 1 K were considerably lower, compared to the mK-operation. One of the identified reasons was the charge noise dependence, linearly or even exponentially increasing with temperature in silicon quantum dots depending, for example, on the uniformity of charge fluctuators' distribution near the QDs **[38,49]**. Thus, the hot quantum dot charge noise optimization is one of the main challenges for large-scale quantum computing based on hot qubits operated above 1 K. A horizontal cut of the Coulomb diamond dataset (dev#1, QD1) from the left panel of Fig. 2(e) is shown in Fig. 3(a). It was acquired at  $V_{QD} = 1$  mV. The absence of hysteresis upon sweeping up and down the plunger gate voltage is a characteristic of high-quality poly-Si gates. The numerical derivative of the current versus voltage dependence required to convert the measured low-frequency current noise to equivalent charge noise is shown in Fig. 3(b). Quantifying the low-frequency noise at 1 Hz on the flanks of Coulomb peak where the absolute value of transconductance is maximized is a common metric to benchmark quantum dot charge noise [11,38-41]. Since the variations in charge noise are expected for different Coulomb peaks as local charge defects can be activated, to test that the disorder and charge fluctuators are uniformly distributed across the device which should result in 1/f dependence of  $S_e(f)$ , we performed charge noise measurements for the first three resolved Coulomb peaks.

In Fig. 3(c), the current noise power spectral density (PSD)  $S_I(f)$  curves are shown for the  $V_{pl2}$  set to the Coulomb blockade regime (background), on the top of the 1<sup>st</sup> Coulomb peak, and on the left and right flanks of the first three Coulomb peaks. The PSD curves on the flanks of several Coulomb peaks follow the 1/*f* slope, pointing toward uniformly distributed charge traps. On the flanks of the Coulomb peaks (unlike the top of the Coulomb peak), due to the local extremums in transconductance  $g_{m-pl2}$ , quantum dot chemical potential fluctuations dominate the current noise [39]. The described charge noise measurement technique can be correctly applied when the variation of quantum dot potential is much smaller than the Coulomb peak width, which is the case for the datasets presented in this article.

The charge noise  $S_e(f)$  dependence for the first three Coulomb peaks is shown in Fig. 3(d). The  $S_e(f)$  data for 1<sup>st</sup> Coulomb peak yielded 27  $\mu eV/\sqrt{Hz}$  at 1 Hz for QD1 of dev#1.  $S_e(f)$  was calculated as  $\frac{a^2 \times S_I}{g_{m-pl2}^2}$  [39], where transconductance is  $g_{m-pl2} = dI_{QD}/dV_{pl2}$  and lever arm  $\alpha$  (given by quantum dot capacitance normalized by total capacitance [36]) calculated from the slopes of Coulomb peaks [36,42]. To avoid overestimating  $g_m$ , numerical smoothing was applied after numerical derivation using Savitzky-Golay filtering; the raw and filtered  $g_m$  data are shown in Extended Data Fig. 5. Then, as we fill up the quantum dot with the 2<sup>nd</sup> and 3<sup>rd</sup> electrons, the charge noise becomes smaller. The latter is expected due to the partial screening of the charge traps as more electrons are added to the quantum dot [50] and a decrease in gate-control efficiency which translates into a lower lever arm parameter [49]. Using the same technique, we measured the charge noise for QD2 of dev#1 and QD1-2 of dev#2, see Fig. 3(e) and (g). Across two different (nominally-identical) double quantum dots, we obtained a reasonable charge noise variability of  $S_e(1 \text{ Hz})$  between 15 and 27  $\mu eV/\sqrt{Hz}$  for the first resolved electron in 4 different quantum dots at 5.6 K.

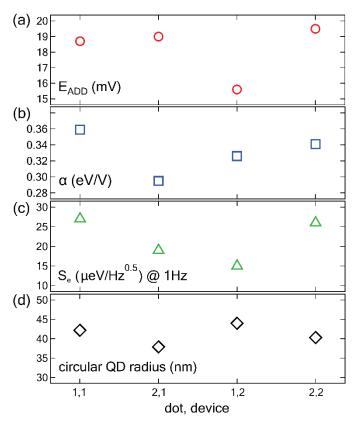

Approximating the QD system as a parallel-plate capacitor, the QD dimensions were estimated from the measured QD capacitance  $C_{QD}$  and the SiMOS geometry using  $r_{QD} = \sqrt{\frac{C_{QD} \times t_{SiO2}}{\varepsilon_0 \times \varepsilon_{SiO2}}}$ , where  $t_{SiO2}$  is the gate oxide thickness (20 nm), the dielectric constant of gate oxide material is  $\varepsilon_{SiO2} = 3.9$ ,  $\varepsilon_0$  is the vacuum permittivity and  $C_{QD} = E_{add}/(\alpha \times e)$ . To estimate  $C_{QD}$ , we used the addition energy and the lever arm of the first resolved electrons.

Let us now focus on the electron QD variability across dev#1 and dev#2, each featuring two QDs. The addition energy, lever arm, low-frequency charge noise, and QD radius for the first resolved electrons are shown in Fig. 4. The average addition energy of 18 meV, lever arm of 0.33 eV/V,  $S_e(1 \text{ Hz}) = 22 \,\mu eV / \sqrt{Hz}$ , and circular QD radius of 41 nm were obtained. We also measured a hole DQD (D[43]) at T = 5.6 K using  $V_{BACK} = 0$  V in the few-hole regime using the same double-quantum dot geometry as electron DQD devices #1 and #2, see Extended Data Fig. 6. For the hole DQD device we found  $E_{add} = 19 \text{ mV}$ , lever arm of 0.23 eV/V, and the two-dimensional circular quantum dot radius of 33.5 nm, comparable to the lithographically

defined quantum dot area, see Fig. 4(d). We measured the hole quantum dot charge noise  $S_e(1 \text{ Hz}) = 28 \frac{\mu eV}{\sqrt{Hz}}$  in the few-hole regime, comparable to the noise measured for our electron quantum dots. The similarity in charge noise for electron and hole QDs was also expected based on the same 4 mV/dec subthreshold swing values (translating into 1.5 meV band tails below  $E_c$  and  $E_v$ ) observed for the n- and p-MOSFETs made in the same fabrication process as QD devices.

Assuming a linear scaling of charge noise with temperature as it was previously reported in Si/SiGe QDs [38], we estimate the charge noise  $S_e$  (1 Hz) for the first electrons and holes to become 0.4 and 0.5  $\mu eV/\sqrt{Hz}$  respectively at 100 mK which is a typical electron temperature in well-designed and filtered spin qubit dilution cryostats. The linear scaling is a rather conservative approximation as depending on, for example, the fluctuators' local distribution, an exponential increase of charge noise with temperature can be expected as was observed for silicon-nanowire-based SiMOS QDs [49]. Moreover, the small size of SiMOS quantum dots of a few tens of nanometer results in avoidable variation in charge noise for nominally identical quantum dots. Our approximated low-frequency SiMOS hole quantum dot charge noise at 100 mK is comparable to the lowest noise hole semiconductor quantum dot charge noise  $S_e(1 \text{ Hz}) = 0.62 \ \mu eV/\sqrt{Hz}$  reported for Ge/SiGe heterostructure QDs with  $\alpha = 0.1 \text{ eV/V}$  at mK temperature [41]. It is instructive to compare our charge noise results for electron quantum dots beyond industrially manufactured FinFET-based SiMOS QDs reported in ref. [11]. The state-of-the-art <sup>28</sup>Si/SiGe electron quantum dots with  $\alpha = 0.12 \text{ eV/V}$  were characterized in the few-electron regime between 0.1 K and 4 K, yielding  $S_e(1 \text{ Hz})$  of 2 and 12  $\mu eV/\sqrt{Hz}$  respectively [38].

While there is room for further improvements to reduce QD charge noise in our devices by optimizing the gate stack and patterning, let's comment on why our (estimated) SiMOS QD charge noise results approach the state-of the-art of Si/SiGe and Ge/SiGe quantum dots at sub-1 K temperatures. The recently demonstrated foundry-grade hole and electron spin qubits used the advanced fabrication process with a high-k metal gate (HKMG) with either high-k oxide and metal gate [9,11] or just a metal gate in the gate stack [10]. The HKMG process introduced into commercial silicon technologies in 2007, is now routinely used in almost all modern advanced CMOS transistors. Importantly, solutions like high-k oxide HfO<sub>2</sub> and TiN metal in the gate stack that allowed for classical transistors scaling down were chosen to make qubits in [9-11]. However, it is known that having both metal gates (instead of doped Poly-Si) and high-k oxide in the gate stack reduces transistors' mobility and results in higher 1/f noise (e.g. [33,51] and references therein). Thus, we envision the foundry-grade wafer-scale planar or FinFET (nanowire) SiMOS spin qubits to reach the performance of the best Si/SiGe spin qubit devices made in the academic cleanrooms when the Si transistor fabrication processes invented in the 1990s, e.g., using SiO<sub>2</sub> gate oxide and doped Poly-Si gate and avoiding having TiN, HfO<sub>2</sub>, and SiN in the proximity of the quantum-dot-based qubits, are adapted for advanced qubit manufacturing. Indeed, another recent demonstration of SiMOS spin qubits on 300 mm wafers with  $S_e(1 Hz) = 3.6 \, \mu eV/\sqrt{Hz}$  measured at a base temperature of 8 mK that used Poly-Si/SiO<sub>2</sub>/Si MOS stack strongly supports the "all-silicon" gate-stack approach [52].

# Quantum dots and cryo-CMOS at 300 mK

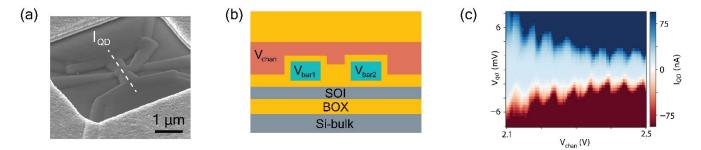

To validate the quantum dot and cryo-CMOS operation at T < 1 K, we cooled down an 8-channel MUX fabricated on the same wafer. This test MUX chip had single electron QD device geometries. Both the ultra-low-power, quasi-dissipationless cryo-CMOS logic functionality and confinement of quantum dots were observed, thus validating the developed hybrid quantum-dot CMOS process. The Coulomb data together with the single QD device layout are given in Extended Data Fig. 7.

## Quantum dot variability and large-scale characterization

While even the best optimized advanced short-channel ( $L_g < 100$ nm) transistor commercial CMOS technologies feature threshold voltage variability of the order of 10 - 100 mV,  $V_{TH}$ -variability becomes more pronounced at low temperatures where, for example, the thermally activated transport in the subthreshold region is greatly suppressed. Thus, the cryogenic  $V_{TH}$ variability is expected to be larger than at 300 K [51,53]. Since  $V_{TH}$  is defined by the gate metal work function, channel doping, built-in electrostatic potential, short-channel effects, and other parameters that challenge circuit designers trying to design reliable cryo-CMOS electronics [14], the situation with the QD's  $V_{TH}$  expected for the first electrons is also far from being trivial. However, electrostatically defined quantum dots, unlike donor-based quantum dots (e.g. [42,48]), are expected to have  $V_{TH}$  of the first electrons relatively close to the  $V_{TH}$  of transistors fabricated in the same process. It is not unexpected to have quantum dot's threshold voltage (i.e., the gate voltages required to load the first electron or hole) variability of a few hundred mV [11,54]. Here, we observe that both electron and hole QD's  $V_{TH}$  are closely following n- and p-MOSFET threshold voltages, indicating the quantum dots were shaped upon the gate-tuned energy level approaching  $E_c$  and  $E_v$ . This is further supported by the estimated electron and hole QD sizes being close to the lithographically defined QD area.

Although we report the in-depth analysis of only a few QD devices, we verified that the gates could be swept at rates between 1-10 kHz, thus enabling fast large-scale acquisition of stability diagrams by applying saw-tooth pulses and performing 1D or 2D buffer acquisition. The sweeping rate was not limited by cryo-CMOS circuitry where only capacitance from the IN & OUT analog switches impacts the measurement bandwidth, estimated to be > 1 MHz for the current realization of transmission gate switches (the frequency bandwidth can be extended beyond 100 MHz by replacing the current transmission gate switch design by an  $1x1 \ \mu m^2$  n-MOSFET connected to the DUTs from both ends), but having the high-impedance device connected by ~ 100 cm-long coaxial cable to the room temperature transimpedance amplifier, which resulted in the RC damping.

#### **Conclusions and Outlook**

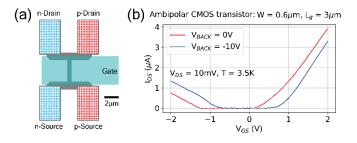

We demonstrated a hybrid quantum-dot CMOS circuit, where a quasi-dissipationless cryo-CMOS multiplexer is monolithically integrated with single and double electron and hole quantum dots. These quantum dots have unprecedently low electron and hole charge noise at 5.6 K comparable to the state of the art of Si/SiGe heterostructures quantum dots for which the best spin qubit fidelities have been reported. We correlated the ultra-low charge noise with the lowest measured cryogenic subthreshold swings of conventional n- and p-MOSFETs, and hence very small disorder-induced tails at the edges of conductance and valence bands in the Si channel. Our results suggest that the CMOS process with doped Poly-Si/SiO<sub>2</sub>/Si MOS stack, commonly used for transistor manufacturing until the early 2000s, when the HKMG process became a semiconductor industry standard, is a very promising technology for spin qubits. We also validated the cryogenic operation of ambipolar CMOS transistors in this Article - ambipolar DQDs were already reported in ref. [26]. Both were fabricated on the same wafer as the cryo-MUX devices.

Given the absence of the static power dissipation (down to sub-1 K temperatures), the cryo-MUXes studied in this Article can be utilized in such variability and reliability analysis that relies on the measurements of millions of nominally identical quantum dot devices. Following the recent progress in the computer-assisted automated characterization of quantum dot devices [55-58], with large-scale realization of our MUXes and application of machine learning auto-tuning and the statistical analysis of basic quantum dot and qubit features (such as addition energy, lever arm parameter, charge noise, spin blockade conditions [42] among others) can be an important enabler in scalable silicon-quantum-dot-based computing.

Integration of the hybrid quantum-dot CMOS circuit technology (by monolithic or heterogeneous means) with other cryogenic devices and microsystems can lead to extended functionalities and speed up the deployment of quantum technologies. For example, solid-state refrigerators utilizing Si-based micro-fabrication could cool the most temperature-sensitive parts of the integrated microsystem to sub-1 K temperatures [59,60] whilst others remain above 1 K, thus simplifying the overall system infrastructure. The read-out of semiconductor qubits can also benefit from integration. Here we envision integration (e.g. by flip-chip) of high-quality HEMTs (high-electron-mobility-transistors) with minimal parasitic capacitances to enable fast and flexible read-out with MHz bandwidth [61-63] without the need of the complex implementation of radio-frequency reflectometry circuitry [16,64,65].

Finally, it is important to note that it is not yet settled whether electron or hole spin qubits hold better potential for largescale silicon quantum computing. Beyond conventional silicon quantum-dot qubit devices based on either electron or hole spins [7,16], the great flexibility in building circuits with ambipolar MOSFETs hosting holes or electrons depending on the gate polarization was recently demonstrated [26,66-68], see also Supplementary Fig. 11. Hybrid ambipolar or separate n- and ptype quantum-dot devices interfaced with CMOS circuits including ultra-low power cryogenic multiplexing can enable fair statistical benchmarking of the single hole and electron spin qubits. Here, electron spins would be driven either through electron-dipole spin resonance (EDSR) [69] or electron spin resonance [70], and hole spins (which have strong spin-orbit coupling in Si) directly through EDSR by applying high-frequency microwave signals to the plunger gate [9,10].

#### **Methods**

**Fabrication.** The devices were fabricated on 150 mm silicon-on-insulator (SOI) wafers with a customized CMOS process in VTT's Micronova cleanroom facilities. The process consisted of 8 UV and 3 e-beam lithography layers. The SOI layer was thinned down to 35 nm by thermal oxidation and oxide stripping and patterned to form the nanowires. A 20 nm thermal SiO2 was grown to provide the insulator between the silicon nanowires and first gate layer. This step reduced the Si layer to its final thickness of 24 nm. The first and second polycrystalline silicon gate layers (gate-1 and gate-2 levels) have thicknesses 50 nm and 80 nm and were degenerately doped with low-energy phosphorous ion implantation. The 35 nm thick SiO2 dielectric layer between the polysilicon gate layers was grown by low-pressure chemical vapor deposition (LPCVD). Openings through the deposited dielectrics were etched on the source/drain regions of the SOI and phosphorous (n-type) or boron (p-type) implantation was used to dope these regions. A 250 nm thick SiO2 was deposited with LPCVD and the wafers were heated to 950 C to activate the dopants and anneal the dielectrics. Contact holes for all three layers were etched with subsequent dry and wet etching processes. Finally, the metallization layer consisting of 25 nm TiW and 250 nm AlSi was deposited and patterned, and the wafers were treated with a forming gas anneal passivation.

Design of cryo-CMOS. First, NMOS and PMOS transistors with different gate lengths and channel widths were characterized at room temperature from several test wafers. Next, using the transistor compact modeling based on room temperature data and Cadence simulations were performed to validate the cryogenic-temperature-aware CMOS logic and switch operation. Although the design did not account for the cryogenic transistors characteristics, it was anticipated that the threshold voltages would more to more positive and negative values for NMOS and PMOS transistors, respectively, and the off-current of transistors will zero due to the suppression of the thermionic current below the threshold voltage at low temperatures. Finally, the MUX chip was mounted onto a microcontroller board with PCB shielding (standard JLCC84 package). The MUXes embedding 64 and 96 devices were tested at room temperature using a digital oscilloscope (MS0-X 2024A) by pulsing address voltage lines with up to 50 Hz repetition rate. The selectivity of different devices was thus confirmed.

**Cryogenic setups and instrumentation.** The 5.6 K measurements were performed in a cryo-free refrigerator (Optistat by Oxford instruments). The 5.6 K setup did not feature any low-frequency cryogenic filtering, but only the intrinsic low-pass cut-off of resistive coaxial cables ( $f_{cut-off}$  between 50 and 100 MHz) used for DC biasing. The DC voltages were supplied using commercial off-shelf digital-to-analog converters (Keysight 34951) and auxiliary voltage output channels of Zurich Instrument's Lock-in (mlfi model). PSD noise measurement parameters were 916Hz sampling rate, 16384 points, 10 averages, frequency bandwidth limited to 150 Hz due to the built-in low-pass filtering of the transimpedance amplifier. A home-made voltage divider by 100 and first-order low-pass filter with  $f_{cut-off} = 211$  Hz was used to apply source-drain bias. Gate and CMOS logic voltages were filtered with home-made low-pass filters

with  $f_{\text{cut-off}} < 1$  kHz. Device current was measured with a commercial low-noise transimpedance amplifier FEMTO DDPCA-300 and a commercial digital multimeter. The current noise measurements were performed by feeding the output of the transimpedance amplifier into the lock-in voltage input followed by FFT processing using mlfi lock-in's built-in spectrum analyzer. The measurements at 2.5 K and 300 mK were performed using a cryo-free version of Oxford Instrument's Heliox with a base temperature of 300 mK. There, the same DAC and lock-in were used to provide DC voltages, and same transimpedance amplifier followed by a commercial digital multimeter was used for measuring current. The Heliox setup featured cryogenic low-pass filtering that resulted in  $f_{\text{cut-off}}$  of few kHz. The ambipolar transistor was measured in a cryogenic probe station with a base temperature of 3.5 K using a parameter analyzer's SMUs with the noise floor of approximately 10 nA.

# Acknowledgements

We would like to thank the VTT's operators and process engineers for supporting the fabrication in the OtaNano Micronova cleanroom facilities. We gratefully acknowledge the financial support from the European Union's Horizon 2020 research and innovation programme under Grant Agreement Nos. 688539 (http://mosquito.eu) and 766853 (http://www.efined-h2020.eu/), the Academy of Finland project QuMOS (project numbers 288907 and 287768), ETHEC (No. 322580), CRYOPOC (No. 350325) and Center of Excellence program project (No 312294). We also acknowledge funding from Business Finland through Quantum Technology Industrial (QuTI) project no. 128291.

#### References

[1] Montanaro, A. "Quantum algorithms: an overview," Npj Quantum Information 2, 15023 (2016).

[2] Terhal, B.M. "Quantum error correction for quantum memories," Review of Modern Physics 87, 307 (2015).

[3] Fowler, A.G., Mariantoni, M., Martinis, J.M., & Cleland, A.N. "Surface codes: Towards practical large-scale quantum computation," Physical Review A **86**, 032324 (2012).

[4] Kane, B.E. "A silicon-based nuclear spin quantum computer," Nature 393, 133-137 (1998)

[5] Loss, D. & Divincenzo, D.P. "Quantum computation with quantum dots," Physical Review A 57, 120-126 (1998).

[6] DiVincenzo, D.P. "The Physical Implementation of Quantum Computation," Fortschritte der Physik 48 (9-11): 771-783 (2000)

[7] Chatterjee, A., Stevenson, P., De Franceschi, S., Morello, A., de Leon N.P. & Kuemmeth F. "Semiconductor qubits in practice," Nature Reviews Physics **3**, 157–177 (2021).

[8] Petta, J.R., Johnson, A.C., Taylor, J.M., Laird, E.A., Yacoby, A., Lukin, M.D., Marcus, C.M., Hanson, M.P. & Gossard, A.C. "Coherent manipulation of coupled electron spins in semiconductor quantum dots," Science **309**, 2180–2184 (2005).

[9] Maurand, R., Jehl, X., Kotekar-Patil, D., Corna, A., Bohuslavskyi, H., Laviéville, R., Hutin, L., Barraud, S., Vinet, M., Sanquer M. & De Franceschi, S. "A CMOS silicon spin qubit," Nature Communications **7**, 13575 (2016).

[10] Camenzind, L.C., Geyer, S., Fuhrer, A., Warburton, R.J., Zumbühl, D.M. & Kuhlmann A.V. "A hole spin qubit in a fin field-effect transistor above 4 Kelvin," Nature Electronics 5, 178–183 (2022).

[11] Zwerver, A.M.J., Krähenmann, T., Watson, T.F., Lampert, L., George, H.C., Pillarisetty, R., Bojarski, S.A., Amin, P., Amitonov, S.V., Boter, J.M.,

Caudillo, R., Correas-Serrano, D., Dehollain, J.P., Droulers, G., Henry, E.M., Kotlyar, R., Lodari, M., Lüthi, F., Michalak, D.J., Mueller, B.K., Neyens, S., Roberts, J., Samkharadze, N., Zheng, G., Zietz, O.K., Scappucci, G., Veldhorst, M., Vandersypen L.M.K. & Clarke J.S. "Qubits made by advanced semiconductor manufacturing," Nature Electronics **5**, 184–190 (2022).

[12] Veldhorst, M., Hwang, J.C.C., Yang, C.H., Leenstra, A.W., de Ronde, B., Dehollain, J.P., Muhonen, J.T., Hudson, F.E., Itoh, K.M., Morello, A. & Dzurak, A.S. "An addressable quantum dot qubit with fault-tolerant control-fidelity," Nature Nanotechnology **9**, 981–985 (2014).

[13] Veldhorst, M., Yang, C.H., Hwang, J.C.C., Huang, W., Dehollain, J.P., Muhonen, J.T., Simmons, S., Laucht, A., Hudson, F.E., Itoh, K.M., Morello, A. & Dzurak, A.S. "A two-qubit logic gate in silicon," Nature 526, 410–414 (2015).

[14] Charbon, E., Sebastiano, F., Vladimirescu, A., Homulle, H., Visser, S., Song, L. & Incandela, R.M. "Cryo-cmos for quantum computing," 2016 IEEE International Electron Devices Meeting (IEDM), pp. 13.5.1–13.5.4 (2016).

[15] Vandersypen, L.M.K., Bluhm, H., Clarke, J.S., Dzurak, A.S., Ishihara, R., Morello, A., Reilly, D.J., Schreiber L.R., & Veldhorst, M. "Interfacing spin qubits in quantum dots and donors—hot, dense, and coherent," Npj Quantum Information **3**(1), 1–10 (2017).

[16] Gonzalez-Zalba, M.F., de Franceschi, S., Charbon, E., Meunier, T., Vinet M. & Dzurak, A.S. "Scaling silicon-based quantum computing using CMOS technology," Nature Electronics 4, 872–884 (2021).

[17] Xue, X., Patra, B., van Dijk, J.P.G., Samkharadze, N., Subramanian, S., Corna, A., Paquelet Wuetz, B., Jeon, C., Sheikh, F., Juarez-Hernandez, E., Perez Esparza, B., Rampurawala, H., Carlton, B., Ravikumar, S., Nieva, C., Kim, S., Lee, H.-J., Sammak, A., Scappucci, G., Veldhorst, M., Sebastiano, F., Babaie, M., Pellerano, S., Charbon, E. & Vandersypen, L.M.K. "CMOS-based cryogenic control of silicon quantum circuits," Nature **593**, 205–210 (2021)

[18] Yang, C.H., Leon, R.C.C., Hwang, J.C.C., Saraiva, A., Tanttu, T., Huang, W., Camirand Lemyre, J., Chan, K.W., Tan, K.Y., Hudson, F.E., Itoh, K.M., Morello, A., Pioro-Ladrière, M., Laucht A., & Dzurak, A.S. "Operation of a silicon quantum processor unit cell above one kelvin," Nature **580**, 350–354 (2020).

[19] Petit, L., Eenink, H.G.J., Russ, M., Lawrie, W.I.L., Hendrickx, N.W., Philips, S.G.J., Clarke, J.S., Vandersypen L.M.K. & Veldhorst M. "Universal quantum logic in hot silicon qubits," Nature **580**, 355–359 (2020).

[20] Pauka, S.J., Das, K., Hornibrook, J.M., Gardner, G.C., Manfra, M.J., Cassidy, M.C. & Reilly, D.J. "Characterizing Quantum Devices at Scale with Custom Cryo-CMOS," Physical Review Applied **13**, 054072 (2020).

[21] Ruffino, R., Yang, T.-Y., Michniewicz, J., Peng, Y., Charbon E., & Gonzalez-Zalba, M.F. "A cryo-CMOS chip that integrates silicon quantum dots and multiplexed dispersive readout electronics," Nature Electronics **5**, 53–59 (2022).

[22] Potočnik, A., Brebels, S., Verjauw, J., Acharya, R., Grill, A., Wan, D., Mongillo, M., Li, R., Ivanov, T., Van Winckel, S., Mohiyaddin, F.A., Govoreanu, B., Craninckx, J. and Radu, I.P. "Millikelvin temperature cryo-CMOS multiplexer for scalable quantum device characterization," Quantum Science and Technology **7**, 015004 (2022)

[23] Paquelet Wuetz, B., Bavdaz, P.L., Yeoh, L.A., Schouten, R., van der Does, H., Tiggelman, M., Sabbagh, D., Sammak, A., Almudever, C.G., Sebastiano, F., Clarke, J.S., Veldhorst, M. & Scappucci, G. "Multiplexed quantum transport using commercial off-the-shelf CMOS at sub-kelvin temperatures," npj Quantum Information 6, 43 (2020)

[24] Schaal, S., Rossi, A., Ciriano-Tejel, V.N., Yang, T.-Y., Barraud, S., Morton J.J.L. & Gonzalez-Zalba, M.F. "Dynamic random access architecture for radio-frequency readout of quantum devices," Nature Electronics 2, 236–242 (2019)

[25] Patra, B., Van Dijk, J. P. G., Corna, A., Xue, X., Samkharadze, N., Sammak, A., Scappucci, G., Veldhorst, M., Vandersypen, L. M. K., Babaie, M., Sebastiano, F., Charbon, E. & Pellerano, S. "A Scalable Cryo-CMOS 2-to-20GHz Digitally Intensive Controller for 4×32 Frequency Multiplexed Spin Qubits/Transmons in 22nm FinFET Technology for Quantum Computers," 2020 IEEE International Solid State Circuits Conference (ISSCC), pp. 304-306 (2020).

[26] Duan, J., Lehtinen, J.S., Fogarty, M.A., Schaal, S., Lam, M.M.L., Ronzani, A., Shchepetov, A., Koppinen, P., Prunnila, M., Gonzalez-Zalba, F. & Morton J.J.L. "Dispersive readout of reconfigurable ambipolar quantum dots in a silicon-on-insulator nanowire," Applied Physics Letters **118**, 164002 (2021).

[27] Bohuslavskyi, H., Barraud, S., Barral, V., Cassé, M., Le Guevel, L., Hutin, L., Bertrand, B., Crippa, A., Jehl, X., Pillonnet, G., Jansen, A.G.M., Arnaud, F., Galy, P., Maurand, R., De Franceschi, S., Sanquer, M. & Vinet, M. "Cryogenic Characterization of 28-nm FD-SOI Ring Oscillators With Energy Efficiency Optimization," IEEE Transactions on Electron Devices 65, 9 (2018).

[28] Lundstrom, M. "Fundamentals of nanotransistors (Lessons from Nanoscience: A Lecture Notes Series, Vol. 6)," Singapore, World Scientific Co. Pte. Ltd., (2018).

[29] Bohuslavskyi, H., Jansen, A.G.M., Barraud, S., Barral, V., Cassé, M., Le Guevel, L., Jehl, X., Hutin, L., Bertrand, B., Billiot, G., Pillonnet, G., Arnaud, F., Galy, P., De Franceschi, S., Vinet, M. & Sanquer, M. "Cryogenic Subthreshold Swing Saturation in FD-SOI MOSFETs Described With Band Broadening," IEEE Electron Device Letters 40, 5, 784-787 (2019).

[30] Lifshitz, I.M., "The energy spectrum of disordered systems," Advances in Physics 13, 52, 483-536 (1964).

[31] Mott, N. "The mobility edge since 1967," Journal of Physics C: Solid State Physics 20, 3075 (1987).

[32] Guevel, L.L, Billiot, G., Jehl, X., De Franceschi, S., Zurita, M., Thonnart, Y., Vinet, M., Sanquer, M., Maurand, R., Jansen, A.G.M. & Pillonnet, G.

"19.2 A 110mK 295µW 28nm FDSOI CMOS Quantum Integrated Circuit with a 2.8GHz Excitation and nA Current Sensing of an On-Chip Double

Quantum Dot, "2020 IEEE International Solid- State Circuits Conference - (ISSCC), pp. 306-308, (2020).

[33] Theodorou, C. & Ghibaudo, G. "Noise and Fluctuations in Fully Depleted Silicon-on-Insulator MOSFETs," In: Grasser, T. (eds) Noise in Nanoscale Semiconductor Devices. Springer, Cham. (2020).

[34] Saraiva, A., Lim, W.H., Yang, C.H., Escott, C.C., Laucht, A. & Dzurak, A.S. "Materials for Silicon Quantum Dots and their Impact on Electron Spin Qubits," Advanced Functional Materials 2022, 32, 2105488.

[35] Hu, C. "Modern semiconductor devices for integrated circuits," 6th ed., Upper Saddle River, N.J., Prentice Hall, (2010)

[36] van der Wiel, W.G., De Franceschi, S., Elzerman, J.M., Fujisawa, T., Tarucha, S. & Kouwenhoven, L.P. "Electron transport through double quantum dots," Reviews of Modern Physics **75**, 1 (2002).

[37] Yoneda, J., Takeda, K., Otsuka, T., Nakajima, T., Delbecq, M.R., Allison, G., Honda, T., Kodera, T., Oda, S., Hoshi, Y., Usami, N., Itoh K.M. & Tarucha S. "A quantum-dot spin qubit with coherence limited by charge noise and fidelity higher than 99.9%," Nature Nanotechnology 13, 102–106 (2018).

[38] Petit, L., Boter, J.M., Eenink, H.G.J., Droulers, G., Tagliaferri, M.L.V., Li, R., Franke, D.P., Singh, K.J., Clarke, J.S., Schouten, R.N., Dobrovitski, V.V., Vandersypen, L.M.K. & Veldhorstet M. "Spin Lifetime and Charge Noise in Hot Silicon Quantum Dot Qubits," Physical Review Letters 121, 076801 (2018).

[39] Connors, E.J., Nelson, J.J., Qiao, H., Edge, L.F. & Nichol, J.M. "Low-frequency charge noise in Si/SiGe quantum dots," Physical Review B 100, 165305 (2019).

[40] Chanrion, E., Niegemann, D.J., Bertrand, B., Spence, C., Jadot, B., Li, J., Mortemousque, P.-A., Hutin, L., Maurand, R., Jehl, X., Sanquer, M., De Franceschi, S., Bäuerle, C., Balestro, F., Niquet, Y.-M., Vinet, M., Meunier, T. & Urdampilleta, M. "Charge Detection in an Array of CMOS Quantum Dots," Physical Review Applied **14**, 024066 (2020).

[41] Lodari, M., Hendrickx, N.W., Lawrie, W.I.L., Hsiao, T.-K., Vandersypen, L.M.K., Sammak, A., Veldhorst, M. & Scappucci, G. "Low percolation density and charge noise with holes in germanium," Materials for Quantum Technology **1**, 011002 (2021).

[42] Zwanenburg, F.A., Dzurak, A.S., Morello, A., Simmons, M.Y., Hollenberg, L.C.L., Klimeck, G., Rogge, S., Coppersmith, S.N. & Eriksson, M.A. "Silicon quantum electronics," Review of Modern Physics **85**, 961 (2013).

[43] Nadj-Perge, S., Frolov, S.M., Bakkers, E.P.A.M. & Kouwenhoven, L.P. "Spin-orbit qubit in a semiconductor nanowire," Nature 468, 1084 (2010).

[44] van den Berg, J.W.G., Nadj-Perge, S., Pribiag, V.S., Plissard, S.R., Bakkers, E.P.A.M., Frolov, S.M. & Kouwenhoven, L.P. "Fast Spin-Orbit Qubit in an Indium Antimonide Nanowire," Physical Review Letters **110**, 066806 (2013).

[45] Bylander, B., Gustavsson, S., Yan, F., Yoshihara, F., Harrabi, K., George Fitch, F., Cory, D.G., Nakamura, Y., Tsai, J.-S. & Oliver, W.D. "Noise spectroscopy through dynamical decoupling with a superconducting flux qubit," Nature Physics **7**, 565–570 (2011).

[46] Noiri, A., Takeda, K., Nakajima, T., Kobayashi, T., Sammak, A., Scappucci G., & Tarucha S. "Fast universal quantum gate above the fault-tolerance threshold in silicon," Nature **601**, 338–342 (2022).

[47] Xue, X., Russ, M., Samkharadze, N., Undseth, B., Sammak, A., Scappucci, G., & Vandersypen, L.M.K. "Quantum logic with spin qubits crossing the surface code threshold," Nature **601**, 343–347 (2022).

[48] Mądzik, M.T., Asaad, S., Youssry, A., Joecker, B., Rudinger, K.M., Nielsen, E., Young, K. C., Proctor, T.J., Baczewski, A.D., Laucht, A., Schmitt, V., Hudson, F.E., Itoh, K.M., Jakob, A.M., Johnson, B.C., Jamieson, D.N., Dzurak, A.S., Ferrie, C., Blume-Kohout R. & Morello A. "Precision tomography of a three-qubit donor quantum processor in silicon," Nature **601**, 348–353 (2022).

[49] Spence, C., "Charge noise and spin in single-electron silicon CMOS quantum dots," PhD thesis, Université Grenoble Alpes (2021).

[50] Hofheinz, M. "Coulomb blockade in silicon nanowire MOSFETs," PhD thesis, Université Joseph Fourier (2006).

[51] Bohuslavskyi, H., "Cryogenic electronics and quantum dots on silicon-on-insulator for quantum computing," PhD thesis, Université Grenoble Alpes (2018).

[52] Stuyck, N.I.D., Li, R., Godfrin, C., Elsayed, A., Kubicek, S., Jussot, J., Chan, B.T., Mohiyaddin, F.A., Shehata, M., Simion, G., Canvel, Y., Goux, L., Heyns, M., Govoreanu, B. & Radu, I.P. "Uniform Spin Qubit Devices with Tunable Coupling in an All-Silicon 300 mm Integrated Process," 2021 Symposium on VLSI Circuits, pp. 1-2 (2021).

[53] Paz, B.C., Le Guevel, L., Cassé, M., Billiot, G., Pillonnet, G., Jansen, A.G.M., Maurand, R., Haendler, S., Juge, A., Vincent, E., Galy, P., Ghibaudo, G., Vinet, M., de Franceschi, S., Meunier, T. & Gaillard, F. "Variability Evaluation of 28nm FD-SOI Technology at Cryogenic Temperatures down to 100mK for Quantum Computing," 2020 IEEE Symposium on VLSI Technology, pp. 1-2 (2020).

[54] Ansaloni, F., Chatterjee, A., Bohuslavskyi, H., Bertrand, B., Hutin, L., Vinet, M. & Kuemmeth, F. "Single-electron operations in a foundry-fabricated array of quantum dots," Nature Communications **11**, 6399 (2020).

[55] Ares N., "Machine learning as an enabler of qubit scalability," Nature Reviews Materials 6, 870-871 (2021).

[56] Chatterjee, A., Ansaloni, F., Rasmussen, T., Brovang, B., Federico Fedele, Bohuslavskyi, H., Krause, O. & Kuemmeth F. "Autonomous estimation of high-dimensional Coulomb diamonds from sparse measurements," arXiv:2108.10656 (2021).

[57] Kalantre, S.S., Zwolak, J.P., Ragole, S., Wu, X., Zimmerman, N.M., Stewart Jr., M.D. & Taylor, J.M. "Machine learning techniques for state recognition and auto-tuning in quantum dots," npj Quantum Information 5, 6 (2019).

[58] Baart, T.A., Eendebak, P.T., Reichl, C., Wegscheider, W. & Vandersypen, L.M.K. "Computer-automated tuning of semiconductor double quantum dots into the single-electron regime," Applied Physics Letters **108**, 213104 (2016).

[59] Muhonen, J.T., Meschke, M. & Pekola, J.P. "Micrometre-scale refrigerators," Reports on Progress in Physics 75, 046501 (2012).

[60] Mykkänen E., Lehtinen J.S., Grönberg, L., Shchepetov, A., Timofeev, A.V., Gunnarsson, D., Kemppinen, A., Manninen, A.J. & Prunnila, M.

"Thermionic junction devices utilizing phonon blocking," Science Advances 6, 15, eaax9191 (2020).

[61] Tracy, L.A., Reno, J.L., Fallahi, S. & Manfra, M.J. "Integrated high electron mobility transistors in GaAs/AlGaAs heterostructures for amplification at sub-Kelvin temperatures," Applied Physics Letters **114**, 053104 (2019).

[62] Blumoff, J.Z., Pan, A.S., Keating, T.E., Andrews, R.W., Barnes, D. W., Brecht, T.L., Croke, E.T., Euliss, L.E., Fast, J.A., Jackson, C.A.C., Jones, A.M., Kerckhoff, J., Lanza, R.K., Raach, K., Thomas, B.J., Velunta, R., Weinstein, A.J., Ladd, T.D., Eng, K., Borselli, M.G., Hunter, A.T. & Rakher, M.T., "Fast and high-fidelity state preparation and measurement in triple-quantum-dot spin qubits," arXiv:2112.09801 (2022).

[63] Mills, A.R., Guinn, C.R., Feldman, M.M., Sigillito, A.J., Gullans, M.J., Rakher, M., Kerckhoff, J., Jackson, C.A.C. & Petta, J.R., "High fidelity state preparation, quantum control, and readout of an isotopically enriched silicon spin qubit," arXiv:2204.09551 (2022).

[64] Noiri, A., Takeda, K., Yoneda, J., Nakajima, T., Kodera, T. & Tarucha, T. "Radio-Frequency-Detected Fast Charge Sensing in Undoped Silicon Quantum Dots," Nano Letters **20**, 947–952 (2020).

[65] Liu, Y.-Y., Philips, S.G.J., Orona, L.A., Samkharadze, N., McJunkin, T., MacQuarrie, E.R., Eriksson, M.A., Vandersypen, L.M.K. & Yacoby,

A. "Radio-Frequency Reflectometry in Silicon-Based Quantum Dots," Physical Review Applied 16, 014057 (2021).

[66] Betz, A.C. Gonzalez-Zalba, M.F., Podd, G., & Ferguson, A.J. "Ambipolar quantum dots in intrinsic silicon," Applied Physics Letters **105**, 153113 (2014).

[67] Müller, F., Konstantaras, G., Spruijtenburg, P.-C., van der Wiel, W.G., & Zwanenburg, F.A. "Electron–Hole Confinement Symmetry in Silicon Quantum Dots," Nano Letters **15**, 5336 (2015).

[68] Kuhlmann, A.V., Deshpande, V., Camenzind, L. C., Zumbühl, D. M. & Fuhrer, A. "Ambipolar quantum dots in undoped silicon fin field-effect transistors," Applied Physics Letters **113**, 122107 (2018).

[69] Pioro-Ladrière, M., Obata, T., Tokura, Y., Shin, Y.-S., Kubo, T., Yoshida, K., Taniyama, T. & Tarucha, S. "Electrically driven single-electron spin resonance in a slanting Zeeman field," Nature Physics **4**, 776–779 (2008).

[70] Dehollain, J.P, Pla, J.J., Siew, E., Tan, K.Y., Dzurak, A.S. & Morello, A. "Nanoscale broadband transmission lines for spin qubit control," Nanotechnology **24**, 015202 (2013).

**Fig. 1** | **Multiplexer, CMOS logic, and quantum dots. (a)** Optical micrograph of the 64-channel multiplexer. (b) Tilted SEM image over cryo-CMOS logic. (c) A Tilted SEM image over three double quantum dot devices. (d) Cross-section of a MOSFET used in the logic. The cut is taken along the dashed red line in (a). (e) Tilted SEM over one of the DQD devices taken around the yellow dashed rectangle in (f). A schematic showing how the analog switch selection of a MUX-embedded device operates

is given in (**f**). The transmission gate switches (see the inset in (f)) are connected from both sides of the selected device. Address line voltages turn on the pair of analog switches that connect to the selected device. (**g**) MUX schematic. It consists of 6 address lines (A0 – A5) that are supplied to the decoder. The output of the decoder allows selecting one of the devices represented by black and orange rectangles that correspond to test nanowire and quantum dot devices respectively. The cryo-CMOS logic is powered by  $V_{DD}$  and its operation can be adjusted with a global back-gate  $V_{BACK}$ .

**Fig. 2** | **Tunable few-electron double quantum dots**. Two nominally identical electron DQD devices #1 and #2 measured at  $V_{BACK} = -10V$  and T = 5.6 K. (a) A sketch showing the cross-section of the DQD device shown in Fig. 1(e). (b-c) Stability diagrams of coupled electron DQDs measured on dev#1 and dev#2. (d) Tunability of the DQD (dev#1). By increasing  $V_{bar1}$  that controls the interdot tunnel coupling, from left to right: a weakly coupled DQD becomes a strongly coupled DQD. (e-f) Coulomb diamonds of QD1 and QD2 of dev#1 and #2 measured by filling up QD2 and QD1, respectively with a dozen of electrons, and using the latter as an extended reservoir to probe QD1 and QD2. The black dashed lines indicate the first detected electrons.

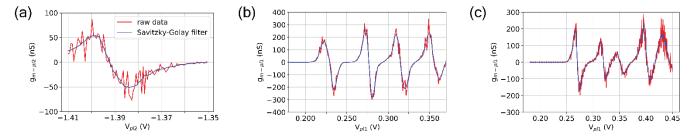

**Fig. 3** | **Low-frequency charge noise in electron quantum dots. (a)** Coulomb peaks of QD1, dev#1 measured at  $V_{DS} = 1 \text{ mV}$  and T = 5.6 K corresponding to a vertical cut of the 2D Coulomb map shown in Fig. 3(e). Note the absence of hysteresis demonstrated by sweeping up and down  $V_{pl1}$ . (b) Numerical derivative  $dI_{DS}/dV_{pl1}$  of data in (a). The colored star markers are used to highlight the gate-voltage points at which noise measurements were performed. (c) Low-frequency current noise measured using the  $V_{pl1}$  points indicated with the star markers of the same color in (b). (d) Charge noise of the first three detected electrons calculated from (c), measured at the flanks of Coulomb peaks. (e-g) The same charge noise experiment was performed for QD2 of dev#1 and both QDs of dev#2.

Fig. 4 | Variability of electron quantum dots at 5.6 K. (a) Addition energy, (b) lever arm parameter, (c), low-frequency charge noise extracted at f = 1 Hz, and (d) the estimated two-dimensional circuital QD radius are shown for four characterized quantum dots from electron DQD dev#1 and dev#2 described in the main text. The data are given for the 1<sup>st</sup> detected electron. Note the low variability within the same DQD device and between two nominally identical DQD devices. The circular quantum dot radiuses are close to the lithographically defined quantum dot dimensions given by  $L_g \times W = 50 \times 70$  nm.

#### **EXTENDED DATA FIGURES**

**Extended data Fig. 1** | **Quasi-dissipationless operation of cryo-CMOS MUX. (a)** An optical micrograph showing n- and p-type nanowires (D[0] and D[1]) connected to the IN and OUT pairs of analog switches are shown. **(b)** The nanowire geometry devices D[0] and D[1]. **(c)** The device selectivity depending on the  $V_{add}$  is shown: with  $V_{add} = \{A0 = 0 \text{ V}, A1 = 0 \text{ V}, A2 = 0 \text{ V}, A3 = 0 \text{ V}, A4 = 0 \text{ V}, A5 = 0 \text{ V}\}$ , D[0] is selected, and  $V_{add} = \{0, 0, 0, 0, 0, 0, X\}$  connects D[1]. *X* voltage value (logical one) is typically above 1 V, and it defines the gate voltage of n- and p-type MOSFETs forming IN and OUT analog switches. For the selectivity to work, the switch's MOSFETs need to be in strong inversion corresponding to the saturation regime. **(d)** The current through the p-type nanowire at  $V_{BACK} = 0 \text{ V}$ . The device is selected when  $V_{DD}$  (also used for MOSFET gate-biasing in the decoder logic) approaches the threshold voltage of p-MOSFET since n-MOSFET threshold voltage is much lower due to the n++ doping of the Poly-Si gate. **(e)** Following the  $V_{TH}$  tunability of n- and p-MOSFET (see Extended Data Fig. 2), the CMOS logic operation improves by making  $V_{TH}$  of n- and p-MOSFET more symmetrical, thus allowing for CMOS logic to operate at  $V_{DD}$  down to 0.7 V. (**f-g**) CMOS logic leakage current  $I_{cryoCMOS}$  measured between  $V_{DD}$  and ground. Measured  $I_{cryoCMOS}$  is below the noise floor of the setup for both cases of  $V_{BACK} = 0 \text{ V}$  and -10 V.

**Extended data Fig. 2** | **Back-gate tunability of cryo-CMOS MOSFETs.**  $I_{DS}(V_{GS})$  of n- and p-type MOSFETs. The device and measurement parameters are given in the inset. The threshold voltage  $V_{TH}$ -tunability with  $V_{BACK}$  is shown.

**Extended data Fig. 3** | **Transfer characteristics and subthreshold swing.** (a) Gate stack of a standard n- and p-type MOSFETs, used in cryo-CMOS MUXes. (b) Gate stack of reconfigurable quantum dot – FET devices (D[56] and D[57] from

the MUX#2). All transfer characteristic  $I_{DS}(V_{GS})$  shown in (b,c,e,f) were measured at  $V_{BACK} = 0$  V and T = 5.6 K. The dashed black line in (b,c,e,f) indicates the saturation of the room temperature transimpedance amplifier. (**b**-c)  $I_{DS}(V_{GS})$  of n- and p-type MOSFETs with  $L_g = 4 \mu$ m used in the cryo-CMOS logic and analog switches are shown. The  $I_{DS}(V_{GS})$  of the n- and p-type QD-FET shown in (**e**-f) were measured by sweeping three gates in series (each measuring 50 nm) at the same time. The barrier gates  $V_{bar1}$  and  $V_{bar2}$  at the gate-2 level were swept using a coefficient of  $\theta = V_{p11} \times 2.75$  to account for the gate oxide difference: 55 nm for the gate-2 and 20nm for the gate-1 level. The source-drain bias was set to  $|V_{DS}| = 24$  mV, above the characteristic addition energy of the first detected hole and electrons in quantum dots described in the main text. (**g**) Subthreshold swing as a function of source-drain current measured for long- and short-channel MOSFETs in the linear regime at small  $V_{DS}$ . The black dashed line indicates the record *SS* value of 4 mV/dec that all tested transistors show in the weak inversion. The non-constant SS as  $I_{DS}$  increases is explained by the presence of localized states near  $E_c$  and  $E_v$  having an exponential distribution. The exponential tail of localized states (different from the band-broadening tail of 1.5 meV that provides mobile states and is discussed in the main text) affects the gate efficiency and has a typical extension of 5 – 10 meV below  $E_c$  and  $E_v$  which corresponds to an increase in density of interface traps of 10-30% near  $E_c$  and  $E_v$ , see refs. [29,51] for more details. Also, *SS*( $I_{DS}$ ) curves are affected when  $I_{DS}$  is close to 100 nA because this was the saturation current level of the room temperature TIA with gain (transimpedance) of  $10^8$  V/A.

**Extended data Fig. 4** | **CMOS logic down to 300 mK temperature. (a)** Left: standard CMOS inverter (NOT-gate) topology is shown. Right: an optical micrograph of the NOT-gate. (b) Characterization of the inverter at 2.5 and 300 mK as a function of  $V_{DD}$ . Top panel: no difference between the  $V_{OUT}(V_{IN})$  swing behavior of the CMOS inverter logic between 2.5 K and 300 mK temperatures, as expected from the cryogenic saturation of subthreshold swing and mobility. Lower panel: the effect of

negative back-gate biasing making  $V_{\text{TH}}$  of n- and p-MOSFET more symmetrical, the swing curves moved to the right. The perfect matching condition is usually achieved by choosing different channel widths for n- and p-MOSFET and boosting p-MOSFET mobility. This corresponds to the swing centered at  $V_{\text{IN}} = V_{\text{DD}}/2$ . (c) The voltage gain  $dV_{\text{OUT}}/dV_{\text{IN}}$  of the inverter obtained by taking numerical derivatives of data in (b). The sharp and narrow gain peak together with gain reaching 30 is a typical feature of commercial analog circuits based realized with advanced CMOS technologies.

**Extended data Fig. 5** | **numerical filtering of**  $g_m$  for  $S_e$  calculations. Raw data (red) from numerical derivatives of quantum dot current with respect to the plunger gate voltage and numerically post-filtered (blue)  $g_{m-pl2(pl1)}$  are shown for (a) hole quantum dot shown in Extended Data Fig. 6, (b) electron quantum dot shown in Fig. 3, and (c) electron quantum dot shown in Supplementary Fig. 10.

Extended data Fig. 6 | Hole double quantum dot and its charge noise. (a) A stability diagram of a hole DQD device with the same geometry as the electron DQD devices discussed in Fig. 2 and 3 in the main text.  $V_{QD} = 3 \text{ mV}$ ,  $V_{chan} = -3.7 \text{ V}$  were used to acquire (a). (b) A zoom over (a) in the regime where Coulomb diamonds of QD2 were measured. (c) Coulomb diamonds in the few-hole regime measured along the dashed black line in (b). (d) The Coulomb blockade peak which corresponds to the vertical cut of (c) (taken at  $V_{DS} = 4 \text{ mV}$ ) is shown. The lever arm measured from the slopes of the Coulomb diamonds is 0.23 eV/V. (e) The numerical derivative of data in (d) is shown. (f) Low-frequency current noise measured in Coulomb blockade, on top of the coulomb peak shown in (d), and at the left and right flanks where  $g_{m-pl2}$  reaches local extremums. (g) Charge noise calculated from data in (f). The hole quantum dot charge noise at 1Hz is 28  $\mu eV/\sqrt{Hz}$ .

**Extended data Fig. 7** | **Electron quantum dots at 300 mK. (a)** A tilted SEM image of the test device measured in a simpler 8-channel MUX with the same circuit topology for the decoder and switches as in 64-channel MUXes #1 and #2 discussed in the main text. (b) The cross-section schematic of the device (a). (c) Coarse-resolution stability diagram showing Coulomb diamonds of the test device measured at 300 mK. Both, quantum dot devices and cryo-CMOS function at sub-Kelvin temperatures.

# SUPPLEMENTARY MATERIAL

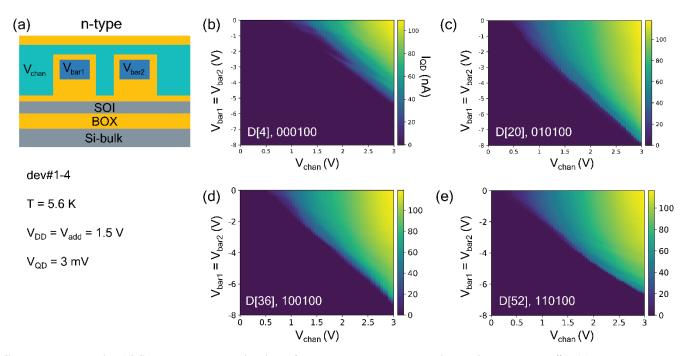

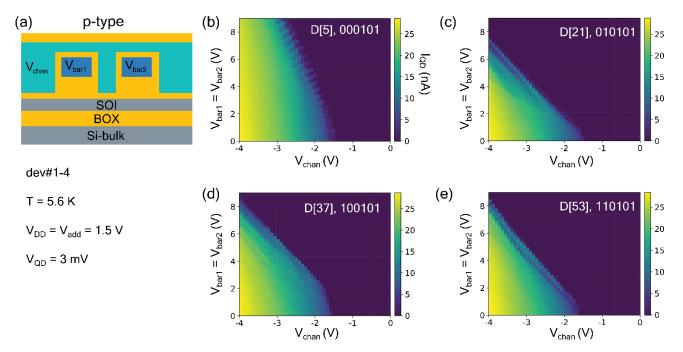

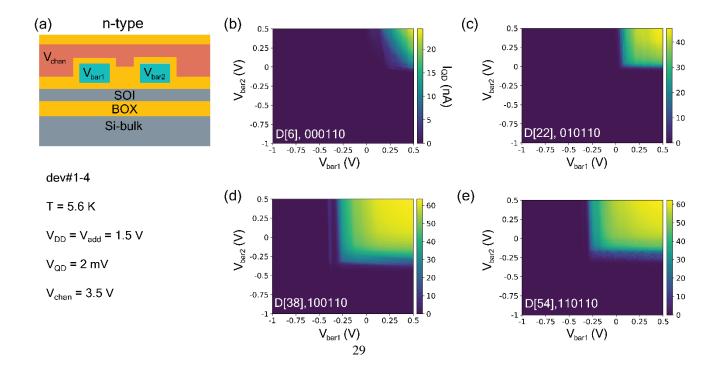

Supplementary Fig. 1 | Scalable characterization of n-type quantum dot devices using MUX dev#1. (a) (Top) A crosssection schematic of the electron (n-type) quantum dot device geometry with  $G_{chan}$  at gate-1 level, and  $G_{bar1}$  and  $G_{bar2}$  at gate-2 level. (Bottom) The parameters used to measure stability diagrams presented in this figure. (b-e) Measured coarse-resolution stability diagrams for 4 nominally identical devices.

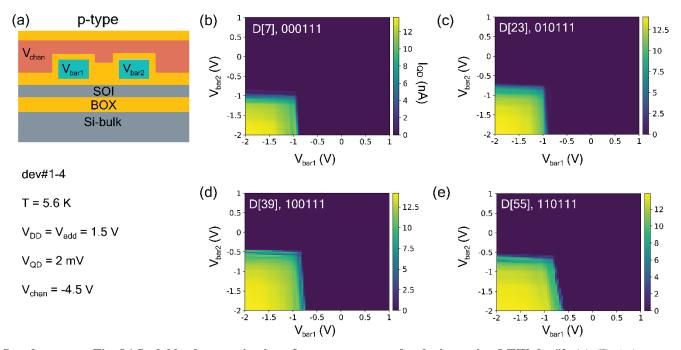

Supplementary Fig. 2 | Scalable characterization of p-type quantum dot devices using MUX dev#1. (a) (Top) A crosssection schematic of the hole (p-type) quantum dot device geometry with  $G_{chan}$  at gate-1 level, and  $G_{bar1}$  and  $G_{bar2}$  at gate-2 level. (Bottom) The parameters used to measure stability diagrams presented in this figure. (b-e) Measured coarse-resolution stability diagrams for 4 nominally identical devices.

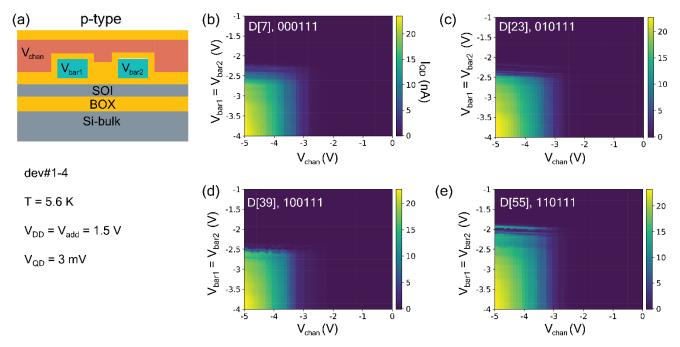

Supplementary Fig. 3 | Scalable characterization of p-type quantum dot devices using MUX dev#1. (a) (Top) A crosssection schematic of the hole quantum dot device geometry with  $G_{chan}$  at gate-2 level and  $G_{bar1}$  and  $G_{bar2}$  at gate-1 level. (Bottom) The parameters used to measure stability diagrams presented in this figure. (b-e) Measured coarse-resolution stability diagrams for 4 nominally identical devices.

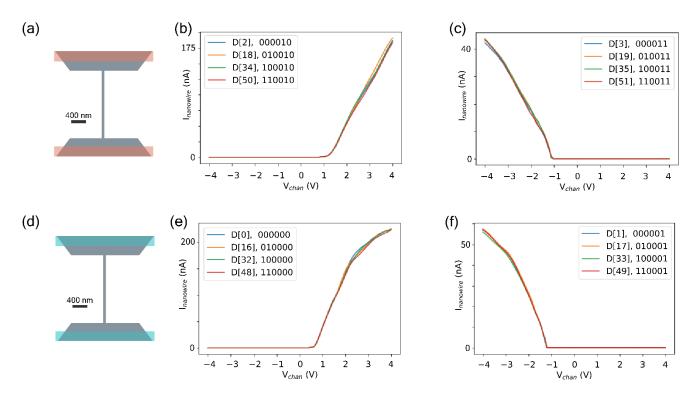

Supplementary Fig. 4 | Scalable characterization of nanowires using MUX dev#2. Sketches of the nanowire geometry (topview) with  $G_{chan}$  at gate-2 level (a) and gate-1 level (b). Nanowire current as a function of  $V_{chan}$  acquired for 4 nominally identical devices are shown in (b-c), acquired for n- and p-type nanowires with  $G_{chan}$  at gate-2, respectively. The characterization identical to (b-c) but for the nanowire devices with  $G_{chan}$  at gate-1 level is shown in (e-f). All the data were acquired at  $V_{BACK} = 0$  V and T = 5.6 K.

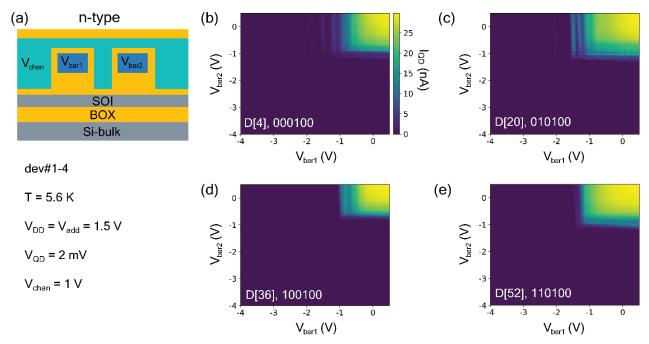

Supplementary Fig. 5 | Scalable characterization of n-type quantum dot devices using MUX dev#2. (a) (Top) A crosssection schematic of the electron quantum dot device geometry with  $G_{chan}$  at gate-1 level, and  $G_{bar1}$  and  $G_{bar2}$  at gate-2 level. (Bottom) The parameters used to measure stability diagrams presented in this figure. (b-e) Measured coarse-resolution stability diagrams for 4 nominally identical devices.

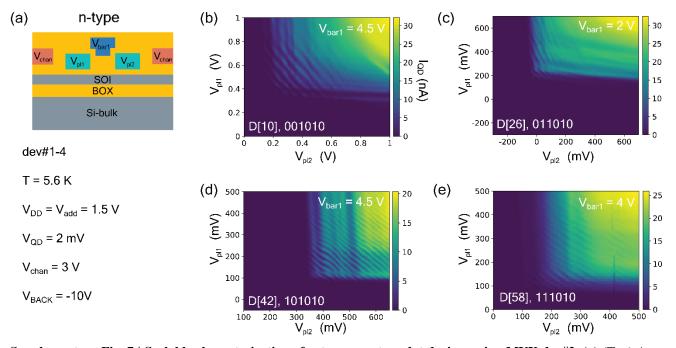

Supplementary Fig. 6 | Scalable characterization of n-type quantum dot devices using MUX dev#2. (a) (Top) A crosssection schematic of the electron quantum dot device geometry with  $G_{chan}$  at gate-2 level, and  $G_{bar1}$  and  $G_{bar2}$  at gate-1 level. (Bottom) the parameters used to measure stability diagrams presented in this figure. (b-e) Measured coarse-resolution stability diagrams for 4 nominally identical devices.

Supplementary Fig. 7 | Scalable characterization of n-type quantum dot devices using MUX dev#2. (a) (Top) A crosssection schematic of the electron double quantum dot device geometry with  $G_{chan}$  and  $G_{bar1}$  at gate-2 level and  $G_{pl1}$  and  $G_{pl2}$  at gate-1 level. (Bottom) the parameters used to measure stability diagrams presented in this figure. (b-e) Measured (plungerplunger) stability diagrams for 4 nominally identical devices. The inner barrier voltage  $V_{bar1}$  was configured for each device individually to have strongly coupled DQDs. D[42] and D[58] were studied in detail and are discussed in the main text.

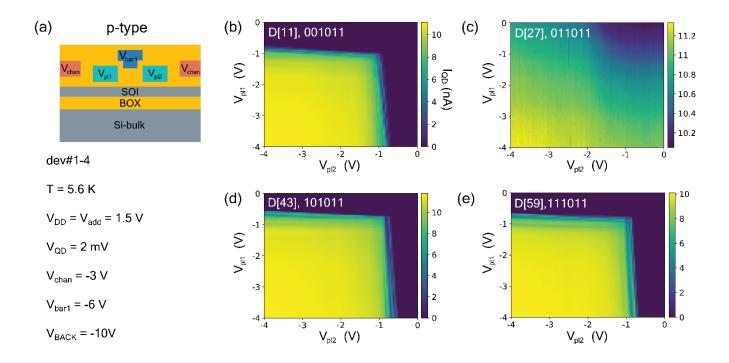

Supplementary Fig. 8 | Scalable characterization of p-type quantum dot devices using MUX dev#2. (a) (Top) A crosssection schematic of the hole quantum dot geometry with  $G_{chan}$  at gate-2 level and  $G_{bar1}$  and  $G_{bar2}$  at gate-1 level. (Bottom) the parameters used to measure stability diagrams presented in this figure. (b-e) Measured coarse-resolution stability (barrierbarrier) diagrams for 4 nominally identical devices.

Supplementary Fig. 9 | Scalable characterization of p-type quantum dot devices using MUX dev#2. (a) (Top) A crosssection schematic of the hole double quantum dot device geometry with  $G_{chan}$  and  $G_{bar1}$  at gate-2 level and  $G_{pl1}$  and  $G_{pl2}$  at gate-1 level. (Bottom) The parameters used to measure stability diagrams shown in this figure. (b-e) Measured coarse-resolution (plunger-plunger) stability diagrams for 4 nominally identical devices. D[43] tuned to have coupled QDs was discussed in the main text.

Supplementary Fig. 10 | Electron DQD (dev#1) at  $V_{BACK} = 0V$ . (a) Stability diagram of the electron DQD dev#1 discussed in the main text is shown. It was acquired at 5.6 K with  $V_{BACK} = 0$  V and  $V_{bar1} = 3.5$  V. (b) Coulomb diamonds corresponding to (dev#1, QD2) at  $V_{BACK} = 0$  V and  $V_{bar1} = 2$  V are shown. (c) Horizontal cut of (b) at  $V_{DS} = 1$ mV. (d) Numerical derivative of (c). (e) Low-frequency current noise measured for several  $V_{p12}$  points according to the start markers in (d). (f) Charge noise

calculated based on (e). It should be noted that unlike the PSD noise data shown in the main text which were averaged for several minutes each, here the noise was measured in the single shot-manner (1 average), so the measurements' standard deviation is higher as compared to data shown Fig. 3 in the main text.

Supplementary Fig. 11 | Ambipolar CMOS transistors. (a) Sketch showing the ambipolar CMOS MOSFET. The ambipolar MOSFET features two pairs of electron and hole Source/Drain connected to the ends of the planar device. The ambipolar devices were fabricated within the same run, on the same wafer as the cryo-MUX devices. (b) Transfer characteristics  $I_{DS}(V_{GS})$  of the ambipolar transistors measured at  $V_{BACK} = 0V$  and -10 V.