# An Isolated Gate Driver for Multi-Active Bridges with Soft Switching

Ferdinand Grimm, Pouya Kolahian, John Wood, Richard Bucknall and Mehdi Baghdadi

Abstract—The design of gate drivers is an important topic in power converter topologies that can help reduce switching losses and increase power density. Gate driving techniques that offer zero-voltage switching and/or zero current switching have recently been successfully proposed for different modular multilevel converters such as the cascaded H bridge. Previous papers on other multilevel converters such as the multi-active bridge, however, do not sufficiently assess the topics of gate driver design for this topology. This work presents a novel isolated gate driver architecture tailored to the multi-active bridge topology. Zero voltage switching is then achieved using two multi-winding transformers. The advantages of the proposed topology are not only a reduction of switching losses but also reduced component count. The topology is evaluated on a prototype using experimental results. It was shown using simulation and experiments that the proposed topology has a high efficiency while providing compact power packaging. Especially for converters with many levels, the proposed topology is therefore advantageous compared to existing solutions.

Index Terms—Zero voltage switching, auxiliary supply, gate driver, multi-active bridge

#### Nomenclature

- Second time derivative of x.First time derivative of x.

- A System matrix.

- b Input vector.

- x State-space variable.

- x<sup>ss</sup> Steady state of the state-space variable.

- $C_{

m DC}$  DC-link capacitance of the multi-active bridge circuit.

- $C_{\rm dc}$  DC-link capacitance of the gate driver.

- $C_{\rm DS}$  Drain-Source capacitance.

- $C_{\text{eq}}$  Equivalent gate-source capacitance of the multi-active bridge.

- $C_{\rm GS}$  Gate-Source capacitance.

- $i_m$  Magnetization current of the gate driver transformer.

- $i_{GS}$  Current charging the gate-source capacitance.

- $L_s$  Stray inductance of the gate driver transformer.

- $L_M$  Magnetization inductance of the multi-active bridge circuit.

- $L_m$  Magnetization inductance of the gate driver.

- M Number of modules of the multi-active bridge.

- N Turns number of the multi-active bridge circuit transformer windings.

- n Turns number of the gate driver transformer windings.

- Q Switch on the multi-active bridge circuit.

- q Switch on the gate driver.

- $R_c$  Conduction resistance of the gate driver.

- $R_{\rm eq}$  Equivalent resistance of the gate driver.

- $R_{\rm ON}$  ON-state resistance of the gate drive MOSFET.

- $S_i$  Signal that is applied to switch i.

- $t_{\rm fall}$  Timing constant.

- $t_{\rm high}$  Timing constant.

- $t_{\text{low}}$  Timing constant.

- $t_{\rm rise}$  Timing constant.

- $t_{\rm zero}$  Timing constant.

- $V_{\rm DC}$  DC-voltage of the multi-active bridge.

- $V_{\rm gd}$  Supply voltage of the gate driver.

- $V_{\rm GS}$  Voltage between the Gate and Source terminals on the

- multi-active bridge circuit.

- $V_{

m mid}$  Midpoint voltage of the multi-active bridge circuit.

- $V_{\rm S}$  Supply voltage of the multi-active bridge.

- $x_i$  i-th entry of the vector  $\mathbf{x}$ .

- GND Multi-active bridge reference voltage.

- gnd Gate driver reference voltage.

- u Input variable.

## I. INTRODUCTION

Recent advances in multi-winding transformer research have produced interesting novel approaches for power converters derived from the multi-winding transformer technology [1].

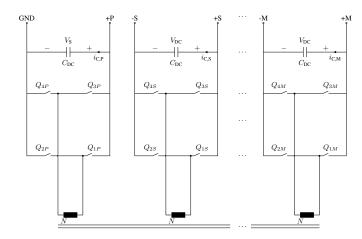

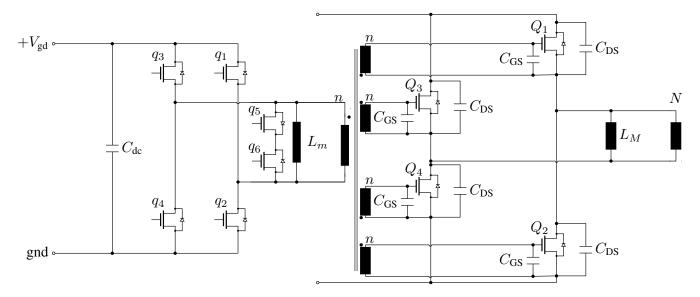

Fig. 1. Circuit diagram of the multi-active bridge converter with ideal switches. This DC/AC topology consists of M active bridges that are connected through a multi-winding transformer in the AC domain. If all the windings of the transformer share a single core, the DC-voltages of the circuit will be balanced. The conversion from DC to AC is achieved through the switching pattern of  $Q_1,\,Q_2,\,Q_3,\,$  and  $Q_4.$

A promising multi-winding transformer-based DC/DC topology is the multi-active bridge (MAB) [1]–[9]. The circuit diagram of a MAB converter is shown in Fig. 1. In [2], a more detailed introduction to MAB-based DC/DC converters is given. The MAB topology is a combination of many

active bridges connected magnetically through a multi-winding transformer [3]. Its advantage over regular cascaded H-bridgebased multilevel converters is the strong self-balancing which can be achieved by using a multi-winding transformer with a single core. In this way, all windings will be exposed to the same magnetic flux. If all windings also possess the same number of turns, the AC voltage in each active bridge will be similar which results in a balanced state. This solves the problem of the requirement of large DC/DC converters which significantly increases the power density of the converter. Over the past few years, several applications for MABs have been identified such as wireless charging [4], grid connections [5], and battery balancing [6]. Furthermore, the usage of the MAB has been proposed as a versatile solution for hybrid renewable energy systems [7], multilevel inverters [8] and energy routers [9].

Since the MAB is an AC-link-based topology, it requires constant switching at high frequencies to prevent its magnetics from going into saturation. For this reason, the reduction of switching losses in MAB-based topologies is of great importance. Over the past few decades, several approaches to quick and lossless gate-driving of MOSFET switches have been introduced [10]-[15]. Common state-of-the-art approaches include charge-pump [10] and bootstrap [11], [12] solutions. To reduce losses, [13] suggested saving the energy stored in the input capacitance of the MOSFET in an external resonant circuit. While those gate drivers rely on a half-bridge to generate the switching signal, an approach based on a class  $\Phi_2$ inverter consisting only of a single switch has been proposed in [14]. In addition to that, [15] proposed to isolate the switching signal from the power circuit by using a transformer to transfer the information about the desired switching state as shown in Fig. 2 (a). While those solutions have been proven to work well for driving a single MOSFET which is sufficient for simple circuits, more complex topologies might consist of more than one switch. A key question, therefore, is how these concepts can be generalized to drive more than one switch with a minimal increase in complexity of the driving circuit. Isolating the driving circuits from each other is important not only because it offers protection of the gate driver from faulty switches but also allows to safely connect one power supply to many switches which are placed at different voltage levels to a common reference voltage [16]-[20]. Therefore, based on the approach presented in [15], many solutions for isolated gate drivers have been introduced, [16]-[20]. For certain applications, such as half-bridges, some of the switches always will be opened in a mutually exclusive manner. In this case, all switches can be attached to the transformer isolation as a tertiary winding and the mutual exclusive switching can be implemented by different turn directions of the windings [16]. Furthermore, the concept has been extended to highpower switches, adding overcurrent protection and thermal protection in [17]. In the case of a multilevel converter, the gate driver concepts have to be further extended to drive not only a few but an arbitrarily large amount of switches. While the basic concept of gate driving remains similar, the transformer isolation now is realized with a multi-winding transformer such as the cascaded half-bridge [18]. In [19] several techniques to reduce the EMI for this configuration have been examined. Furthermore, an isolated gate driver for a different multilevel inverter concept, the solid-state transformer, has been introduced in [20].

While several approaches for the topology of power supplies of MABs have been proposed, the design of a transformerisolation-based power supply for gate drivers comes with several challenges [21]–[25]. One of these challenges is designing the transformer which starts with choosing the correct basic transformer geometry. While regular transformers, such as the toroidal transformer [21] have small parasitic capacitances, they are bulky and reduce the power density of the supply [21]. Planar transformers, on the other hand side, provide a high power density but larger parasitic capacitances [22]. Once the basic geometry has been chosen, its parameters can be optimized to obtain the best transformer tailored to the desired application [22], [23] and reduce the effects of parasitic elements. To reduce the parasitic capacitance, several techniques have been examined such as geometric optimization with the help of finite element analysis [22]. Alternatively, formulas to estimate the parasitic capacitance from the parameters of this geometry can be used as shown in [23]. It is moreover possible to supply other low-power components using the same multi-winding transformer as the gate driver [24]. This can be achieved by attaching more windings to the transformer. If different voltage levels are required, the number of turns can be varied for those cases [24]. In addition to the optimization of the transformer, system theoretic aspects such as the stability of the gate driver can be taken into account when designing the circuit to ensure safe and reliable operation [25].

Several solutions for zero voltage switching in MABs have been proposed in [26]–[28]. A resonant tank can be used to reduce the voltage oscillations within the circuit as shown in [26]. Furthermore, the resonant tank can be used to increase the balancing speed of the DC-voltages of the MAB which was presented for battery balancing in [27]. In [28], the authors derived soft-switching conditions for MABs and gave guidelines for the selection of a suitable operating point.

Although a variety of interesting concepts for power supplies for modular multilevel converters as well as resonant configurations for MABs has been presented in the literature, a combination of the two approaches, i.e. a power supply for MABs that allows lossless switching, is still subject to research.

In this paper, we propose an advanced isolated gate driver for MABs with a unique energy recovery technique that allows lossless switching of all transistors of the circuit. To store the energy of the parasitic capacitances of the switching in the MAB and the gate driver, two multi-winding transformers will be employed, one being part of the gate driver and the other being the regular MAB transformer that connects the modules. Contrary to the regular transformer isolation shown in Fig. 2 (a), the control part of the gate driver is entirely on the primary side of the multi-winding transformer which results in a centralized control approach, shown in Fig. 2 (b). In addition, the proposed gate driver is capable of ensuring synchronized switching of all modules.

The remainder of the paper is structured as follows: Section II

provides an overview of the proposed topology and its basic operating principle. In Section III, a state-space model and analysis of the proposed model are presented. Experiment results are given in Section IV and the conclusion follows in Section V.

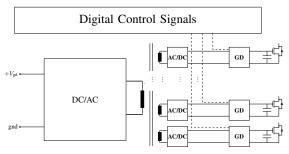

(a) Conventional Power Supply, see e.g [18].

(b) Proposed Gate Driver

Fig. 2. Overview of different isolated auxiliary supply concepts for MOSFET switches. Dashed lines show data signals from the controller. The conventional approach, shown in (a), generates an AC signal from the voltage supply which is then distributed to all MOSFETs using a multi-winding transformer. At the MOSFETs, the voltage is rectified and serves as a supply for the gate drivers connected to each MOSFET. The gate driver then generates the signals that are required to switch the MOSFET. The switching state is determined by a controller run e.g. on an FPGA. The FPGA communicates with each MOSFET directly. In the proposed approach, shown in (b), the voltage supply is converted to an AC signal as well. Similar to the conventional approach, the AC signal is then distributed to the MOSFETs using a multi-winding transformer. At the MOSFET however, the multi-winding transformer is directly connected to the gate and source terminals to enable the switching. Since there is no gate driver in between, the controller is directly connected to the primary side DC/AC part, switching all MOSFETs synchronously.

### II. TOPOLOGY OVERVIEW AND OPERATING PRINCIPLE

An overview of the overall design is shown in Fig. 2 (b). The switches in the MAB change their switching state when the gate-source capacitance is charged or discharged, for which an auxiliary power supply is used. A primary DC/AC converter topology is fed by the auxiliary power supply and determines whether the gate-source capacitors are charged or discharged. To synchronously charge or discharge all gate-source capacitances and ensure isolation of the switches from each other, a multi-winding transformer is used that transmits the power from the primary DC/AC converter circuit to all switches in the MAB. The goal is to minimize the power consumption of this circuit which is provided by the auxiliary supply.

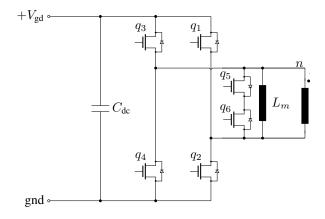

Fig. 3. Circuit diagram of a midpoint-clamped active bridge with MOSFET switches and primary winding. This topology represents an implementation of the DC/AC black box in Fig. 2 and will be used as basic gate driver topology in the following. The switches  $q_1, ..., q_6$  are low-power and controlled directly by the FPGA.

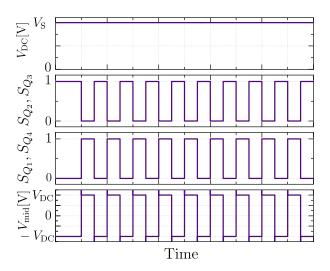

Fig. 4. The waveform of the AC-voltage of a MAB. To provide a stable DC-voltage shown in the top subfigure, the switches  $Q_1$  and  $Q_4$  must be switched alternating with  $Q_2$  and  $Q_3$  as depicted in the two middle subfigures which is the central requirement to the proposed gate driver. This results in the squarewave AC-voltage shown in the bottom subfigure under the assumption of an ideal high-voltage transformer. Phase shift control is not considered in this paper, thus every bridge uses the above switching pattern.

# A. Proposed topology

To properly drive the MOSFETs of an active bridge, the gate driver topology must be able to produce the following switching states:

- 1) a positive output voltage which indicates that the switches which are to be driven are closed

- 2) a negative output voltage which shows that the switches to be driven by the gate driver are open. In case there are other switches connected to the gate driver transformer with the opposite turns direction, those switches will be closed when the negative voltage is applied.

- 3) A third switching state that gives the possibility to save

Fig. 5. Connection of an active bridge with MOSFETs as switches to the proposed gate driver. The dot above the windings indicates winding directions. For all windings with no dot, the direction does not matter.  $L_M$  and  $L_m$  denote magnetizing inductances for the MAB and the gate driver transformer respectively. Gate drain capacitances of the MOSFETs are not shown. Small case indices imply that the quantity belongs to the gate driver while capitalized indices represent components of the main circuit. N and N represent the turns number of the MAB and gate driver transformers respectively.

the energy which is stored in the gate-source capacitance of the MOSFETs.

4) A switching state that sets the midpoint voltage to zero and allows energy exchange between the high power transformer and the drain-source capacitances of the MOSFETs to be switched to reduce switching losses.

Quantities that refer to the low-power gate driver will use small case letters while quantities that refer to the high-power MAB will be capitalized for the remainder of this paper. An example of a topology that satisfies those requirements is the clamped active bridge, shown in Fig. 3. Using the auxiliary supply  $V_{\rm gd}$  as well as the switches  $q_i$ ,  $i \in \{1,2,3,4,5,6\}$ , the following midpoint voltages can be created: If the switches  $q_2$  and  $q_3$  are closed the midpoint voltage will be positive. In case the switches  $q_1$  and  $q_4$  are closed, the midpoint voltage will be negative. Closing the switches  $q_5$  and  $q_6$  yields a zero midpoint voltage. Opening all switches gives a floating midpoint. An overview of the switching states can be seen in table I.

TABLE I

OVERVIEW OVER THE SWITCHING STATES OF THE GATE DRIVER AND ITS IMPLICATIONS TO THE MIDPOINT VOLTAGE

|          | $q_1$ | $q_2$ | $q_3$ | $q_4$ | $q_5$ | $q_6$ | $V_{ m mid}$       |

|----------|-------|-------|-------|-------|-------|-------|--------------------|

| High     | 0     | 1     | 1     | 0     | 0     | 0     | $+V_{\mathrm{gd}}$ |

| Low      | 1     | 0     | 0     | 1     | 0     | 0     | $-V_{\mathrm{gd}}$ |

| Zero     | 0     | 0     | 0     | 0     | 1     | 1     | 0                  |

| Floating | 0     | 0     | 0     | 0     | 0     | 0     | Varying            |

The goal is to use the gate driver topology to drive all switches of the MAB synchronously. To successfully drive all switches in the MAB, the gate driver needs to be able to access all switches in the MAB converter. This is achieved by connecting it to each of the switches with a multi-winding transformer. Each winding of the multi-winding transformer is connected to one MOSFET of the MAB. All switches of the MAB that are mutually exclusive (as seen in Fig. 4) must

furthermore have different turns directions in the secondary windings to ensure that they cannot be closed at the same time as shown in Fig. 5. To connect a MAB, other active bridges can be connected magnetically to the gate driver transformer in a similar way. Furthermore, the energy that is stored in the gate-source capacitors of the switches that are turned off can be transferred to the magnetization inductance  $L_m$  of the gate-driver transformer during the floating state which achieves lossless operation of the gate driver. During the zero states, the energy stored in the drain-source capacitors will be stored in the magnetization inductance  $L_M$  of the main circuit which results in the lossless operation of the MAB switches as well.

# B. Operating principle

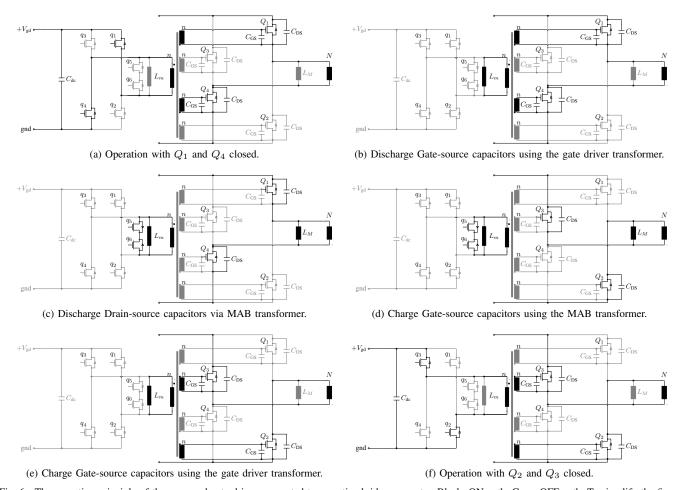

An overview of the operating principle during one switching can be seen in Figure 6. For this section, we assume that the switching frequency is high enough so that both transformers will not go into saturation. One operation cycle consists of 6 steps which will be given in the following:

- Step 1: In the beginning,  $Q_1$  and  $Q_4$  are closed, and their gate-source and drain-source capacitors are fully charged. The gate driver ensures this by keeping  $q_1$  and  $q_4$  closed which results in a voltage of  $+V_{\rm gd}$  at the transformer windings attached to  $Q_1$  and  $Q_4$  and  $-V_{\rm gd}$  at the transformer windings attached to  $Q_2$  and  $Q_3$ . This configuration is shown in Fig. 6 (a).

- Step 2: As soon as  $Q_1$  and  $Q_4$  should be opened, the gate driver opens  $q_1$  and  $q_4$  resulting in all gate driver switches being open and the midpoint voltage changing to floating. Since the voltage across the gate-driver magnetization inductance  $L_m$  is now not fixed by the gate driver anymore, it will start discharging the gate-source capacitors of  $Q_1$  and  $Q_4$ , storing the energy from those two capacitors. Fig. 6 (b) shows this configuration.

Fig. 6. The operating principle of the proposed gate driver connected to an active bridge converter. Black: ON-path, Gray: OFF-path. To simplify the figure, only one module of the MAB is shown. Starting from a regular operation with  $Q_1$  and  $Q_4$  closed shown in subfigure (a), the gate driver discharges all gate-source capacitances shown in subfigure (b) and drain-source capacitances (c) of the MAB by exchanging energy with the multi-winding transformer magnetizing inductances  $L_m$  and  $L_M$ . The energy exchange is triggered by changing the switching state of the gate driver. After that, first, the drain-source capacitors of  $Q_2$  and  $Q_3$  are charged as shown in subfigure (d) and then the gate-source capacitance (e). This again is achieved by changing the switching state of the gate driver. As soon as  $Q_2$  and  $Q_3$  are closed, normal operation continues as shown in subfigure (f). Switching back to  $Q_1$  and  $Q_4$  follows the same principle, in reverse order.

- Step 3: When the gate-source capacitors are fully discharged, the gate-driver changes to its zero state by closing  $q_5$  and  $q_6$ . This forces the midpoint voltage to zero and allows the drain-source capacitors of the gate driver to discharge through the main transformer's magnetization inductance  $L_M$  in a similar manner as the gate-source discharge in the previous step. This setup can be seen in Fig. 6 (c).

- Step 4: Once all capacitors of  $Q_1$  and  $Q_4$  are fully discharged, the drain-source capacitors of  $Q_2$  and  $Q_3$  are charged through the magnetization inductance of the MAB transformer. This step is shown in Fig. 6 (d).

- Step 5: As soon as the drain-source capacitors of  $Q_2$  and  $Q_3$  are fully charged, the gate driver midpoint switches  $q_5$  and  $q_6$  are opened again leaving the midpoint floating. This allows energy exchange between the magnetization inductance  $L_m$  and the gate-source capacitances of the MOSFETs to take place again. This time, however, the capacitors belonging to  $Q_1$  and  $Q_4$  will be charged negatively while the capacitors belonging to  $Q_2$  and  $Q_3$

- will be charged positively resulting in the switches  $Q_2$  and  $Q_3$  being closed. Fig. 6 (e) shows this step.

- Step 6: When  $Q_2$  and  $Q_3$  are closed, the corresponding gate-driver switches  $q_2$  and  $q_3$  will be closed as well to ensure that the midpoint voltage will stay constant and the switches will not open again. The final step is shown in Fig. 6 (f).

Switching  $Q_2$  and  $Q_3$  off and  $Q_1$  and  $Q_4$  on again follows a similar pattern, in reverse order. If the capacitors charge and discharge linearly, the switching losses of the MAB will be negligible if combined with the proposed gate driver. A hard-switching gate driver with the same auxiliary supply would yield losses of  $\frac{1}{2}C_{\rm GD}(2V_{\rm gd})^2$  for each of the 4M switches per switching action.

#### III. STATE-SPACE MODELLING AND ANALYSIS

In this section, a system model of the gate driver is derived to get a more detailed insight into its behavior. The purpose of the state-space model is to analyze the behavior of the system

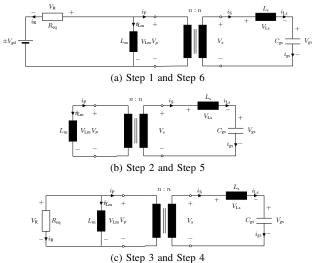

Fig. 7. Equivalent circuits of the proposed gate driver during one switching (e) period. The transformer is modeled with a primary winding and a single secondary winding representing all switches under the assumption that the windings are identical and perfectly synchronized. Each winding has an equivalent stray inductance  $L_s$  and the primary side furthermore has a magnetizing inductance  $L_m$  that models the behavior of the core. The equivalent resistance  $R_{\rm eq}$  represents the ON-state resistance of the switches of the and the winding resistance of the transformer. In the first and last Step, shown in (a), the auxiliary supply of the gate driver is used for the model as well. The difference in the topology in these Steps is implemented as a different sign for the voltage source. For Step 2 and Step 5 this voltage does not influence the behavior of the midpoint and is therefore removed as shown in (b). In (c) the supply is disconnected as well, however, the ON-state resistance on the primary side is taken into account. This represents the behavior during Step 3 and Step 4.

and derive design criteria for a prototype. The modeling is based on the following assumptions:

- 1) Negligible parasitic capacitances within the transformer.

- 2) All switches are synchronized.

- 3) All transformer windings are identical.

- Linear magnetization inductance, stray inductances, conduction losses, and Gate-source capacitances of the driven MOSFET.

- 5) 100% coupling of transformer windings.

- 6) The behavior of all circuit elements is independent of the frequency of the signals given to the gate driver.

A multi-active full-bridge converter consists of 4M highpower MOSFETs. Since all windings of the gate driver transformer share the same magnetic flux, the secondary AC voltages of each winding are identical. The second assumption together with the third assumption allows replacing the 4Msecondary windings attached to the gate-source capacitances  $C_{\rm GS}$  of the MAB with one single equivalent winding. Furthermore, it is assumed that each element has a linear resistance resulting in one equivalent resistance  $R_{\rm eq}$  for each Step, consisting of  $R_{ON}$ , the ON-state resistance of the gatedriver MOSFETs  $q_1, ..., q_6$  and  $R_c$  which is the conduction resistance of the multi-winding transformer. In addition to the equivalent capacitance, assuming negligible cross-coupling allows representing the multi-winding transformer as a single T-model shown in Fig. 7. To fully describe the system, a threedimensional state-space vector  $\mathbf{x}(t)$  is necessary, consisting of

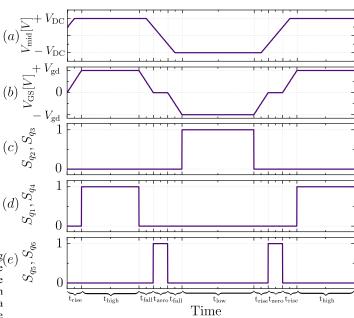

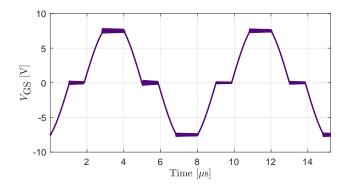

Fig. 8. The waveform of the gate-source voltage of the proposed gate driver together with the AC-voltage of the MAB. The resulting AC-voltage of the MAB is shown in (a). Below, in (b), is the midpoint voltage of the gate driver measured at the primary winding of the multi-winding transformer. The bottom three subfigures (c), (d), and (e) show the transients of the switching signals that are given to the gate driver switches  $q_1$ ,  $q_2$ ,  $q_3$ ,  $q_4$ ,  $q_5$  and  $q_6$  shown in Fig. 3. The timings are assumed to be ideal which results in a voltage waveform without discontinuous jumps as seen in the experiment results.

Fig. 9. Simulation results of the gate driver midpoint waveform with correctly timed modulator. The timing parameters in this condition are  $t_{\rm rise}=1000$  ns,  $t_{\rm zero}=800$  ns and  $f_{\rm s}=125$  kHz. The simulation is modeled after the prototype presented in section 5.

the gate-source current  $i_{\rm gs}(t)$ , the gate-source voltage  $V_{\rm gs}(t)$ , as well as the magnetization current  $i_{\rm Lm}(t)$ :

$$\mathbf{x}(t) = \begin{bmatrix} i_{gs}(t) & V_{gs}(t) & i_{Lm}(t) \end{bmatrix}^T \in \mathbb{R}^3. \tag{1}$$

Furthermore, the input u(t) of the gate driver shall be defined as the gate-driver supply voltage, which is changing for different different steps,

$$u(t) = \begin{cases} -V_{\rm gd}, & \text{Step 1} \\ 0, & \text{Step 2, Step 3, Step 4, Step 5} \\ +V_{\rm gd}, & \text{Step 6.} \end{cases}$$

(2)

While the switches of the MAB are ON, the gate driver is represented by the equivalent circuit shown in Fig. 7 (a). Using Kirchhoff's equations, the dynamics of the system can be derived as

$$\dot{\mathbf{x}}(t) = \begin{bmatrix} -\frac{R_{\text{eq}}}{L_s} & -\frac{1}{L_s} & -\frac{R_{\text{eq}}}{L_s} \\ \frac{1}{C_{\text{GS}}} & 0 & 0 \\ -\frac{R_{\text{eq}}}{L_m} & 0 & -\frac{R_{\text{eq}}}{L_m} \end{bmatrix} \mathbf{x}(t) + \begin{bmatrix} \frac{1}{L_s} \\ 0 \\ \frac{1}{L_m} \end{bmatrix} u(t), (3)$$

for Step 1 and Step 6. For those cases, the system reaches steady state for

$$\mathbf{x}_{1,6}^{\text{ss}} = \begin{bmatrix} 0 & 0 & \frac{u}{R_{\text{eq}}} \end{bmatrix}^T. \tag{4}$$

This indicates that the transformer will go into saturation and the magnetization current will become 0 after a while. In this situation, the gate driver loses its functionality and the supply will simply force a current going through the primary side. To avoid this, the circuit must be operated at a minimum operating frequency.

During the floating phase, no external power supply is connected to the gate driver transformer. An equivalent circuit for this case is given in Fig. 7 (b). Therefore, the only way to change the voltage across the magnetization inductance is through exchange with the gate-source capacitance. For this reason, the input u(t) will not influence the system behavior in this case. Since there is no resistor current  $i_R$ , the third row of the state-space matrix will be zero and the system matrix will be overdetermined.

$$\dot{\mathbf{x}}(t) = \begin{bmatrix} 0 & -\frac{1}{L_m + L_s} & 0\\ \frac{1}{C_{GS}} & 0 & 0\\ 0 & 0 & 0 \end{bmatrix} \mathbf{x}(t) + \begin{bmatrix} 0\\ 0\\ 0 \end{bmatrix} \cdot u(t). \quad (5)$$

In this situation, the entire system dynamics can be formulated as a second order differential equation,

$$\ddot{x}_1(t) = \frac{1}{C_{GS}(L_m - L_s)} x_1(t). \tag{6}$$

This equation is a homogeneous linear differential equation of second order and thus has a sinusoidal solution in a steady-state condition. It can therefore be observed that there will be a constant fluctuation of energy between the magnetization inductance and the gate-source capacitance.

An equivalent circuit for the case when the switches at the midpoint clamping are closed is given in Fig. 7 (c). As in the previous step, there is no external source supplying the primary side of the gate driver. In this case, however, there is a current  $i_R$  flowing through the midpoint clamping which can be characterized from the ON-state resistance of the closed switches  $q_5$  and  $q_6$ . The system equations for this situation are given as

$$\dot{\mathbf{x}}(t) = \begin{bmatrix} -\frac{R_{\text{eq}}}{L_s} & -\frac{1}{L_s} & -\frac{R_{\text{eq}}}{L_s} \\ \frac{1}{C_{\text{GS}}} & 0 & 0 \\ -\frac{R_{\text{eq}}}{L_{\text{DS}}} & 0 & -\frac{R_{\text{eq}}}{L_{\text{DS}}} \end{bmatrix} \mathbf{x}(t) + \begin{bmatrix} 0 \\ 0 \\ 0 \end{bmatrix} \cdot u(t). \quad (7)$$

The steady state conditions for this case are given as

$$\mathbf{x}_{3,4}^{\text{ss}} = \begin{bmatrix} 0 & 0 & 0 \end{bmatrix}^T. \tag{8}$$

This indicates that the system will converge towards an idle state during this switching state, allowing charge exchange for the drain-source capacitances  $C_{\rm DS}$  with the main transformer magnetization inductance  $L_M$ . It should be noted that the system matrix for this switching state is identical to the one for Steps 1 and 6. During all Steps, the system has a linear structure of

$$\dot{\mathbf{x}}(t) = \mathbf{A}\mathbf{x}(t) + \mathbf{b}u(t). \tag{9}$$

Having the system equations, it is possible to predict the behavior of the gate-source voltage of the MAB switches under ideal operating conditions:

Ideal operating conditions are defined as the switching frequency being high enough to have an almost constant gate-source voltage during Step 1 and Step 6 and a gate driver supply that ensures that the gate-source voltage is almost linear during the floating state. Furthermore, the clamping switches shall be activated when the midpoint voltage reaches zero. In this case, behavior such as the one depicted in Fig. 8 can be observed. This behavior can also be seen in simulation results as shown in Fig. 9.

# A. Design Guidelines

This section discusses several design aspects of a prototype of the proposed gate driver topology. The design process in this paper is based on the assumption that the user has already selected a MAB with a known MOSFET gate-source capacitance  $C_{\rm GS}$ . Then, the remaining steps are as follows:

- Select a switching frequency and compute the desired magnetization inductance that can charge and discharge the MOSFET capacitors within this frequency.

- 2) Compute values for  $L_s$  and  $R_{\rm eq}$  that guarantee a stable system during  $t_{\rm high}$ ,  $t_{\rm low}$  and  $t_{\rm zero}$ .

- 3) Tune the timing constants  $t_{zero}$ ,  $t_{high}$ ,  $t_{fall}$ ,  $t_{rise}$ ,  $t_{low}$  to ensure operation with minimal switching losses.

The following sections discuss these steps in more detail. Having selected the magnetization inductance, the question of how to choose the other parameters  $L_s$  and  $R_{\rm eq}$  shall be selected. Therefore, we examine the stability properties of the system matrix  ${\bf A}$  derived in the previous section. To examine the dynamic behavior of the system, the Eigenvalues  $\lambda$  were computed for different scenarios:

$$\det\left(\mathbf{A} - \lambda \mathbf{I}\right) = 0,\tag{10}$$

where I is a  $3 \times 3$  identity matrix. Since the system matrix is the same for the switching Steps 1,3,4,6 and the system is always boundary stable for Steps 2 and 5, only the system matrices for Steps 1,3,4,6 are discussed. Although the presented system has a switching nature, and thus stability for all individual Steps does not necessitate stability for the system under switching conditions, it can be achieved in this case by changing to Step 3 or 4 and waiting until the dynamic components of the system discharge through the equivalent resistance.

Using the Eigenvalue analysis, it was found that  $\bf A$  does not become unstable for all examined realizations of the system. However, choosing the correct values for  $L_s$  and  $R_{\rm eq}$  has an impact on the oscillations in the system and thus the power

#### losses.

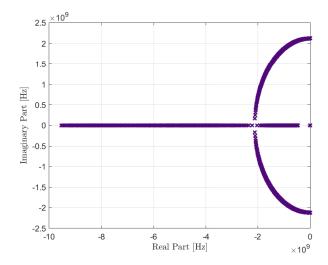

The system has two complex conjugated and one real eigenvalue as can be seen from Fig. 10. In case the resistance  $R_{\rm eq}$  is zero, the real part of all Eigenvalues is 0 and the system will continue to oscillate. Increasing  $R_{\rm eq}$  will add a negative real part to all three Eigenvalues. This reduces the amplitude of the oscillations and introduces damping to the system. A high resistance however also increases the conduction losses of the system and thus decreases the efficiency. For this reason, a trade-off has to be reached for  $R_{\rm eq}$ .

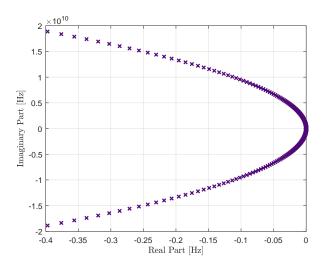

A variation in the stray inductance  $L_s$  only influences the two

Fig. 10. Root locus of the gate driver system matrix for changing  $R_{\rm eq}$ . A magnetization inductance of  $L_m=4.1\mu{\rm H}$ , a stray inductance of  $L_s=0.1{\rm nH}$  and a gate-source capacitance of  $C_{\rm GS}=2.23{\rm nF}$  were selected for this scenario. Then, 500 values with logarithmic spacing between  $1{\rm n}\Omega$  and  $1\Omega$  were chosen for  $R_{\rm eq}$ . The figure shows the change of the eigenvalues of the system matrix  ${\bf A}$  for the different values of  $R_{\rm eq}$ .

complex conjugated eigenvalues as can be seen from Fig. 11. The smaller the value, the more negative the real part of the eigenvalue pair. In addition to that, small values of  $L_s$  also increase the imaginary part of the eigenvalues which results in higher oscillation frequencies. Those oscillations would, however, decay over time due to the negative real part of the Eigenvalue. Furthermore, having no  $L_s$  will result in an LC-resonant tank formed by the magnetization inductance  $L_m$  and the MOSFET capacitance  $C_{\rm DS}$ . For decreasing  $L_s$  the behavior of the system will therefore converge towards the one of a conventional RLC parallel circuit.

# B. Operation Timing Selection

To successfully operate the gate driver, the timing constants have to be chosen correctly which shall be discussed in this paragraph. To minimize losses of the gate driver, it is important to obtain a curve with continuous transitions at the midpoint as shown in Fig. 8. In this case, the timings are selected in a way that the transition to the zero-state will take place when the midpoint voltage is zero and the transition to the high/low state takes place when the midpoint voltage is  $\pm V_{\rm GD}$ . Additionally, the zero-time must be chosen to be large enough to accommodate discharging and charging the drain-source capacitances of  $Q_s$  and allowing a sign change in the midpoint

Fig. 11. Root locus of the gate driver system matrix for different values of the stray inductance  $L_s$ . For this scenario, a magnetization inductance of  $L_m=4.1\mu\mathrm{H}$ , an equivalent resistance of  $R_{\mathrm{eq}}=0.125\Omega$  and a gate-source capacitance of  $C_{\mathrm{GS}}=2.230$  nF were chosen. After that, the Eigenvalues of the system matrix  $\mathbf{A}$  were evaluated for 500 different values of the stray inductance which were logarithmically spaced between  $L_s=0.001\mathrm{nH}$  and  $L_s=1\mathrm{H}$ . Shown are the trajectories of the two complex conjugated Eigenvalues. The third Eigenvalue is independent of  $L_s$  and does not move.

voltage of the MAB, as seen in Fig. 8. Furthermore, the overall operating frequency should be chosen to be small enough to allow the required energy transfers to take place. For small transformers, where the number of windings is small enough to allow full identification of all parasitic inductances, an analytic formula using the system model can be used to tune the timing constants. In the case of larger transformers, where the number of required tests to identify all parameters becomes too numerous, the parameters can be tuned by inspection, using low-power tests as shown in the next section.

# IV. PROTOTYPE CONSTRUCTION AND EXPERIMENTAL RESULTS

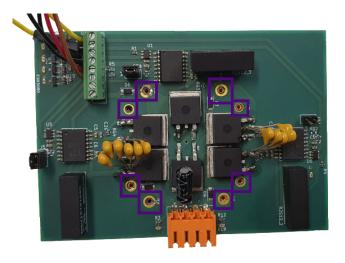

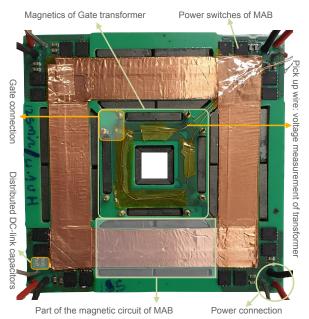

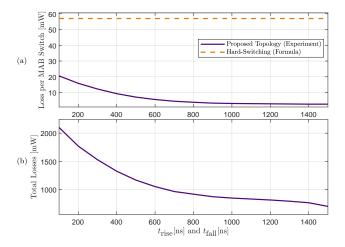

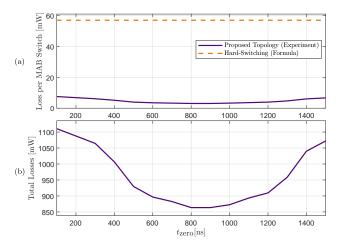

To verify the findings proposed in this paper, a gate driver prototype shown in Fig. 12 was built. The prototype consists of two assemblies, the primary gate driver board which can be seen in Fig. 12 (a) and the gate driver transformer together with a MAB shown in Fig. 12 (b). To verify the efficiency for large-scale multilevel converters, the gate driver is tested for a MAB with 4 groups of modules, each of which is made up of 4 active bridges that are connected in parallel. The 400 V MAB thus consists of 16 modules with 64 switches which were used to test the proposed gate driver. The 64 switches each have an input capacitance of 2330 pF and output capacitance of 220 pF that need to be charged during the switching. To get insight into the efficiency of the proposed topology, the switching losses for hard-switching can be estimated by  $E_{\rm sw} = 0.5 C_{\rm GS} V_{\rm GS}^2 \approx 0.456 \mu \rm J$  per switch. In the case of a frequency of 125 kHz, the average power loss is equal to 57 mW for each switch. To change the switching state, it is furthermore necessary to maintain a threshold voltage of 2.9 V across the gate-source terminals of the MOSFETs. A DC voltage of 7.0 V was selected as the operating voltage of the gate driver to ensure the

#### (a) Gate Driver Board

# (b) Gate Driver transformer and MAB

# (c) Interleaving pattern of the Prototype

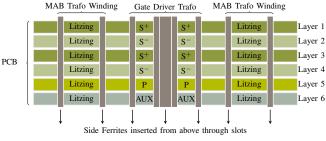

Fig. 12. The prototype realizes the proposed circuit. The prototype is split into two subsystems, the gate driver board shown in (a) and the transformer board shown in (b). The transformer board contains both the gate driver transformer and MAB circuit. To drive the MOSFETs in the transformer board, the gate driver board is connected to the transformer board through the holes H5, H6, H7, H8, H9, H10, H11, H12 highlighted in purple. For the experiment results, a Spartan 6 FPGA was used to generate the control signals and an auxiliary power supply was connected. Each PCB of the transformer board consists of one full bridge with gate driver windings. The interleaving pattern of each of the PCBs is shown in (c).

threshold voltage requirements are met. The gate driver prototype, therefore, needs a multi-winding transformer with 64 secondary windings. To optimize the power packaging and increase the power density, the gate driver transformer is implemented as a planar transformer with 16 primary windings (P) and 64 secondary windings (S) as shown in Fig. 12 (c). The winding arrangement is  $S^+-S^--S^+-S^--P$ . All windings are identical and have 2 turns where the notation S<sup>+</sup> and S<sup>-</sup> refer to the turn directions of each winding. Since a full identification of this transformer requires  $0.5 \cdot 80 \cdot 79 = 3160$  measurements, a full characterization of the prototype will not be given in this paper and all tuning will be performed "by inspection" to obtain preliminary results for the verification of our findings. However, a qualitative assessement of the behaviour of the device For the remainder of this section, symmetric operation is assumed, i.e.  $t_{\text{rise}} = t_{\text{fall}}$  and  $t_{\text{high}} = t_{\text{low}}$ .

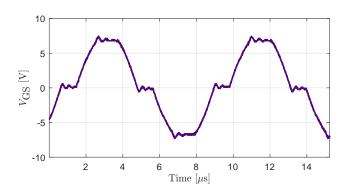

Figure 13 shows the midpoint waveform with the modulator

Fig. 13. Experiment results of the gate driver midpoint waveform with correctly timed modulator. The timing parameters in this condition are  $t_{\rm rise}=1000~{\rm ns}$ ,  $t_{\rm zero}=800~{\rm ns}$  and  $f_{\rm s}=125~{\rm kHz}$ .

being timed correctly. The curve verifies the theoretical analysis and modeling shown in Fig. 8, which suggests a similar pattern in the second subfigure. The main difference is seen as a decaying sinusoidal noise during the high-, low- and zero states. This is due to the limited resolution of the FPGA which is controlling the modulator. All timings are selected as an integer multiple of the clock frequency of the FPGA. In case this value is not exactly equal to the optimal value, a small deviation will remain which is further amplified by the turn- ON and turn- OFF delays of the switches on the gate driver circuits.

If the timings are not chosen correctly, the gate-source voltage waveform will be distorted. Choosing the rise/fall time too small will result in ripples as seen in Fig. 14 which occur due to the gate-source voltage not yet reaching the desired value when the next switching state is applied. Choosing the timings too small will result in a curved waveform during the rise/ fall time. This is due to the sinusoidal nature of the voltage during that switching state which was derived in the previous section. Choosing a correct timing however, will result in only the approximately linear part of the waveform being present since the circuit switches to Step 1 or Step 6 before the peak of the sinusoidal is reached. Figure 15 shows that the overall energy consumption of the gate driver circuit

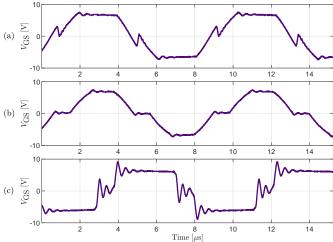

Fig. 14. Experiment results of the effects of different timing selections on the gate driver waveform concerning  $t_{\rm rise}$ . The top subfigure (a) shows a waveform corresponding to a value of  $t_{\rm rise}=100$  ns. The middle subfigure (b) depicts a waveform with  $t_{\rm rise}=1000$  ns and the bottom subfigure (c) represents  $t_{\rm rise}=1500$  ns. In all cases, the zero-time is  $t_{\rm zero}=800$  ns and the switching frequency is  $f_{\rm s}=125$  kHz.

Fig. 15. Experiment results of the power loss for different values of  $t_{\rm rise}$ . The top figure (a) shows the energy loss of the main gate driver circuit per MAB MOSFET in mW. For reference, the power loss that would occur on a gate driver topology with hard switching is shown in orange. The lower subfigure (b) shows the overall losses of all 64 MAB MOSFETs and the auxiliary power losses for DC/DC converters, diagnostics LEDs, ... For these experiments, the zero-time is  $t_{\rm zero}=800$  ns and the switching frequency is  $f_{\rm s}=125$  kHz.

decreases until the optimal value is found and stays constant after that.

A similar effect can be seen when the zero time is varied. Selecting a zero time too short will result in the drain-source capacitor not fully discharging which results in distorted waveforms (Fig. 16) and higher losses (Fig. 17). Similarly, choosing the zero time too large will result in an increase in losses as seen in Fig. 17, which can be explained by staying in the zero states while the energy is completely transferred and the energy might flow back to the drain-source capacitance. In between of those effects, an optimal value can be obtained as shown in Fig. 17.

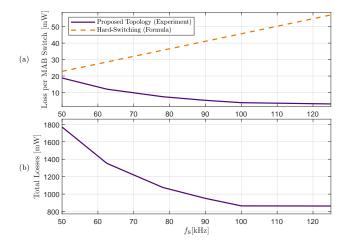

Varying the switching frequency of the MAB frequency will

Fig. 16. Experiment results of the effects of different timing selections on the gate driver waveform with respect to  $t_{\rm zero}$ . The top subfigure (a) shows the midpoint waveform for  $t_{\rm zero}=100$  ns. A zero-time of  $t_{\rm zero}=800$  ns can be seen in the middle subfigure (b) while the bottom subfigure (c) shows a waveform with  $t_{\rm zero}=1500$  ns. A rise time of  $t_{\rm rise}=1000$  ns and a switching frequency of  $f_{\rm s}=125$  kHz were selected during the experiments.

Fig. 17. Experiment results of the power loss for different values of  $t_{\rm zero}$ . The top figure (a) represents the power that is used by the primary active bridge to maintain operation, normalized for the total number of high-power MAB switches. In addition, the power loss of a gate driver topology based on hard-switching is shown in orange. The bottom figure (b) depicts the total power losses, used by the MAB as well as the auxiliary supply for the gate driver circuit. To obtain a fair comparison, the rise time of  $t_{\rm rise} = 1000$  ns and switching frequency of  $f_{\rm s} = 125$  kHz were used in all cases.

decrease the power consumption of the gate driver as seen in Fig. 18. However, choosing a frequency too low will result in restrictions of the zero and rise timings which will again yield a decrease in performance.

#### V. Conclusion

This paper presented a novel gate driver model for MAB DC/DC converters. To maximize the efficiency of the MAB, a zero-voltage switching scheme was employed within the gate driver. Therefore, the topology utilizes a multi-winding transformer to exchange energy stored in the gate-source capacitances of the MOSFETs in the MAB. Similarly, the energy within the drain-source capacitance was exchanged

Fig. 18. Experiment results of the power losses of the gate driver over different switching frequencies. At each frequency, the timings are tuned to optimal values. An overview of the power losses of a hard-switching-based topology on each switch is shown in the orange curve. The top subfigure (a) shows the development of losses over one of the 64 MAB switches while the bottom subfigure (b) shows the development of the sum of all losses of the MAB as well as the gate driver circuit itself.

with the parasitic inductances in the drain-source capacitance. The fundamental working principle was derived with a system model and verified with experiment results. The advantages of the topologies are the lower switching losses and the requirement for fewer components. Furthermore, guidelines for the modulation of the gate driver are given. However, it is not possible to implement phase-shifts between the individual active bridges of the MAB which is the major limitation of the proposed topology.

#### REFERENCES

- Y.-M. Chen, Y.-C. Liu, and F.-Y. Wu, "Multi-input dc/dc converter based on the multiwinding transformer for renewable energy applications," *IEEE Transactions on Industry Applications*, vol. 38, no. 4, pp. 1096– 1104, 2002.

- [2] T. Pereira, F. Hoffmann, R. Zhu, and M. Liserre, "A comprehensive assessment of multiwinding transformer-based dc-dc converters," *IEEE Transactions on Power Electronics*, vol. 36, no. 9, pp. 10020–10036, 2021.

- [3] C. Zhao, S. D. Round, and J. W. Kolar, "An isolated three-port bidirectional dc-dc converter with decoupled power flow management," *IEEE Transactions on Power Electronics*, vol. 23, no. 5, pp. 2443–2453, 2008.

- [4] M. Liserre, F. Hoffman, and T. Pereira, "Multiwinding-transformer-based dc-dc converter solutions for charging stations [technology leaders]," *IEEE Electrification Magazine*, vol. 9, no. 2, pp. 5–9, 2021.

- [5] S. Falcones, R. Ayyanar, and X. Mao, "A dc-dc multiport-converter-based solid-state transformer integrating distributed generation and storage," *IEEE Transactions on Power Electronics*, vol. 28, no. 5, pp. 2192–2203, 2013.

- [6] D.-J. Park, S.-Y. Choi, R.-Y. Kim, and D.-S. Kim, "A novel battery cell balancing circuit using an auxiliary circuit for fast equalization," in *IECON 2014 - 40th Annual Conference of the IEEE Industrial Electronics Society*, 2014, pp. 2933–2938.

- [7] M. A. Rahman, M. R. Islam, K. M. Muttaqi, and D. Sutanto, "Modeling and design of a multiport magnetic bus-based novel wind-wave hybrid ocean energy technology," *IEEE Transactions on Industry Applications*, pp. 1–1, 2021.

- [8] F. Grimm, J. Wood, and M. Baghdadi, "A dc-autotransformer based multilevel inverter for automotive applications," arXiv preprint arXiv:2011.12164, 2020.

- [9] L. Yin, X. Weng, K. Zhang, Z. Zhao, L. Yuan, and S. Yi, "A new topology of energy router with multiple hvac ports for power distribution networks," in 2016 19th International Conference on Electrical Machines and Systems (ICEMS), 2016, pp. 1–5.

- [10] Jintae Kim, Gwanbon Koo, and Chung Yuen Won, "Loss analysis design of charge-pumped voltage supply for floating gate driver circuits in battery management system," in 2016 IEEE Transportation Electrification Conference and Expo, Asia-Pacific (ITEC Asia-Pacific), 2016, pp. 061– 065.

- [11] A. Soldati, E. Imamovic, and C. Concari, "Bidirectional bootstrapped gate driver for high-density sic-based automotive dc/dc converters," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 8, no. 1, pp. 475–485, 2020.

- [12] N. Rouger, Y. Barazi, M. Cousineau, and F. Richardeau, "Modular multilevel soi-cmos active gate driver architecture for sic mosfets," in 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2020, pp. 278–281.

- [13] D. Maksimovic, "A mos gate drive with resonant transitions," in PESC '91 Record 22nd Annual IEEE Power Electronics Specialists Conference, 1991, pp. 527–532.

- [14] H. Jedi, T. Salvatierra, A. Ayachit, and M. K. Kazimierczuk, "High-frequency single-switch zvs gate driver based on a class  $\phi_2$  resonant inverter," *IEEE Transactions on Industrial Electronics*, vol. 67, no. 6, pp. 4527–4535, 2020.

- [15] S. H. Weinberg, "A novel lossless resonant mosfet driver," in PESC '92 Record. 23rd Annual IEEE Power Electronics Specialists Conference, 1992, pp. 1003–1010 vol.2.

- [16] Z. Zhang, F. Li, and Y. Liu, "A high-frequency dual-channel isolated resonant gate driver with low gate drive loss for zvs full-bridge converters," *IEEE Transactions on Power Electronics*, vol. 29, no. 6, pp. 3077–3090, 2014.

- [17] D. Rothmund, D. Bortis, and J. W. Kolar, "Highly compact isolated gate driver with ultrafast overcurrent protection for 10 kv sic mosfets," CPSS Transactions on Power Electronics and Applications, vol. 3, no. 4, pp. 278–291, 2018.

- [18] M. Takasaki, Y. Miura, and T. Ise, "Wireless power transfer system for gate power supplies of modular multilevel converters," in 2016 IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), 2016, pp. 3183–3190.

- [19] V.-S. Nguyen, P. Lefranc, and J.-C. Crebier, "Gate driver supply architectures for common mode conducted emi reduction in series connection of multiple power devices," *IEEE Transactions on Power Electronics*, vol. 33, no. 12, pp. 10265–10276, 2018.

- [20] U. Khalid, M. M. Khan, Z. Xiang, and Y. Jianyang, "Bidirectional modular dual active bridge (dab) converter using multi-limb-core transformer with symmetrical lc series resonant tank based on cascaded converters in solid state transformer (sst)," in 2017 China International Electrical and Energy Conference (CIEEC), 2017, pp. 627–632.

- [21] J. Gottschlich, M. Schäfer, M. Neubert, and R. W. De Doncker, "A galvanically isolated gate driver with low coupling capacitance for medium voltage sic mosfets," in 2016 18th European Conference on Power Electronics and Applications (EPE'16 ECCE Europe), 2016, pp. 1–8.

- [22] L. Zhang, S. Ji, S. Gu, X. Huang, J. Palmer, W. Giewont, F. Wang, and L. M. Tolbert, "Design considerations of high-voltage-insulated gate drive power supply for 10 kv sic mosfet in medium-voltage application," in 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), 2019, pp. 425–430.

- [23] A. Anurag, S. Acharya, Y. Prabowo, G. Gohil, and S. Bhattacharya, "Design considerations and development of an innovative gate driver for medium-voltage power devices with high dv/dt," *IEEE Transactions on Power Electronics*, vol. 34, no. 6, pp. 5256–5267, 2019.

- [24] A. Christe, M. Petkovic, I. Polanco, M. Utvic, and D. Dujic, "Auxiliary submodule power supply for a medium voltage modular multilevel converter," CPSS Transactions on Power Electronics and Applications, vol. 4, no. 3, pp. 204–218, 2019.

- [25] S. Fuchs and J. Biela, "Output voltage stability of series connected transformers for isolated auxiliary supplies in modular medium voltage converter systems," in 2018 20th European Conference on Power Electronics and Applications (EPE'18 ECCE Europe), 2018, pp. P.1–P.9.

- [26] S. Wei, Z. Zhao, L. Yuan, W. Wen, and K. Chen, "Voltage oscillation suppression for the high-frequency bus in modular-multiactive-bridge converter," *IEEE Transactions on Power Electronics*, vol. 36, no. 9, pp. 9737–9742, 2021.

- [27] S. K. Dam and V. John, "A multi-active-half-bridge converter based softswitched fast voltage equalizer for multi-cell to multi-cell charge trans-

- fer," in 2019 IEEE Transportation Electrification Conference (ITEC-India), 2019, pp. 1–6.

[28] P. Zumel, C. Fernandez, A. Lazaro, M. Sanz, and A. Barrado, "Overall analysis of a modular multi active bridge converter," in 2014 IEEE 15th Workshop on Control and Modeling for Power Electronics (COMPEL), 2014, pp. 1–9.