## Low-Power Silicon Strain Sensor Based on CMOS Current Reference Topology

Nicolas Roisin<sup>a</sup>, Thibault P. Delhaye<sup>a</sup>, Nicolas André<sup>a</sup>, Jean-Pierre Raskin<sup>a</sup>, Denis Flandre<sup>a</sup>

<sup>a</sup>Institute of Information and Communication Technologies, Electronics and Applied Mathematics (ICTEAM), UCLouvain, Place du levant 3, 1348 Louvain-la-Neuve, Belgium

#### Abstract

A strain sensor inspired by a Widlar self-biased current source topology called  $\beta$ -multiplier is developed to obtain a strain-dependent

A strain sensor inspired by a Widlar self-biased current source topology called β-multiplier is developed to obtain a strain-dependent reference current with high supply rejection. The sensor relies on the piezoresistive effect in the silicon MOS transistors that form the current reference circuit. The device behavior is analytically computed and verified with experimental measurements under four-point bending test. A basic implementation with an integrated resistor reaches a strain sensitivity of 2.54 nA/με (gauge factor of 324) for a temperature sensitivity of 5.20.6 nA/°C. A more advanced full-transistor circuit based on current subtraction principle is furthered implementation includes a CMOS active load to tune the strain and temperature sensitivity of 2.20.7 nA/με (gauge factor of 1773) and temperature sensitivity of 2.20.7 nA/με (gauge factor of 1773) and temperature sensitivity of 2.20.7 nA/με (gauge factor of 1773) and temperature sensitivity of 2.20.7 nA/με (gauge factor of 1773) and temperature sensitivity of 2.20.7 nA/με (gauge factor of 1773) and temperature sensitivity of 2.20.7 nA/με (gauge factor of 1773) and temperature sensitivity of 2.20.7 nA/με (gauge factor of 1773) and temperature sensitivity of 2.20.7 nA/με (gauge factor of 1773) and temperature sensitivity of 2.20.7 nA/με (gauge factor of 1773) and temperature sensitivity of 2.20.7 nA/με (gauge factor of 1773) and temperature sensitivity of 2.20.7 nA/με (gauge factor of 1773) and temperature sensitivity of 2.20.7 nA/με (gauge factor of 1773) and temperature sensitivity of 2.20.7 nA/με (gauge factor of 1773) and temperature sensitivity of 2.20.7 nA/με (gauge factor of 1773) and temperature sensitivity of 2.20.7 nA/με (gauge factor of 1773) and temperature sensitivity of 2.20.7 nA/με (gauge factor of 1773) and temperature sensitivity of 2.20.7 nA/με (gauge factor of 1773) and temperature sensitivity of 2.20.7 nA/με (gauge factor of 1773) and temperature sensitivity of 2.20.7 nA/με (gauge factor of 1773) and temperature sensitivity of 2.20

graphene [15] or carbon nanotubes [16], allow high gauge factor up to 1000. However, the fabrication cost and complexity, added to the fragility, make long-term applications difficult. On the other hand, silicon is a well-known material in electronics with reasonable cost and fabrication complexity [17]. Its crystallographic configuration leads to high piezoresistive variation with potential gauge factor above 150 [18].

Email address: nicolas.roisin@uclouvain.be (Nicolas Roisin)

pendencies. We complete the study with the strain and temperature analyses of the  $\beta$ -multipliers to evaluate the performances of the different implementations.

### 2. Analytical Model

#### 2.1. Piezoresistive effect

The piezoresistive effect in silicon is mainly due to the change in the carrier mobility that is much higher than the change in the dimensions [21]. By considering infinitesimal displacement, the relative variation of the mobility can be expressed as

$$-\frac{d\mu_i}{\mu_i} = \pi_{i,l}\sigma_l + \pi_{i,t}\sigma_t,\tag{1}$$

where i stands for the electron (n) or holes (p) contributions,  $\pi_l$  and  $\pi_t$  are, respectively, the piezoresistive coefficients in the longitudinal and transverse directions while  $\sigma_l$  and  $\sigma_t$  are the applied stresses in those two directions. We consider the longitudinal direction to be the direction of the transistor channel while the transverse direction is perpendicular to it. In ceramic material, the strain-stress relation can be expressed by considering elastic deformation [22] as

$$\sigma_i = E \cdot \varepsilon_i, \tag{2}$$

where E is the Young's modulus of around 165 GPa for silicon in the [110] crystal direction [23] and  $\varepsilon_j$  is the applied strain in direction j.

Solving relation 1 leads to

$$\mu_i = \mu_{i,0} \ e^{-(\pi_{i,l}\sigma_l + \pi_{i,l}\sigma_t)}, \tag{3}$$

where  $\mu_{i,0}$  is the mobility in the relaxed case.

The piezoresistive coefficients are intrinsic parameters that are linked to the effective masses variations of the electrons and the holes. As the variations of the effective mass depend on the crystal direction of the applied strain, so do these coefficients [24].

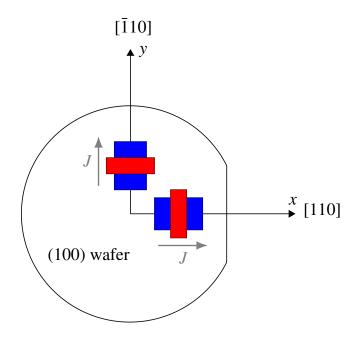

In this work, we consider MOS transistor with channel oriented in parallel and perpendicular to the [110] direction of the crystal as displayed in Fig. 1.

Figure 1: Illustration of the transistors orientations along <110> directions on a (100) silicon wafer.

In this orientation, the transverse and longitudinal piezoresistive coefficients  $\pi_{i,l}$  and  $\pi_{i,t}$  can be expressed as [25]

$$\pi_{i,l} = \frac{\pi_{i,11} + \pi_{i,12} - \pi_{i,44}}{2},

\pi_{i,t} = \frac{\pi_{i,11} + \pi_{i,12} + \pi_{i,44}}{2},$$

(4)

where  $\pi_{i,11}$ ,  $\pi_{i,12}$  and  $\pi_{i,44}$  are the main components of the piezoresistance tensor. The values for n-type and p-type silicon are given in Table 1 [26].

|      | $\pi_{11}$ | $\pi_{12}$ | $\pi_{44}$ | $\pi_t$ | $\pi_l$ |

|------|------------|------------|------------|---------|---------|

| n-Si | -1022      | 534        | -136       | -176    | -312    |

| p-Si | 66         | -11        | 1381       | -663    | 718     |

Table 1: Main components of the piezoresistance tensor for p- and n-type transistors [26]. The effective longitudinal and transverse piezoresistive coefficients for strain applied in the [110] direction are also computed. The values are expressed in TPa<sup>-1</sup>.

At the circuit level, it was found that perpendicular transistors placed in current mirror configuration lead to higher strain sensitivity with regards to ratio of the transistor currents [27, 28, 29]. Indeed, this configuration leads to an effective sensitivity that is equal to the difference of the piezoresistive coefficients of the two transistors. If these coefficients are of opposite sign, an enhanced strain sensitivity can be obtained. Such features can be found by placing PMOS (NMOS) transistors perpendicularly along the [110] ([100]) directions. This perpendicular current mirror works as the main sensing element of our proposed solution for strain sensing applications.

#### 2.2. Current reference configuration

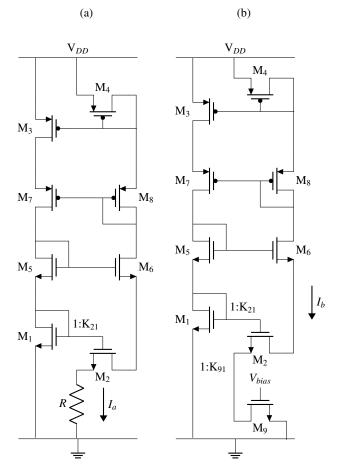

In this work, we first imagined a  $\beta$ -multiplier-like reference shown in Fig. 2.a as strain sensor. This is inspired by a self-biased reference based on Widlar current source topology. A cascode configuration is implemented in order to further reduce the supply sensitivity.

In this circuit, the two PMOS transistors  $M_3$  and  $M_4$  impose the same current in both in the absence of strain branches while the two NMOS transistors and the resistor impose a quadratic relation between the currents of the two branches. The transistors are assumed in saturation with long channel model and no mismatch between them. When the upper and lower parts of the circuits are connected, the equilibrium in the absence of strain leads to

$$I_a = 2 \frac{\left(1 - 1/\sqrt{K_{21}}\right)}{R^2 \beta_{n,0}},\tag{5}$$

where R is the resistance,  $K_{21}$  is the ratio between the width of the NMOS transistors,  $\beta_{n,0} = \frac{W}{L}C_{ox}\mu_{n,0}$  with  $C_{ox}$  the capacitance of the transistor gate, W the width and L the length of the transistor  $M_1$ . This last term leads to the name  $\beta$ -multiplier for the current reference.

Under strain conditions, the mobility of the different transistors is impacted. The expression of the reference current under

Figure 2:  $\beta$ -multiplier reference circuits with (a) resistor and (b) full-transistor implementations. The reference currents are, respectively, written  $I_a$  and  $I_b$ .

uniaxial stress is then given by

$$I_a = 2 \frac{\left(e^{(\pi_3 - \pi_1 - \pi_4)\frac{\sigma}{2}} - e^{-\pi_2\frac{\sigma}{2}} / \sqrt{K_{21}}\right) e^{-2\pi_r \sigma}}{R^2 \beta_{n,0}}, \quad (6)$$

where  $\pi_j$  is the piezoresistive coefficient of transistor  $M_j$ ,  $\pi_r$  is the piezoresistive coefficient of the resistor and  $\sigma$  is the uniaxial stress applied on the circuit.

A second circuit is presented in Fig. 2.b where the resistor is replaced with an active load. The transistor adds a control on the reference current by tuning the gate voltage  $V_{bias}$ . This tuning allows to control the power consumption of the circuit along with the sensitivities to strain and temperature.

The reference current in this case can be expressed as

$$I_{b} = 2V_{ov}^{2} \beta_{n,0} \cdot \frac{\left(e^{(\pi_{3} - \pi_{4} - \pi_{1})\frac{\sigma}{2}} - e^{-2\pi_{2}\sigma} / \sqrt{K_{21}}\right)^{2}}{\left[\left(e^{(\pi_{3} - \pi_{4} - \pi_{1})\frac{\sigma}{2}} - e^{-2\pi_{2}\sigma} / \sqrt{K_{21}}\right)^{2} + e^{\pi_{9}\sigma} / \sqrt{K_{91}}\right]}, (7)$$

where  $K_{91}$  is the ratio between the width of the transistors  $M_9$  and  $M_1$ , and  $V_{ov} = (V_{bias} - V_{th,n})$  with  $V_{th,n}$  the threshold voltage of transistor  $M_9$ .

The complete development to find the expressions of the reference currents  $I_a$  and  $I_b$  can be found in Appendices Appendix A and Appendix B, respectively.

In both circuits, the PMOS and NMOS pairs  $(M_1/M_2, M_3/M_4$  and  $M_1/M_9)$  are oriented perpendicularly to maximize the strain sensitivity. This configuration is necessary to observe the variations caused by the applied strain on the equilibrium current.

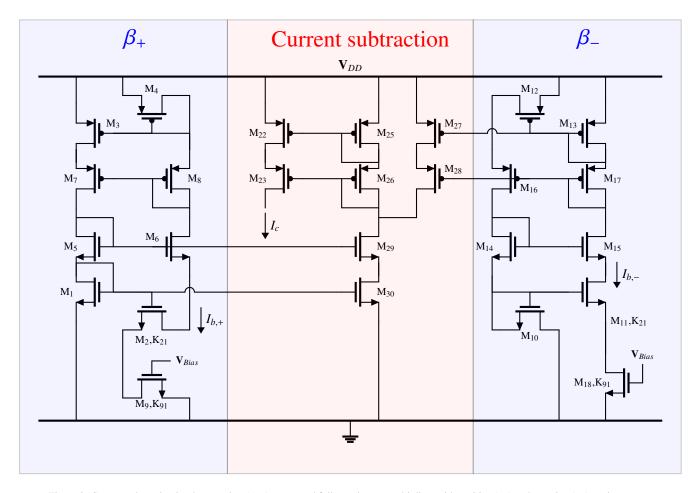

#### 2.3. Current subtraction configuration

It is possible to reach a larger strain sensitivity by combining circuits with positive and negative strain responses. Furthermore, a reduction of the temperature sensitivity can be achieved if the temperature responses of the two circuits are of the same sign thanks to the current subtraction approach [30]. In order to obtain negative strain response, a rotation by  $90^{\circ}$  of the sensitive transistors in Fig 2.b is made. Two  $\beta$ -multiplier circuits can then be combined with a current subtraction circuit as displayed in Fig. 3. The sensing parts with positive and negative strain sensitivities are highlighted in blue while the current subtraction part is represented in red.

The output current of this circuit is given by

$$I_c = C_+ I_{b,+} - C_- I_{b,-},$$

(8)

where  $I_{b,+}$  and  $I_{b,-}$  are the current of the  $\beta$ -multiplier with positive and negative responses, respectively.  $C_+$  and  $C_-$  are constants that can be tuned by changing the ratio between the size of the MOSFETs of the  $\beta$ -multipliers and the current subtraction, i.e.  $M_{27}$  and  $M_{30}$ . The linear combination of the two currents  $I_{b,+}$  and  $I_{b,-}$  with chosen constants ensures a positive output current  $I_c$  regardless the applied strain.

#### 3. Experiment and discussion

#### 3.1. Experimental set-up

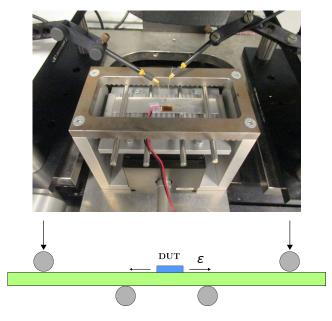

The circuits were fabricated using UMC L180 technology. The transistors have low threshold voltage with 1.8 V voltage maximum supply voltage. For the temperature measurements, a bare die was put on a heating stage while the strain measurements were performed in a four-point bending machine. In this last case, the device under test (DUT) is ground down to a thickness of 50 um and next glued with M-Bond 200 adhesive from Vishay on a 1 mm-thick aluminium strip. The strain is then applied using a four-point bending machine as displayed in Fig. 4. The bottom cylinders are spaced of 3 cm while a space of 8 cm is set for the the upper ones. The four-point bending method is a well-known mechanical test that allows a simple, stable and homogeneous deformation on a glued device [31]. A reference metallic strain gauge of 350  $\Omega$  from *Micro-Measurements* is mounted next to the die in order to measure the strain applied to the device. The resistance of the gauge was measured with a Series 2000 digital multimeter from *Keithley*.

The electrical measurements are made with a *B-1500 Semi-conductor Device Parameter Analyzer* from *Keysight*. The electrical contact was made with tungsten probes directly on the die under test for both temperature or strain experiments.

Figure 3: Current subtraction implementation  $(\beta_{sub})$  composed full-transistor  $\beta$ -multipliers with positive  $(\beta_+)$  and negative  $(\beta_-)$  strain response

Figure 4: Illustration of the set-up for the four-point bending test.

The transistors are first measured separately in order to analyze the impact of strain and temperature on the mobility and the threshold voltage. Then, the currents of the four reference

circuits are measured, i.e. the  $\beta$ -multiplier with resistor ( $\beta_R$ ), the full-transistor  $\beta$ -multipliers with positive ( $\beta_+$ ) and negative ( $\beta_-$ ) strain responses and the current subtraction implementation ( $\beta_{sub}$ ).

#### 3.2. Transistor analysis

The tested NMOS and PMOS transistors have both a gate width of  $8.5 \,\mu\text{m}$  and gate length of  $5 \,\mu\text{m}$ . Each transistor type is duplicated and rotated by  $90^{\circ}$  in order to retrieve the transverse and longitudinal piezoresistive coefficients.

The significant parameters, i.e. the mobility and the threshold voltage, were extracted from I-V curves at different strain levels with the method from Jeppson [32]. This method is based on a least-square fit that is stable and insensitive to the mobility degradation and series resistances. We measured the drain current and we varied the gate voltage between 0 and 1.8 V while the source and the drain were, respectively, put to ground (1.8 V) and 50 mV (1.75 V) the for the NMOS (PMOS) transistors (resp.). The body for both types of transistor is connected to the source.

The low-field mobilities obtained in the relaxed case at  $25^{\circ}$ C are  $1131~\text{cm}^2\text{V}^{-1}\text{s}^{-1}$  and  $191~\text{cm}^2\text{V}^{-1}\text{s}^{-1}$  for the NMOS and PMOS transistors, respectively. The threshold voltages in these conditions are, respectively, 73.6 mV and -330.5 mV for the NMOS and PMOS transistor.

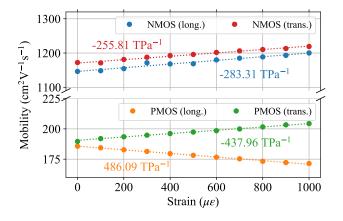

The results of the strain measurements are displayed in Fig. 5. The piezoresistive coefficients are extracted by computing a linear interpolation on the mobility variation using relation 1. We obtain a transverse and longitudinal coefficients of -255 (-437) TPa<sup>-1</sup> and -283 (486) TPa<sup>-1</sup> for the NMOS (PMOS) transistors, respectively. The PMOS transistor presents high and opposite piezoresistive coefficients while the coefficients for the NMOS transistor are smaller and of the same sign.

Table 2 compares the experimentally measured data with piezoresistive coefficients published in the literature. The results we obtained are in agreement with the ones shown in other works. The differences observed in the piezoresistive coefficients between the different works can be due to extrinsic perturbations that influence the strain response. Indeed, the bias condition as well as the regime of the measured transistors can have a strong impact on the extracted coefficients due to the different scattering mechanisms [33].

|                     | $\pi_{n,t}$ | $\pi_{n,l}$ | $\pi_{p,t}$ | $\pi_{p,l}$ | Dimensions                        |

|---------------------|-------------|-------------|-------------|-------------|-----------------------------------|

| This work           | -255        | -283        | -437        | 486         | $WxL = 8.5 \mu m x 5 \mu m$       |

| Wacker et al. [34]  | -470        | -220        | -450        | 520         | $WxL = 16$ $\mu m  x  16$ $\mu m$ |

| Bradley et al. [35] | -250        | -320        | -385        | 415         | $L = 15 \mu m$                    |

Table 2: Longitudinal and transverse piezoresistive coefficients in TPa<sup>-1</sup> experimentally measured and from the literature.

Figure 5: Mobility variation with regards to the applied strain for NMOS and PMOS transistors oriented in the longitudinal or transverse directions. The extracted piezoresistive coefficients are written next to the curves.

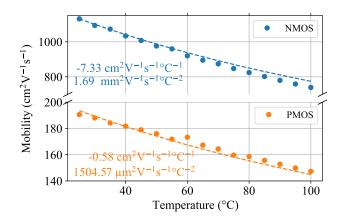

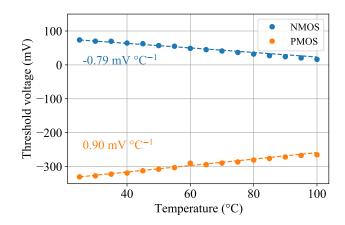

The results of the temperature measurements are displayed in Fig. 6 and 7. Mobility and threshold voltage sensitivities of -7.33 cm $^2V^{-1}s^{-1}{}^{\circ}C^{-1}/1.69~mm^2V^{-1}s^{-1}{}^{\circ}C^{-2}$  and -0.79 mV $^{\circ}C^{-1}$  are, respectively, found for n-type transistors while the p-type transistors show a mobility sensitivity of -0.58 cm $^2V^{-1}s^{-1}{}^{\circ}C^{-1}/1504.57~\mu m^2V^{-1}s^{-1}{}^{\circ}C^{-2}$  and a threshold voltage sensitivity of 0.90 mV $^{\circ}C^{-1}$ . The dashed curves are com-

puted using the theoretical model provided by the circuit supplier. The curves are in good agreement with the experimental work for both NMOS and PMOS transistors.

Figure 6: Mobility variation with regards to the temperature for NMOS and PMOS transistors. The temperature sensitivity extracted from the measurements is written next to it. The dashed lines represent the theoretical model from the transistor technology given by the UMC foundry.

Figure 7: Threshold voltage with regards to the temperature for NMOS and PMOS transistors. The temperature sensitivity extracted from the measurements is written next to it. The dashed lines represent the theoretical model from the transistor technology given by the UMC foundry.

#### 3.3. *\beta*-multiplier analysis

The  $\beta$ -multiplier circuits are tested similarly with the four-point bending method. Strain and temperature measurements are conducted on four circuits where the output current is measured according to the supply voltage for the implementation with resistor or bias voltage for the full-transistor ones. The first circuit is the  $\beta$ -multiplier with resistor ( $\beta_R$ ) displayed in Fig. 2.a where the output current is  $I_a$ . The resistor is made of poly-silicon and reaches a value of  $10 \text{ k}\Omega$ . The configuration with an active load is then investigated with two transistor orientations leading to positive ( $\beta_+$ ) and negative ( $\beta_-$ ) strain sensitivities. The output currents of these circuits represented in Fig. 2.b are  $I_{b,+}$  ( $I_{b,-}$ ) for the positive (negative) contribution. Finally, the output current  $I_c$  of the circuit with current subtraction ( $\beta_{sub}$ ) represented in Fig. 3 is measured.

The gauge factor GF is used to analyze and compare the strain sensitivity. This factor is defined as the relative current variation with regards to the strain, i.e.

$$\frac{\Delta I}{I(\varepsilon = 0)} = GF \cdot \varepsilon \tag{9}$$

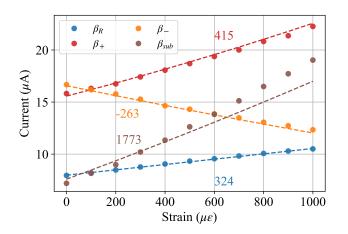

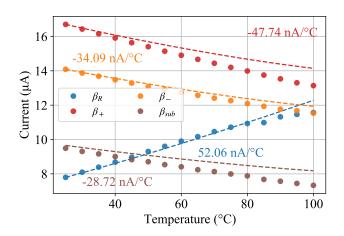

The current variations under strain stimuli are displayed in Fig. 8 while the variations according to the temperature are shown in Fig. 9.

Figure 8: Output current with regards to the strain of the different implementations at  $V_{DD}=1.8~\rm V$  and  $V_{bias}=1.2~\rm V$ , i.e. the  $\beta$ -multiplier with resistor  $(\beta_R)$ , the full-transistor  $\beta$ -multipliers with positive  $(\beta_+)$  and negative  $(\beta_-)$  strain responses and the current subtraction implementation  $(\beta_{sub})$ . The gauge factors extracted from the measurements are written next to the curves. The dashed lines represent the theoretical results obtained with the piezoresistive coefficients inserted in the analytical relations.

Figure 9: Output current with regards to the temperature of the different implementations at  $V_{DD}=1.8~\rm V$  and  $V_{bias}=1.2~\rm V$ , i.e. the  $\beta$ -multiplier with resistor  $(\beta_R)$ , the full-transistor  $\beta$ -multipliers with positive  $(\beta_+)$  and negative  $(\beta_-)$  strain responses and the current subtraction implementation  $(\beta_{sub})$ . The temperature sensitivities extracted from the measurements are written next to the curves. The dashed lines represent the theoretical results obtained by simulation using the spice model of the UMC180 transistors given by the UMC foundry.

The dashed curves represent the theoretical results obtained by simulations for the temperature data and analytically for the strain results. The simulations are made using the spice model given by the UMC foundry for the UMC180 transistors while the strain impact is computed by injecting the piezoresistive coefficients found (cfr. Table 2) in relations (6) and (7).

#### 3.3.1. $\beta$ -multiplier with resistor (Fig. 2.a)

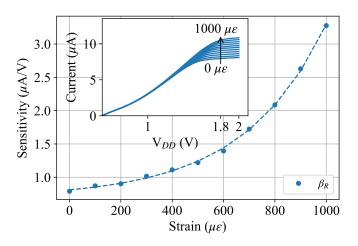

Figure 10: Output current sensitivity to supply voltage of the  $\beta$ -multiplier with resistor ( $\beta_R$ ) with regards to the applied strain. The inset represents the raw results with the arrow at the supply voltage where the sensitivity is computed (1.8 V).

Figure 11: Output current sensitivity to supply voltage of the  $\beta$ -multiplier with resistor ( $\beta_R$ ) with regards to the temperature. The inset represents the raw results with the arrow at the supply voltage where the sensitivity is computed (1.8 V).

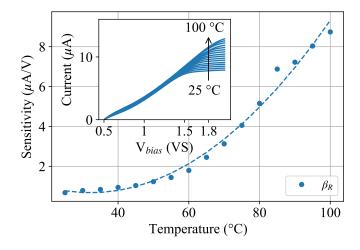

The implementation  $\beta_R$  shows a gauge factor of 324 (2.59 nA/ $\mu\epsilon$ ) and temperature sensitivity of 52.06 nA/°C with a supply voltage of 1.8 V. The sensitivity to supply voltage of the implementation is investigated in Fig. 10. A sensitivity of 0.79  $\mu$ A/V is obtained in the relaxed case. The sensitivity increased with the strain due to the voltage limit to keep the transistors in saturation regime being closer to the operating voltage of 1.8 V. Under high strain condition of 1000  $\mu\epsilon$ , the sensitivity is up to 3.28  $\mu$ A/V. The effect of the temperature on the supply sensitivity presents the same behavior and is displayed in Fig. 11. We

obtained a sensitivity of  $0.79 \,\mu\text{A/V}$  at  $25^{\circ}\text{C}$  that increases up to  $8.74 \,\mu\text{A/V}$  at  $100^{\circ}\text{C}$ . The cascode implementation allows low supply sensitivity but brings the bias limit of the circuit close to the operating point.

# 3.3.2. $\beta$ -multiplier with active load (Fig. 2.b) and subtraction circuit (Fig. 3)

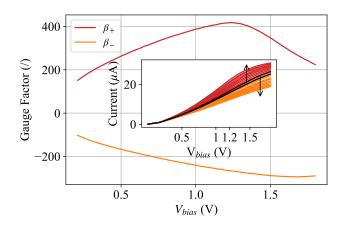

Figure 12: Gauge factor computed according to the bias voltage for the full-transistor implementations in strong inversion with positive  $(\beta_+)$  and negative  $(\beta_-)$  responses. The inset presents the raw I-V results with the arrow indicating the direction of the strain increase from 0 to  $1000~\mu\epsilon$ .

Figure 13: Gauge factor computed according to the bias voltage for the full-transistor current subtraction implementation ( $\beta_{sub}$ ) in strong inversion. The inset presents the raw I-V results with the arrow indicating the direction of the strain increase from 0 to 1000  $\mu\epsilon$ .

The implementation  $\beta_-$  and  $\beta_+$  show a gauge factor of -263 (-4.37 nA/ $\mu\epsilon$ ) and 415 (6.47 nA/ $\mu\epsilon$ ) depending on the transistor orientation while the temperature sensitivities are -34.09 nA/°C and -47.74 nA/°C, respectively.

The active load allows a current control by tuning the bias voltage. As consequence, the strain and temperature sensitivities of the output current depend on the voltage applied. The gauge factor variations according to the bias voltage is shown in Fig. 12. A maximum gauge factor of 415 (resp. -290) around 1.2 V (resp. 1.6 V) is found for  $\beta_+$  (resp.  $\beta_-$ ) implementation. At higher bias voltage, the current flowing through the devices

increases the gate voltage of the current mirrors. This bring the transistors into the triode regime and degraded the gauge factor of the circuit.

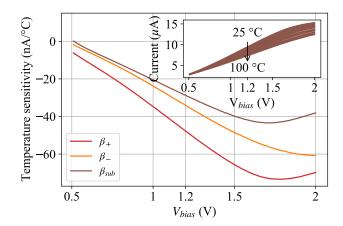

Figure 14: Temperature sensitivity according to the bias voltage for full-transistor implementations in strong inversion, i.e.  $\beta$ -multiplier with positive  $(\beta_+)$  and negative  $(\beta_-)$  strain response combined with a current subtraction circuit  $(\beta_{sub})$ . The inset shows the raw I-V curves of the measurements for the current of  $\beta_{sub}$ .

The temperature sensitivity depending on the bias voltage is represented in Fig. 14. At 1.2 V, sensitivities of -47.74 nA/°C and -34.09 nA/°C are obtained for the output currents of  $\beta_+$  and  $\beta_-$ , respectively.

The circuit with current subtraction  $\beta_{sub}$  presents the highest factor with 1773 (12.02 nA/ $\mu\epsilon$ ) and a temperature sensitivity of -28.72 nA/°C for a bias voltage of 1.2 V. The gauge factor of the current subtraction circuit is displayed in Fig. 13.

As the temperature sensitivities are both negative for  $\beta_+$  and  $\beta_-$  circuits, the current subtraction leads to lower temperature sensitivity. On top of that, we obtained strain sensitivity nearly three times higher.

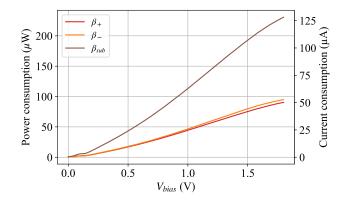

Figure 15: Power and current consumption according to the bias voltage for full-transistor implementations, i.e.  $\beta$ -multiplier with positive ( $\beta_+$ ) and negative ( $\beta_-$ ) strain response combined with a current subtraction circuit ( $\beta_{sub}$ ).

The improvement of the performances is however counterbalanced by the larger power consumption of 145.45  $\mu$ W. It is possible to reduce the current consumption (and therefore the power consumed) of the circuit by reducing the bias voltage as

| Implementation                             | $\beta_R$ | $eta_+$ | $\beta_{-}$ | $\beta_{sub}$ |

|--------------------------------------------|-----------|---------|-------------|---------------|

| Strain sensitivity ( $nA/\mu\varepsilon$ ) | 2.59      | 6.47    | -4.37       | 12.02         |

| Gauge Factor (/)                           | 324       | 415     | -263        | 1773          |

| Temperature sensitivity (nA/°C)            | 52.06     | -47.74  | -34.09      | -28.72        |

| Power Consumption $(\mu W)$                | 28.6      | 56.96   | 60.02       | 145.45        |

Table 3: Summary of the main performances at  $V_{DD} = 1.8$  V and  $V_{bias} = 1.2$  V of the different implementations, i.e. the  $\beta$ -multiplier with resistor ( $\beta_R$ ), the full-transistor  $\beta$ -multipliers with positive ( $\beta_+$ ) and negative ( $\beta_-$ ) strain responses and the current subtraction implementation ( $\beta_{sub}$ ).

displayed in Fig. 15. Indeed, a consumption of around 50  $\mu$ W can for example be obtained with a bias voltage of 0.5 V but with a gauge factor of around 1200 instead of 1773.

Table 3 summarizes the performances of the different implementations. The modifications of the  $\beta_R$  implementation allow for reaching higher strain sensitivity and gauge factor (from 324 to 1773) at the cost of higher power consumption (from 28.6  $\mu$ W to 145  $\mu$ W). Furthermore, the more advanced solution  $\beta_{sub}$  also shows better temperature sensitivity compared with the basic reference circuit (from 52.06 nA/°C to -28.72 nA/°C).

#### 4. Conclusion

In this work, we developed a new strain sensor based on  $\beta$ -multiplier topology in order to reduce the device sensitivity to supply voltage. The piezoresistive effect in silicon is exploited directly in the elements composing the circuit. This allows the circuit to work directly as the sensing element, leading to high performances and easy-to-measure output. We presented a reference circuit adapted for strain sensing applications by changing the relative orientations of the transistors. The strain impact on the reference currents is analytically described and verified with the experimental results. The theoretical methodology developed shows the possibility to easily compute the strain impact in reference circuit. The analytical work should allow further predictions of the performances of the circuit depending on the elements and device orientations.

The transistors used in the circuits were first characterized to predict the response of the different implementations. The basic topology with resistor gives a strain sensitivity of 2.54 nA/ $\mu\epsilon$  (gauge factor of 324) with a low power consumption of 28.6  $\mu$ W. The temperature sensitivity was 52.06 nA/°C. This solution was improved with full-transistor implementation combined in a current subtraction circuit. This leads to high strain sensitivity of 12.02 nA/ $\mu\epsilon$  (gauge factor of 1773) but at the cost of higher power consumption of 145.45  $\mu$ W. The temperature sensitivity was lower down to -28.72 nA/°C with the subtraction principle. Furthermore, the full-transistor principle allows to tune the performances of the circuit with a gauge factor between 800 and 1800 for a power consumption between 20 and 200  $\mu$ W.

#### Appendix A. Output current in $\beta$ -multiplier with resistor

By applying Kirchhoff's voltage law on the resistor and NMOS transistors  $M_1$  and  $M_2$  from Fig. 2.a, the following relation is obtained

$$V_{GS.1} = V_{GS.2} + RI_{D.2}. (A.1)$$

where  $V_{GS,i}$  and  $I_{D,i}$  stand for the gate-to-source voltage and drain current of transistor  $M_i$ , respectively. If the transistors are working in saturation and by neglecting the Early effect,  $V_{GS,i}$  is given by

$$V_{GS,i} = V_{n,i}^{th} + \sqrt{\frac{2I_{D,i}}{\beta_{n,i}(\sigma)}}, \tag{A.2}$$

where  $V_{n,i}^{th}$  is the threshold voltage of transistor i and  $\beta_{j,i}(\sigma) = \left(\frac{W}{L}\right)_i \mu_{n,i} C_{ox}$  with j standing for the electrons (n) or holes (p) contribution. At the level of the PMOS transistors  $M_3$  and  $M_4$ , the current mirror configuration gives

$$\begin{cases} V_{SG,3} = V_{SG,4} \\ I_{D,2} = I_{D,4} \\ I_{D,3} = I_{D,1} \end{cases} \Rightarrow \frac{I_{D,1}}{\beta_{p,3}(\sigma)} = \frac{I_{D,2}}{\beta_{p,4}(\sigma)}. \quad (A.3)$$

The currents of the transistors  $M_3$  and  $M_1$  are equal, the same goes for transistors  $M_2$  and  $M_4$ .

Substituting relations (A.2) and (A.3) in relation (A.1), we obtain

$$V_{n,2}^{th} + \sqrt{\frac{2I_{D,2}}{\beta_{n,2}(\sigma)}} + RI_{D,2} = V_{n,1}^{th} + \sqrt{\frac{2I_{D,2}}{\beta_{n,1}(\sigma)}} \frac{\beta_{p,3}(\sigma)}{\beta_{p,4}(\sigma)},$$

(A.4)

$$RI_{D,2} - \sqrt{I_{D,2}} \underbrace{\sqrt{2} \left( \sqrt{\frac{\beta_{p,3}(\sigma)}{\beta_{p,4}(\sigma)\beta_{n,1}(\sigma)}} - \frac{1}{\sqrt{\beta_{n,2}(\sigma)}} \right)}_{f(\sigma)} + \Delta V_n^{th} = 0,$$

$$\sqrt{I_{D,2}} = \frac{f(\sigma) \pm \sqrt{f(\sigma)^2 + 4R\Delta V_n^{th}}}{2R}.$$

(A.5)

By assuming no threshold voltage mismatch between the transistors, i.e.  $\Delta V_n^{th} = 0$ , we obtain

$$I_{D,2} = \begin{cases} 0\\ \frac{f(\sigma)^2}{R^2} \end{cases} . \tag{A.6}$$

Equation (A.6) shows two solutions for the current  $I_{D,2}$ . In order to avoid the zero-current solution, a start-up circuit is thus needed.

Using relation (3), the current is given by

$$I_{D,2} = \frac{2\left(\sqrt{\frac{\beta_{p,3}(\sigma)}{\beta_{p,4}(\sigma)\beta_{n,1}(\sigma)}} - \frac{1}{\sqrt{K_{21}\beta_{n,2}(\sigma)}}\right)^{2}}{R^{2}}.$$

(A.7)

We used the exponential relation for the gain, i.e.  $\beta(\sigma) = \beta^0 \cdot e^{-\pi\sigma}$ , to find

$$I_{D,2} = 2 \frac{\left(e^{-(\pi_3 - \pi_1 - \pi_4)\frac{\sigma}{2}} - e^{\pi_2 \frac{\sigma}{2}} / \sqrt{K_{21}}\right) e^{-2\pi_r \sigma}}{R^2 \beta^0}, \quad (A.8)$$

with  $\beta^0 = \beta_{n,1}(\sigma=0) = \beta_{p,3}(\sigma=0) = \beta_{p,4}(\sigma=0) = \frac{\beta_{n,2}(\sigma=0)}{K_{21}}$ .  $\pi_i$  is the piezoresistive coefficient of transistor  $M_i$  and  $\pi_r$  is the one of the resistor.

In the absence of strain, we find the classical expression for the reference current of the  $\beta$ -multiplier:

$$I_{D,2} = 2\frac{\left(1 - 1/\sqrt{K_{21}}\right)}{R^2 \beta^0}.$$

(A.9)

#### Appendix B. Output current in full-transistor $\beta$ -multiplier

A similar development than in Appendix Appendix A can be done for the full-transistor circuit. In this case, the resistor is replaced by a transistor  $(M_9)$  in triode region as displayed in Fig. 2.

By Kirchhoff's law and the saturation current relation (by neglecting the Early effect)

$$V_{GS,1} = V_{GS,2} + V_{DS,9} (B.1)$$

$$\sqrt{\frac{2I_{D,1}}{\beta_{n,1}(\sigma)}} + V_{n,1}^{th} = \sqrt{\frac{2I_{D,2}}{\beta_{n,2}(\sigma)}} + V_{n,2}^{th} + V_{DS,9} \quad (B.2)$$

$$V_{DS,9} = V_{GS,9} - V_{n,9}^{th} \pm \sqrt{(V_{GS,9} - V_{n,9}^{th})^2 - \frac{2I_{D,9}}{\beta_{n,9}}}.$$

(B.3)

By using the exponential law for the gain, i.e.  $\beta = \beta^0 \cdot e^{-\pi \sigma}$

$$\sqrt{\frac{2I_{D,2}}{\beta^0}} \underbrace{\left(\sqrt{\frac{e^{-(\pi_3 - \pi_4)\sigma}}{e^{-\pi_1\sigma}}} - \frac{1}{\sqrt{K_{21}e^{-\pi_2\sigma}}}\right) - \underbrace{\left(V_{n,2}^{th} - V_{n,1}^{th}\right)}_{\Delta V_n^{th}}}_{f(K_{21},\sigma)} = V_{ov,9} \pm \sqrt{(V_{ov,9})^2 - \frac{2I_{D,9}}{\beta_{n,9}}}. \quad (B.4)$$

with  $V_{ov,i} = V_{GS,i} - V_{n,i}^{th}$ .

The equation is put to the square a first time, giving

$$\frac{2I_{D,2}}{\beta^0} f(K_{21}, \sigma)^2 - \Delta V_n^{th}$$

$$= (V_{ov,9})^2 \pm 2(V_{ov,9}) \sqrt{(V_{ov,9})^2 - \frac{2I_{D,9}}{\beta_{n,9}}} + V_{ov,9} - \frac{2I_{D,9}}{\beta_{n,9}}. \quad (B.5)$$

with  $I_{D,2} = I_{D,9}$  and  $\beta^0 = \beta_{n1}^0 = \frac{\beta_{9}^0}{K_{91}}$ , expression (B.5) can be expressed as

$$\frac{2I_{D,2}}{\beta^{0}} \underbrace{\left(f(K_{21},\sigma)^{2} + \frac{1}{K_{91}e^{-\pi_{9}\sigma}}\right)}_{g(K_{21},K_{91},\sigma)} - \Delta V_{n}^{th} - (V_{ov,9})^{2}$$

$$= \pm 2(V_{ov,9}) \sqrt{(V_{ov,9})^{2} - \frac{2I_{D,9}}{\beta_{n,9}}} + V_{ov,9} - \frac{2I_{D,2}}{K_{91}\beta^{0}e^{-\pi_{9}\sigma}}. \quad (B.6)$$

We have a second-order equation for  $I_{D2}$  by elevating equation (B.6) to the square a second time:

$$4\frac{I_{D,2}^{2}}{(\beta^{0})^{2}}g(K_{21}, K_{91}, \sigma)^{2} + (-\Delta V_{n}^{th} - 2(V_{ov,9})^{2})^{2}$$

$$+ 4\frac{I_{D,2}}{\beta^{0}}g(K_{21}, K_{91}, \sigma)(-\Delta V_{n}^{th} - 2(V_{ov,9})^{2})$$

$$= 4(V_{ov,9})^{2}((V_{ov,9})^{2} - \frac{2I_{D,2}}{\beta^{0}}), \quad (B.7)$$

$$(I_{D,2})^{2} \underbrace{\left[\frac{4}{(\beta^{0})^{2}}g(K_{21}, K_{91}, \sigma)^{2}\right]}_{A} + I_{D2}.$$

$$\underbrace{\left[\frac{4}{\beta^{0}}g(K_{21}, K_{91}, \sigma)(-\Delta V_{n}^{th} - 2(V_{ov,9})^{2}) + 8\frac{(V_{ov,9})^{2}}{K_{91}\beta^{0}e^{-\pi_{9}\sigma}}\right]}_{B}$$

$$+\underbrace{\left[(-\Delta V_{n}^{th} - 2(V_{ov,9})^{2})^{2} - 4(V_{ov,9})^{4}\right]}_{C} = 0, \quad (B.8)$$

$$I_{ref} = I_{D2} = \frac{-B \pm \sqrt{B^2 - 4AC}}{2A}.$$

(B.9)

By neglecting the threshold voltage mismatch, C becomes zero. Again, two solutions are obtained with the zero-current one. A start-up circuit is thus needed for this circuit too. The

non-zero solution is given by

$$I_{D,2} = \frac{-B \pm \sqrt{B^2}}{2A}$$

(B.10)

$$=\frac{-B}{A} \tag{B.11}$$

$$=\frac{-\left[\frac{4}{\beta^{0}}g(K_{21},K_{91},\sigma)(-2(V_{ov,9})^{2})+8\frac{(V_{ov,9})^{2}}{K_{91}\beta^{0}e^{-\pi_{9}\sigma}}\right]}{\frac{4}{(\beta^{0})^{2}}g(K_{21},K_{91},\sigma)^{2}}$$

(B.12)

$$=2\frac{(V_{ov,9})^2\beta^0\left(g(K_{21},K_{91},\sigma)-\frac{1}{K_{91}e^{-\pi_9\sigma}}\right)}{g(K_{21},K_{91},\sigma)^2}$$

(B.13)

$$= 2(V_{ov,9})^2 \beta^0 \frac{\left(\sqrt{\frac{e^{-(\pi_3 - \pi_4)\sigma}}{e^{-\pi_1\sigma}}} - \frac{1}{\sqrt{K_{21}e^{-\pi_2\sigma}}}\right)^2}{\left[\left(\sqrt{\frac{e^{-(\pi_3 - \pi_4)\sigma}}{e^{-\pi_1\sigma}}} - \frac{1}{\sqrt{K_{21}e^{-\pi_2\sigma}}}\right)^2 + \frac{1}{K_{91}e^{-\pi_9\sigma}}\right]^2}.$$

(B.14)

The reference current can be expressed as

$$I_{D,2} = 2(V_{ov,9})^2 \beta_{n,0} \cdot \frac{1}{\left[e^{-(\pi_3 - \pi_4 - \pi_1)\frac{\sigma}{2}} - \frac{e^{\pi_2}\frac{\sigma}{2}}{\sqrt{K_{21}}} + \frac{1}{\left(e^{-(\pi_3 - \pi_4 - \pi_1)\frac{\sigma}{2}} - \frac{e^{\pi_2}\frac{\sigma}{2}}{\sqrt{K_{21}}}\right) K_{91}e^{-\pi_9\sigma}}\right]^2}.$$

(B.15)

#### References

- H. Cao, S. K. Thakar, M. L. Oseng, C. M. Nguyen, C. Jebali, A. B. Kouki, J. C. Chiao, Development and Characterization of a Novel Inter-digitated Capacitive Strain Sensor for Structural Health Monitoring, IEEE Sensors Journal 15 (11) (2015) 6542–6548. doi:10.1109/JSEN.2015.2461591.

- URL http://ieeexplore.ieee.org/document/7169510/

- [2] A. Downey, S. Laflamme, F. Ubertini, Distributed thin film sensor array for damage detection and localization, in: J. P. Lynch (Ed.), Proceedings of SPIE - The International Society for Optical Engineering, Vol. 9803, Department of Civil, Construction, and Environmental Engineering, Iowa State University, Ames, IA, United States, 2016, p. 98030R. doi:10.1117/12.2219301.

- URL http://proceedings.spiedigitallibrary.org/

proceeding.aspx?doi=10.1117/12.2219301

- [3] Z. J. Chew, T. Ruan, M. Zhu, M. Bafleur, J.-M. Dilhac, Single Piezoelectric Transducer as Strain Sensor and Energy Harvester Using Time-Multiplexing Operation, IEEE Transactions on Industrial Electronics 64 (12) (2017) 9646–9656. doi:10.1109/TIE.2017.2711562.

- [4] T. Yamashita, S. Takamatsu, H. Okada, T. Itoh, T. Kobayashi, Ultra-Thin Piezoelectric Strain Sensor Array Integrated on a Flexible Printed Circuit Involving Transfer Printing Methods, IEEE Sensors Journal 16 (24) (2016) 8840–8846. doi:10.1109/JSEN.2016.2578936.

- [5] S. Liehr, K. Krebber, Application of quasi-distributed and dynamic length and power change measurement using optical frequency domain reflectometry, IEEE Sensors Journal 12 (1) (2012) 237–245. doi:10.1109/ JSEN.2011.2157126.

- [6] Y. Guo, J. Kong, H. Liu, D. Hu, L. Qin, Design and Investigation of a Reusable Surface-Mounted Optical Fiber Bragg Grating Strain Sensor, IEEE Sensors Journal 16 (23) (2016) 8456–8462. doi:10.1109/JSEN. 2016.2614009.

- [7] K. Y. Song, Z. He, K. Hotate, Distributed strain measurement with millimeter-order spatial resolution based on Brillouin optical correlation domain analysis, Optics Letters 31 (17) (2006) 2526–2528. doi: 10.1364/0L.31.002526.

- URL https://www.osapublishing.org/ol/abstract.cfm?uri= ol-31-17-2526

- [8] A. Fiorillo, C. Critello, S. Pullano, Theory, technology and applications of piezoresistive sensors: A review, Sensors and Actuators A: Physical 281 (2018) 156-175. doi:https://doi.org/10.1016/j.sna.2018.07. 006.

- URL https://www.sciencedirect.com/science/article/pii/S0924424718308434

- V. Gridchin, V. Lubimsky, M. Sarina, Piezoresistive properties of polysilicon films, Sensors and Actuators A: Physical 49 (1) (1995) 67-72. doi:https://doi.org/10.1016/0924-4247(95)01013-Q. URL https://www.sciencedirect.com/science/article/pii/0924424795010130

- [10] D. Zymelka, K. Togashi, R. Ohigashi, T. Yamashita, S. Takamatsu, T. Itoh, T. Kobayashi, Printed strain sensor array for application to structural health monitoring, Smart Materials and Structures 26 (10). doi: 10.1088/1361-665X/aa8831.

- [11] S. Pettinato, D. Barettin, V. Sedov, V. Ralchenko, S. Salvatori, Fabry-perot pressure sensors based on polycrystalline diamond membranes, Materials 14 (7). doi:10.3390/ma14071780.

URL https://www.mdpi.com/1996-1944/14/7/1780

- [12] J. X. Zhang, K. Hoshino, Chapter 6 mechanical transducers: Cantilevers, acoustic wave sensors, and thermal sensors, in: J. X. Zhang, K. Hoshino (Eds.), Molecular Sensors and Nanodevices (Second Edition), second edition Edition, Micro and Nano Technologies, Academic Press, 2019, pp. 311–412. doi:https://doi.org/10.1016/B978-0-12-814862-4.00006-5.

- URL https://www.sciencedirect.com/science/article/pii/B9780128148624000065

- [13] S. A. Jabir, N. K. Gupta, Condition monitoring of the strength and stability of civil structures using thick film ceramic sensors, Measurement 46 (7) (2013) 2223-2231. doi:https://doi.org/10.1016/j. measurement.2013.03.018. URL https://www.sciencedirect.com/science/article/pii/

- S0263224113000857 [14] T. P. Delhaye, N. André, L. A. Francis, D. Flandre, New universal figure

- of merit for embedded si piezoresistive pressure sensors, IEEE Sensors Journal 21 (1) (2021) 213–221. doi:10.1109/JSEN.2020.3013017.

- [15] Q. Zheng, J. hun Lee, X. Shen, X. Chen, J.-K. Kim, Graphene-based wearable piezoresistive physical sensors, Materials Today 36 (2020) 158– 179. doi:https://doi.org/10.1016/j.mattod.2019.12.004. URL https://www.sciencedirect.com/science/article/pii/ S1369702119308776

- [16] K. Ke, V. Solouki Bonab, D. Yuan, I. Manas-Zloczower, Piezoresistive thermoplastic polyurethane nanocomposites with carbon nanostructures, Carbon 139 (2018) 52–58. doi:10.1016/j.carbon.2018.06.037.

- [17] G. Fisher, M. R. Seacrist, R. W. Standley, Silicon crystal growth and wafer technologies, Proceedings of the IEEE 100 (Special Centennial Issue) (2012) 1454–1474. doi:10.1109/JPROC.2012.2189786.

- [18] A. Taroni, M. Prudenziati, G. Zanarini, Semiconductor sensors: Ii—piezoresistive devices, IEEE Transactions on Industrial Electronics and Control Instrumentation IECI-17 (6) (1970) 415–421. doi:10. 1109/TIECI.1970.230445.

- [19] E. Vittoz, J. Fellrath, Cmos analog integrated circuits based on weak inversion operations, IEEE Journal of Solid-State Circuits 12 (3) (1977) 224–231. doi:10.1109/JSSC.1977.1050882.

- [20] S. Liu, R. Baker, Process and temperature performance of a cmos betamultiplier voltage reference, in: 1998 Midwest Symposium on Circuits and Systems (Cat. No. 98CB36268), 1998, pp. 33–36. doi:10.1109/ MWSCAS.1998.759429.

- [21] G. K. Johns, Modeling piezoresistivity in silicon and polysilicon, Journal of Applied Engineering Mathematics April 2 (2006) 1–5.

- [22] Z. D. Jastrzebski, R. Komanduri, The Nature and Properties of Engineering Materials, Journal of Engineering Materials and Technology 110 (3) (1988) 294. doi:10.1115/1.3226051. URL https://doi.org/10.1115/1.3226051

- [23] M. A. Hopcroft, W. D. Nix, T. W. Kenny, What is the Young's Modulus of Silicon?, Journal of Microelectromechanical Systems 19 (2) (2010) 229–238.

- [24] Y. Tan, X. Li, L. Tian, Z. Yu, Analytical electron-mobility model for arbitrarily stressed silicon, IEEE Transactions on Electron Devices 55 (6) (2008) 1386–1390. doi:10.1109/TED.2008.921074.

- [25] Y. Kanda, A graphical representation of the piezoresistance coefficients

- in silicon, IEEE Transactions on Electron Devices 29 (1) (1982) 64–70. doi:10.1109/T-ED.1982.20659.

- URL http://ieeexplore.ieee.org/document/1482156/

- [26] C. S. Smith, Piezoresistance effect in germanium and silicon, Phys. Rev. 94 (1954) 42-49. doi:10.1103/PhysRev.94.42.

URL https://link.aps.org/doi/10.1103/PhysRev.94.42

- [27] B. Rue, B. Olbrechts, J.-P. Raskin, D. Flandre, A SOI CMOS smart strain sensor, in: IEEE 2011 International SOI Conference, no. 0, IEEE, 2011, pp. 1–2. doi:10.1109/SOI.2011.6081791. URL http://ieeexplore.ieee.org/document/6081791/

- [28] R. Jaeger, R. Ramani, J. Suhling, Y. Kang, Cmos stress sensor circuits using piezoresistive field-effect transistors (pifets), in: Digest of Technical Papers., Symposium on VLSI Circuits., 1995, pp. 43–44. doi:10.1109/ VLSIC.1995.520680.

- [29] R. Jaeger, J. Suhling, R. Ramani, A. Bradley, J. Xu, Cmos stress sensors on [100] silicon, IEEE Journal of Solid-State Circuits 35 (1) (2000) 85– 95. doi:10.1109/4.818923.

- [30] S. Tang, S. Narendra, V. De, Temperature and process invariant mosbased reference current generation circuits for sub-1v operation, in: Proceedings of the 2003 International Symposium on Low Power Electronics and Design, 2003. ISLPED '03., 2003, pp. 199–204. doi:10.1109/ LPE.2003.1231862.

- [31] R. Beaty, R. Jaeger, J. Suhling, R. Johnson, R. Butler, Evaluation of piezoresistive coefficient variation in silicon stress sensors using a fourpoint bending test fixture, IEEE Transactions on Components, Hybrids, and Manufacturing Technology 15 (5) (1992) 904–914. doi:10.1109/ 33.180057.

- [32] K. O. Jeppson, Three- and four-point Hamer-type MOSFET parameter extraction methods revisited, IEEE International Conference on Microelectronic Test Structures (4) (2013) 141–145. doi:10.1109/ICMTS. 2013.6528161.

- [33] R. C. Jaeger, J. C. Suhling, First and Second Order Piezoresistive Characteristics of CMOS FETs: Weak through Strong Inversion, in: 2018 48th European Solid-State Device Research Conference (ESSDERC), IEEE, 2018, pp. 126–129. doi:10.1109/ESSDERC.2018.8486881. URL https://ieeexplore.ieee.org/document/8486881/

- [34] N. Wacker, H. Richter, M.-U. Hassan, H. Rempp, J. N. Burghartz, Compact modeling of CMOS transistors under variable uniaxial stress, Solid-State Electronics 57 (1) (2011) 52–60. doi:10.1016/j.sse.2010.12.003.

- URL https://linkinghub.elsevier.com/retrieve/pii/S0038110110004235

- [35] A. Bradley, R. Jaeger, J. Suhling, K. O'Connor, Piezoresistive characteristics of short-channel MOSFETs on (100) silicon, IEEE Transactions on Electron Devices 48 (9) (2001) 2009–2015. doi:10.1109/16.944190. URL http://ieeexplore.ieee.org/document/944190/

Nicolas Roisin received the M.S. degree from the University of Louvain, Louvain-la-Neuve, Belgium, in 2019, where he is currently pursuing the Ph.D. degree with the Institute of Information and Communication Technologies, Electronics and Applied Mathematics (ICTEAM). His research topics are oriented towards strained silicon in sensing and optical applications.

Thibault Delhaye received the M.S. degree from the University of Louvain, Louvain-la-Neuve, Belgium, in 2015, where he is currently pursuing the Ph.D. degree with the Institute of Information and Communication Technologies, Electronics and Applied Mathematics (ICTEAM). He was a Visiting International Research Student with The University of British Columbia, Canada, in fall

2018. His research topic is on highly sensitive and ultra-low-power MEMS pressure sensor based on SOI technology.

Nicolas André received the M.S. degree in electrical engineering from the Louvain School of Engineering, Université Catholique de Louvain (UCL), Louvain-la-Neuve, Belgium, in 2004, and the Ph.D. degree in applied sciences in the field of microelectromechanical systems (MEMS) co-integration from UCL in 2011. From 2011 to 2012, he was with UdeS, Sherbrooke, Canada, as

a Postdoctoral Researcher on bio-inspired methods to improve the LED efficiency. He has coauthored more than 100 research articles in international journals and holds two patents. He was a team member in several Walloon, FEDER, and EU projects as STARFLO+, FEDER MINATIS, and MICRO+. His expertise is about microfabrication and sensors (flow, humidity, pressure, and light) integrated with SOI CMOS Circuits.

Jean-Pierre Raskin (M'97–SM'06) received the M.S. and Ph.D. degrees in applied sciences from the Université catholique de Louvain, Louvain-la-Neuve, Belgium, in 1994 and 1997, respectively. He was a Visiting Professor with Newcastle University, Newcastle upon Tyne, U.K., from 2009 to 2010. His research interests are the modeling, wideband

characterization, and fabrication of advanced SOI MOSFETs as well as micro and nanofabrication of MEMS/NEMS sensors and actuators, including the extraction of intrinsic material properties at nanometer scale.

Denis Flandre received the M.S. degree in electrical engineering, and the Ph.D. and Research Habilitation degrees from the Université catholique de Louvain (UCL), Louvain-la-Neuve, Belgium, in 1986, 1990 and 1999, respectively. His doctoral research was on the modeling of Silicon-on-Insulator (SOI) MOS devices for characterization and circuit simulation, his Postdoc-

toral thesis on a systematic and automated synthesis methodology for MOS analog circuits. Since 2001, he has been a full-time Professor with UCL. He has participated or coordinated numerous research projects funded by regional and European institutions. He has organized or lectured many short courses on SOI technology, devices and circuits in universities, industrial companies, and conferences. He has authored or coauthored more than 1000 technical papers or conference contributions. He is a Co-Inventor of 11 patents. He is currently involved in the research and development of SOI MOS devices, digital and analog circuits, as well as sensors and MEMS, for special applications, more specifically high-speed, low-voltage low-power, microwave, biomedical, radiation-hardened, and high-temperature electronics and microsystems.