# Parameter Conditions to Prevent Voltage Oscillations Caused by LTC-Inverter Hunting on Power Distribution Grids

Jaimie Swartz<sup>1</sup>, Federico Celi<sup>2</sup>, Fabio Pasqualetti<sup>2</sup>, and Alexandra von Meier<sup>1</sup>

Abstract—As more distributed energy resources (DERs) are connected to the power grid, it becomes increasingly important to ensure safe and effective coordination between legacy voltage regulation devices and inverter-based DERs. In this work, we show how a distribution circuit model, composed of two LTC's and two inverter devices, can create voltage oscillations even with reasonable choices of control parameters. By modeling the four-device circuit as a switched affine hybrid system, we analyze the system's oscillatory behavior, both during normal operation and after a cyber-physical attack. Through the analysis we determine the specific region of the voltage state space where oscillations are possible and derive conditions on the control parameters to guarantee against the oscillations. Finally, we project the derived parameter conditions onto 2D spaces, and describe the application of our problem formulation to grids with many devices.

#### I. INTRODUCTION

The traditional voltage regulation problem is to design load-tap changer (LTC), voltage regulator, and capacitor bank control parameters such that, over a minutes-to-day duration, the distribution grid voltage is kept within 5% of the nominal voltage (ANSI C84.1 standard) to avoid interrupting or damaging customer equipment. The addition of naively controlled DERs such as solar PV makes this voltage regulation problem harder [1] and can cause LTCs to actuate much more frequently, reducing their lifespan. Depending on the control logic and design parameters, connecting smart inverters can either alleviate [2] these voltage fluctuations or be a source of adverse interactions [3].

One type of adverse interaction is *device hunting* which we define as one or more devices actuating in a repeated sequence that results in periodic voltage oscillations. Hunting among LTCs has been observed by utilities since the 1980s [4], [5] and has been modeled as a hybrid system in the literature [5]. Inverter-based DERs may be able to solve these problems if their control parameters are set appropriately. However, current inverter standards [6] require inverter control parameters to be adjustable by a remote entity's communication network, which introduces a potential vulnerability to cyberattacks [7]. Bad parameters sent to inverters on a circuit, whether deliberately or by mistake, can trigger adverse interactions [8]. This motivates our investigation into

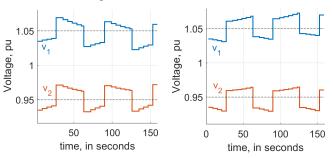

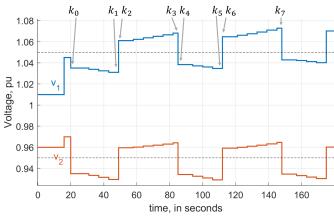

how a poor choice of device parameters can lead to hunting, as simulated in Fig. 1.

(a) Device hunting for g=0.7 (b) Device hunting for g=-0.5 Fig. 1: Simulation of two LTCs and two inverters that create voltage oscillations with a period of 140 seconds. Circuit is in Fig. 2 and parameters are the defaults listed in Table I.

Related work: There are two common approaches when selecting distribution-grid device parameters for voltage control: an approach based on rules of thumb followed by simulation, and an optimization-based approach. For basic operation of LTCs and parameter rules of thumb we refer to the text [9, Chapter 9.3], and to papers [1], [10]. One limitation of this approach is the assumed timescale separation between the LTC and inverters, which may not hold when LTCs delays are shortened to handle increased voltage variability [11]. Moreover, the simulations in these papers are not sufficient to guarantee against the possibility of sustained voltage oscillations.

Meanwhile, optimization methods focus on addressing the non-convexity of the mixed-integer optimal power flow problem resulting from including both continuous (smart inverter) and discrete (LTC and voltage regulator) dynamics [12], [13]. However, the optimal parameter solution determines tap positions and power dispatch rather than the device parameters in the control law. As such, the optimal solution does not provide significant insights into the symbolic relationship between control parameters and adverse interactions.

Our goal of deriving symbolic parameter conditions for hybrid systems stability is a challenging task and remains relatively unexplored in control systems literature. The design of switching strategies for stabilization commonly assumes one can switch modes at any time, rather than switching according to parameterized conditions [14], [15]. Linear parameter variation (LPV) literature commonly assumes the parameters to be time-varying, but here our parameters are time-independent and we want to solve for them symbolically [16]. Therefore, our methodology leverages our familiarity with the specific system's model dynamics.

<sup>\*</sup>This work supported in part by the U.S. Department of Energy, Award DE-EE0008008.

<sup>&</sup>lt;sup>1</sup>J. Swartz A. von Meier are with the Department and Engineering Electrical and Computer Science. University of California at Berkeley, Berkeley, California, USA {jaimie.swartz, vonmeier}@berkely.edu

<sup>&</sup>lt;sup>2</sup>F. Celi and F. Pasqualetti are with the Department of Mechanical Engineering, University of California at Riverside, Riverside, California, USA {fceli, fabiopas}@engr.ucr.edu

Paper contribution: We seek to analyze how parameters of LTCs and inverters prevent or contribute to voltage oscillations created by device hunting. The results yield two distinct benefits: (i) the parameter conditions can provide intuition for improving the rules of thumb used to operate these devices in industry and (ii) the conditions can be directly checked on each device without simulations, enabling real-time checks on incoming parameter updates by remote entities.

Paper Organization: The remainder of the paper is organized as follows. In Sec. II, the system equations are presented and the parameter condition problem is solved for two subsystems. In Sec. III, the parameter condition problem is solved for the full system. In Sec. IV the full system conditions are illustrated with parameter space plots and application of the work to larger systems is described. In Sec. V we lay out the conclusions and future work.

# II. SYSTEM DYNAMICS AND SUBSYSTEM ANALYSIS

#### A. Notation

Let  $\mathbb{R}^c$  be the c-dimensional vectors of real numbers. Given a time-varying vector x, we let x[k] be its value at time k, and  $x_i[k]$  be the value of the i-th element of x at time k. Let  $x^{\top}$  be the transpose of vector x. Let  $||.||_i$  denote the  $\ell_i$  vector norm for  $i=1,2,\infty$ . We define the  $margin\ M$  as the set of points x that are within distance d from a set S. That is,  $M(S,d) := \{x: \exists\ s_i \in S: \|x-s_i\|_2 \leq d\}$ . We define a partition of a set S to be a collection of subsets  $S_i$ , i=1,...k such that  $\bigcup_{i=1,...,k} S_i = S$  and  $S_i \cap S_j = \emptyset$  for all  $i \neq j$ . We use  $\to$  and  $\to$  to indicate possible and impossible transitions between partitions, respectively. Let S' denote the complement of set S, and S/Q be the set S that is not in Q.

# B. Overview of Four-Device System

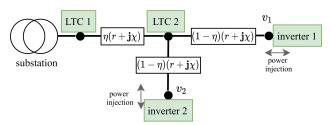

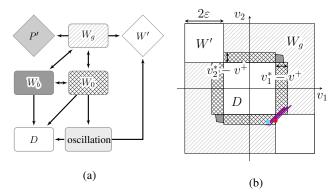

Fig. 2: Distribution circuit with LTC and inverter devices

We model four devices operating on the radial distribution circuit shown in Fig. 2. Suppose there are constant loads at all nodes shown. LTC1 and inverter1 regulate  $v_1$ , while LTC2 (sometimes called a line voltage regulator) and inverter2 regulate  $v_2$ . The LTCs monitor these voltages using line drop compensation, and the inverters monitors these voltages with their inverter voltage sensors. All devices operate with a fixed time delay logic; that is, they only respond when the voltage remains outside the deadband throughout a certain delay d. The goal is to coordinate the device action so that  $v_1$  and  $v_2$  land inside the deadband without device hunting.

Table I summarizes the notation for the states, fixed parameters, and symbolic parameters we are interested in designing to guarantee against hunting. The table also assumes relationships from basic operation of power systems that are drawn from [9, Chapter 9.3] and [17]. In the table,

all fixed and symbolic variables except for g are taken to be positive and real valued due to their physical meaning.

TABLE I: Notation and variable types

|             | type     | description           | default | relationship               |

|-------------|----------|-----------------------|---------|----------------------------|

| $v^{ref}$   | fixed    | voltage ref. (p.u.)   | 1.0     | _                          |

| ε           | fixed    | half of deadband      | 0.1     | deadband is                |

|             |          | width                 |         | $v^{ref} - \varepsilon$ to |

|             |          |                       |         | $v^{ref} + \varepsilon$    |

| χ           | fixed    | line reactance to the | 0.1     | _                          |

|             |          | substation (p.u.)     |         |                            |

| $\eta$      | fixed    | impedance damping     | 0.9     | $0 < \eta < 1$             |

|             |          | factor                |         |                            |

| $v_{10}$    | state    | node 2 initial volt-  | 1.035   | _                          |

|             |          | age (p.u.)            |         |                            |

| $v_{20}$    | state    | node 3 initial volt-  | 0.935   | -                          |

|             |          | age (p.u.)            |         |                            |

| $d_{inv}$   | symbolic | inverter 1 and 2 de-  | 4       | $d_{inv} < d_{L1}$         |

|             |          | lay (s)               |         |                            |

| $d_{L1}$    | symbolic | LTC1 delay (s)        | 30      | _                          |

| $d_{L2}$    | symbolic | LTC2 delay (s)        | 40      | $d_{L1} < d_{L2},$         |

|             |          |                       |         | $d_{L2} < 2d_{L1}$         |

| $\bar{v}_L$ | symbolic | tap voltage (p.u.)    | 0.03    | $\bar{v}_L < 2\varepsilon$ |

| g           | symbolic | inverter 1 and 2      | -       | -                          |

|             |          | control gain          |         |                            |

#### C. Conditions for two-LTC System

Let the  $\Sigma_1$  be the subsystem where only LTC1 and LTC2 act on the circuit in Fig. 2. Both devices have the same deadband width  $2\varepsilon$  that is centered on the same voltage reference  $v^{ref}$ . When the voltage is outside the deadband for  $d_{L1}$  ( $d_{L2}$ ) seconds, LTC1 (LTC2) taps, which updates both voltages according to  $v[k+1] = v[k] + [\bar{v}_L \ \bar{v}_L]^{\top}$  where  $v = [v_1 \ v_2]^{\top} \in \mathbb{R}^2$ . Because all tap actions shift both voltages by  $\bar{v}_L$  amount, tapping manifests as discrete jumps on the  $(v_1, v_2)$  space with slope of  $\pm 1$  between the initial and after-tap voltage.

We denote the upper deadband boundary as  $v^+ = v^{ref} + \varepsilon$ , and lower deadband boundary as  $v^- = v^{ref} - \varepsilon$ . Then we define the deadband as

$$D := \{(v_1, v_2) : v^- < v_1 < v^+, \ v^- < v_2 < v^+\}.$$

(1)

Because there are no active dynamics when both voltages are in the deadband, the set D is invariant. When  $v_i > v^+$  we say  $v_i$  has an *overvoltage*, and when  $v_i < v^-$  we say  $v_i$  has an *undervoltage*. With the shorthand  $v_i \in D$  or  $v_i \notin D$ , we refer to whether  $v^- < v_i < v^+$  is satisfied or not.

Next, we define

$$H := \{ (v_1, v_2) : (v_1 < v^- \text{ xor } v_2 > v^+) \text{ and }$$

$$(v_1 > v^+ \text{ xor } v_2 < v^-) \}$$

$$(2)$$

$$P := \{ (v_1, v_2) : \|v[k] - v^{ref}\|_{\infty} < 3\varepsilon \}.$$

(3)

The hourglass-shaped set H disallows one voltage from being above  $v^+$  when the other is below  $v^-$ . P bounds the distance each voltage can be away from  $v^{ref}$ . We define the system's normal operating states to be  $W \coloneqq (H \cap P)$ .

**Assumption 1.** All systems analyzed in this work  $(\Sigma_1, \Sigma_2, \Sigma_3)$  operate in normal operating states W.

We consider states outside W to be abnormal operating conditions that should be addressed with the grid's protection

system rather than the system dynamics analyzed in this work. We are interested in the system behavior while  $v \in W$ , especially if the initial condition (IC) starts in W and eventually leaves W.

**Lemma 1.** If  $\bar{v}_L > 2\varepsilon$ , system  $\Sigma_1$  will have marginally stable oscillations for all time when any  $v_1[0] \in M(D,c)$  or  $v_2[0] \in M(D,c)$  where  $c = \bar{v}_L - 2\varepsilon > 0$ .

Distribution engineers know not to set  $\bar{v}_L>2\varepsilon$  when choosing LTC settings, so next we focus on how oscillations could occur when  $\bar{v}_L\leq 2\varepsilon$ .

We partition W into four regions D,  $W_g$ ,  $W_b$ ,  $W_o$ , based on the possible trajectories from starting the system in each region. We define  $W_o$  such that from there we only transition to the deadband or oscillate. For example,  $v_1$  should satisfy  $v_1 - \bar{v}_L < v^+$ . Therefore we define the boundary of  $W_o$  in terms of the  $v_i^*$  that satisfies  $v_i^* - \bar{v}_L = v^+$  for i = 1, 2. This gives the regions

$$\begin{split} W_o &= \{(v_1,v_2) \in W : (v_1 \in M(D,v_1^* - v^+) \text{ and } v_2 \in D), \\ &\text{ or } (v_2 \in M(D,v_2^* - v^+) \text{ and } v_1 \in D)\}, \\ W_b &= \{(v_1,v_2) \in W : (v_1,v_2 > v^+ \text{ and } v_1 + v_2 \leq v^+ \\ &+ \bar{v}_L), \text{ or } (v_1,v_2 < v^- \text{ and } v_1 + v_2 \geq v^- - \bar{v}_L)\}, \end{split}$$

and  $W_g$  is what remains of W ( $W_g = W/(D \cup W_o \cup W_g)$ ).

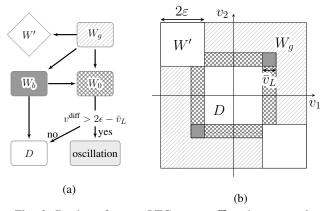

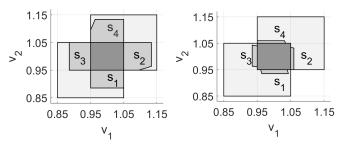

Fig. 3: Regions for two-LTC system  $\Sigma_1$  when  $\bar{v}_L < 2\varepsilon$ .

Fig. 3 shows these regions in the state space as well as the possible transitions between regions  $W_g, W_o, W_b, D, W'$ , and P'. For  $W_g$  possibilities, LTC jumps having a slope of  $\pm 1$  implies that  $W_g \nrightarrow P'$ . Because  $W_g$  is  $\bar{v}_L$  away from  $D, W_g \nrightarrow D$ . As such,  $W_g$  can only transition to  $W', W_b, W_o$ . For  $W_b$  possibilities, LTC jumps having a slope of  $\pm 1$  implies that  $W_b \nrightarrow P', W'$ , and  $W_g$ . As such,  $W_b$  can only transition to  $W_o$  or D. For  $W_o$  possibilities, LTC jumps having a slope of  $\pm 1$  implies that  $W_o \nrightarrow P', W_b$ , and  $W_g$ . As such,  $W_o$  can only transition to D or W'. Furthermore, from the geometry of Fig. 3, observe that if  $v^{\text{diff}}[0] < 2\varepsilon$ ,  $W_o \nrightarrow W'$ .

**Lemma 2.** If  $\bar{v}_L \leq 2\varepsilon$ ,  $v[T] \in W_o$ , and  $v^{diff} < 2\varepsilon - \bar{v}_L$ , system  $\Sigma_1$  will have marginally stable oscillations starting at time T.

A simulation of marginally stable oscillations due to Lemma 2 hunting is in Fig. 4.

Fig. 4: Simulation of system  $\Sigma_1$  when Lemma 2 holds. Parameters are the defaults listed in Table I.

# D. Conditions for 2-Inverter System

Let the  $\Sigma_2$  be the subsystem where only the two inverters act on the circuit in Fig. 2. For now we omit the deadband in the control logic. We employ a discrete integrator (also called incremental volt-var control in [17], [18]) for computing inverter power set-points with

$$q^{inv}[k+1] = q^{inv}[k] - G(v[k] - v^{ref}), \tag{5}$$

where G is a diagonal matrix containing integrator controller gains. G being diagonal enforces that each inverter is injecting power to regulate the voltage at its own node. For any radial circuit with n inverters at different nodes,  $v \in \mathbb{R}^n$  and  $q \in \mathbb{R}^n$ .

The algebraic power flow equations that map inverter power injections to voltages can be represented by

$$v[k+1] = v[k] + X(q^{inv}[k+1] - q^{inv}[k])$$

from [19, equation 8]. Matrix element  $X_{ij}$  is the common ancestor path reactance between node i and node j on the network. Next we substitute (5), giving

$$v[k+1] = v[k] - XG(v[k] - v^{ref}).$$

(6)

Finally, we subtract  $v^{ref}$  from both sides and define  $e[k]\coloneqq v[k]-v^{ref}$ . This gives

$$e[k+1] = (I - XG)e[k]$$

(7)

from [19, equation 12]. Because only a subset of the network nodes are controlled,  $v^{ref}$  can be assigned to the nominal vector of ones 1.

Author [19] proves in their Theorem 3.1 that for the system (7),  $v \rightarrow v^{ref}$  iff

$$0 \prec G \prec 2X^{-1}.\tag{8}$$

In the scalar case (one inverter acting on a single phase circuit), this condition is  $0 < g < 2/\chi$ . This implies that under normal operation, g should be positive but not too large to have the voltages converge. We are also interested in the possibility of g < 0, where the inverters push the voltage away from  $v^{ref}$ .

**Lemma 3.** If  $G \prec 0$ , system  $\Sigma_2$  given by (7) has  $v \to \pm \infty$ .

When the deadband is introduced, inverters only operate according to (5) when their voltage is outside the deadband.

Because  $v^{ref}$  is centered in the deadband, the divergence Lemma 3 holds in the same way as the no-deadband case, and the convergence condition (8) yields  $v \to D$  instead of  $v \to v^{ref}$ .

For our system  $\Sigma_2$ ,  $G = diag([g\ g])$  and  $q = [q_1\ q_2]$ . The dissipative nature of power grids due to line impedances causes the diagonal terms of X to be larger than the off-diagonal terms. From the circuit in Fig. 2, system  $\Sigma_2$  has

$$X = \begin{bmatrix} \chi & \eta \chi \\ \eta \chi & \chi \end{bmatrix},\tag{9}$$

where the damping factor  $\eta$  satisfies  $0 < \eta < 1$ . In general, if inverters have different reactances in the line path to the substation,  $\eta_1 = X_{21}/X_{11}$  and  $\eta_2 = X_{12}/X_{22}$ . Because in this work we only use  $\eta$  for its property of  $0 < \eta < 1$ , using  $\eta = \eta_1 = \eta_2$  does not change the results.

#### III. FULL SYSTEM ANALYSIS

# A. Modeling the Four Devices as a Hybrid System

Next we model the devices and circuit in Fig. 2 as a switched affine hybrid system,  $\Sigma_3$ . The state vector is  $x=\begin{bmatrix}z_1&z_2&z_3&v_1&v_2\end{bmatrix}^{\top}$ , where  $z_1,z_2,z_3$  are the internal timers for LTC1, LTC2, and inverter1 and 2, respectively. The two inverters use the same timer  $z_3$  because they have the same delay of  $d_{inv}$ . Let  $T_s$  be the timestep of the discrete model. Each hybrid mode has a label with the format  $m^{\star}0$  where  $\star=1,2,...8$ , and has dynamics of the form x[k+1]=Ax[k]+c where  $A\in\mathbb{R}^{5\times5}$  and  $c\in\mathbb{R}^5$ .

To define the switching conditions, we define a function f that indicates whether a voltage is inside the deadband:

$$f_i := max(v_i - v^+, 0) - max(v^- - v_i, 0)$$

for  $i = 1, 2$ . (10)

For i=1,2, if  $v_i$  is an overvoltage then  $f_i>0$ . If it is an undervoltage then  $f_i<0$ , and if inside D then  $f_i=0$ . Inverter1 (LTC1) responds when  $f_1\neq 0$  for  $d_{inv}$  ( $d_{L1}$ ) seconds, and Inverter2 (LTC2) responds when  $f_2\neq 0$  for  $d_{inv}$  ( $d_{L2}$ ) seconds.

Now we introduce the hybrid model, where we make the symbolic variables bold:

m10: tap LTC1 up

Switch condition:  $z_1 > \mathbf{d_{L1}}$  and  $(f_1 + f_2 < 0)$

Dynamics:

$$\begin{bmatrix} z_1 \\ z_2 \\ z_3 \\ v_1 \\ v_2 \end{bmatrix}_{t=1} = \begin{bmatrix} 0 & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} z_1 \\ z_2 \\ z_3 \\ v_1 \\ v_2 \end{bmatrix}_{t} + \begin{bmatrix} T_s \\ T_s \\ \bar{\mathbf{v}}_{\mathbf{L}} \\ \bar{\mathbf{v}}_{\mathbf{L}} \end{bmatrix}$$

m20 (tap LTC1 down) is the same as m10 except the condition has  $(f_1 + f_2) > 0$  and the affine term is  $[T_s \ T_s \ T_s \ -\bar{\mathbf{v}}_{\mathbf{L}} \ -\bar{\mathbf{v}}_{\mathbf{L}}]^{\top}$ .

m30: tap LTC2 up

Switch condition:  $z_2 > \mathbf{d_{L2}}$  and  $(f_1 + f_2 < 0)$

Dynamics:

m40 (tap LTC2 down) is the same as m30 except the condition has  $(f_1 + f_2) > 0$  and the affine term is  $[T_s \ T_s \ T_s \ -\bar{\mathbf{v}}_{\mathbf{L}} \ -\bar{\mathbf{v}}_{\mathbf{L}}]^{\top}$ .

m50: inverter(s) respond to voltage issues

Switch condition:  $z_3 > \mathbf{d_{inv}}$  and  $(f_1 \neq 0 \text{ or } f_2 \neq 0)$ Dynamics:

$$\begin{bmatrix} T_s & T_s & \chi \mathbf{g} v^{ref} + s \chi \mathbf{g} v^{ref} & s \chi \mathbf{g} v^{ref} + \chi \mathbf{g} v^{ref} \end{bmatrix}^{\top}$$

m60: reset LTC2 and inverter timers

Switch condition:  $[m = m10 \text{ and } (f_1 > 0 \text{ or } f_2 > 0)]$

or  $[m = m20 \text{ and } (f_1 < 0 \text{ or } f_2 < 0)]$

Dynamics:

$$z_2[k+1] = T_s$$

,  $z_3[k+1] = T_s$ ,  $v[k+1] = v[k]$

m70: reset LTC1 and inverter timers

Switch condition:  $[m = m30 \text{ and } (f_1 > 0 \text{ or } f_2 > 0)]$

or  $[m = m40 \text{ and } (f_1 < 0 \text{ or } f_2 < 0)]$

Dynamics:

$$z_1[k+1] = T_s$$

,  $z_3[k+1] = T_s$ ,  $v[k+1] = v[k]$

m80: increment timers

Switch condition: no other mode conditions hold

Dynamics:  $z_i[k+1] = z_i[k] + T_s \ \forall i = 1, 2, 3, \ v[k+1] = v[k]$

**Remark 1.** The relationship  $d_{inv} < d_{L1} < 2d_{L2}$  from Table I indicates that the inverters respond to voltage issues before LTC1. This assumption is a less conservative version of  $d_{inv} \ll d_{L1}$  that is often made in power systems literature [1]. By this assumption, an LTC will never tap twice before an inverter acts.

# B. Behavior when q > 0

For positive values of the inverter gain g, our control action renders the voltage dynamics stable, as shown next.

**Proposition 1.** If system  $\Sigma_3$  has  $0 < g < \frac{2}{\chi}$ , there exists T > 0 such that  $v[k] \in D$  for all  $k \ge T$ .

*Proof.* We give an intuitive sketch of the proof through a Lyapunov argument. We notice that when g=0 circuit  $\Sigma_3$  behaves equivalently to  $\Sigma_1$ . Lemma 2 establishes that if  $\bar{v}_L < 2\varepsilon$ , then the system exhibits marginally stable oscillations

(recall Fig. 4). This implies that the energy of the system  $Y_k$  remains positive and bounded by fixed values  $\bar{Y}_1$  and  $\bar{Y}_2$ , i.e.,  $0 < \bar{Y}_1 \le Y_k \le \bar{Y}_2 < \infty$ , when g = 0.

Now if we consider a positive gain  $0 < g < 2/\chi$  in  $\Sigma_3$ , equation (8) guarantees that the inverter acts as a stabilizing controller during mode m50, decreasing the system energy and driving v closer to the deadband. Finally, from Remark 1 we know that because of the conditions on the timers, we will always return to m50 regularly, at least once between each LTC tap. Therefore, the system  $\Sigma_3$  has maximum energy of  $Y_2$  and will only lose energy from there until landing in the deadband.

The consequence of Lemma 1 is that for realistic values of the network with g>0, the system exhibits damped oscillations which eventually reach the deadband. Thus, we focus the remainder of this paper on the more dangerous scenario where g<0 renders the oscillations unstable.

#### C. Trajectory Walkthrough for g < 0

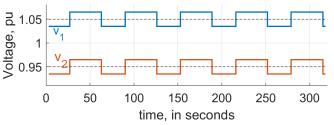

Fig. 5: Simulation of system  $\Sigma_3$  for g < 0 with parameters being the defaults in Table I. System start time is at  $k_0$ .

Here, we describe a scenario on system  $\Sigma_3$  that can result in the beginning of unstable oscillations. Suppose an adversary gains access to the inverter firmware and installs malware onto the devices. The malware logic could, for example, negate the two inverter controller gain g when the voltage suddenly changes substantially ( $|v_i[k+1]-v_i[k]| > 0.6\varepsilon$ ), and the voltage lands far from  $v^{ref}$  ( $|v_i[k+1]-v^{ref}| > 0.6\varepsilon$ ). Such an attack is plausible because the it requires only a minor modification to the existing inverter control logic, and the trigger by external voltage event(s) conceals the time when the cyber *breach* occurred, which could be much earlier than the parameter negation.

Follow along with Fig. 5. Suppose shortly before time  $k_0$  some external event(s), such as a fault or affect from the transmission grid, causes the voltages to shift abruptly. Suppose the voltage shifts increase  $v^{\text{diff}}$ , make  $v_2$  an undervoltage, and triggers the negation of the inverter parameter g. See tinyurl.com/yj7avpet for power flow examples of this voltage shift on realistic circuits. Now we are interested in what happens after the system  $\Sigma_3$  start time of  $k_0$ . From  $k_0$  to  $k_1$ : at  $k_0$  we have  $f_2 < 0$  while  $f_1 = 0$ , so inverter2 actuates several times, each time causing  $v_2$

to get further from the deadband. For  $k_1$  to  $k_2$ : the LTC2 delay is complete so LTC2 taps, fixing the  $v_2$  undervoltage but making  $v_1$  an overvoltage. For  $k_2$  to  $k_3$ : the inverter1 actuates several times, each time causing  $v_1$  to get further from the deadband. For  $k_3$  to  $k_4$ : the LTC1 delay is complete so LTC1 taps, fixing the  $v_1$  overvoltage but making  $v_2$  an undervoltage again. At  $k_4$  we have  $f_2 < 0$  while  $f_1 = 0$  which was the case for  $k_0$ , so we have completed one quasiperiodic oscillation. In future sections we show how these oscillations continue.

# D. Single Inverter Action Preliminaries

In this section we present some properties of inverter actions between LTC taps to prepare for later proofs.

Suppose inverter i is acting during a time interval  $[k \dots k+N]$ . Define the change in  $v_j \in \mathbb{R}^1$  due to the inverter's action as  $\Delta v_j^{inv}(X_{ij},k+N,k,v_i[k]) \coloneqq v_j[k+N] - v_j[k] \in \mathbb{R}^1$ .  $\Delta v_j^{inv}$  can be thought of as the projection of inverter's actuation onto the  $v_j$  axis of the  $(v_i,v_j)$  space. Occasionally we omit some of the four parameters from  $\Delta v^{inv}$  when they are not relevant.

**Assumption 2.** (Bounds on LTC and inverter action)  $\bar{v}_L + \Delta v_i^{inv}(X_{ii}, k + N, k, v_i[k]) < 2\varepsilon$  for  $v_i[k] \in W$ , and  $\forall k, N$ .

This assumption implies that  $\bar{v}_L < 2\varepsilon$  and  $\Delta v_i^{inv}(X_{ii}, k+N, k, v_i[k]) < 2\varepsilon$  for  $v_i[k] \in W$ , and  $\forall k, N$ . The Assumption is reasonable because  $\bar{v}_L$  is typically significantly less than  $\varepsilon$ , and  $\Delta v^{inv}$  imparting a voltage change of close to  $2\varepsilon$  would require unreasonably large combinations of circuit impedance and inverter capacity.

Recall the voltage update equation (6)  $v[k+1] = v[k] - XG(v[k] - v^{ref})$ . The inverter acts  $N_1 := \operatorname{floor}(d_{L1}/d_{inv})$  times if after the interval  $[k \dots k + N_1]$  the LTC1 taps, or  $N_2 := \operatorname{floor}(d_{L2}/d_{inv})$  times if after  $[k \dots k + N_2]$  LTC2 taps. The  $i^{th}$  row of (6) implies that node i's voltage is

$$v[k+1] = v[k] + \chi(v[k] - v^{ref}) \in \mathbb{R}^1,$$

(11)

and each other voltage on the network is given by

$$v[k+1] = v[k] + s\chi(v[k] - v^{ref}) \in \mathbb{R}^1$$

(12)

from substituting (9) into (6). Now consider the accumulation of (6) for  $N=N_1$  or  $N=N_2$  timesteps:

$$v[N+k] = (I - XG)^N v[k] + \sum_{r=0}^{N-1} (1 - XG)^r (XGv^{ref}).$$

(13)

The  $j^{th}$  row of (13) gives a parameterization of  $\Delta v_i^{inv}$ :

$$\Delta v_j^{inv}(X_{ij}, k+N, k, v_i[k], g) = v_j[N+k] - v_j[k]$$

$$= ((1-\chi g)^N - 1)v[k] + \sum_{r=0}^{N-1} (1-\chi g)^r (X_{ij}gv^{ref}). \quad (14)$$

**Remark 2.** (Remarks about  $\Delta v_i^{inv} \ \forall \ i=1,2$ )

- 1) Because  $\Delta v_i^{inv} < 2\varepsilon$  from Assumption 2,  $\Delta v_i^{inv}(X_{ii}, k+1, k)$  has the same sign for k=0...N.

- 2) If g > 0,  $sign\{\Delta v_i^{inv}(v[k])\} = -sign\{v_i[k] v^{ref}\}$ .

- 3) If g < 0,  $sign\{\Delta v_i^{inv}(v[k])\} = sign\{v_i[k] v^{ref}\}$ .

The first item establishes that each inverter actuates in the same direction between LTC taps. The second (third) items establish that when g>0 (g>0), the inverters push the voltage toward (away) from the deadband.

**Lemma 4.**  $(\Delta v^{inv})$  is a homogeneous function) The coupling effect of a single inverter actuating at node i on the voltage at node j is damped by a factor of  $\eta$ . That is,  $\Delta v_j^{inv}(k+N,k,v_i[k]) = \eta \Delta v_i^{inv}(k+N,k,v_i[k])$ .

# E. Partitioning W in State Space when g < 0

In this section we will partition W into D,  $W_g$ ,  $W_b$ ,  $W_o$ , based on the possible trajectories from starting the system in each region. We use a similar process to Section II-C. The  $W_b$  region will be when both voltages are above or below the deadband. In that case, both inverters act between LTC taps, and from Assumption 2 oscillations cannot occur. Then  $W_o$  will be where only one inverter acts between taps, and is close enough to D for oscillations to occur. An oscillation would begin with an inverter pushing the voltages further from the deadband (Remark 2 #3) until an LTC tap towards the deadband and overshoots it. Therefore, the boundary of  $W_o$  comes from the states v where after inverter action(s) and an LTC tap the state is within the deadband edge:

$$v_1 + r_1 - \bar{v}_L < v^+ \tag{15a}$$

$$v_2 + r_2 - \bar{v}_L < v^+ \tag{15b}$$

$$v_1 + r_1 + \bar{v}_L > v^-$$

(15c)

$$v_2 + r_2 + \bar{v}_L > v^-.$$

(15d)

Function r is the inverters' change in v before an LTC taps:

$$r_1 := \Delta v_1^{inv}(\chi, N_1, v_1) + \Delta v_1^{inv}(X_{12}, N_1, v_2)$$

(16a)

$$r_2 := \Delta v_2^{inv}(X_{12}, N_1, v_1) + \Delta v_2^{inv}(\chi, N_1, v_2).$$

(16b)

Note that r depends on both  $v_1$  and  $v_2$ , but when only one inverter acts, one term in each of (16a) and (16b) zeros out, causing eqs. (15a) to (15d) to depend on only  $v_1$  or  $v_2$ . We can now define the state space regions as

$$\begin{split} W_o = & \{(v_1, v_2) \in W: \\ & (v_1 \in M(D, v_1^* - v^+) \text{ and } v_2 \in D), \\ & \text{or } (v_2 \in M(D, v_2^* - v^+) \text{ and } v_1 \in D)\}, \\ W_b = & \{(v_1, v_2) \in W: \\ & (v_1, v_2 > v^+, v_2 \leq v_1, (15\text{a) holds}), \\ & \text{or } (v_1, v_2 > v^+, v_2 > v_1, (15\text{b) holds}), \\ & \text{or } (v_1, v_2 < v^-, v_2 > v_1 (15\text{c) holds}), \\ & \text{or } (v_1, v_2 < v^-, v_2 \leq v_1, (15\text{d) holds})\}, \end{split}$$

and  $W_g$  is what remains of W ( $W_g = W/(D \cup W_o \cup W_g)$ ). The  $v_1^*$  and  $v_2^*$  in (17a) are the  $v_1$  and  $v_2$  when (15a) and (15b) are set to be equalities. The  $W_o$  region definition is the same as that of the 2-LTC system  $\Sigma_1$  (17), with the distinction that equations (15) have the additional r term.

Fig. 6 shows these state space regions as well as the possible transitions between regions. The trajectory of Fig. 5 is plotted on Fig. 6 with a square marker for the IC and circular marker for when it leaves W. In addition to the

Fig. 6: Regions for four-device system  $\Sigma_3$  when g < 0.

possible transitions for system  $\Sigma_1$  in Fig. 3, this system has:  $W_g \to P', \ W_b \to W_g, \ W_o \to W_b$ , and  $W_o \to W_b$  since the inverter pushes voltages away from D.

When the IC is in  $W_g$  or  $W_b$ , there may exist a  $k_0 > 0$  where the full state vector  $x[k_0] = [0,0,0,v_1[0],v_2[0]]^{\top}$ . Because  $\Sigma_3$  is time-invariant, the Fig. 6 regions apply to any  $x[k_0]$  where  $x[k_0] = x[0]$ . For example, the system IC could be in  $W_g$  then later have  $x[k_0] \in W_o$ , after which point the behavior would be the same as if the system started in  $W_o$ .

# F. Conditions for Oscillations to Begin when g < 0

In this section we consider trajectories where  $v[k_0] \in W_o$ . As illustrated in Fig. 6,  $W_o$  is comprised of four disjoint regions. If hunting occurs in the lower region of  $W_o$  ( $f_1=0$  while  $f_2<0$ ), the hybrid system mode sequence (MS) that creates one period of oscillation is  $\alpha_1:=\{m50,m10,m60,m50,m40,m70\}$  after omitting the increment mode (m80) for brevity. Similarly, let  $\alpha_2$ ,  $\alpha_3$ , and  $\alpha_4$  be the oscillation sequences when the IC is in the upper, left, and right-hand regions of  $W_o$ , respectively.

**Lemma 5.** (Basis step for oscillations) Consider system  $\Sigma_3$  with g < 0. When  $f_1 = 0$  while  $f_2 < 0$ , necessary and sufficient conditions for completing one oscillation period starting at time  $k_0$  are

$$v_1[k_0] + \eta \Delta v^{inv}(\chi, k_0 + N_2, k_0, v_2[k_0]) > v^- \quad \ (18a)$$

$$v[T_1] > v^-$$

(18b)

$$v[T_1] + \eta \Delta v^{inv}(\chi, k_0 + N_1, k_0, v[T_1]) < v^+$$

(18c)

$$v[T_2] + \Delta v^{inv}(\chi, k_0 + N_1, k_0, v[T_2]) - \bar{v}_L < v^+$$

(18d)

where

$$v[T_1] = v_2[k_0] + \Delta v^{inv}(\chi, k_0 + N_2, k_0, v_2[k_0]) + \bar{v}_L$$

, and  $v[T_2] = v_1[k_0] + \eta \Delta v^{inv}(\chi, k_0 + N_2, k_0, v_2[k_0]) + \bar{v}_L$ .

*Proof.* Follow along with Fig. 5. We will express sequence  $\alpha_1$  in terms of the system voltage trajectories. For the IC,  $v_2[k_0]$  is an undervoltage and  $v_1[k_0]$  in the deadband. Inverter2 responds to the  $v_2$  undervoltage, but due to g<0 it decreases both voltages. To prevent inverter2 from pushing both voltages below the deadband, we require that

$$v_1[k_0] + \Delta v_1^{inv}(\chi_{12}, k_0 + N_2, k_0, v_2[k_0]) > v^-.$$

Next, with the persisting  $v_2$  undervoltage, LTC2 taps which increases both voltages. To create overshoot so that  $v_1$  has

an overvoltage, we require that

$$v_2[k_0] + \Delta v_2^{inv}(\chi, k_0 + N_2, k_0, v_2[k_0]) + \bar{v}_L > v^-.$$

Inverter1 responds to the  $v_1$  overvoltage, but due to g<0 it increases both voltages. To prevent inverter1 from pushing both voltages above the deadband, we require that

$$v[T_1] + \Delta v_2^{inv}(\chi_{12}, k_0 + N_1, k_0, v_1[T_2]) < v^+.$$

With the persisting  $v_1$  overvoltage, LTC1 taps which decreases both voltages. To create overshoot so that  $v_2$  becomes an undervoltage, we require that

$$v[T_2] + \Delta v_1^{inv}(\chi, k_0 + N_1, k_0, v_1[T_2]) - \bar{v}_L < v^+.$$

Finally, we use the homogeneity Lemma 4 to factors out  $\eta$  from  $\Delta v^{inv}$  gives the conditions stated by this lemma.  $\Box$

G. Showing Oscillations Continue and Grow when g < 0

Next we show that once the MS  $\alpha_1$  occurs, the next MS will be  $\alpha_1$  while  $v \in W_o$ . The same process can be applied to the other MS  $\alpha_2$ ,  $\alpha_3$ , and  $\alpha_4$ .

Define  $m[k_i]$  as the mode that system  $\Sigma_3$  is in at time  $k_i$ . Across each  $\alpha_1$  MS,  $v^{\text{diff}}$  increases. We will prove that in the next section, but note that as a result the voltage that is outside D gets further from  $v^{ref}$  across each  $\alpha_1$  MS.

**Lemma 6.** (Induction step for oscillations) Consider system  $\Sigma_3$  with g = 0.5. Assuming condition (19) and Assumption 1 holds, if the system completes MS  $\alpha_1$ , the MS  $\alpha_1$  will repeat

*Proof.* Use Fig. 5 to follow along.  $m[k_4]$ : at  $k_0$  inverter2 actuates and  $m[k_0] = m50$  so  $v_2[k_0] \notin D$ . Because  $v_2$  gets further from  $v^{ref}$ ,  $v_2[k_4] < v_2[k_0]$ , so  $v_2[k_4] \notin D$  too. From Assumption 1,  $v_1[k_4]$  cannot be outside D, so  $v_1[k_4] \in D$ . Thus inverter2 actuates at  $k_4$  and  $m[k_4] = m50$ .

$m[k_5]$ : Because g<0, inv2 actuating  $(m[k_4]=m50)$  will keep  $v_2\notin D$ . If the inverter's coupling effect on  $v_1$  is strong enough, even though  $v_1[k_4]\in D$ ,  $v_1$  could go below the deadband by the time of  $k_5$ . By Assumption 2, the inverter actions summed with an LTC tap are not large enough for this. Thus at  $k_5$ ,  $v_1$  is still inside D and  $v_2$  is still outside D. So at  $k_5$  LTC2 taps up and  $m[k_5]=m30$ .

$m[k_6]$ : The LTC2 tap may not overshoot the deadband at  $k_6$ . If

$$v_1^{inv}(k_5, k_4, v_1[k_4]) + \Delta v_1^{inv}(k_3, k_2, v_1[k_2]) > 0$$

(19)

does not hold, then  $v_1[k_6] \in D$ , by Assumption 1  $v_2[k_6] \in D$  too, and the system stays in the deadband. If the condition does hold, inverter1 actuates and  $m[k_4] = m50$ .

$m[k_7]$ : Assumption 2 disallows  $v_2$  from going above D (like how in  $m[k_5]$  it disallows  $v_1$  from going below D). Thus at  $k_7$ ,  $v_2$  is still inside D and  $v_1$  is still outside D. So at  $k_7$  LCT1 taps down and  $m[k_7] = m20$ .

**Lemma 7.** (Oscillations grow) If system  $\Sigma_3$  with g < 0 has oscillations,  $v^{diff}$  increases after each oscillation period.

Let  $s_1$  be the set of  $(v_1[k_0], v_2[k_0])$  where basis conditions (18) hold. The sets of conditions that correspond to sequences  $\alpha_2, \alpha_3$ , and  $\alpha_4$  are derived with the same process

as the Lemma 5 proof, and we call their corresponding sets  $s_2, s_3, \text{and } s_4$ . Then define  $S \coloneqq (\bigcup_{i=1,\dots,4} s_i) \in W_o$ , which is the only voltage region where oscillations can begin. Note that with the  $\Delta v^{inv}$  parametrized form (14), S can be represented by purely the variables listed in Table I.

**Theorem 1.** When g < 0,  $v[k_0] \in S$  is necessary but not sufficient for System  $\Sigma_3$  to exhibit growing oscillations starting at time  $k_0$ . These oscillations terminate either at time  $T_1 > k_0$  or  $T_2 > k_0$ , where  $v[T_1] \in D$  and  $v[T_2] \in W'$ .

*Proof.* Lemma 5 (basis step) establishes that (18) are necessary for on period of oscillations to occur. By Lemma 6 (induction step), the system continues to oscillate after the first oscillation period. Lemma 7 establishes that the oscillations grow, so the system will land in D or outside W eventually.

Theorem 1 implies that when g < 0, the only way for  $\Sigma_3$  to exhibit oscillations is when  $v[k_0] \in S$ . To use this theorem, distribution engineers would choose control parameters such that  $S = \emptyset$ , or setup devices to reject incoming parameter changes if  $S \neq \emptyset$ .

#### IV. RESULTS AND SCALABILITY

#### A. Parameter Plots

In this section we use MATLAB's MPT toolbox to plot set S in the  $(v_1, v_2)$  space and examine its implications on the ratio of the device control delays. Recall that S is the only voltage region where oscillations can begin, and includes the projection of basis conditions (18) onto the  $(v_1, v_2)$  space.

(a)  $s_i$  regions when g=0.5 (b)  $s_i$  regions when g=-0.3 Fig. 7: S in medium gray on  $(v_1,v_2)$  space; W in light gray

In Fig. 7 we plot S on the  $(v_1, v_2)$  space, and validate that S in Fig. 7b is indeed a subset of  $W_o$  from (??), as both sets have width of 0.0095 pu. Observe that some corners of  $W_o$  are not included in S because trajectories that start there leave W before completing an oscillation period. We also observe that in Fig. 7b where oscillations can grow, the area of S is smaller compared to when oscillations are damped in Fig. 7b. It is relieving that the regions where dangerous oscillations could occur are narrow.

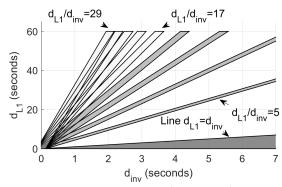

Next we examine the appropriate timescale separation between the inverters and LTC1 for system  $\Sigma_3$  when g < 0. Because  $N_1 = \mathrm{floor}(d_{L1}/d_{inv})$  and  $N_1$  enters  $\Delta v^{inv}$  as the exponent (see (14)), Each fixed  $N_1$  represents the slope of a line through the origin on the  $(d_{L1}, d_{inv})$  space. As such, varying  $d_{L1}$  and  $d_{inv}$  such that  $N_1$  is fixed will not change the S region on (v1, v2). Therefore, rather than iterate over

Fig. 8: Lines for whether  $S = \emptyset$  or  $S \neq \emptyset$  on  $(d_{L1}, d_{inv})$  space; hunting impossible (possible) in light (dark) gray

the  $(d_{L1}, d_{inv})$  in a meshgrid, we compare the area of set S for lines corresponding to different  $N_1$  values.

We set all variables except  $(v_1[k_0] \text{ and } v_2[k_0])$  to the defaults in Table I. Instead of  $d_{L1}=30$  and  $d_{L2}=40$ , which have a ratio of  $\frac{4}{3}$ , we set  $N_2=\frac{4}{3}N_1$  since  $\frac{N_2}{N_1}=\frac{d_{L2}}{d_{L1}}$ . We vary  $N_1$  from 5 to 29. For each  $N_1$  value, if  $S=\emptyset$ , then hunting oscillations are impossible for all  $v[k_0]\in W$ , and we mark the line with slope  $N_1$  as light gray in Fig. 8. Conversely, if  $S\neq\emptyset$  then the  $N_1$  line is dark gray. The line  $d_{inv}=d_{L1}$  is also marked to only allow the  $d_{inv}< d_{L1}$  from Table I. We observe that  $N_1=17=\operatorname{floor}(d_{L1}/d_{inv})$  is the borderline case where hunting is impossible. For example, if the inverters have a 3-second delay, the substation LTC needs at least a 51-second delay to prevent hunting for all IC in W.

# B. Scaling to Grids with Many Devices

Radial distribution grids are typically tree graph networks whose root is the substation. Each node has one or more branch(es), which is the tree network connected to that node's edge(s). Suppose there is at most one LTC and at most two actively controlled inverters on each branch of the root node. Then each branch has a system comprised of the substation LTC, the LTC on the branch, and two inverters on the branch. One can characterize each system as  $\Sigma_3$  and analyze it independently using the methodology of section III. Then, concatenate the parameter conditions that involve the substation LTC parameters. As the number of root-node branches increases, only the number of conditions on the substation LTC, rather than those on all devices, grows.

# V. CONCLUSION

We have presented a novel hybrid system model for LTCs with inverters on radial distribution circuits. Leveraging the system dynamics, we have derived conditions on the control parameters to guarantee against voltage oscillations created by device hunting. The conditions inform the design of appropriate parameters, such as the minimal timescale separation of control delays between LTCs and inverters. The conditions also pave the way for implementing on-board certificates that guard against malicious firmware updates of control parameters.

Future work will more formally investigate the types of events that widen the voltage difference enough for hunting to be possible. Additionally, the relationships between parameters captured by the conditions derived here will be examined in more detail. Finally, the behavior of the system in the abnormal but not impossible operating state where one voltage is above the deadband while the other is below will be explored.

#### VI. APPENDIX

**Lemma 1** If  $\bar{v}_L > 2\varepsilon$ , system  $\Sigma_1$  will have marginally stable oscillations for all time when any  $v_1[0] \in M(D,c)$  or  $v_2[0] \in M(D,c)$  where  $c=\bar{v}_L-2\varepsilon>0$

*Proof.* If  $v_1[0] \in M(D,c)$ , LTC1 taps, causing  $\bar{v}_L$  to overshoot the deadband of width  $2\varepsilon$  and land outside D. After a delay  $d_{L1}$ , LTC1 will tap in the opposite direction, landing at the system IC. Then these actions repeat, causing  $v_1$  and  $v_2$  to oscillate with constant amplitude for all time. When  $v_2[0] \in M(D,c)$  we get the same oscillatory behavior.  $\square$

**Lemma 2.** If  $\bar{v}_L \leq 2\varepsilon$ ,  $v[T] \in W_o$ , and  $v^{\text{diff}} < 2\varepsilon - \bar{v}_L$ , system  $\Sigma_1$  will have marginally stable oscillations starting at time T

*Proof.* First consider an IC in  $W_o$  (i.e. T=0) where  $v_2[0]$  is an undervoltage. Overshooting the deadband with an LTC tap can be represented with

$$v_2[0] < v^-$$

start with undervoltage  $v_1[0] + \bar{v}_L > v^+$ .

Combining the above two equations gives  $v^{\rm diff}>2\varepsilon-\bar{v}_L$ . These conditions for  $v_2[0]$  being an *overvoltage* would yield the same  $v^{\rm diff}>2\varepsilon-\bar{v}_L$ . Now consider where our IC is not in  $W_o$  but at time T we land in  $W_o$ . Because the system has no internal memory states, oscillations will begin after this nonzero T as if the zero-start time was at T.

**Lemma 3.** If  $G \prec 0$ , system  $\Sigma_2$  given by (7) has  $v \to \pm \infty$ .

*Proof.* Let F=-G. Because  $G \prec 0$  and is diagonal, F is diagonal and positive definite. The proof of Theorem 3.1 in [19] shows that  $eig(XS)=eig(S^{\frac{1}{2},\top}XS^{\frac{1}{2}})\in (0,2)$  for symmetric X and diagonal positive definite S. Thus  $eig(XF)=eig(F^{\frac{1}{2},\top}XF^{\frac{1}{2}})\in (0,2)$ . Then all eig(I-XG)=eig(I+XF)=1+eig(XF)=1+(0,2)>1. Thus the spectral radius of (I-XG) is greater than 1, so  $e\to\infty$ , and  $v\to\infty$  or  $v\to-\infty$ .  $\square$

**Lemma 4.** The coupling effect of a single inverter actuating at node i on the voltage at node j is damped by a factor of  $\eta$ . That is,  $\Delta v_j^{inv}(k+N,k,v_i[k]) = \eta \Delta v_i^{inv}(k+N,k,v_i[k])$

*Proof.* From the update equations (11) and (12),

$$\begin{split} \Delta v_i^{inv}(X_{ii}, k+1, k, v_i[k]) &= -\chi(v_i[k] - v^{ref}) \\ \Delta v_j^{inv}(X_{ij}, k+1, k, v_i[k]) &= -\eta \chi(v_i[k] - v^{ref}) \\ &= \eta \Delta v_i^{inv}(X_{ii}, k+1, k, v_i[k]) \end{split}$$

By Remark 2, the voltage change at each timestep over  $[0\ N]$  is additive in the same direction. If we consider a duration

over two timesteps,

$$\Delta v_j^{inv}(X_{ij}, k+2, k, v_i[k]) = v[k+2] - v[k+1] + v[k+1] - v[k]$$

$$= \Delta v_j^{inv}(\chi, k+2, k+1, v_i[k+1]) + \Delta v_j^{inv}(\chi, k+1, k, v_i[k])$$

$$= -\eta \chi(v_i[k+1] - v^{ref}) - \eta \chi(v_i[k] - v^{ref})$$

$$= \eta \Delta v_i^{inv}(X_{ii}, k+2, k, v_i[k])$$

**Lemma 7.** If system  $\Sigma_3$  with g < 0 has oscillations,  $v^{\text{diff}}$  increases after each oscillation period

*Proof.* We consider the case that the IC is below the deadband. We express the voltages after the first sequence of modes and compare  $v^{\text{diff}}[k_0]$  to  $v^{\text{diff}}[k_4]$

$$\begin{aligned} v_1[k_4] &= v_1[k_0] + \eta \Delta v_2^{inv}(k_0 + N_2, k_0, v_2[k_0]) + \bar{v}_L \\ &+ \Delta v_1^{inv}(k_0 + N_1, k_0, c) - \bar{v}_L \\ v_2[k_4] &= v_2[k_0] + \Delta v_2^{inv}(k_0 + N_2, k_0, v_2[k_0]) + \bar{v}_L \\ &+ \eta \Delta v_1^{inv}(k_0 + N_1, k_0, c) - \bar{v}_L \end{aligned}$$

where  $c := v_1[k_0] + \eta \Delta v_1^{inv}(k_0 + N_2, k_0, v_2[k_0]) - \bar{v}_L$ . Subtracting the above two equations, we have

$$v^{\text{diff}}[k_4] = v^{\text{diff}}[k_0] + \eta \Delta v_2^{inv}(k_0 + N_2, k_0, v_2[k_0]) + \Delta v_1^{inv}(k_0 + N_1, k_0, c) - \Delta v_2^{inv}(k_0 + N_2, k_0, v_2[k_0]) - \eta \Delta v_1^{inv}(k_0 + N_1, k_0, c) - \bar{v}_L$$

which simplifies to

$$v^{\text{diff}}[k_4] - v^{\text{diff}}[k_0] = (\eta - 1)(\Delta v_2^{inv}(v_2[0], N_2) - \Delta v_1^{inv}(k_0 + N_1, k_0, c))$$

(20)

The damping factor has  $0<\eta<1$ , so  $(\eta-1)$  is negative.  $v_2[k_0]$  is below the deadband, so  $\Delta v_2^{inv}(N_2,v_2[k_0])<0$ , and  $v_1[k_2]$  is above the deadband, so  $\Delta v_1^{inv}(c,N_1)$  is positive. Together, (20) is always positive. Thus  $v^{\text{diff}}[k_4]>v^{\text{diff}}[k_0]$ .

If we repeat this process for the case of the IC being an overvoltage, we get the same final equation (20).

#### VII. ACKNOWLEDGEMENT

The authors would like to express their sincere gratitude to Professor Murat Arcak and Lawrence Berkeley National Lab Scientist Daniel Arnold for their insightful comments.

# REFERENCES

- M. Ahmed, R. Bhattarai, S. J. Hossain, S. Abdelrazek, and S. Kamalasadan, "Coordinated Voltage Control Strategy for Voltage Regulators and Voltage Source Converters Integrated Distribution System," *IEEE Transactions on Industry Applications*, July 2019.

- [2] M. Chamana and B. H. Chowdhury, "Impact of Smart Inverter Control with PV Systems on Voltage Regulators in Active Distribution Networks," in *IEEE International Symposium on High-capacity Optical* Networks and Emerging/Enabling Technologies, Dec. 2014.

- [3] M. Kraiczy, T. Stetz, and M. Braun, "Parallel Operation of Transformers With on Load Tap Changer and Photovoltaic Systems With Reactive Power Control," *IEEE Transactions on Smart Grid*, Nov. 2018.

- [4] C. Smith, M. Redfern, and S. Potts, "Improvement in the Performance of On-load Tap Changer Transformers Operating in Series," in 2003 IEEE Power Engineering Society General Meeting, July 2003.

- [5] V. Donde and I. A. Hiskens, "Analysis of Tap-Induced Oscillations Observed in an Electrical Distribution System," *IEEE Transactions on Power Systems*, Nov. 2007.

- [6] "IEEE Standard for Interconnection and Interoperability of Distributed Energy Resources with Associated Electric Power Systems Interfaces," IEEE Std 1547-2018 (Revision of IEEE Std 1547-2003), Apr. 2018.

- [7] S. Sahoo, T. Dragičević, and F. Blaabjerg, "Cyber Security in Control of Grid-Tied Power Electronic Converters-Challenges and Vulnerabilities," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, 2019.

- [8] C. Roberts, S.-T. Ngo, A. Milesi, A. Scaglione, S. Peisert, and D. Arnold, "Deep Reinforcement Learning for Mitigating Cyber-Physical DER Voltage Unbalance Attacks," in 2021 American Control Conference (ACC), May 2021.

- [9] T. Gönen, Electric Power Distribution System engineering. USA: CRC Press, 3rd ed., 2014.

- [10] L. Wang, F. Bai, R. Yan, and T. K. Saha, "Real-Time Coordinated Voltage Control of PV Inverters and Energy Storage for Weak Networks With High PV Penetration," *IEEE Transactions on Power Systems*, May 2018.

- [11] S. Mahdavi and A. Dimitrovski, "Integrated coordination of voltage regulators with distributed cooperative inverter control in systems with high penetration of dgs," in 2020 IEEE Texas Power and Energy Conference (TPEC), 2020.

- [12] K. Christakou, M. Paolone, and A. Abur, "Voltage control in active distribution networks under uncertainty in the system model: A robust optimization approach," *IEEE Transactions on Smart Grid*, no. 6, 2018

- [13] B. A. Robbins, H. Zhu, and A. D. Domínguez-García, "Optimal Tap Setting of Voltage Regulation Transformers in Unbalanced Distribution Systems," *IEEE Transactions on Power Systems*, vol. 31, Jan. 2016.

- 14] D. Mignone, G. Ferrari-Trecate, and M. Morari, "Stability and stabilization of piecewise affine and hybrid systems: an LMI approach," in *Proceedings of the 39th IEEE Conference on Decision and Control*, Dec. 2000.

- [15] H. Lin and P. J. Antsaklis, "Stability and Stabilizability of Switched Linear Systems: A Survey of Recent Results," *IEEE Transactions on Automatic Control*, Feb. 2009.

- [16] S. Lim and K. Chan, "Analysis of Hybrid Linear Parameter-varying Systems," in *Proceedings of the 2003 American Control Conference*, 2003., June 2003.

- [17] N. Li, G. Qu, and M. Dahleh, "Real-time decentralized voltage control in distribution networks," in 2014 52nd Annual Allerton Conference on Communication, Control, and Computing, pp. 582–588, Sep. 2014.

- [18] M. Farivar, X. Zho, and L. Chen, "Local voltage control in distribution systems: An incremental control algorithm," in 2015 IEEE International Conference on Smart Grid Communications, Nov. 2015.

- [19] R. E. Helou, D. Kalathil, and L. Xie, "Communication-free voltage regulation in distribution networks with deep PV penetration," in Hawaii International Conference on System Sciences, Jan. 2020.