# A Mixed-Signal Structured AdEx Neuron for Accelerated Neuromorphic Cores

Syed Ahmed Aamir, *Student Member, IEEE*, Paul Müller, Gerd Kiene, Laura Kriener, Yannik Stradmann, Andreas Grübl, Johannes Schemmel, *Member, IEEE*, and Karlheinz Meier, *Member, IEEE*

Abstract—Here we describe a multi-compartment neuron circuit based on the Adaptive-Exponential I&F (AdEx) model, developed for the second-generation BrainScaleS hardware. Based on an existing modular Leaky Integrate-and-Fire (LIF) architecture designed in 65 nm CMOS, the circuit features exponential spike generation, neuronal adaptation, inter-compartmental connections as well as a conductance-based reset. The design reproduces a diverse set of firing patterns observed in cortical pyramidal neurons. Further, it enables the emulation of sodium and calcium spikes, as well as N-Methyl-D-Aspartate (NMDA) plateau potentials known from apical and thin dendrites. We characterize the AdEx circuit extensions and exemplify how the interplay between passive and non-linear active signal processing enhances the computational capabilities of single (but structured) on-chip neurons.

Keywords—Analog integrated circuits, Neuromorphic, Leaky, Integrate-and-Fire, 65 nm CMOS, Spiking, Bursting, Neuron, Adaptation, Exponential, LIF, AdEx, Multi-compartment, Dendrites, NMDA

## I. INTRODUCTION

Low-complexity point neuron models are mathematically tractable and lead to a cost-effective in-silico implementation [1]. In order to realize large-scale neuromorphic systems, they offer efficient utilization of silicon die area and maintain an energy-efficient solution. The classical LIF neuron [2], [3] has therefore been the popular choice in many first-generation neuromorphic systems [4]–[6]. However, compared to experimental spike data, the LIF model falls short of predicting the spike-times and reproduce the diverse properties of biological neurons. Extended threshold-based models, such as two-dimensional models add a second slow variable or additional state variable to define the membrane evolution. When coupled with a non-linear term [7]–[10], they can more accurately predict the physiological data [11]–[13].

The role of single neurons in computation is however more sophisticated than linear pre-processing of synaptic inputs or their integration on the membrane that leads to an output event once a threshold is reached [14], [15]. More specifically, passive dendrites [16] provide computational functions such as independent computation of local non-linear operations [17], directional selectivity in retinal ganglion cells [18], [19] or coincidence detection in auditory pathway [20], [21] to state a few. In addition, the active properties of dendrites contribute to an internal feedback mechanism with back-propagating action potentials [22]–[24] that induce Long-Term Potentiation (LTP) in CA1 [25], Layer 5 neurons [26] or evoke broad Ca<sup>2+</sup> spikes in apical dendrites [27]. Further, in the thin dendrites they contribute to local NMDA plateau potentials [28], [29] marked by an extraordinary duration and significant amplitude, and proposed to play a significant role in cortical information processing and memory consolidation [30].

In this paper, we present a 65 nm CMOS AdEx neuron circuit with multi-compartment emulation capturing properties of passive and non-linear active dendrites. We enhance our modular LIF point neuron architecture characterized in detail in [31], [32] with AdEx extensions [33]. Further, as detailed in [34], in addition to the sodium spikes, the dendritic implementation allows to emulate calcium spikes and NMDA plateau potentials. The neuron description in [33], [34] is based on circuit simulations, while here we demonstrate the measured results from the prototype chip.

The implemented neuron model is designed for integration in the second-generation BrainScaleS 65 nm physical model platform [35], operated ("accelerated" to) 1000 times faster than biological real-time. The presented analog continuoustime neuron in this work is measured on a 65 nm prototype chip that implements a scaled-down array of 32 neurons, connected to  $32 \times 32$  synapses. A finalized version of this circuit will feature in the larger HICANN-DLS chip - the basic building block of the second-generation BrainScaleS hardware targeting a wafer-scale implementation [36]. We omit here the description and architecture of the prototype chip [37] and detailed characterization of the LIF neuron (see [31], [32] for details). In the subsequent sections, we describe the hardware neuron model and the corresponding implemented architecture (Sec. II and Sec. III). The circuit description of the AdEx and multi-compartment extensions are detailed in Sec. IV, followed by experimental results in Sec. V. A discussion on the presented neuron and its comparison with other architectures concludes the paper (Sec. VI and Sec. VII).

## II. NEURON MODEL

The neuron circuit adheres to the AdEx point-neuron model. However it replaces a fixed reset with a conductance-based reset. The evolution of the neuron membrane in the AdEx

Funded by the European Union Seventh Framework Programme ([FP7/2007-2013]) under grant agreement nos. 604102 (HBP), 269921 (Brain-ScaleS), the Horizon 2020 Framework Programme ([H2020/2014-2020]) under grant agreement no. 720270 (HBP) as well as from the Manfred Stärk Foundation.

All authors are with the Kirchhoff Institute for Physics, Heidelberg University, D-69120 Heidelberg, Germany (email: aamir@kip.uni-heidelberg.de).

model is described by a two-variable equation [9] given by

$$C_{\text{mem}} \frac{dV_{\text{mem}}}{dt} = I - w - g_{\text{leak}} (V_{\text{mem}} - V_{\text{leak}}) + g_{\text{leak}} \Delta_T \exp\left(\frac{V_{\text{mem}} - V_T}{\Delta_T}\right)$$

(1)

$$\tau_{\rm w} \frac{dw}{dt} = a (V_{\rm mem} - V_{\rm leak}) - w \tag{2}$$

where I is the sum of external, synaptic and inter-compartment input currents, w is the adaptation current. The last two terms in Eq. 1 model the leak and exponential currents.  $C_{\text{mem}}$  is the membrane capacitance,  $V_{\text{mem}}$  is the membrane potential,  $g_{\text{leak}}$  and  $V_{\text{leak}}$  are the leak conductance and leak potential respectively, a denotes the subthreshold adaptation,  $V_{\text{T}}$  is the exponential threshold and  $\Delta_{\text{T}}$  is its slope factor. At spike time, the membrane is reset to a specified reset potential, and the adaptation variable w is updated by a current b, such that  $w \to w + b$ .

For hardware realization, a transformation is performed for the adaptation term [38] equating the adaptation output current,

$$w = a(V_{\rm w} - V_{\rm leak}) \tag{3}$$

whose substitution modifies Eq. 2 as

$$-C_{\rm w}\frac{dV_{\rm w}}{dt} = g_{\rm w}(V_{\rm w} - V_{\rm mem}) \tag{4}$$

The dendritic structure is implemented using controlled conductance between adjacent isopotential membranes. The inter-compartmental current flowing through the tunable conductance connecting the two membranes is expressed as:

$$I_{\rm ic} = g_{\rm ic}(V_{\rm i} - V_{\rm j}) \tag{5}$$

where  $g_{ic}$  is the inter-compartmental conductance between two shunted membranes with potentials  $V_i$  and  $V_j$ .

## **III. NEURON ARCHITECTURE**

## A. Multi-Compartment Architecture

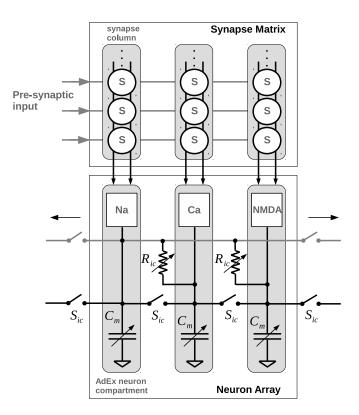

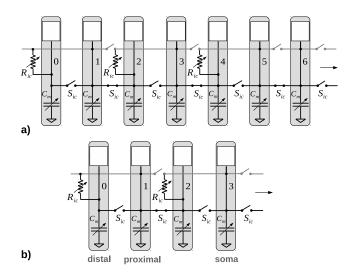

The BrainScaleS neuron can merge its dendritic tree by connecting adjacent neuron compartments in the array - resulting in a larger membrane capacitor with increased inputs. Additionally, this AdEx point-neuron emulation can be extended to multiple compartments in the circuit using an inter-compartmental resistor. This architecture is highlighted in Fig. 1. It shows a matrix of synapse circuits connected to an array of neurons. Every neuron circuit is shown receiving excitatory and inhibitory input lines from a single column of synapses in the matrix. Inside the neuron array, a single column corresponds to a point neuron. The merged dendritic tree is realized by using the switches  $S_{ic}$ , whereas multiple compartments may be realized by utilizing inter-compartmental resistors  $R_{ic}$ . Each neuron compartment may be configured to emulate either Sodium spikes or broad plateau potentials [34].

Fig. 1: A conceptual view of the multi-compartment, highinput count AdEx neuron array architecture connected to a matrix of input synapses that receive asynchronous presynaptic inputs – adapted from [34].

## B. Point Neuron Architecture

The LIF neuron circuit proposed and characterized in [31], [32] introduces a modular architecture, where individual subcircuits are interconnected using transmission-gate switches. The multi-compartment, AdEx neuron with non-linear dendrites is an extended enhancement of this base LIF architecture.

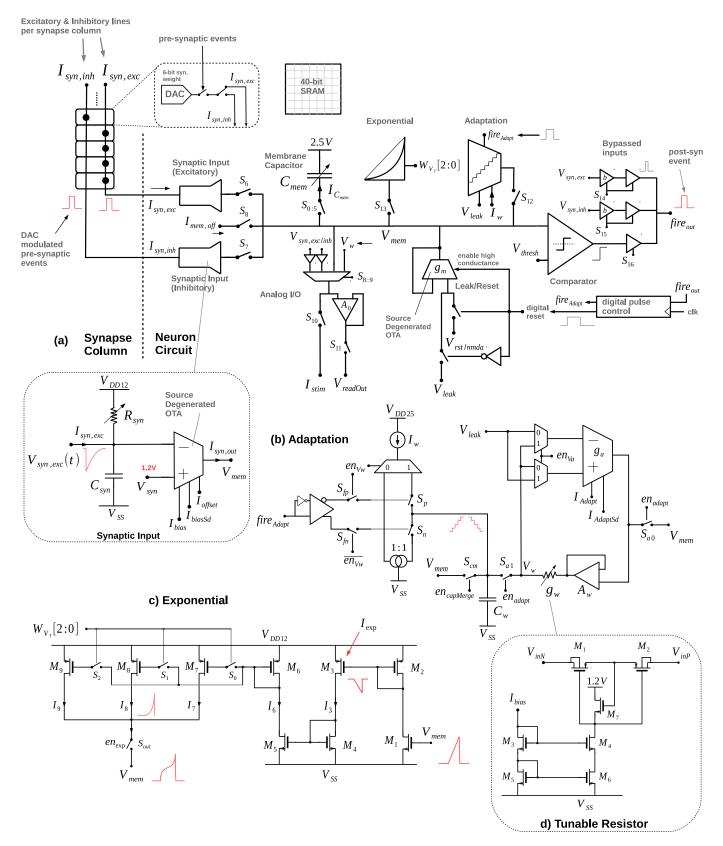

The architecture of a single integrated neuron circuit connected to a synapse column is shown in Fig. 2a. On the left half, the figure shows a single synapse column relaying input current on two wires – one for excitatory inputs and another for inhibitory inputs. Each asynchronous pre-synaptic network event enables a 6-bit DAC for a 4 ns duration. The 6-bit DAC code is the synaptic weight that modulates the amplitude of the input pulse event.

The right half shows the AdEx neuron circuit which receives the two input lines from each synapse column and implements synaptic dynamics within the synaptic input subcircuits. The current output of the synaptic input circuits (excitatory/inhibitory) is integrated on the neuronal membrane, formed by a 6-bit tunable capacitor labeled  $C_{\text{mem}}$ . The neuron introduces a membrane leak circuit using a source-degenerated OTA in unity gain feedback with a conductance  $g_{\text{m}}$  that models  $g_{\text{leak}}$ . During the refractory period, the circuit utilizes this very leak conductance as reset conductance by enabling higher

Fig. 2: Simplified schematic diagrams of: a) a single integrated AdEx neuron circuit in a point-neuron configuration receiving input events from a synapse column. b) adaptation circuit. c) exponential circuit. d) tunable resistor used inside the adaptation circuit.

conductance (approx.  $\times 10 g_{\rm m}$ ). When the membrane potential  $V_{\rm mem}$  on the capacitor  $C_{\rm mem}$  reaches a specified threshold  $V_{\text{thresh}}$ , the comparator toggles its output to logic high ( $V_{\text{OH}}$ ). The output of the comparator triggers a pulse with a variable pulse-width duration that is fed to the merged leak/reset circuit. This pulse input connects the membrane to the reset potential  $V_{\rm rst}$  via the OTA conductance  $(g_{\rm m})$ , as well as enabling its high-conductance mode [32] (for  $\times 10g_m$  reset conductance). As soon as the membrane  $(V_{mem})$  resets, the comparator outputs logic low  $(V_{OL})$ . At the end of refractory period, the OTA switches back to low-conductance mode where the leak conductance is  $g_{\rm m}$ . This circuit realizes the conductancebased reset as opposed to a fixed reset suggested by the I&F neurons to model the relative conductances between different compartments - which, for example, enables the effect of synaptic excitation and inhibition on the neuron compartment during plateau potentials. If we neglect the synaptic inputs, the height of the plateau potentials is then determined by the potential  $V_{\rm NMDA}$ .

The digital output event also enables the adaptation circuit (for a programmable duration, see fire<sub>adapt</sub>) connected to the membrane via the switch  $S_{12}$ . An exponential circuit integrates a positive exponentially increasing current onto the membrane enabled by the digital implementation of exponential threshold  $(W_{V_T})$ , and connected to the membrane via the switch  $S_{13}$ . The input synaptic events may also bypass membrane integration, evoking a single output event for every single input. These inputs are enabled via the switch  $S_{14,15}$  for excitatory and inhibitory bypassed inputs. An integrated buffer  $A_0$  reads out multiplexed neuronal voltages. These include the membrane potential  $(V_{\text{mem}})$ , the voltage at the two synaptic input lines  $(V_{\text{syn,exc}}, V_{\text{syn,inh}})$ , as well as the adaptation voltage  $V_{\text{w}}$  inside the adaptation circuit. Similarly, another pin marked Istim helps in measurement, for example for measuring output current generated by each subcircuit. The membrane also receives a current input from on-chip current source via  $S_8$  (tunable per neuron), to tune the offset currents as well as to stimulate the membrane without an external source.

The neuron's voltage and current bias parameters are stored on-chip in analog memory [39] adjacent to every neuron circuit. A total of 20 dedicated biases tune every neuron (14 currents, 6 voltages) whereas 3 current biases are shared among all neurons in the array. These biases can be tuned with a 10bit resolution. All digital configuration bits, e.g., the enables of switches are stored in a 40-bit SRAM memory in each neuron. In the implemented chip all SRAM bits are jointly controlled by a global synchronous controller.

## C. Neuron Configurations

To summarize the neuron implements the following firing configurations:

1) Bypass: This mode generates an output event for every input synaptic event. This is achieved in a digital I/O configuration and all analog circuits except for the bypass inputs (controlled by  $S_{14,15}$ ) are disabled. Input synaptic events with a large pulse amplitude and pulse-width > 30 ns trigger this bypass link. The bypass circuit is an inverter with shifted trip-

points, driven by the voltage drop created by the synaptic event at the input synaptic line.

2) *LIF:* This reduces the neuron circuit to the LIF configuration [31] where all non-LIF extensions are disabled. The output tri-state buffer formed by switch  $S_{16}$  is enabled.

3) AdEx: The standard LIF neuron when supported with AdEx extensions evoke exponential spikes and accelerating and decelerating spike-triggered adaptation. The switches  $S_{12,13}$  enable the two terms.

4) Plateau Potentials: Along with Sodium spikes emulated by the standard LIF and AdEx configurations [40], the neuron is designed to evoke broad spikes, such as the Calcium spikes or NMDA plateau potentials [34]. When enabled, the membrane is held on to the NMDA plateau potential  $V_{\rm NMDA}$ for a duration  $\tau_{\rm NMDA}$ , followed by a return to the leak potential  $V_{\rm leak}$  at the end of pulse duration. Due to a counter-based digital implementation a very large pulse-width duration of up to 1 sec is possible [41].

5) Multi-compartment & High Input Count: This configuration utilizes multiple point-neuron circuits in the neuron array [34]. For high input count it shunts multiple adjacent membrane capacitors to realize neurons with increased synaptic input count in the merged neuronal membrane. For multicompartment realization [34], [42], two independent compartments are connected via an inter-compartmental resistance, for example, to model somatic and dendritic compartments.

#### IV. CIRCUIT IMPLEMENTATION

## A. Adaptation Circuit

The adaptation circuit implements accelerating and decelerating spike-triggered adaptation as well as adaptation current given by Eq. 3 and Eq. 4. A simplified circuit schematic is shown in Fig. 2b. The circuit has been inspired from our firstgeneration design presented in [38].

The top right part of the circuit implements Eq. 3, where the output current w generated by the OTA with conductance  $g_a$  emulates the model's subthreshold conductance parameter a. It senses the difference between  $V_{\text{leak}}$  and  $V_w$  at its inputs and switches them with a configuration bit  $e_{N_a}$  to realize negative  $g_a$ . The OTA is a source-degenerated architecture identical to the one used in the leak term. (for details, see [32]).

The lower right part of the schematic implements Eq. 4 where the input current  $g_w(V_w - V_{mem})$  is integrated on the adaptation capacitor  $C_{\rm w}$ . The membrane is buffered by an OTA labeled  $A_w$  and a tunable floating conductance  $g_w$  connects this buffered membrane to the capacitor  $C_{\rm w}$ . The circuit is enabled by asserting the bit  $en_{adapt}$  and dis-asserting  $en_{capMerge}$ . This connects the output to the membrane  $V_{\text{mem}}$  via switch  $S_{a0}$  while connecting the capacitor  $C_w$  to the node  $V_w$ . The configuration bit encapMerge should always stay low during adaptation usage - however when it is disabled (e.g., in LIF mode), the unused adaptation capacitor can be merged with the membrane capacitor  $C_{mem}$  by enabling  $en_{capMerge}$  essentially increasing the maximum  $C_{\text{mem}}$  from 2.36 pF to 4.36 pF. The voltage on the capacitor  $V_{\rm w}$  emulates the adaptation variable in the model. The presence of a tunable conductance implements adaptation time constant  $\tau_{\rm w} = R_{\rm w}C_{\rm w}$ , where  $R_{\rm w} = 1/g_{\rm w}$ .

The left side of the circuit shows a charge pump, where an on-chip bias current  $I_w$  is sourced or sinked from the node  $V_{\rm w}$  via the pass transistors  $S_{\rm p}$  and  $S_{\rm n}$  (assuming en<sub>adapt</sub> = 1). The circuit is triggered by the input event fire<sub>adapt</sub>, whose presence indicates a digital spike event. The pulsewidth of fire<sub>adapt</sub> is variable and an equivalent charge q = $I_{\rm w} \cdot t_{\rm pulse}$  is integrated (or removed) with every input event from the capacitor  $C_{\rm w}$ . The configuration bit  $en_{\rm Vw}$  controls whether to source or sink current  $I_w$ , essentially implementing either decelerating or accelerating output spiking response. The charge pump therefore models the spike-triggered adaptation in terms of integrated voltage, since every output event updates  $V_{\rm w} \rightarrow V_{\rm w} \pm \Delta V_{\rm w}.$

The switches  $S_{a0}$ ,  $S_{a1}$  and  $S_{cm}$  are transmission gate switches. All multiplexed inputs are implemented using transmission-gate multiplexers. The tunable conductance  $g_w$  is implemented as a high value tunable floating resistor.

1) Tunable Floating Resistor: The adaptation circuit requires a high value floating tunable resistor that implements a resistive range from 16 M $\Omega$  to 600 M $\Omega$  [33], [43]. The circuit to implement this large resistive range is designed using bulk-drain connected PMOS devices [44], [45]. The simplified schematic of the implemented resistor is shown in Fig. 2d. Between the positive and negative resistor terminals are two series PMOS bulk-drain connected transistors  $M_1$  and  $M_2$ . Each of the two devices connect the bulk terminals to its drain (instead of source) and biased in subthreshold region to contribute a very large resistance. Both of the devices are connected back-to-back such that their source terminals are connected. In this arrangement, only one of the devices is connected as a bulk-drain connected device at a time. When  $V_{inN} > V_{inP}$ , the device  $M_2$  is in bulk-drain configuration, while  $M_1$  is in the nominal bulk-source connected configuration and therefore  $R_{\text{SD2}} \gg R_{\text{SD1}}$ . This is because denominations of source and drain are with respect to MOS terminal potentials. For  $V_{inP} > V_{inN}$ , the roles flip and  $R_{SD1} \gg R_{SD2}$ . A single bias current  $I_{\text{bias}}$  tunes the resistance. A cascode current mirror realized using the transistors  $M_{3-6}$  mirrors the bias current  $I_{\text{bias}}$ , while the transistor  $M_7$  sets the bias point.

## B. Exponential Circuit

This circuit integrates an exponentially rising positive current on the membrane capacitor, as governed by the AdEx model. The schematic is shown in Fig. 2c. The circuit uses transistor  $M_1$  to sense the membrane potential at its gate. Together with transistor  $M_2$ , it provides an inverted membrane voltage to  $M_3$ . It further ensures that this inverted voltage range of membrane potential (from 0.6 V to 1.05 V) biases  $M_3$  in its subthreshold region. To maximize this range  $M_3$  is chosen as a high- $V_{\rm th}$  device. In subthreshold region the drain current of a transistor for drain-source drop  $V_{\rm DS} > 4U_{\rm T}$  is:

$$I_{\rm D} = I_0 e^{\frac{V_{\rm GS} - V_{\rm th}}{nU_{\rm T}}} \tag{6}$$

where  $I_0 = 2n\mu C_{\text{ox}} \frac{W}{L} U_T^2$  [46]. The parameter *n* is equivalent to  $\frac{C_{\text{ox}} + C_{j0}}{C_{\text{ox}}}$  where  $C_{j0}$  is the junction-depletion capacitance per unit area of a reversed bias diode (0 V bias).

FPGA

board

USB

Main

Array of 32 neurons

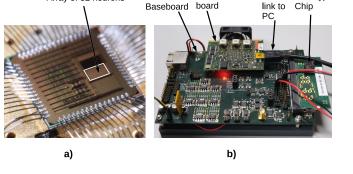

Fig. 3: a) Chip micrograph. b) The prototype evaluation system.

The output drain current of transistor  $M_3$  therefore increases exponentially with a linearly rising membrane potential. It is copied by a current mirror formed by  $M_{4,5}$  and further by three separate current mirrors formed by  $M_{6,7}$ ,  $M_{6,8}$  and  $M_{6,9}$ . The input/output current ratio of each of the three mirrors is 1:0.25, 1:0.5 and 1:1. The output of all three mirrors is merged into a single output current and integrated onto the membrane. The three mirrors are enabled by a 3-bit digital bus labeled  $W_{V_{T}}$  – essentially realizing the digital exponential threshold of the model parameter  $V_{\rm T}$ . The exponential circuit is enabled when the output switch is asserted by bit enexp. The circuit limits the output current above a membrane voltage of approx. 1.1 V, since  $V_{SD}$  of transistors  $M_{7,8,9}$  is below  $V_{SD,sat}$  in this case. The 3-bit  $W_{V_T}$  as well as all configuration bits are stored in the local SRAM integrated per neuron.

#### C. Analog Read-Out

The output of read-out buffers within each neuron circuit (see V<sub>readOut</sub> in Fig. 2a) are connected via two output buffers (not shown) to the chip pads. Out of the 32 neuron read-out buffers, all odd ones are connected to the first output buffer, while all even read-out buffers are connected to the second output buffer. This scheme enables us to read out any two simultaneous voltages from the neuron array.

## V. EXPERIMENTAL RESULTS

The array of 32 AdEx neurons has been integrated on a prototype chip occupying a total of 286  $\mu$ m  $\times$  376  $\mu$ m. Each neuron occupies 11.76  $\times$  286  $\mu m$  of silicon area. The prototype chip is fabricated in a low-K 1P9M 65-nm lowpower digital CMOS process with a total die area of 1.9  $\times$  1.9 mm<sup>2</sup>. The bonded die on the chip daughterboard as well the measurement setup is shown in Fig. 3. The data has been acquired using a Keithley 2635B Sourcemeter for current measurements as well as a LeCroy Wavesurfer 44Xs digital oscilloscope for transient signals. The PCB baseboard designed for measurement comprises of an on-board Xilinx Spartan-6 FPGA that takes command packets via a USB interface. The chip and all neuron parameters are directly programmable via a C++/Python based software setup.

Prototype

Chip

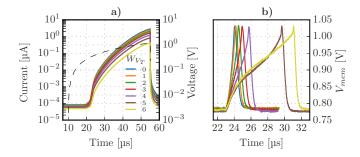

Fig. 4: a) A simulation where the exponential circuit is exposed to a ramp voltage input and its output current is plotted on a logarithmic-scale, while sweeping the exponential threshold parameter  $W_{V_T}$ . b) Measured successive membrane traces from the prototype chip with swept  $W_{V_T}$  [40].

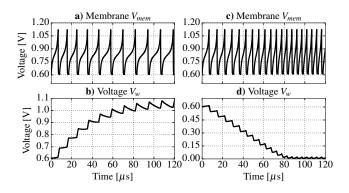

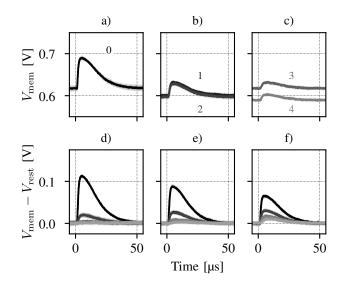

Fig. 5: Spike-triggered adaptation: (a,b) Decelerating membrane as a result of increasing adaptation variable  $V_{\rm w}$ . (c,d) Accelerating membrane as a result of decreasing adaptation variable  $V_{\rm w}$ .

## A. Exponential

To demonstrate the functionality of the exponential circuit, it is subjected to a slow rising ramp, while its  $W_{V_T}$  is swept. Fig. 4a shows this rising voltage ramp (dashed line) in logscale as well as the corresponding output currents of the exponential circuit. Note that the output exponential current increases as  $W_{V_T}$  decreases, with 0 indicating all mirrors enabled. The output log current increases near-linearly for the swept values of  $W_{V_T}$  for the required current range from 10 nA to  $\geq 1 \ \mu$ A.

Fig. 4b shows the experimental results of the neuron firing tonically as a results of input current, where the exponential current pulls the membrane voltage up. The digital parameter  $W_{V_T}$  is being swept again during successive runs. Note how the strength of exponential current decreases with every decreasing value of  $W_{V_T}$ . Further, one may also notice the finite time constant that exists during the membrane reset – this is due to the conductance based reset realization.

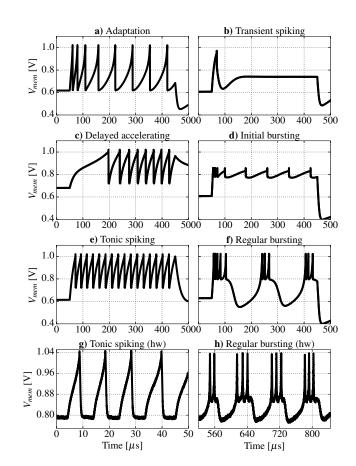

Fig. 6: Firing patterns of the designed AdEx neuron. From a) to f) are those simulated on a circuit netlist [33], [47], whereas g) and h) are measured results from the prototype chip [40].

## B. Adaptation

The accelerating and decelerating spike-triggered adaptation realized by the integration of adaptation circuit is shown in Fig. 5. The adaptation voltage  $V_w$  grows from 0.6 V and increments approx 0.1 V with every spike evoked – resulting in decelerating adaptation (Fig. 5a and Fig. 5b). With the same parameters and toggled en<sub>Vw</sub>, a decreasing  $V_w$  results which accelerates the membrane (Fig. 5c and Fig. 5d).

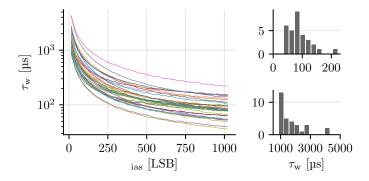

The time constant of the adaptation circuit ( $\tau_w = R_w C_w$ ) is tuned with the resistor's tunable bias since the capacitor is fixed at 2 pF. The achievable time constants in the array of 32 neurons is shown in Fig. 7. The short time constants below 100 µs are realized by setting the maximum value of resistor's tunable current bias (1 µA), whereas the long time constants are realized with a minimum available bias of 15 nA. The measured decaying traces show the mismatch between individual curves. This mismatch is more pronounced when the circuit is biased with very small current compared to short time constants where bias current is set much higher. A distribution of minimum and maximum adaptation time constants measured from 31 adaptation circuits on the prototype chip is shown on the right side of Fig. 7.

Fig. 7: The adaptation time constant ( $\tau_w$ ) as a function of bias current of the floating resistor. An uncalibrated distribution of minimum and maximum  $\tau_w$  is plotted for 31 samples.

## C. Example Firing Patterns

Being a two-variable neuron model, the AdEx circuit reproduces a diverse set of firing patterns [48] known from biological neurons [49], and typically characterized by the response to a step current stimulus. Fig. 6 shows a set of example firing patterns from the designed circuit. Fig. 6a-f show the adaptation, transient spiking, delayed accelerating, initial bursting, tonic spiking as well as regular bursting. These have been simulated on the circuit netlist prior to fabrication on the chip. Fig. 6g,h shows tonic spiking and regular bursting as measured on the prototype chip.

# D. Multi-Compartment Configuration Using Passive Dendrites

To demonstrate the inter-compartment functionality we configure a chain of resistively connected neurons as highlighted in Fig. 8a. Fig. 9 shows the attenuation of a stimulus—applied to compartment 0—as it passes the neighboring compartments. Tuning the strength of the variable resistor changes the propagation length of the initial stimulus (panels d–f). The varying levels of shift are caused by input offsets of the sourcedegenerated leak OTA and the readout amplifier in different compartments.

# E. Multi-Compartment Configuration Using Active Dendrites

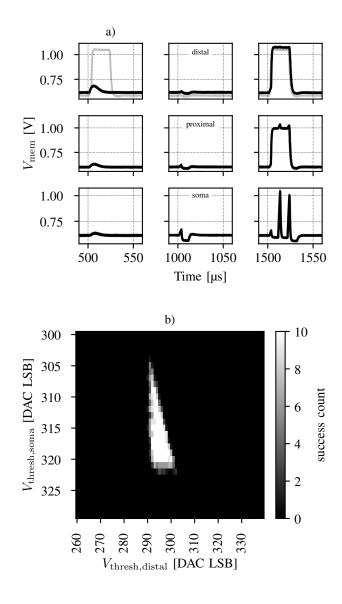

To showcase the successful operation of multiple AdEx circuits in a multi-compartment configuration we implement a benchmark that is derived from measurements described in [50]: The authors show that single neurons are capable of acting as coincidence detectors that are dependent on the site of stimulation. In our benchmark, we reduce the biological reference to the following target behavior: A neuron contains three compartment is configured for sodium-like spikes—the exponential term is enabled and the reset potential is below the resting potential, with a comparatively short refractory period. The other compartments are configured as active compartments which can generate plateau potentials, so the refractory period is set to a higher value and the reset potential is set significantly higher than the leakage potential. The resulting array

Fig. 8: a) Compartment connectivity for the experiment shown in Fig. 8. Compartment 0 is the start of a chain of compartments, two of which (1 and 2, 3 and 4, etc.) are interconnected directly. Each such pair is connected to its neighbors using the inter-compartment resistors. b) Compartment connectivity for the experiment shown in Fig. 9. Four physical compartments form a chain of three resistively connected parts. The distal (compartment 0) and soma (compartment 3) units receive external synaptic input. Compartments 0 and 1 are configured to produce plateau potentials. Compartment 2 is passive and has its leak and reset circuit disabled. Compartment 3 is configured for Na-spikes.

configuration is shown in Fig. 8b. The functional requirement on the neuron is that a somatic stimulus of a certain strength evokes exactly one spike at the soma and no spike at the distal dendrite. Stimulus at the distal dendrite should cause no spikes. Both stimuli combined should evoke a plateau potential in the dendrite and a burst in the soma compartment.

To achieve this, the refractory times are configured such that the duration of a plateau potential is approximately three times the refractory period in the soma. A coarse parameter sweep is used to determine the approximate parameter values that lead to the desired behavior. Fig. 10 b) shows the result of ten repeated parameter sweeps over the somatic and dendritic firing threshold. The panel indicates the number of experiment runs in which the target behavior is achieved. Although the available region is narrow, the stability of the system for repeated runs is sufficient to reliably reproduce the behavior. Parameters from the center of the stable region are selected and the membrane voltage is recorded for 60 repeated trials. The results are shown in Fig. 10 a): Only one out of 60 samples deviates from the standard response shape (shown with gray color). The height of the voltage spikes in the bottom right panel in Fig. 10 a) differs because the soma compartment is configured with small (one out of 15 clock cycles) holdofftime at the end of the refractory period (during hold-off the neuron is set to the leak conductance but no new spike may trigger). Consequently, in the presence of a plateau potential in

Fig. 9: Five neighboring neuron circuits are configured to form a multi-compartment neuron. a)-c) The compartments 0-6 are interconnected in a chain. Each even compartment connects via  $R_{ic}$  to the shared line, whereas each odd compartment connects to the shared line and, using  $S_{ic}$ , to its right neighbor. Compartment 0 is stimulated via the synaptic input at time 0. The attenuated signal can be observed in consecutive compartments. b) Because two neighboring compartments, starting from compartment 1, are short-circuited, the same response is recorded over two output buffers. c) Due to different mismatch in the readout chain, the recorded signals show a varying degree of offset (see [31], [32] for offset characterization.) d)f) Membrane voltage for all compartments in the chain after subtracting the baseline resting voltage  $V_{\text{rest}}$ . The current bias which controls the inter-compartment resistance is varied: d)  $I_{\text{Ric}} = 50 \text{ LSB e}$ )  $I_{Ric} = 150 \text{ LSB f}$ )  $I_{\text{Ric}} = 1000 \text{ LSB}$ . Each line shows one standard deviation acquired from ten consecutive measurements.

the neighboring compartment the membrane voltage is pulled up above the firing threshold before a new spike is emitted and a reset is triggered.

## VI. DISCUSSION

This paper summarized the AdEx and multi-compartment extensions developed to enhance the base 65 nm CMOS LIF neuron for the HICANN-DLS prototype chip. For pointneuron model enhancement, we integrated adaptation and exponential circuit to the modular LIF neuron architecture. The AdEx enhancement let us qualitatively reproduce exponential spikes, and diverse spiking and bursting regimes. Using a floating tunable resistor we can tune very long adaptation time constants. Further, by utilizing controlled inter-compartmental resistance and transmission-gate switches, we extend the AdEx emulation to multiple compartments. The conductance-based

Fig. 10: Multi-compartment configuration. a) Membrane voltage of individual compartments in an interconnected neuron. Top row: distal compartment, center row: proximal compartment, bottom row: soma compartment. Left column: A single input spike is sent to the distal compartment. Center column: A single input spike is sent to the soma compartment, which evokes a spike event. Right column: Both stimuli are combined. The stimulus magnitude is unchanged. Each panel shows 20 superimposed voltage recordings. Because at most two compartments can be recorded simultaneously, the data shown in different rows stem from consecutive experiments. Thus, data from 60 experiments are shown in total. b) Parameter sweep of the firing threshold in the soma and distal compartments. The color indicates the number of successful repetitions out of ten trials. The success is evaluated using the number of spikes in the soma and distal compartments (see text).

| multi-comp. AdEx             |

|------------------------------|

| 32                           |

| $11.76 \times 286 \ \mu m^2$ |

| 2.5/1.2 V                    |

| 65-nm CMOS                   |

| $\times 1000$                |

| 3 current biases             |

| 20 (14 I-bias, 6 V-bias)     |

| 40-bit SRAM                  |

| 2.36 pF (6-bit config.)      |

| 10 µA, 4 ns pulses           |

|                              |

<sup>1</sup> available from on-chip tunable capacitive memory cells [39], [51]

- <sup>2</sup> binary weighted with 37 fF unit capacitance; extendable to 4.36 pF if adaptation is not used

- <sup>3</sup> amplitude and length of each current pulse emitted by the synapse circuit

TABLE I: A summary of neuron array specifications.

|                                      | TrueNorth         | Neurogrid        | This          |

|--------------------------------------|-------------------|------------------|---------------|

|                                      | [52]              | [53]             | Work          |

| CMOS tech. [nm]                      | 28                | 180              | 65            |

| Architecture                         | digital           | analog<br>subth. | analog        |

| Speed-up <sup>a</sup>                | $\times 1$        | $\times 1$       | $\times 1000$ |

| Neuron Model                         | augmented<br>LIF  | QIF              | AdEx          |

| Dedicated Parameters                 | Yes               | No               | Yes           |

| Biophysical<br>Dynamics <sup>b</sup> | No                | Yes              | Yes           |

| Neuron Area [µm <sup>2</sup> ]       | 2900 <sup>c</sup> | 1800             | 3372          |

<sup>a</sup> compared to biological real-time

<sup>b</sup> tunable  $\tau_{refr}$ ,  $\tau_{mem}$ ,  $\tau_{syn}$

<sup>c</sup> multiplexed 256 times per time step

TABLE II: An overview of neuron model specifications in large-scale neuromorphic architectures.

reset and digital pulse control let us emulate the broad spikes (plateau potentials) known from apical and thin dendrites. We have demonstrated the functionality of emulated passive dendrites in the circuit by connecting multiple adjacent compartments. Furthermore, we have configured two adjacent neuronal compartments of an on-chip neuron as proximal and distal dendrites to demonstrate active coincidence detection that leads to plateau potentials in proximal dendrites and a burst of sodium-like spikes in the somatic compartment.

This prototype chip demonstrates a scaled-down AdEx multi-compartment neuron accelerated to 1000 times compared to biological real-time. Each neuron occupies 11.76  $\times$  286 µm<sup>2</sup>, including the digital circuits for pulse control,

AdEx multi-compartment extensions and dedicated SRAM. This neuron circuit together with number of input synapses and analog bias memory is scheduled to scale up for a larger chip that will feature 512 neurons with increased silicon area. The achieved neuron specifications are listed in Table I.

The neuron circuit reduces the effect of device mismatch and resulting input offsets after calibration (see [32] for calibration of LIF circuits). The variation in adaptation time constant among individual neurons is to be calibrated for, although it does not preclude successful network operation. During the design phase, the possibility of calibration has been ensured for the circuit netlist using device Monte Carlo models. The simulated energy per output spike expended by the neuron circuit is 200 pJ for a 300 Hz output firing rate. The energy per synaptic event depends on the realized network configuration, number of input synapses, etc., and for the first-generation 180 nm wafer-scale system varies between 100 pJ and 10 nJ [54].

A plethora of silicon neuron designs can be found in literature - from simple LIF neurons to two-dimensional models and those implementing dendritic properties in analog circuits [38], [53], [55]-[70] - as well as digital phenomenological implementations [71]-[75]. Here we restrict our comparison to neuron circuits implemented for large-scale neuromorphic architectures, and summarized in Table II. The TrueNorth neuron [52], [73] features an augmented LIF neuron model in a scaled 28 nm CMOS process targeted mainly for synthetic computation. The implementation therefore does not feature tunable biophysical dynamics such as synaptic time constant or refractory period duration. The neuron occupies 2900 µm<sup>2</sup> despite a scaled process node, but the possibility of timemultiplexing reduces the effective area by 256 times. In comparison, Neurogrid [53] implements biophysical dynamics like the BrainScaleS system. The neuron model is a twocompartment quadratic model implemented using subthreshold MOS dynamics in a 180 nm CMOS process. The subthreshold implementation typically reduces the occupied area. The system is tiled in NeuroCores, each containing 64k neurons that share the neuron parameters. Both TrueNorth and Neurogrid system implement real-time dynamics compared to the accelerated implementation of the BrainScaleS system and the current work. Our current multi-compartment AdEx neuron emulation with its tunable dynamics present a biologically plausible neuromorphic platform. The distributed memory architecture with dedicated analog parameter memory and local SRAM in every neuron makes the system highly flexible, re-configurable and amenable to calibration that evolves as a profoundly nonvon Neumann implementation.

## VII. CONCLUSION

In this work, we presented circuit extensions to enhance the previously designed modular LIF neuron architecture to multi-compartment AdEx model. The architecture presented a re-configurable circuit for firing configurations ranging from simple LIF to multi-compartment and AdEx modes. It allowed us to reproduce exponential and adapting spike response as well as diverse spiking firing patterns. By integrating multicompartment extensions, we have demonstrated properties

## ACKNOWLEDGMENT

The authors would like to express their gratitude to Andreas Hartel, Christian Pehle, Korbinian Schreiber, Sebastian Billaudelle and David Stöckel for the teamwork during design, verification and measurement of the prototype chip. Further, the authors would like to thank Eric Müller, Sebastian Schmitt and Mihai Petrovici for systems support and theoretical discussions.

The authors would like to thank TU-Dresden for providing the PLL macro cell [76] used in the prototype chip.

## AUTHOR CONTRIBUTION

S.A.A. wrote the manuscript, designed and measured AdEx neuron circuit array. P.M. devised the pre tape-out calibration, performed experiments on structured neurons and wrote Sec. V-D & Sec. V-E. G.K. designed the digital circuits for neuron pulse control. L.K. verified firing patterns on the pre tape-out netlist. Y.S. provided measurements on adaptation time constant and software support. A.G. was the chip assembly responsible. J.S. was the overall system architect and designed multi-compartment/non-linear dendritic extensions. The conceptual advice was given by K.M.

## REFERENCES

- E. M. Izhikevich, "Which model to use for cortical spiking neurons?" *IEEE Transactions on Neural Networks*, vol. 15, no. 5, pp. 1063–1070, Sept 2004.

- [2] L. Lapicque, "Recherches quantitatives sur l'excitation electrique des nerfs traitee comme une polarization," *Journal de Physiologie et Pathologie General*, vol. 9, pp. 620–635, 1907.

- [3] R. Stein, "Some Models of Neuronal Variability," *Biophysical Journal*, vol. 7, no. 1, pp. 37–68, Jan. 1967.

- [4] T. Pfeil, A. Grübl, S. Jeltsch, E. Müller, P. Müller, M. A. Petrovici, M. Schmuker, D. Brüderle, J. Schemmel, and K. Meier, "Six networks on a universal neuromorphic computing substrate," *Frontiers in Neuro-science*, vol. 7, p. 11, 2013.

- [5] G. Indiveri, E. Chicca, and R. Douglas, "A VLSI array of low-power spiking neurons and bistable synapses with spike-timing dependent plasticity," *IEEE Transactions on Neural Networks*, vol. 17, no. 1, pp. 211–221, Jan 2006.

- [6] J.-s. Seo, B. Brezzo, Y. Liu, B. D. Parker, S. K. Esser, R. K. Montoye, B. Rajendran, J. A. Tierno, L. Chang, D. S. Modha *et al.*, "A 45nm cmos neuromorphic chip with a scalable architecture for learning in networks of spiking neurons," in *Custom Integrated Circuits Conference (CICC)*, 2011 IEEE. IEEE, 2011, pp. 1–4.

- [7] E. M. Izhikevich, "Simple Model of Spiking Neurons," *IEEE Transac*tions on Neural Networks, vol. 14, pp. 1569–1572, 2003.

- [8] P. Latham, B. Richmond, P. Nelson, and S. Nirenberg, "Intrinsic dynamics in neuronal networks. i. theory," *Journal of neurophysiology*, vol. 83, no. 2, pp. 808–827, 2000.

- [9] R. Brette and W. Gerstner, "Adaptive exponential integrate-and-fire model as an effective description of neuronal activity," *J. Neurophysiol.*, vol. 94, pp. 3637 – 3642, 2005.

- [10] J. Touboul and R. Brette, "Dynamics and bifurcations of the adaptive exponential integrate-and-fire model," *Biological Cybernetics*, vol. 99, no. 4, pp. 319–334, Nov 2008. [Online]. Available: http://dx.doi.org/10.1007/s00422-008-0267-4

- [11] R. Jolivet, A. Rauch, H.-R. Lüscher, and W. Gerstner, "Integrate-andfire models with adaptation are good enough," in *Advances in neural information processing systems*, 2006, pp. 595–602.

- [12] A. Rauch, G. La Camera *et al.*, "Neocortical pyramidal cells respond as integrate-and-fire neurons to in vivo–like input currents," *Journal of neurophysiology*, vol. 90, no. 3, pp. 1598–1612, 2003.

- [13] W. Gerstner, W. Kistler, R. Naud, and L. Paninski, *Neuronal Dynamics*. Cambridge University Press, 2014, p. 24.

- [14] C. Koch and I. Segev, "The role of single neurons in information processing." *Nat Neurosci*, vol. 3 Suppl, pp. 1171–1177, Nov. 2000.

- [15] I. Segev, "Single neurone models: oversimple, complex and reduced," *Trends in neurosciences*, vol. 15, no. 11, pp. 414–421, 1992.

- [16] W. Rall, "Theoretical significance of dendritic trees for neuronal inputoutput relations," *Neural theory and modeling*, pp. 73–97, 1964.

- [17] G. Liu, "Local structural balance and functional interaction of excitatory and inhibitory synapses in hippocampal dendrites," *Nature neuroscience*, vol. 7, no. 4, p. 373, 2004.

- [18] H. B. Barlow and R. M. Hill, "Selective sensitivity to direction of movement in ganglion cells of the rabbit retina," *Science*, pp. 412–414, 1963.

- [19] W. R. Taylor, S. He, W. R. Levick, and D. I. Vaney, "Dendritic computation of direction selectivity by retinal ganglion cells," *Science*, vol. 289, no. 5488, pp. 2347–2350, 2000.

- [20] M. Konishi, "How the owl tracks its prey: experiments with trained barn owls reveal how their acute sense of hearing enables them to catch prey in the dark," *American Scientist*, vol. 61, no. 4, pp. 414–424, 1973.

- [21] C. Carr and M. Konishi, "A circuit for detection of interaural time differences in the brain stem of the barn owl," *Journal of Neuroscience*, vol. 10, no. 10, pp. 3227–3246, 1990.

- [22] G. J. Stuart and B. Sakmann, "Active propagation of somatic action potentials into neocortical pyramidal cell dendrites," *Nature*, vol. 367, no. 6458, p. 69, 1994.

- [23] G. Stuart, N. Spruston, B. Sakmann, and M. Häusser, "Action potential initiation and backpropagation in neurons of the mammalian cns," *Trends in neurosciences*, vol. 20, no. 3, pp. 125–131, 1997.

- [24] M. London and M. Häusser, "Dendritic computation," Annu. Rev. Neurosci., vol. 28, pp. 503–532, 2005.

- [25] J. C. Magee and D. Johnston, "A synaptically controlled, associative signal for hebbian plasticity in hippocampal neurons," *Science*, vol. 275, no. 5297, pp. 209–213, 1997.

- [26] H. Markram, J. Lübke, M. Frotscher, and B. Sakmann, "Regulation of synaptic efficacy by coincidence of postsynaptic aps." *Science*, vol. 275, pp. 213–215, 1997.

- [27] M. Häusser, N. Spruston, and G. J. Stuart, "Diversity and dynamics of dendritic signaling," *Science*, vol. 290, no. 5492, pp. 739–744, 2000.

- [28] J. Schiller, G. Major, H. J. Koester, and Y. Schiller, "Nmda spikes in basal dendrites of cortical pyramidal neurons," *Nature*, vol. 404, no. 6775, p. 285, 2000.

- [29] M. E. Larkum, T. Nevian, M. Sandler, A. Polsky, and J. Schiller, "Synaptic integration in tuft dendrites of layer 5 pyramidal neurons: a new unifying principle," *Science*, vol. 325, no. 5941, pp. 756–760, 2009.

- [30] S. D. Antic, W.-L. Zhou, A. R. Moore, S. M. Short, and K. D. Ikonomu, "The decade of the dendritic nmda spike," *Journal of neuroscience research*, vol. 88, no. 14, pp. 2991–3001, 2010.

- [31] S. A. Aamir, P. Müller, A. Hartel, J. Schemmel, and K. Meier, "A highly tunable 65-nm cmos LIF neuron for a large scale neuromorphic system," in *Proc. 42nd ESSCIRC Conf.*, Sept 2016, pp. 71–74.

- [32] S. A. Aamir, Y. Stradmann, P. Müller, C. Pehle, A. Hartel, A. Grübl, J. Schemmel, and K. Meier, "An accelerated LIF neuronal network

array for a large scale mixed-signal neuromorphic architecture," *arXiv* preprint, arXiv:1804.01906.

- [33] S. A. Aamir, P. Müller, L. Kriener, G. Kiene, J. Schemmel, and K. Meier, "From lif to adex neuron models: Accelerated analog 65 nm cmos implementation," in *IEEE Biomedical Circuits and Systems Conference (BioCAS)*, October 2017.

- [34] J. Schemmel, L. Kriener, P. Müller, and K. Meier, "An accelerated analog neuromorphic hardware system emulating nmda- and calciumbased non-linear dendrites," in *International Joint Conference on Neural Networks (IJCNN)*, May 2017, pp. 2217–2226.

- [35] J. Schemmel, "Brainscales 2: A novel architecture for analog accelerated neuromophic computing and hybrid plasticity," *Internal document, ASIC Lab., Kirchhoff-Institute for Physics*, 2017.

- [36] J. Schemmel, D. Brüderle, A. Grübl, M. Hock, K. Meier, and S. Millner, "A wafer-scale neuromorphic hardware system for large-scale neural modeling," in *Proc. ISCAS*, 2010, pp. 1947–1950.

- [37] J. Schemmel, S. A. Aamir, S. Billaudelle, A. Grübl, A. Hartel, G. Kiene, C. Pehle, K. Schreiber, and K. Meier, "An analog neurormorphic hardware system combining structured neurons with hybrid learning," *IEEE Transactions of Circuits and Systems - I*, in preparation 2018.

- [38] S. Millner, A. Grübl, K. Meier, J. Schemmel, and M.-O. Schwartz, "A VLSI implementation of the adaptive exponential integrate-and-fire neuron model," in *Advances in NIPS*, 2010, pp. 1642–1650.

- [39] M. Hock, A. Hartel, J. Schemmel, and K. Meier, "An analog dynamic memory array for neuromorphic hardware," in *Circuit Theory and Design (ECCTD)*, 2013 European Conference on, Sep. 2013, pp. 1– 4.

- [40] S. A. Aamir, "Mixed signal circuit implementation of spiking neuron models," Ph.D. dissertation, Karlsruhe Institute of Technology, 2018.

- [41] G. Kiene, "Mixed-signal neuron and readout circuits for a neuromorphic system," Master's thesis, Universität Heidelberg, 2017.

- [42] S. Millner, A. Hartel, J. Schemmel, and K. Meier, "Towards biologically realistic multi-compartment neuron model emulation in analog VLSI," in *Proceedings ESANN 2012*, 2012.

- [43] P. Müller, "Modeling and verification for a scalable neuromorphic substrate," Ph.D. dissertation, Universität Heidelberg, 2017.

- [44] F. Cannillo, C. Toumazou, and T. S. Lande, "Bulk-drain connected load for subthreshold mos current-mode logic," *Electronics Letters*, vol. 43, no. 12, pp. 662–664, June 2007.

- [45] A. Tajalli, E. J. Brauer, Y. Leblebici, and E. Vittoz, "Subthreshold source-coupled logic circuits for ultra-low-power applications," *IEEE J. Solid-State Circuits*, vol. 43, no. 7, pp. 1699–1710, July 2008.

- [46] C. C. Enz, F. Krummenacher, and E. A. Vittoz, "An analytical mos transistor model valid in all regions of operation and dedicated to lowvoltage and low-current applications," *Analog integrated circuits and signal processing*, vol. 8, no. 1, pp. 83–114, 1995.

- [47] L. Kriener, "Characterization of single-neuron dynamics in the development of neuromorphic hardware," Master's thesis, Heidelberg University, March 2017.

- [48] R. Naud, N. Marcille, C. Clopath, and W. Gerstner, "Firing patterns in the adaptive exponential integrate-and-fire model," *Biological Cybernetics*, vol. 99, no. 4, pp. 335–347, Nov 2008.

- [49] H. Markram *et al.*, "Interneurons of the neocortical inhibitory system," *Nature Rev. Neurosci.*, vol. 5, no. 10, pp. 793–807, 2004.

- [50] M. Larkum, "A cellular mechanism for cortical associations: an organizing principle for the cerebral cortex," *Trends in neurosciences*, vol. 36, no. 3, pp. 141–151, 2013.

- [51] M. Hock, "Modern semiconductor technologies for neuromorphic hardware," Ph.D. dissertation, Ruprecht-Karls-Universität Heidelberg, 2014.

- [52] P. A. Merolla, J. V. Arthur *et al.*, "A million spiking-neuron integrated circuit with a scalable communication network and interface," *Science*, vol. 345, no. 6197, pp. 668–673, 2014.

- [53] B. V. Benjamin, P. Gao, E. McQuinn et al., "Neurogrid: A mixed-

analog-digital multichip system for large-scale neural simulations," *Proceedings of the IEEE*, vol. 102, no. 5, pp. 699–716, May 2014.

- [54] S. Schmitt, J. Klähn, G. Bellec, A. Grübl, M. Guettler, A. Hartel, S. Hartmann, D. Husmann, K. Husmann, S. Jeltsch *et al.*, "Neuromorphic hardware in the loop: Training a deep spiking network on the brainscales wafer-scale system," in 2017 International Joint Conference on Neural Networks (IJCNN). IEEE, 2017, pp. 2227–2234.

- [55] C. A. Mead, Analog VLSI and Neural Systems. Reading, MA: Addison Wesley, 1989.

- [56] M. Mahowald and R. Douglas, "A silicon neuron," *Nature*, vol. 354, no. 6354, pp. 515–518, Dec 1991. [Online]. Available: http://dx.doi.org/10.1038/354515a0

- [57] B. Linares-Barranco, E. Sánchez-Sinencio, A. Rodríguez-Vázquez, and J. L. Huertas, "A cmos implementation of fitzhugh-nagumo neuron model," *IEEE Journal of Solid-State Circuits*, vol. 26, no. 7, pp. 956– 965, 1991.

- [58] P. Häfliger, M. Mahowald, and L. Watts, "A spike based learning neuron in analog vlsi," in *Advances in Neural Information Processing Systems*, 1997, pp. 692–698.

- [59] C. Rasche and R. J. Douglas, "Forward- and backpropagation in a silicon dendrite," *IEEE Transactions on Neural Networks*, vol. 12, no. 2, pp. 386–393, Mar 2001.

- [60] E. Farquhar and P. Hasler, "A bio-physically inspired silicon neuron," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 52, no. 3, pp. 477–488, 2005.

- [61] P. A. Merolla and K. Boahen, "Dynamic computation in a recurrent network of heterogeneous silicon neurons," in *Proceedings of the 2006 IEEE International Symposium on Circuits and Systems (ISCAS 2006)*, 2006.

- [62] J. Wijekoon and P. Dudek, "Compact silicon neuron circuit with spiking and bursting behaviour," *Neural Networks*, vol. 21, no. 2, pp. 524 – 534, 2008.

- [63] P. Livi and G. Indiveri, "A current-mode conductance-based silicon neuron for address-event neuromorphic systems," in *International Symposium on Circuits and Systems*, May 2009, pp. 2898–2901.

- [64] R. J. Vogelstein, U. Mallik, J. T. Vogelstein, and G. Cauwenberghs, "Dynamically reconfigurable silicon array of spiking neurons with conductance-based synapses," *IEEE transactions on neural networks*, vol. 18, no. 1, pp. 253–265, 2007.

- [65] A. Van Schaik, C. Jin, A. McEwan, and T. J. Hamilton, "A logdomain implementation of the izhikevich neuron model," in *Circuits and Systems (ISCAS), Proceedings of 2010 IEEE International Symposium on.* IEEE, 2010, pp. 4253–4256.

- [66] Y. Wang and S.-C. Liu, "A two-dimensional configurable active silicon dendritic neuron array," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 58, no. 9, pp. 2159–2171, 2011.

- [67] S. Saïghi, Y. Bornat, J. Tomas, G. Le Masson, and S. Renaud, "A library of analog operators based on the hodgkin-huxley formalism for the design of tunable, real-time, silicon neurons," *IEEE transactions on biomedical circuits and systems*, vol. 5, no. 1, pp. 3–19, 2011.

- [68] F. Folowosele, T. J. Hamilton, and R. Etienne-Cummings, "Silicon modeling of the mihalas-niebur neuron," *IEEE Transactions on Neural Networks*, vol. 22, no. 12, pp. 1915–1927, Dec 2011.

- [69] S. Ramakrishnan, R. Wunderlich, J. Hasler, and S. George, "Neuron array with plastic synapses and programmable dendrites," *IEEE transactions on biomedical circuits and systems*, vol. 7, no. 5, pp. 631–642, 2013.

- [70] C. Mayr, J. Partzsch, M. Noack, S. Hnzsche, S. Scholze, S. Hppner, G. Ellguth, and R. Schffny, "A biological-realtime neuromorphic system in 28 nm cmos using low-leakage switched capacitor circuits," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 10, no. 1, pp. 243–254, Feb 2016.

- [71] A. Cassidy and A. G. Andreou, "Dynamical digital silicon neurons," in 2008 IEEE Biomedical Circuits and Systems Conference, Nov 2008, pp. 289–292.

- [72] P. Merolla, J. Arthur, F. Akopyan, N. Imam, R. Manohar, and D. S. Modha, "A digital neurosynaptic core using embedded crossbar memory with 45pj per spike in 45nm," in 2011 IEEE Custom Integrated Circuits Conference (CICC), Sept 2011, pp. 1–4.

- [73] A. S. Cassidy, P. Merolla, J. V. Arthur, S. Esser et al., "Cognitive computing building block: A versatile and efficient digital neuron model for neurosynaptic cores," *International Joint Conference on Neural Networks (IJCNN)*, 2013.

- [74] C. Frenkel, J. D. Legat, and D. Bol, "A compact phenomenological digital neuron implementing the 20 izhikevich behaviors," in 2017 IEEE Biomedical Circuits and Systems Conference (BioCAS), Oct 2017, pp. 1–4.

- [75] M. Davies *et al.*, "Loihi: A neuromorphic manycore processor with on-chip learning," *IEEE Micro*, vol. 38, no. 1, pp. 82–99, 2018.

- [76] S. Hoppner, H. Eisenreich, S. Henker, D. Walter, G. Ellguth, and R. Schuffny, "A compact clock generator for heterogeneous gals mpsocs in 65-nm cmos technology," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 21, no. 3, pp. 566–570, March 2013.

Laura Kriener received the M.Sc. degree in Physics from Heidelberg University, Germany, in 2017. Her Master's thesis in the Electron Vision(s) group at the Kirchhoff Institute for Physics focused on the preproduction characterization of single neuron dynamics on neuromorphic hardware. Her research interests are the development and application of neuromorphic hardware.

Yannik Stradmann received the B.Sc. degree in Physics from Heidelberg University, Germany, in 2016. His research as a Master's student within the Electronic Vision(s) group focuses on the development and verification of mixed-signal VLSI circuits for neuromorphic hardware.

**Syed Ahmed Aamir** (S'11) received the M.Sc. degree from Linköping University, Sweden and Ph.D. degree from Karlsruhe Institute of Technology, Germany, both in electrical engineering in 2010 and 2018 respectively. He has worked as a Research Engineer at Linköping University and currently works as a Postdoctoral Researcher in Electronic Vision(s) group at Kirchhoff Institute for Physics, Heidelberg. His current research interests include low-power analog design, integrated mixed-signal transceivers and biologically-inspired systems.

signal SoCs.

Andreas Grübl received the Dipl. Phys. and Ph.D. degrees from Heidelberg University, Heidelberg, Germany in 2003 and 2007, respectively. Currently, he is a Senior Postdoctoral Researcher in the Electronico Vision(s) group and leader of the Electronics Department of the Kirchhoff Institute for Physics at Heidelberg University. He has eight years of postdoctoral experience in designing and building complex microelectronics systems for brain-inspired information processing. His research focus is on new methods for the implementation of large mixed-

**Paul Müller** received the Dipl. Phys. degree from Heidelberg University, Heidelberg, in 2011. He was working as a research assistant at the Electronic Vision(s) group until 2013, and received his Ph.D. degree in Physics in 2017. His current research interest is the development, operation and application of mixed-signal neuromorphic devices.

Johannes Schemmel (M'08) received the Ph.D. degree in physics from Heidelberg University, Heidelberg, Germany, in 1999. Currently, he is 'Akademischer Oberrat' in the Kirchhoff Institute of Physics, Heidelberg, where he is head of the ASIC laboratory and the Electronic Vision(s) group. His research interests are mixed-mode VLSI systems for information processing, especially the analog implementation of biologically realistic neural network models. He is the architect of the Spikey and BrainScaleS accelerated Neuromorphic hardware systems.

Gerd Kiene received the M.Sc. degree in Physics from Heidelberg University, Germany, in 2017. Currently he is working as a research assistant in the Electronic Vision(s) group at the Kirchhoff Institute for Physics developing analog readout and mixedsignal circuits for neuromorphic systems. His research interests are the development of novel computing systems as well as digital, analog and RF integrated circuits.

Karlheinz Meier (M'17) received the Ph.D. degree in physics from Hamburg University, Hamburg, Germany, in 1984. He is currently a Professor of Physics at Heidelberg University, Heidelberg, Germany, and Co-Founder of the Kirchhoff-Institut and the Heidelberg ASIC Laboratory in Heidelberg. His research interests include the application of microelectronics in particle physics, electronic realizations of brain circuits, and principles of information processing in spiking neural networks.