# Experimental Demonstration of a Josephson Magnetic Memory Cell with a Programmable $\pi$ -Junction

Ian M. Dayton <sup>1</sup>, Tessandra Sage <sup>1</sup>, Eric C. Gingrich <sup>1</sup>, Melissa G. Loving <sup>1</sup>, Thomas F. Ambrose <sup>1</sup>, Nathan P. Siwak <sup>1</sup>, Shawn Keebaugh <sup>1</sup>, Christopher Kirby <sup>1</sup>, Donald L. Miller <sup>1</sup>, Anna Y. Herr <sup>1</sup>, Quentin P. Herr <sup>1</sup>, Ofer Naaman <sup>1</sup>

<sup>1</sup>Northrop Grumman Systems Corp., Baltimore, Maryland 21240, USA

We experimentally demonstrate the operation of a Josephson magnetic random access memory unit cell, built with a  $Ni_{80}Fe_{20}/Cu/Ni$  pseudo spin-valve Josephson junction with Nb electrodes and an integrated readout SQUID in a fully planarized Nb fabrication process. We show that the parallel and anti-parallel memory states of the spin-valve can be mapped onto a junction equilibrium phase of either zero or  $\pi$  by appropriate choice of the ferromagnet thicknesses, and that the magnetic Josephson junction can be written to either a zero-junction or  $\pi$ -junction state by application of write fields of approximately 5 mT. This work represents a first step towards a scalable, dense, and power-efficient cryogenic memory for superconducting high-performance digital computing.

Index Terms—Superconducting spintronics, Josephson junctions, Josephson magnetic random-access memory, cryogenic memory, superconducting quantum interference devices.

#### I. Introduction

Ultra-low power superconducting digital technologies such as Reciprocal Quantum Logic (RQL) [1], offer to address the energy dissipation challenge that is now facing traditional machines based on complementary metal-oxide semiconductor (CMOS). Even after including the energy cost associated with their cryogenic operation, superconducting logic technologies [2], [3] dissipate 10-100 times less 'wall power' than CMOS at comparable clock rates, and are projected to be capable of meeting the U.S. Department of Energy exa-scale power dissipation target for high-performance computing [3]–[5]. While there has been considerable progress in superconductor fabrication technology [6], [7], automated design tools [8], and circuit complexity [9], [10], the lack of a suitable memory solution has, hitherto, remained a major risk to the eventual integration of superconducting logic into highperformance computing systems [3]. Recent efforts to advance the cryogenic memory state-of-the-art beyond superconducting quantum interference device (SQUID)-based memories [11] include hybrid Josephson-CMOS [12] and magnetic [13], [14] memory solutions. Here, we report on an experimental demonstration of a cryogenic magnetic memory unit cell built in a superconducting integrated circuit, paving the way to a memory solution that is dense, fast, robust, energy-efficient, and compatible with superconducting logic fabrication and signal levels.

Our memory architecture, which we call Josephson magnetic random-access memory (JMRAM) [13], is based on a magnetic pseudo spin-valve with superconducting electrodes forming a magnetic Josephson junction. Like conventional field-switched MRAM [15], [16], JMRAM encodes information in the relative orientation of the two magnetic layers of a spin-valve, and is written by applying bit- and word-write magnetic fields to a selected memory address to set

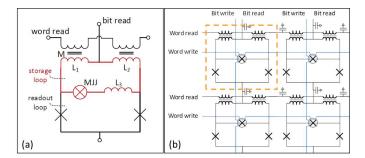

Fig. 1. (a) Schematic of the JMRAM unit cell, including an rf-SQUID storage loop (red) that contains the magnetic Josephson junction and a dc-SQUID readout loop. The word-read current applies flux to a selected memory cell such that the bit-read current exceeds the readout SQUID critical current in one memory state, but not in the other. (b) Unit cells can be tiled to form an x-y addressable memory array, with word- and bit-write lines applying hard- and easy-axis fields. Read lines use the cell inductance to form LC ladder transmission lines for fast signal propagation.

the magnetization of its free layer. Unlike MRAM, readout is not based on sensing the resistance of the bit—rather, JMRAM readout is anchored in the well-established physics of the Josephson effect in magnetic  $\pi$ -junctions [17]–[20]. The magnetic state of a bit is mapped, by appropriate choice of magnetic layer thicknesses, into one of two possible junction ground states differing in their equilibrium superconducting phase. The phase of the magnetic Josephson junction (MJJ), written to zero or  $\pi$  depending on the encoded bit, is then accessible for fast, efficient, and high-fidelity readout by a dc-SQUID. Unlike readout schemes that are based on the magnitude of the bit's resistance or critical current and are inherently analog, the JMRAM readout of a phase that can only be zero or  $\pi$ , is fundamentally digital.

### II. EXPERIMENT

The JMRAM unit cell is shown schematically in Figure 1(a). An rf-SQUID containing the magnetic junction, labeled

as MJJ in the figure, and inductors  $L_1$ ,  $L_2$ , and  $L_3$ , forms a storage loop that encloses a spontaneously generated flux  $\Phi_0/2$  when the MJJ is in a  $\pi$ -junction state and zero flux otherwise. To enable storage, the loop linear inductance must be greater than the Josephson inductance of the MJJ. A portion of the stored flux is coupled into the dc-SQUID readout loop and can be sensed by passing a bit-read current through the device. A word-read current tunes the dc-SQUID flux such that in the memory state associated with an MJJ  $\pi$  phase  $(\Phi_0/2)$  in the storage loop), the bit-read current causes the dc-SQUID to switch to its voltage state. In the other memory state, which is associated with an MJJ zero phase, the dc-SOUID critical current is higher than the bit-read current and the SQUID remains in the zero-voltage state. Figure 1(b) shows how cells can be tiled to form an x-y addressable memory array [13]. Fast transmission of read signals through the array is enabled by harnessing the inductance of the cells to form LC transmission lines. The energy dissipated in a write operation on an N-bit word,  $E_{\rm ww}$  can be estimated as  $E_{\text{ww}} = \eta^{-1} N_b \left( N_w L_b I_b^2 + L_w I_w^2 \right) / 2$  where  $N_{b(w)}$  is the size of the array in the bit (word) dimension,  $L_{b(w)}$  is the bit (word) write line inductance per cell,  $I_{b(w)}$  is a mA-level bit (word) write current, and  $\eta$  is the driver efficiency factor—up to 20% for RQL drivers [21]

Our magnetic spin-valve Josephson junctions are built with  $Ni_{80}Fe_{20}$  (NiFe) as a free layer, Ni as a fixed layer, and a Cu spacer that separates the two layers. Additional Cu layers separate the magnetic stack from the Nb electrodes. This particular choice of material combination follows Refs. [22]–[24], which have shown that similar stacks can have substantial critical current densities. In our cell design, the critical current of the MJJ must be higher than that of the readout SQUID junctions; this requirement, together with the desire to size the junction to contain a single magnetic domain, drive the need for high critical current densities. With higher MJJ critical current, the storage loop inductance can be made smaller, resulting in higher memory density and favorable power budget associated with lower write-line inductance per bit.

The supercurrent  $I_{cM}$  through a junction with ferromagnetic (FM) metal barrier decays exponentially with increasing barrier thickness d on a length scale that is inversely proportional to the exchange energy of the FM [17]. Superimposed on this decay are oscillations in the critical current  $I_{cM}(d)$ . These oscillations reverse the sign of  $I_{cM}$ , and the minimum energy of the junction periodically alternates to favor zero- or  $\pi$ -phase as a function of thickness on a characteristic scale  $\xi_F$ . Mapping of the magnetic parallel (P) or anti-parallel (AP) state of a spinvalve with  $d_{1,2}$  and  $\xi_{F_{1,2}}$  (subscript 1 and 2 refers to first and second magnetic layer) onto a junction phase requires that the sum of the superconducting phases accumulated in the P state  $(d_1/\xi_{F1})+(d_2/\xi_{F2})$ , and their difference  $(d_1/\xi_{F1})-(d_2/\xi_{F2})$ in the AP state, put the junction on opposite-sign lobes of the  $I_{cM}(d)$  curve [25]. Our approach builds on the work of Ref. [23], which clearly demonstrated that a properly tuned Josephson spin-valve functions as a programmable  $\pi$ -junction whose phase is controlled by the P or AP alignment of the FM layers.

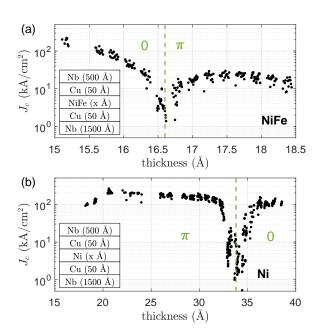

Fig. 2. Critical current density  $J_c$  of (a) Nb/Cu/NiFe/Cu/Nb and (b) Nb/Cu/Ni/Cu/Nb Josephson junctions vs magnetic barrier thickness. All data in each of the panels were measured on a single wafer, and the thickness gradient was produced by depositing the respective ferromagnetic metal at a 30 degree angle to the wafer normal. Regions of equilibrium 0- or  $\pi$ -phase are labeled according to Refs. [26] and [27].

To tune the layer thicknesses in our spin-valves, we first characterize the critical current through each of the FM layers separately as a function of their thickness. We fabricated MJJs containing Cu/NiFe/Cu and Cu/Ni/Cu barriers by depositing the FM layer at a 30 degree angle from the wafer normal, producing a gradient in the FM layer thickness across the wafer. Figure 2 shows the critical current density  $J_c$ , measured at 4.2 K and zero field, of a series of 1  $\mu$ m  $\times$  2  $\mu$ m ellipseshaped MJJs as a function of NiFe [Figure 2(a)] and Ni [Figure 2(b)] thickness across a 150 mm wafer. We see the expected oscillatory decay in the critical current, with Ni having a much longer decay length than NiFe; the range of the data, however, is not sufficient for a meaningful fit to theory. The pronounced dips in  $J_c$ , at 16.6 Å for NiFe and at 34 Å for Ni, dashed lines in Fig. 2, indicate these respective thicknesses as  $0-\pi$ transitions in these layers, in agreement with Refs. [26] and [27]. With this information, we set the Ni layer thickness in our spin-valve to 33 Å, right at its  $0 - \pi$  transition thickness, and that of NiFe at 16 Å —just below the transition. This choice ensures robust mapping between the junction magnetic state and its phase.

Unit cell devices were fabricated at Northrop Grumman on 150 mm wafers in a fully planarized Nb process with four metal layers, 0.26  $\mu m$  minimum linewidth and spacing, featuring both Nb/Al/AlO $_x$ /Nb trilayer Josephson junctions and the magnetic spin-valve Josephson junctions shown in the inset of Figure 3. The spin-valve stack was deposited using conventional DC magnetron sputtering from single targets at ambient temperature and a base pressure  $<3\times10^{-9}$  torr. In all data shown below, the MJJs are  $1~\mu m \times 2~\mu m$

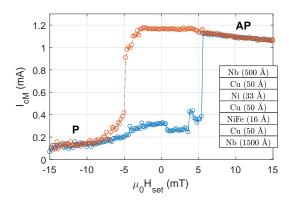

Fig. 3. Critical current of a 1  $\mu$ m $\times$ 2  $\mu$ m elliptical junction containing the layer stack shown in the inset. Measurements were performed at zero-field following the application of a set field shown on the x-axis. Blue (red) data points represent an increasing (decreasing)  $H_{set}$  sweep. The data trace the minor magnetization loop of the junction NiFe free layer.

ellipses, magnetic fields are applied in-plane along the MJJ's easy axis from an off-chip superconducting solenoid, and all measurements were done at 4.2 K.

To probe the critical current of the MJJ, which is not directly accessible in the unit cell, and its dependence on the spinvalve magnetic state, we measure co-fabricated stand-alone MJJ test structures. Representative data are shown in Figure 3. The junction is first initialized to a P state by applying a field of -125 mT, and then we perform a remnant magnetization experiment, in which each of the data points in the figure is acquired at zero field after the application of a set field as shown on the x-axis. This way we can trace the minor magnetization loop of the free layer in our junction. The data clearly shows a switch in the magnetization of the free layer when the set-field is increased to about  $\mu_0 H = 5.5$  mT, associated with a change in the junction critical current from approximately 0.14 mA at -10 mT to 1.1 mA at 10 mT. As the set-field is traced back down through zero, the junction remains in the AP state until  $\mu_0 H = -4.9$  mT, where it switches back to its initial P state. The hysteretic switching and the existence of two stable states at zero field are the hallmarks of a memory element. In all junctions, we observe  $I_{cM,P} < I_{cM,AP}$  because in the P state the net magnetization field of the FM barrier suppresses the zero-field critical current via the Fraunhofer effect [24], while in the AP state the net field through the barrier, along with the Fraunhofer pattern shift, is significantly lower. This effect becomes much less significant in sub-micrometer junctions [24]. We also observe that while the switching of the free layer often progresses through several intermediate states, the application of  $\pm 10$  mT saturates the free layer and reliably selects one of the stable states.

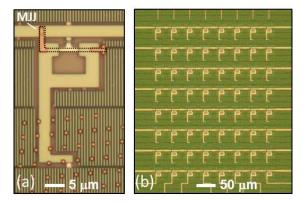

Having characterized the MJJ both electrically and magnetically, we now turn to the measurement of the unit cell device, whose schematic is shown in Figure 1(a). Fig. 4 shows an optical micrograph of a unit cell device (a) similar to the one measured, and an 8x8 memory array (b). The present design shown in the figure makes no attempt to exercise the full process capability, with lines and spaces many times larger

Fig. 4. (a) Optical micrograph of the unit cell and (b) an 8x8 array, prior to deposition of the final metal layer. The position of inductor  $L_3$ , which closes the storage loop in the top layer, is indicated with a dashed line in (a).

than the minimum design rule. In our device, the inductances of the storage loop were designed to be  $L_1=L_2=5.88$  pH, and  $L_3=10.93$  pH, and the total critical current of the readout SQUID is 13  $\mu$ A. The MJJ critical current in either state of the bit, as can be seen from Figure 3, is such that the MJJ Josephson inductance is considerably smaller than the loop linear inductance, making the storage loop multistable as it can store a number of flux quanta. As we describe below, this is a nuisance that is particular to the current measurement and is not a fundamental property of the technology, nor does it affect our ability to distinguish between the memory states.

When a flux  $\Phi_s$  is enclosed in the storage loop, a portion of that flux is mutually induced in the readout loop  $\Phi_r$  by the current flowing through inductor  $L_3$ :  $\Phi_r = \Phi_s \frac{L_3}{L_1 + L_2 + L_3} \sim$  $0.5\Phi_s$ . The ratio  $\Phi_r/\Phi_s$  was measured in a separate experiment by comparing the readout SQUID modulation period in two cells, where in one of the cells the branch containing  $L_3$  and the MJJ was disconnected from the circuit, but were otherwise identical. We observed that severing the MJJ branch reduces the SQUID modulation period by a factor of 2 as expected. Therefore, each  $\Phi_0$  change in the flux state of the storage loop will cause the readout SQUID modulation curve  $I_{c,sq}(\Phi_r)$  to shift by half a period. However, a  $\pi$ -phase shift in the MJJ that is the contrast between memory states will correspond to a change in the stored flux by  $\Phi_0/2$ , and will offset  $I_{c,sq}(\Phi_r)$  by a quarter of a period. Therefore a zero- to  $\pi$ -junction transition can be easily distinguished from  $\Phi_0$  flux jumps in the large-inductance rf-SQUID storage loop.

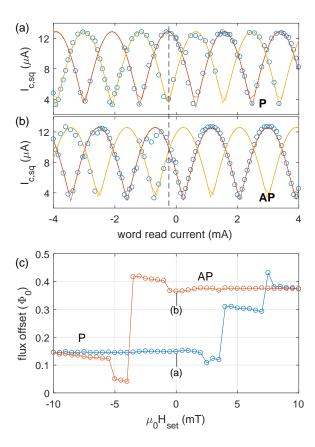

After initializing the cell to a parallel state in a -100 mT field, we apply a set-field pulse  $H_{set}$  and then measure the readout SQUID critical current modulation vs word-read current at zero field. The measurement repeats for varying  $\mu_0 H_{set}$  from -10 mT to 10 mT and back, tracing the free layer minor magnetization loop. Figure 5(a) shows the SQUID critical current  $I_{c,sq}(\Phi_r)$  for  $H_{set}=0$  in the parallel memory state of the bit. Each  $I_{c,sq}$  data point represent the average over 50 switching events from bit-read current ramps [28]. As shown in the figure, the  $I_{c,sq}$  data traces two modulation curves, offset by half a period, that represent states of the storage loop that differ by integer number of flux quanta.

Fig. 5. Measurement of the readout SQUID critical current  $I_{c,sq}$  vs word-read current, for a parallel (a) and anti-parallel (b) alignment of the spin-valve layers. The quarter-period shift between the (a) and (b) data (see dashed line as a guide) is indicative of a  $\pi$  phase change in the MJJ. The  $I_{c,sq}$  data (circles) are fit simultaneously to two SQUID modulation curves offset by half a period (red and yellow solid lines). The overall flux offset is extracted from these fits, and is plotted (modulo  $\Phi_0/2$ ) vs set field  $H_{set}$  in (c), which traces the free layer minor magnetization loop with blue and red data representing increasing and decreasing fields, respectively. The data points in (c) that were extracted from traces (a) and (b) are marked in the figure.

We fit the data simultaneously to the two offset modulation curves (solid lines in the figure), to obtain the overall flux offset of the pattern. Figure 5(b) shows the results of the same experiment but with the bit in the anti-parallel memory state. A comparison of Figures 5(a) and 5(b) clearly shows a quarterperiod shift in the SQUID modulation pattern between the P and AP state, indicating a  $\pi$  phase shift in the MJJ. Stray field from the junction magnetic barrier can offset the SQUID modulation curve, but we have measured that contribution to amount to less than 0.1  $\Phi_0$ , and the observed shifts cannot be explained by that mechanism alone. Note that the experiment is only sensitive to changes in the MJJ phase, and cannot determine whether the  $\pi$  (0) phase occurs in the parallel (anti-parallel) state or vice versa.

An important observation from the data of Figures 5(a) and 5(b) is that the magnitude of the MJJ critical current, which changes significantly between the P and AP states (Figure 3), has little to no effect on the readout characteristics. This is a desirable design feature of the JMRAM unit cell because the MJJ critical current depends exponentially on the thickness

of a deposited barrier, which is difficult to control to subangstrom accuracy across the wafer. The cell's insensitivity to that parameter means that this architecture can be scaled without loss of operating margins due to uncertainties in the barrier thickness.

Figure 5(c) shows the readout SQUID modulation curve flux offset, modulo  $\Phi_0/2$ , extracted from measurements like those in panels (a) and (b), as a function of  $H_{set}$ . The blue and red data points represent, respectively, increasing and decreasing  $H_{set}$  sweeps. The data shows that as  $H_{set}$ increases, the measured flux offset switches by  $\Phi_0/4$  at around 5 mT, corresponding to a switch in the magnetic state of the bit from P to AP alignment. When  $H_{set}$  is decreased from 10 mT, the flux offset persists in its AP value past zero field, until the the bit switches back to a parallel state at around -4 mT. In both cases, the switching progresses through a couple of intermediate states that change the flux offset by up to 0.1  $\Phi_0$ , consistent with changes in the stray fields picked up by the readout loop. To test the robustness of the saturated P and AP memory state, we performed 300 write/read cycles in which we alternated  $\mu_0 H_{set}$  between  $\pm 10$ mT and read the correct phase state with zero errors. Figure 5 is the main result of this Letter, and represents an unambiguous demonstration of a programmable Josephson zero-junction to  $\pi$ -junction transition, written by an applied magnetic field, and read-out by an integrated SQUID.

#### III. CONCLUSION

We have demonstrated experimentally the operation of a JMRAM memory unit cell, embedding a NiFe/Cu/Ni pseudo spin-valve Josephson junction, and built in a superconducting integrated circuit. We have shown that the magnetization state of the spin-valve, which stores the bit's information, can be mapped onto the junctions's superconducting phase enabling high-fidelity readout by an integrated dc-SQUID. While improvements to the magnetic performance of both free and fixed layers are still required before large memory arrays can be implemented, our experiment lays the basis for this technology, and makes a first step towards a scalable cryogenic memory solution to support power-efficient post-CMOS computing.

## ACKNOWLEDGEMENT

We thank N.O. Birge, N.D. Rizzo, and N. Newman for technical assistance and discussions, R. Pownall, J. Robinson, K. Holman, K. Dinh, and A. Sidorov for measurements support, and S. Van Campen, S. Weiss, and J. Stanbro for program support. We thank W.H. Rippard, M.L. Schneider, and P. Hopkins for independent verification of our experimental results. This work was supported by a Northrop Grumman IRAD program and by the Office of the Director of National Intelligence (ODNI), Intelligence Advanced Research Projects Activity (IARPA), via U.S. Army Research Office contract W911NF-14-C-0115. The views and conclusions contained herein are those of the authors and should not be interpreted as necessarily representing the official policies or endorsements, either expressed or implied, of the ODNI, IARPA, or the U.S. Government.

#### REFERENCES

- Q. P. Herr, A. Y. Herr, O. T. Oberg, and A. G. Ioannidis, "Ultralow-power superconductor logic," *Journal of Applied Physics*, vol. 109, no. 10, p. 103903, 2011.

- [2] O. A. Mukhanov, "Energy-efficient single flux quantum technology," IEEE Transactions on Applied Superconductivity, vol. 21, no. 3, pp. 760–769, June 2011.

- [3] D. S. Holmes, A. L. Ripple, and M. A. Manheimer, "Energy-efficient superconducting computingpower budgets and requirements," *IEEE Transactions on Applied Superconductivity*, vol. 23, no. 3, pp. 1701610– 1701610, 2013.

- [4] M. A. Manheimer, "Cryogenic computing complexity program: Phase 1 introduction," *IEEE Transactions on Applied Superconductivity*, vol. 25, no. 3, pp. 1–4, 2015.

- [5] D. S. Holmes, A. M. Kadin, and M. W. Johnson, "Superconducting computing in large-scale hybrid systems," *Computer*, vol. 48, no. 12, pp. 34–42, Dec 2015.

- [6] S. K. Tolpygo, V. Bolkhovsky, T. Weir, A. Wynn, D. Oates, L. Johnson, and M. Gouker, "Advanced fabrication processes for superconducting very large-scale integrated circuits," *IEEE Transactions on Applied Superconductivity*, vol. 26, no. 3, pp. 1–10, 2016.

- [7] M. W. Johnson, P. Bunyk, F. Maibaum, E. Tolkacheva, A. J. Berkley, E. M. Chapple, R. Harris, J. Johansson, T. Lanting, I. Perminov, E. Ladizinsky, T. Oh, and G. Rose, "A scalable control system for a superconducting adiabatic quantum optimization processor," *Superconductor Science and Technology*, vol. 23, no. 6, p. 065004, 2010. [Online]. Available: http://stacks.iop.org/0953-2048/23/i=6/a=065004

- [8] Q. Xu, C. L. Ayala, N. Takeuchi, Y. Murai, Y. Yamanashi, and N. Yoshikawa, "Synthesis flow for cell-based adiabatic quantum-fluxparametron structural circuit generation with HDL back-end verification," *IEEE Transactions on Applied Superconductivity*, vol. 27, no. 4, pp. 1–5, June 2017.

- [9] A. Y. Herr, Q. P. Herr, O. T. Oberg, O. Naaman, J. X. Przybysz, P. Borodulin, and S. B. Shauck, "An 8-bit carry look-ahead adder with 150 ps latency and sub-microwatt power dissipation at 10 GHz," *Journal of Applied Physics*, vol. 113, no. 3, p. 033911, 2013.

- [10] Q. P. Herr, J. Osborne, M. J. A. Stoutimore, H. Hearne, R. Selig, J. Vogel, E. Min, V. V. Talanov, and A. Y. Herr, "Reproducible operating margins on a 72,800-device digital superconducting chip," *Superconductor Science and Technology*, vol. 28, no. 12, p. 124003, 2015. [Online]. Available: http://stacks.iop.org/0953-2048/28/i=12/a=124003

- [11] S. Tahara, I. Ishida, S. Nagasawa, M. Hidaka, H. Tsuge, and Y. Wada, "A 4-kbit Josephson nondestructive read-out RAM operated at 580 psec and 6.7 mW," *IEEE Transactions on Magnetics*, vol. 27, no. 2, pp. 2626– 2633, 1991.

- [12] T. Van Duzer, L. Zheng, S. R. Whiteley, H. Kim, J. Kim, X. Meng, and T. Ortlepp, "64-kb hybrid Josephson-CMOS 4 Kelvin RAM with 400 ps access time and 12 mW read power," *IEEE Transactions on Applied Superconductivity*, vol. 23, no. 3, pp. 1700504–1700504, 2013.

- [13] A. Herr and Q. Herr, "Josephson magnetic random access memory system and method," Sep. 18 2012, US Patent 8,270,209. [Online]. Available: http://www.google.com/patents/US8270209

- [14] T. Ohki, O. Mukhanov, and A. Kirichenko, "Magnetic RAM array architecture," Jan. 24 2017, US Patent 9,552,862.

- [15] J. Slaughter, "Materials for magnetoresistive random access memory," Annual Review of Materials Research, vol. 39, pp. 277–296, 2009.

- [16] B. N. Engel, J. Akerman, B. Butcher, R. W. Dave, M. DeHerrera, M. Durlam, G. Grynkewich, J. Janesky, S. V. Pietambaram, N. D. Rizzo, J. M. Slaughter, K. Smith, J. J. Sun, and S. Tehrani, "A 4-Mb toggle MRAM based on a novel bit and switching method," *IEEE Transactions on Magnetics*, vol. 41, no. 1, pp. 132–136, Jan 2005.

- [17] A. I. Buzdin, "Proximity effects in superconductor-ferromagnet heterostructures," *Rev. Mod. Phys.*, vol. 77, pp. 935–976, Sep 2005. [Online]. Available: https://link.aps.org/doi/10.1103/RevModPhys.77.935

- [18] M. Eschrig, "Spin-polarized supercurrents for spintronics," *Phys. Today*, vol. 64, no. 1, p. 43, 2011.

- [19] M. Eschrig, "Spin-polarized supercurrents for spintronics: a review of current progress," *Reports on Progress in Physics*, vol. 78, no. 10, p. 104501, 2015.

- [20] A. Feofanov, V. Oboznov, V. Bol'Ginov, J. Lisenfeld, S. Poletto, V. Ryazanov, A. Rossolenko, M. Khabipov, D. Balashov, A. Zorin et al., "Implementation of superconductor/ferromagnet/superconductor pi-shifters in superconducting digital and quantum circuits," *Nature Physics*, vol. 6, pp. 593–597, 2010.

- [21] Q. Herr and A. Herr, "Josephson ac/dc converter systems and method," Nov. 3 2015, US Patent 9,174,840. [Online]. Available: https://www.google.com/patents/US9174840

- [22] B. Baek, W. Rippard, S. Benz, S. Russek, and P. Dresselhaus, "Hybrid superconducting-magnetic memory device using competing order parameters." *Nature communications*, vol. 5, p. 3888, 2014.

- [23] E. Gingrich, B. M. Niedzielski, J. A. Glick, Y. Wang, D. Miller, R. Loloee, W. Pratt Jr, and N. O. Birge, "Controllable 0–π Josephson junctions containing a ferromagnetic spin valve," *Nature Physics*, vol. 12, no. 6, 2016.

- [24] B. M. Niedzielski, T. Bertus, J. A. Glick, R. Loloee, W. Pratt Jr, and N. O. Birge, "Spin-valve Josephson junctions for cryogenic memory," arXiv preprint arXiv:1709.04815, 2017.

- [25] B. Crouzy, S. Tollis, and D. A. Ivanov, "Josephson current in a superconductor-ferromagnet junction with two noncollinear magnetic domains," *Phys. Rev. B*, vol. 75, p. 054503, Feb 2007. [Online]. Available: https://link.aps.org/doi/10.1103/PhysRevB.75.054503

- [26] J. A. Glick, M. A. Khasawneh, B. M. Niedzielski, R. Loloee, W. P. PrattJr., N. O. Birge, E. C. Gingrich, P. G. Kotula, and N. Missert, "Critical current oscillations of elliptical Josephson junctions with single-domain ferromagnetic layers," *Journal of Applied Physics*, vol. 122, no. 13, p. 133906, 2017.

- [27] B. Baek, M. L. Schneider, M. R. Pufall, and W. H. Rippard, "Phase offsets in the critical-current oscillations of Josephson junctions based on Ni and Ni-(Ni<sub>81</sub>Fe<sub>19</sub>)<sub>x</sub>Nb<sub>y</sub> barriers," *Phys. Rev. Applied*, vol. 7, p. 064013, Jun 2017. [Online]. Available: https://link.aps.org/doi/10.1103/PhysRevApplied.7.064013

- [28] T. A. Fulton and L. N. Dunkleberger, "Lifetime of the zero-voltage state in Josephson tunnel junctions," *Phys. Rev.* B, vol. 9, pp. 4760–4768, Jun 1974. [Online]. Available: https://link.aps.org/doi/10.1103/PhysRevB.9.4760