## Fabrication of Graphene *p-n-p* Junctions with Contactless Top Gates

Gang Liu, Jairo Velasco Jr., Wenzhong Bao and Chun Ning Lau\* Department of Physics & Astronomy, University of California, Riverside, CA 92521

We developed a multi-level lithography process to fabricate graphene *p-n-p* junctions with the novel geometry of contactless, suspended top gates. This fabrication procedure minimizes damage or doping to the single atomic layer, which is only exposed to conventional resists and developers. The process does not require special equipment for depositing gate dielectrics or releasing sacrificial layers, and is compatible with annealing procedures that improve device mobility. Using this technique, we fabricate graphene devices with suspended local top gates, where the creation of high quality graphene *p-n-p* junctions is confirmed by transport data at zero and high magnetic fields.

-

<sup>\*</sup> To whom correspondence should be addressed. E-mail address: <u>lau@physics.ucr.edu</u>.

Graphene, a single-layer honeycomb lattice of carbon atoms, has recently emerged as a fascinating system for fundamental studies in condensed-matter physics<sup>1-4</sup>. Because of its unusual band structure, single-layer graphene is a zero-gap semiconductor with a linear energy dispersion relation, where charges behave as massless Dirac fermions. Charge transport in graphene exhibit a number of novel phenomena, such as the half-integer quantum Hall effect<sup>1,3</sup> and bipolar supercurrent transistors. Technologically, as a two-dimensional (2D) relative of carbon nanotubes, graphene has exceptional mobility, current-carrying capacity, and thermal conductivity, attracting significant attention as a promising post-silicon electronic material<sup>5-12</sup>.

A remarkable electronic property of graphene as a 2D system is that both carrier *type* and density can be controlled by the electric field effect, such as that induced by a global back gate. Via the employment of a local gate, this feature also enables *in situ* creation and control of *p-n* or *n-p-n* junctions in graphene<sup>13,14</sup>, which have been demonstrated to induce band gaps in bi-layer garphene<sup>15</sup>, quantum Hall plateaus with fractional values due to mode mixing of edge states<sup>16-18</sup>, and have been predicted to give rise to Vaselago lensing<sup>19,20</sup> and Klein tunneling<sup>21</sup>. In most of the experiments to date, either an organic or a metal oxide layer has been used as the dielectric between graphene and the local top gate. Nevertheless, deposition of a top gate dieletrics on a single atomic layer remains a delicate process which may lead to additional dopants and/or scattering sites. Moreover, dramatically enhanced mobility has been recently observed in suspended graphene devices<sup>22,23</sup>, but fabrication of suspended graphene *p-n* junctions using conventional techniques could prove difficult, since direct deposition of local gate dielectrics may considerably stress or even collapse the atomic layer.

Here we report a novel multi-level lithography technique to fabricate contactless top gates that are suspended ~100 nm above the graphene layers. Deposition of the suspended "air bridge"-styled top gate and its electrical leads is finished in one vacuum cycle, while graphene is only exposed to conventional electron-beam resists and developers, thus minimizing the damage to the atomic layer. The vacuum insulated gap between the bridge and device is not susceptible to pinholes, dielectric breakdown and leakage current. Using this technique, we demonstrated the fabrication of a graphene p-n-p junction, and its quality is established by the presence of the  $2e^2/h$  conductance plateau at high magnetic fields. In the long term, combination of this technique with suspended graphene may enable experimental realization of novel phenomena such as the Veselago lensing effect.

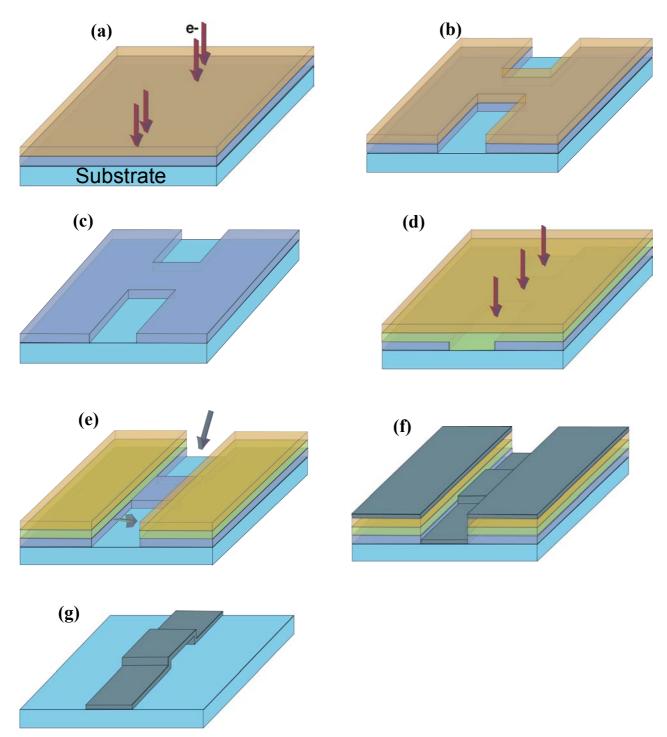

Fig. 1 illustrates the fabrication process, which consists of two lithography steps and a single metal deposition step. The goal of the first lithography step is two-fold: (1) to deposit a resist layer that will act as an initial mechanical support for the suspended portion of the air bridge, and will be removed at the end of the fabrication; and (2) to create windows for the electrical leads or "handles" that contact the suspended structure. To achieve these goals, LOR/PMMA bilayer resists are spun and baked on degenerately doped Si/SiO<sub>2</sub> substrates (Fig. 1a). We then use electron beam to expose the patterns for the electrical leads. The chips are developed twice – first in MIBK/IPA to dissolves the exposed PMMA, then in MF319 to dissolve portions of LOR that are exposed via the PMMA windows (Fig. 1b). Subsequently, acetone is used to lift off the top PMMA layer while leaving LOR intact (Fig. 1c). The final outcome of the first lithography step is an LOR layer with windows for electrical contacts for

the air bridge.

During the second lithography step, MMA/PMMA bilayer resists are spun and baked on top of the LOR layer, followed by electron beam exposure of patterns for both the air bridge and the electrical leads (Fig. 1d). The chips are developed in MIBK that removes exposed MMA and PMMA, leaving windows in MMA/PMMA bilayer for the air bridge, and windows in all three resist layers for the leads (Fig. 1e). The MMA layer is used for creating slight undercuts so as to facilitate the final lift-off.

Lastly, the device is completed by metal deposition. To ensure contact between the suspended structure and the electrical leads, we perform two separate evaporation at 45° and -45°, so as to deposit metals onto the side-walls of the windows (Fig. 1f). For the final lift-off process, the chip is left in PG remover, which is known to be an efficient and clean stripper for LOR, MMA and PMMA (Fig. 1g). After the resists are removed, the chips are rinsed in isopropyl alcohol and dried in nitrogen gas.

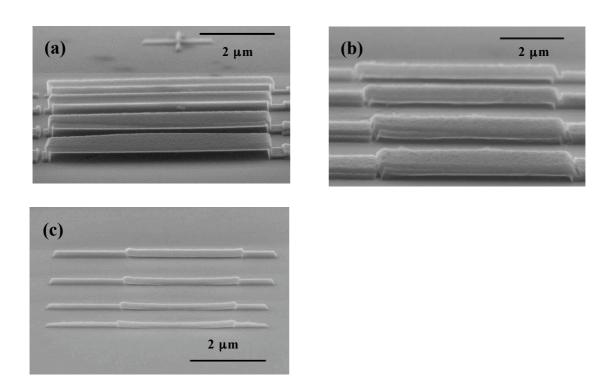

Examples of completed suspended structures are shown in Fig. 2. The fabrication procedure is quite robust; by controlling the lithography conditions, we are able to fabricate suspended air bridges with considerable ranges in dimensions, including span (l), width (w) and height above the substrate (h). For our purpose of using a suspended bridge as a local top gate, the important parameters are l and h: the former directly limits the width of the graphene strip that can be used, the latter determines the gate efficiency. The height of the bridge is determined by the thickness of the LOR resist layer, which may range from 50 nm to 3  $\mu$ m. Fig. 2a and 2b display two bridges that are suspended 300 nm and 100 nm above the substrates, respectively. On the other hand, we find that l increases with w and the material's strength. A few bridges with different w are shown in Fig. 2c: from top to bottom, the bridges are 250, 200, 150 and 100 nm wide, respectively. We can clearly see that the 100 nm-wide bridge sags in the center, while the 250 nm-wide bridge remains straight. The sagging and collapse of the bridges are due to the surface tension of the evaporating liquid when the chips are dried. Without the use of special procedures such as a critical point drying or atomic layer deposition, we are able to create titanium air bridges  $\sim 7 \mu$ m long.

This fabrication process of suspended structures takes advantage of the different exposure, developing and lift-off properties of different resists. Since the metal deposition is the last step of the fabrication (other than the final liftoff), this eliminates complications arising from multiple metal deposition between lithography steps, such as oxidation/etching of the metallic gate, or formation of resist residues that prevents good electrical contacts between the top gate and the leads. Furthermore, since only conventional resists and developers are involved, the fabrication process is much gentler than, *e.g.*, acid etching of SiO<sub>2</sub> sacrificial layers. Structural damage to the graphene layer is minimal. Unlike the standard graphene *p-n* junctions, devices fabricated using this technique are still amiable to annealing techniques that have been shown to be effective in improving device mobility and contact resistance<sup>22,24</sup>.

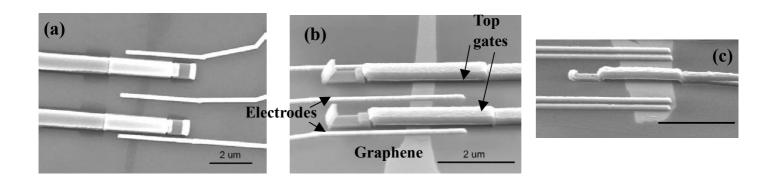

To demonstrate an application of this technique, we fabricate graphene junctions with local top gates (Fig. 3). Single layer graphene device with source-drain electrodes are fabricated using standard procedures<sup>2,4</sup>. We then proceed to fabricate air bridges, which partially cover the graphene sheet and are suspended  $\sim$ 100nm above the substrate. A completed *p-n-p* device, similar to that shown in Fig. 3c, is measured at 260mK in a <sup>3</sup>He

refrigerator using standard lock-in techniques. The device's source-drain separation is 3.5  $\mu$ m, with the top gate covering a  $\sim$ 0.5  $\mu$ m-long segment in the center.

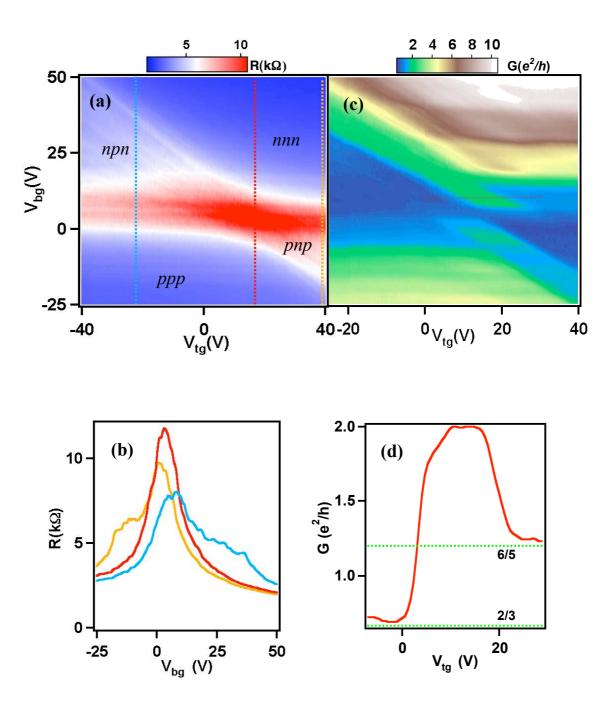

The device's differential resistance R is plotted in Fig. 4a as functions of the back gate voltage  $V_{bg}$  (vertical axis) and top gate voltage  $V_{tg}$  (horizontal axis). The most visible feature is the red horizontal band at  $V_{bg} \sim 14 \text{V}$ , corresponding to the Dirac point of the entire graphene sheet between the source and drain electrodes. Another notable feature is the diagonal white band, indicating the Dirac point for the "covered region", i.e. the portion of the graphene under the top gate. The presence of two Dirac points is more easily seen in Fig. 4b, which plots R vs  $V_{bg}$  at three fixed top gate voltages, corresponding to cuts along the dotted lines in Fig. 4a. Apart from the prominent center peak, the orange curve has an additional shoulder at  $V_{bg}$ ~14V, and the blue curve at  $V_{bg}$ ~28V. These side shoulders correspond to the Dirac point of the covered portion. We note that shoulders, rather than full-blown side peaks, are observed at the second Dirac point; this is indeed reasonable, since the top gate controls less than 15% of the entire device's area. Our results clearly demonstrate individual control of separate regions in the graphene device, and the formation of a graphene p-n-p or n-p-n junction.

The slope of the white line in Fig. 4a yields the ratio of the coupling efficiencies  $\eta$  of the

two gates to graphene, and is determined to be

$$\frac{\eta_{bg}}{\eta_{tg}} = \frac{\Delta V_{tg}}{\Delta V_{bg}} \sim 1.27$$

. From simple geometry

consideration, the coupling is given by the gate-device capacitance,  $C = \varepsilon \varepsilon_0 A/d$ , where  $\varepsilon$  is the dielectric constant of the gate dielectric (3.9 for SiO<sub>2</sub>),  $\varepsilon_0$  is the permittivity of free space, A is the area of the device, and d is the separation between the device and the gate. Hence, the

coupling ratio is given by

$$\frac{C_{bg}}{C_{tg}} = \frac{\varepsilon_{bg}}{\varepsilon_{tg}} \frac{d_{tg}}{d_{bg}} \approx (3.9)(100/300) \approx 1.3$$

, in excellent agreement with the

data. We note that the coupling efficiency of the top gate can be readily improved by using thinner LOR resists during the first lithography step.

Further evidence for the formation of graphene p-n-p junctions is provided by transport data at magnetic field of 8T. For a graphene device with uniform carrier density in high magnetic fields, the formation of quantum Hall edge states leads to a series of conductance plateaus at half integer values of  $4e^2/h$  (the factor of 4 originates from the spin and valley degeneracy). This so-called "half-integer quantum hall effect" arises from the linear dispersion relation of single-layer graphene, and can be attributed to the presence of a Landau level at zero energy, shared by both electrons and holes. In graphene p-n-p junctions, we observe additional conductance plateaus at fractional values (such as 6/5 and 2/3) of  $e^2/h$  (Fig. 4c), which arise from the partial and full equilibration of the edge states at the p-n interfaces. Our results are very similar to those reported by Ozyilmaz  $et\ al.^{18}$ , confirming the presence of two p-n interfaces. There is, however, one notable difference: the conductance plateau with the full value of  $2e^2/h$  are not observed in ref. 18, due to the strong effect of backscattering on states with |v| = |v'|, where v and v' are the filling factors in the "covered" and "bare" regions, respectively. In contrast, we observed a clear plateau at  $2e^2/h$  (Fig. 4d), establishing that transport in our p-n-p junctions experiences relatively weak backscattering.

In conclusion, we have developed a multi-level lithography process to fabricate

suspended top gates ranging from sub-100nm to a few  $\mu$ m in size. The suspended gates have been successfully applied to fabricate a graphene p-n-p junction. Electrical transport data confirm the local control of doping density and type by the top gate, and observation of the previously unreported  $2e^2/h$  quantum Hall plateau in similar p-n-p junctions suggests that our procedure successfully produces clean junctions. In the long term, this versatile technique can also be significantly improved, and extended to fabricate other types of suspended structures such as moving parts in micro-electro-mechanical devices.

We thank Marc Bockrath for helpful discussions, and Peng Wei for assistance with data acquisition software. The research was supported in part by NSF CAREER grant no. DMR/0748910 and ONR/DMEA Award H94003-07-2-0703.

## References

- Y. B. Zhang, Y. W. Tan, H. L. Stormer, and P. Kim, Nature **438**, 201 (2005).

- K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, M. I. Katsnelson, I. V. Grigorieva, S. V. Dubonos, and A. A. Firsov, Nature **438**, 197 (2005).

- <sup>3</sup> K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang, S. V. Dubonos, I. V. Grigorieva, and A. A. Firsov, Science **306**, 666 (2004).

- <sup>4</sup> F. Miao, S. Wijeratne, Y. Zhang, U. Coskun, W. Bao, and C. N. Lau, Science **317**, 1530 (2007).

- <sup>5</sup> Y. W. Son, M. L. Cohen, and S. G. Louie, Phys. Rev. Lett. **97** 216803 (2006).

- <sup>6</sup> D.S. Novikov, Phys. Rev. Lett. **99**, 056802 (2007).

- M. Y. Han, B. Ozyilmaz, Y. B. Zhang, and P. Kim, Phys. Rev. Lett. 98, 206805 (2007).

- <sup>8</sup> Z. H. Chen, Y. M. Lin, M. J. Rooks, and P. Avouris, Physica E **40**, 228 (2007).

- Cho Sungjae, Chen Yung-Fu, and S. Fuhrer Michael, Appl. Phys. Lett. **91**, 123105 (2007).

- C. Berger, Z. M. Song, X. B. Li, X. S. Wu, N. Brown, C. Naud, D. Mayo, T. B. Li, J. Hass, A. N. Marchenkov, E. H. Conrad, P. N. First, and W. A. de Heer, Science 312, 1191 (2006).

- C. Berger, Z. M. Song, T. B. Li, X. B. Li, A. Y. Ogbazghi, R. Feng, Z. T. Dai, A. N. Marchenkov, E. H. Conrad, P. N. First, and W. A. de Heer, J. Phys. Chem. B **108**, 19912 (2004).

- Tombros Nikolaos, Jozsa Csaba, Popinciuc Mihaita, T. Jonkman Harry, and J. van Wees Bart, Nature **448**, 571 (2007).

- B. Huard, J. A. Sulpizio, N. Stander, K. Todd, B. Yang, and D. Goldhaber-Gordon, Phys. Rev. Lett. **98**, 236803 (2007).

- M. M. Fogler, L. I. Glazman, D. S. Novikov, and B.I Shklovskii, Phys. Rev. B 77, 075420 (2008).

- J.B. Oostinga, H.B. Heersche, X. Liu, A.F. Morpurgo, and L.M.K. Vandersypen, Nature Mater., to appear (2007).

- D. A. Abanin and L. S. Levitov, Science **317**, 641(2007).

- <sup>17</sup> J. R. Williams, L. DiCarlo, and C. M. Marcus, Science **317**, 638(2007).

- B. Ozyilmaz, P. Jarillo-Herrero, D. Efetov, D. A. Abanin, L. S. Levitov, and P. Kim, Phys. Rev. Lett. **99**, 166804 (2007).

- <sup>19</sup> V. V. Cheianov, V. Fal'ko, and B. L. Altshuler, Science **315**, 1252 (2007).

- J. Cserti, A. Palyi, and C. Peterfalvi, Phys. Rev. Lett. **99**, 246801 (2007).

- M. I. Katsnelson, K. S. Novoselov, and A. K. Geim, Nature Phys. 2, 620 (2006).

- <sup>22</sup> K.I. Bolotin, K.J. Sikes, Z. Jiang, G. Fudenberg, J. Hone, P. Kim, and H. L. Stormer, arXiv:0802.2389v1 (2008).

- Xu Du, Ivan Skachko, Antony Baker, and Eva Andrei, arXiv:0802.2933 (2008).

- <sup>24</sup> J. Moser, A. Barreiro, and A. Bachtold, Appl. Phys. Lett. **91**, 163513 (2007).

## **Figures and Captions**

**Figure 1.** Schematics of fabrication process. (a). LOR(blue) and PMMA(brown) are deposited onto the substrate, and exposed to electron beams (arrows). (b) Developing in MIBK and MIF solutions opens windows for the electrodes. (c). Liftoff in acetone removes PMMA but leaves LOR layer intact. (d). MMA(green) and PMMA(brown) are deposited, and exposed to e-beam (arrows). (e). Developing in MIBK opens windows for the electrodes and the suspended structure. (f). Metals are evaporated at 45° and -45° (in directions indicated by arrows in e). (g). Resists are lifted off in PG remover, leaving an air bridge contacted to electrodes.

Figure. 2. SEM images of suspended air bridges with different span, width and height.

**Figure 3.** SEM images of two graphene devices with suspended air bridges that act as local top gates. (a) (b) top and angled view (60°) of a device. (c) angled view of another device. Scale bars: 2μm.

**Figure 4.** (a) Differential resistance of a graphene device with a center top gate cover  $\sim 15\%$  of the device, as function of  $V_{bg}$  and  $Vt_g$ . The dotted lines correspond to the line traces in (b). Doping combinations for different regions are labeled. (b) Differential resistance as a function of  $V_{bg}$  at different  $V_{tg}$ . (c). Conductance of the device at 8T magnetic field, as functions of  $V_{bg}$  and  $Vt_g$ . (d). Line trace along the dotted line in (c).