## Noise reduction by bias cooling in gated Si/Si<sub>x</sub>Ge<sub>1-x</sub> quantum dots

Julian Ferrero,<sup>1</sup> Thomas Koch,<sup>1</sup> Sonja Vogel,<sup>1</sup> Daniel Schroller,<sup>1</sup> Viktor Adam,<sup>1,2</sup> Ran Xue,<sup>3</sup> Inga Seidler,<sup>3</sup> Lars R. Schreiber,<sup>3</sup> Hendrik Bluhm,<sup>3</sup> and Wolfgang Wernsdorfer<sup>1,2</sup>

1) Physikalisches Institut, Karlsruhe Institute of Technology, Karlsruhe, Germany

<sup>2)</sup>Institute for Quantum Materials and Technologies, Karlsruhe Institute of Technology, Karlsruhe, Germany

<sup>3)</sup> JARA-FIT Institute for Quantum Information, Forschungszentrum Jülich GmbH and RWTH Aachen University, Aachen, Germany

(\*Electronic mail: wolfgang.wernsdorfer@kit.edu)

(Dated: 10 May 2024)

Silicon-Germanium heterostructures are a promising quantum circuit platform, but crucial aspects as the long-term charge dynamics and cooldown-to-cooldown variations are still widely unexplored quantitatively. In this letter we present the results of an extensive bias cooling study performed on gated silicon-germanium quantum dots with an  $Al_2O_3$ -dielectric. Over 80 cooldowns were performed in the course of our investigations. The performance of the devices is assessed by low-frequency charge noise measurements in the band of  $200\,\mu\text{Hz}$  to  $10\,\text{mHz}$ . We measure the total noise power as a function of the applied voltage during cooldown in four different devices and find a minimum in noise at  $0.7\,\text{V}$  bias cooling voltage for all observed samples. We manage to decrease the total noise power median by a factor of 6 and compute a reduced tunneling current density using Schrödinger-Poisson simulations. Furthermore, we show the variation in noise from the same device in the course of eleven different cooldowns performed under the nominally same conditions.

Electron spins in silicon-germanium represent a promising implementation of the solid state quantum computer. Single and two-qubit gates have been reported to reach gate fidelities above the error correction threshold<sup>1-3</sup>. Recently, quantum error correction was performed on a three qubit device<sup>4</sup> and intermediate range coupling opened new prospects regarding a scaled up quantum processor<sup>3,5–7</sup>. Since quantum-dot based qubits need to be tuned and re-tuned, the long term stability of the qubit working point has gained research interest<sup>8–10</sup>. Furthermore it has been shown that the charge noise level in SiGe devices is strongly dependent on the applied global field<sup>11</sup>. Bias cooling is a readily accessible method which only relies on equipment already present in the typical semiconductor quantum dot setup. To perform bias cooling, the same bias-cooling-voltage V<sub>BC</sub> is applied to all gates of the sample during cooldown from room-temperature to mK temperatures. This causes charges to be trapped in localized defects which interact with the global electric field, thereby changing the stability of gate defined quantum dots. In gallium arsenide, bias cooling has been proven to reduce switching noise and therefore improving the sample stability<sup>12</sup>, by filling DX centers in the dopant layer and therefore reducing the effective leakage rate of electrons from the gate layers into the twodimensional-electron-gas (2DEG). In silicon-germanium, no such centers are present and bias cooling has not been quantitatively investigated yet.

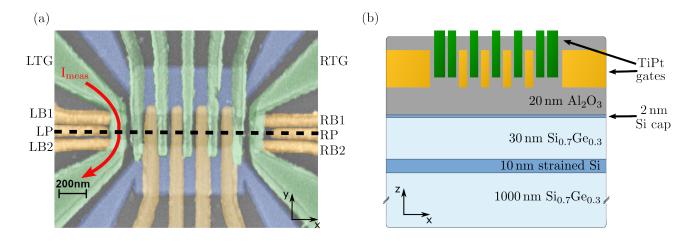

We present the results of a systematic bias-cooling study, quantitatively investigating the noise power in the voltage range in between  $-1\,V$  and  $1\,V$  for  $V_{BC}$ . More then 80 cooldowns were performed, on four different samples. Depending on the applied gate voltage during cooldown, we reduce the total noise power in the frequency band of 200  $\mu Hz$  to  $10\,mHz$  by a factor of 6, in comparison to the zero volt case. We use four gated Si/SiGe devices nominally equal to the device used in  $^{5,13}$  (see Fig. 1 (a)). It contains two single-electron

transistors (SETs) operating as proximal charge detectors and nine central finger gates as well as two confinement gates.

The gatestack is fabricated upon a Si/SiGe heterostructure, which consists of a 1000 nm  $\rm Si_{0.7} \rm Ge_{0.3}$  graded buffer layer on a Si substrate, a 10 nm Si channel, followed by a 30 nm  $\rm Si_{0.7} \rm Ge_{0.3}$  spacer layer and capped by 2 nm naturally oxidized Si (see Fig.1 (b)). The heterostructure confines electrons in the growth direction, effectively forming a 2DEG in the silicon channel, when accumulated. Ohmic contacts to the quantum well layer are realized by implantation of phosphorus and activated by rapid thermal processing at 700 °C for 15 s. The gate stack is an overlay of three metal layers consisting of 15 nm, 22 nm and 29 nm Pt on top of a 5 nm Ti adhesion layer. The metal layers are electrically insulated from the substrate and from each other by 10 nm atomic layer deposited  $\rm Al_2O_3$ .

To characterize the performance under different bias cooling conditions, an efficient thermal cycling mechanism is needed. A heater consisting of constantan wire was installed on the mixing chamber of the used dilution refrigerator. The sample is heated locally to 300 K, while the 4 K stage of the fridge is kept below 10 K. This is achieved by thermally insulating the mixing chamber plate by stopping the circulation of the mixture while a high flow of liquid helium is supplied to the 4K stage. An automated thermal cycle from 30 mK to 300 K and back to 30 mK takes 3.5 h.

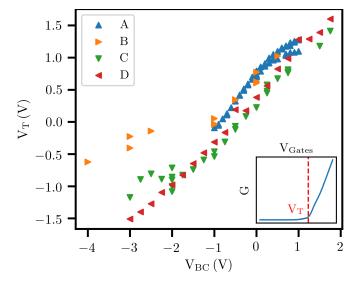

We monitor the turn-on voltage  $V_T$  after reaching base temperature. To do this, we accumulate the electron gas using all gates, effectively forming a conductive sheet underneath the gate structure. This way, we minimize the effect of singular defects on the conducting channel. We measure the conductance G in between the ohmic contacts of the left SET. Once it reaches one third of the saturation value  $(G_{\text{sat}}/3)$ , which was measured in a separate cooldown, the accumulation voltage is not increased further. The first apparent effect of bias cooling is that the accumulation voltage of the device shifts nearly lin-

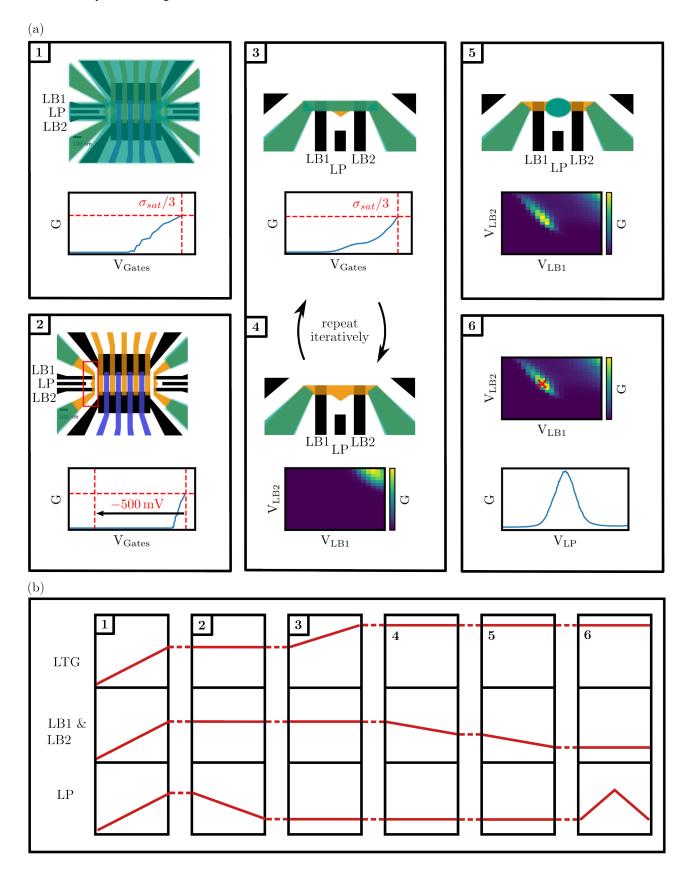

early with the applied bias cooling voltage (Fig. 2). Charge carriers are trapped in between the quantum well and the metal gates. We suspect electrons getting caught at the Si-Al<sub>2</sub>O<sub>3</sub> interface <sup>14,15</sup>. This interface is known to form an SiO<sub>x</sub> layer, in which silicon atoms are partially replaced by aluminium atoms<sup>16,17</sup>. These form acceptor states, which trap electrons. By applying the bias cooling voltage V<sub>BC</sub> during cooldown, we change the electrochemical potential of the defects, allowing thermally excited electrons to change the population of the defect states. Applying positive voltages attracts additional electrons into acceptor-states, increasing the turn-on voltage. Negative biases reduce the population of the Al-vacancies below its equilibrium, creating an excess of positively charged defects, decreasing the accumulation voltage. Next, we characterize the noise power for each bias voltage. To investigate the charge noise we form a single electron transistor in between barrier gates (e.g. LB1 and LB2). The gate layout of the used device is shown in Fig. 1 (b). The challenge hereby is tuning the SETs to comparable working points, although the sample provides a different electrostatic environment in each cooldown. Noise seen by SET devices depends on their working point<sup>18</sup>. Therefore it is essential to repeat a fixed measurement protocol. Our protocol consists of six steps summarized in Fig. 3 (a) and (b). After accumulating the sample to the reference conductance of  $G_{sat}/3$  (step 1), we define the accumulation voltage  $V_{\text{ref}}$  which is used as a starting point for the device tuning. With all gates at V<sub>ref</sub> the device is in a state where a 2DEG is accumulated in the silicon quantum well below every metal gate. In step 2, we lower the voltages of all gates except the topgates and barriers of the SETs by 500 mV to deplete the sample and confine the 2DEG only below the top gates. In the first iteration of step 3, the top gate and barrier voltages are increased until a third of the saturation conductance is reached (not shown in Fig 3(b)). For every subsequent iteration of step 3, only the top gate is raised until accumulation (Fig 3 (b)). In step 3, the topgate voltage (and in the first iteration also the barrier voltages, not shown in the voltage chronogram in Fig. 3 (b)) are increased until a third of the saturation conductance is reached in the measured channel. In step 4 the 'cutoff' voltage of the barrier gates is determined by lowering the voltages of the barrier gates to the point where the conducting channels are fully confined and the measured current is cut off. Slightly above this cutoff voltage, we perform a  $100 \times 100 \text{ mV}^2$  sweep downwards with both barrier gates. We record the current through the channel to see whether Coulomb oscillations are present. If not we now lower the barrier gates by another 100 mV and re-accumulate the conducting channel with the top gate again up to a conductance of  $G_{\text{sat}}/3$ . By repeating steps 3 and 4 iteratively we find the lowest (granulated by the resolution of our voltage steps) topgate voltage that allows formation of quantum dots, which are identified by a 2D barrier sweep exhibiting the Coulomb oscillations (step 5). The barrier gates are tuned to the first Coulomb peak (step 6) and a plunger trace is recorded. If the recorded trace shows a secant-like Coulomb peak, the SET has been formed and the tuning routine came to a successful conclusion.

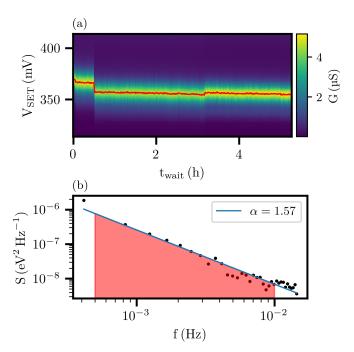

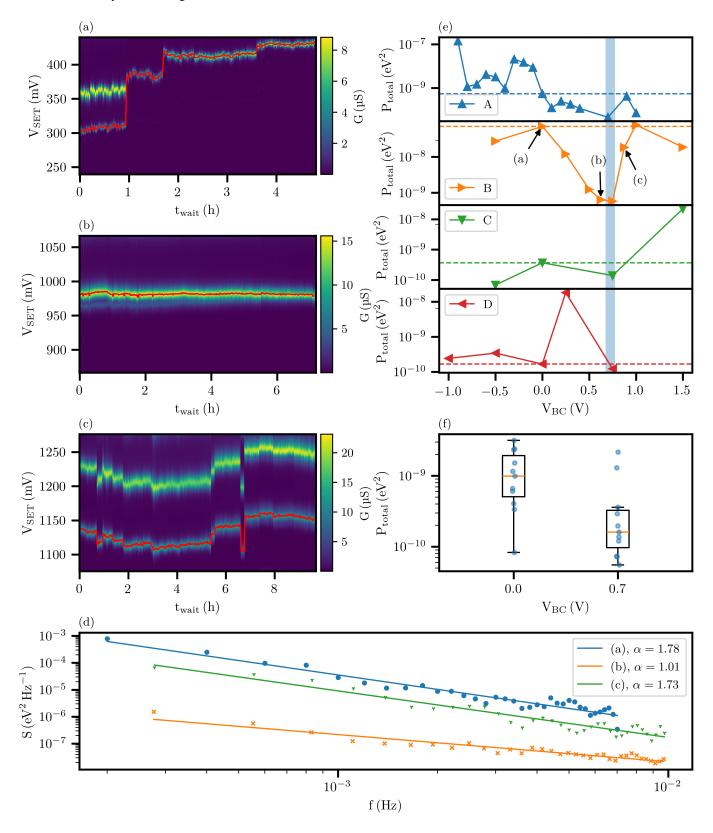

With the quantum dot formed, we characterize its noise in

the band of 200 µHz to 10 mHz using peaktracking<sup>8</sup>. The lower bound on the measured frequencies is set by the total length of our peaktracking measurements (5 h) and the upper bound is set by the rate at which the plunger gate can be swept to record the position of the peak in gatespace. The number of points recorded per plunger sweep varies depending on the expected drift of the sample. Therefore, a trace can contain 150 to 250 individual data points and be measured in 30 s to 70 s depending on the number and sampling rate of the points. We continuously sweep the plunger and record the conductivity of the SET device (Fig. 4 (a)). The shown result was recorded on sample A after being cooled down with 0 V. We extract the exact peak position by fitting each individual trace with a secant function and define the position of its maximum as the peak position. The conversion of V<sub>SET</sub> to eV is done by a static lever arm of 0.039 eV/V. This value is the average of multiple extracted lever arms measured (using Coulomb diamond measurements<sup>19</sup>) for different samples and bias cooling voltages spanning a range from 0.035 to 0.040 eV/V.

Next, we perform a Welch-estimation of the powerspectral-density using the standard signal.welch method from the scipy python package. To exclude artificial frequencies arising from drift in between the start and the end point of a trace, we additionally employ a Hann-type windowing function. The estimation is always performed on the first measured peak. The result can be found in Fig. 4 (b). The resulting spectrum follows a  $1/f^{\alpha}$ -noise distribution with  $\alpha = 1.57$ . This lies in between  $\alpha \approx 1$ , suggesting the presence of many two level fluctuators with a broad distribution of time scales<sup>20</sup>, and  $\alpha \approx 2$ , indicating the presence of random walk noise<sup>21</sup>. Following, we integrate the fitted spectra in the band of 200 µHz to 10 mHz, highlighted in purple in Fig. 4 (b). Quoting the total noise power instead of the e.g. 1 mHznoise has the advantage that all frequencies in the measured band contribute to the noise value. This metric is chosen because we want to weigh both, the rarely occurring large jumps as well as the small displacments in peak position that happen in between every single datapoint.

The procedure is applied to all measured peaktracks. A selection measured on sample B is found in Fig. 5 (a) to (c). Peaktracks dominated by large jumps tend towards  $\alpha \approx 2$ , while peaktracks which are dominated by fluctuations around the original working point tend towards  $\alpha \approx 1$ . Resulting noise spectra are shown in Fig. 5 (d). The noise power versus bias cooling voltage can be seen in Fig. 5 (e). Four samples show a significant noise reduction at 0.7 V. Sample B shows an improvement in the integrated noise power by two orders of magnitude. Towards more positive voltages, samples B and C show an increase in noise.

We identify two types of noise on the SET peak position. A high frequency, low amplitude fluctuation and rarely occurring jumps with a large amplitude. These jumps occur on the timescale of hours and drastically affect the noise performance (Fig. 5). Since the individual peak-tracking measurements have a length of five hours, they may not lead to statistically significant data. To gain insight into the significance of our observations, we performed a measurement campaign consisting of 22 cooldowns of sample A. We measured eleven

times the zerobias followed by the  $0.7\,V$  bias. The results of the noise power integrated from  $200\,\mu\text{Hz}$  to  $10\,\text{mHz}$  are shown in the Fig. 5 (f). The orange line shows the median. The median value of the  $0.7\,V$  measurements is reduced by a factor of 6 in comparison to the median of the  $0\,V$  measurements. To determine the statistical significance of the measured results, we performed an unpaired t-test comparing the measured data sets for  $0\,V$  and  $0.7\,V$ , which results in a probability of  $0.143\,\%$  that the two measured sample means arise from the same normal distribution.

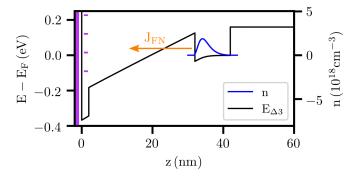

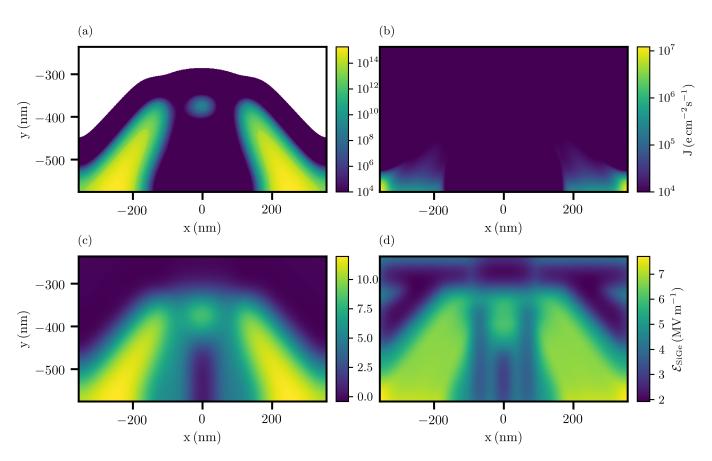

Three-dimensional Poisson-Schrödinger-simulations have been performed on the SET-area of the investigated devices. SiGe-heterostacks are known to induce tunneling currents from the Si-channel<sup>22</sup> into the cap. Charge redistributions, as seen in Fig. 5 (a), could be caused by local metal-to-insulatortransitions, triggered by tunneling into the cap<sup>22,23</sup>. This interpretation is plausible, since the cap-oxide interface itself is MOSFET-like. In MOSFET devices the lengthscales of localization length versus potential variation<sup>24</sup> are known to create a percolation induced metal-to-insulator-transition<sup>25</sup>. In that case the 2DEG in the cap breaks down into charge-carrierpuddles containing mobile carriers. With the simulations we wish to verify that tunneling currents into the cap exist and can therefore source electrons which cause the charge redistributions. Bias cooling was included in simulation by placing interface-charges in the interstitial silicon-oxide layer under the metal gates. The interface-charge density under each gatelayer was calculated based on the turn-on voltage shift. We simulated the density needed to shift the turn-on voltage of gate layer n (with  $n \in \{1,2,3\}$ ) individually. The same charge density is assumed under each gate of a specific gate layer. To reflect the device's real working point, the gate-voltage configurations from individual measurements have been reproduced in simulation. The spatially large regions are treated (substrate, buffer, spacer) in Thomas-Fermi<sup>26–28</sup> approximation. The regions where quantum confinement plays a major role (channel and cap), on the other hand, are treated with a self-consistent Schrödinger-Poisson approach in effective mass approximation<sup>29,30</sup>. In Fig. 6, the simulated band diagram in growth direction for a sample cooled down with  $V_{BC} = 0.7 \, V$  is shown. The barrier in between the silicon channel and the silicon cap-layer is of triangular shape, meaning that the tunneling currents can be calculated using the Fowler-Nordheim<sup>31</sup> model. With the resulting electric field and electrochemical potential, we calculate the tunneling rates from the SiGe-channel into the silicon cap. The spacially varying tunneling currents are shown in Fig. 7 (a) for the 0 V and (b) for the 0.7 V bias cooling case. First, it is important to note that the maximum tunneling rate for the 0.7 V case is reduced by seven orders of magnitude in comparison to the 0 V case. Furthermore, the dot-region itself does not act as a source of electrons in the 0.7 V case, meaning the number of tunneling electrons is not only reduced, but the tunneling events are mainly taking place further away from the region of interest. Generally, the bias cooled samples are operated at lower internal electric fields, as seen in Fig. 7 (c) and (d). In the bias-cooled-case the electric field difference in between the dot region and the barriers is larger. This means that a dot can be accumulated at lower accumulation gate fields, since the electric field of the barriers is more sharply defined due to the frozen-in charges, which are located at the Si-cap-Al $_2$ O $_3$  interface.

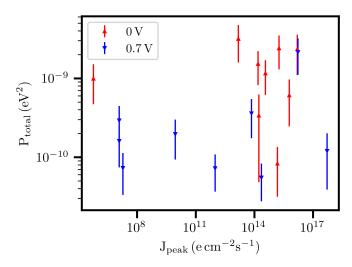

We repeated the simulation for each working point in Fig. 5 (f), to verify an interrelation in between tunneling events and noise. In Fig. 8 the measured noise power is plotted versus the calculated maximum tunneling current. The 0 V cases show a bunching towards high tunneling rates and high noise, whereas the 0.7 V cases show bunching towards low tunneling and low noise. One possible explanation for the correlation of high noise and high tunneling rates is that the electrons flowing from the channel into the cap cause local metal-insulator transitions in the disordered silicon cap<sup>22</sup>. The avalanche-like charge redistributions seen in the peaktracking measurements might be caused by a few excess electrons, locally exceeding the percolation density, triggering a large charge transfer, which is supported by the fact that the number of large charge redistributions is reduced in the 0.7 V dataset. At high bias cooling voltage, a high number of the acceptor defects located at the Si-cap Al<sub>2</sub>O<sub>3</sub> interface are charged. We propose two main mechanisms to explain the increase in noise for voltages above 0.7 V. First, the high density of negatively charged defects leads to working points with high electric fields. Additional tunneling could be a result. Furthermore, the increase in charged defects at the interface could lead to the individual defects exchanging charges, therefore effectively raising the noise again. For bias cooling voltages exceeding 2 V the 2DEG is accumulated without the application of an accumulation voltage. Here, the trapped charges mimic the role of a dopant. For more negative voltages the noise is increasing in the case of sample A and D, not showing a global trend.

In conclusion, we found that bias cooling of undoped Si/Si<sub>x</sub>Ge<sub>1-x</sub> heterostacks causes charges to be trapped in between the silicon channel and the metal gates. This shifts the turn-on voltages linearly with the applied cooldown bias in the range of -1 V to 1 V. We investigated the low frequency charge noise of bias cooled devices. For this we used peaktracking measurements. To quantify the noise for each bias cooling voltage we computed the total noise power for every peak track, which has a minimum around 0.7 V bias cooling voltage. In samples A and B, a global minimum is visible in the total noise power. Samples C and D show a local minimum around 0.7 V. In case of Sample B we could reduce the total noise power by a factor of 120 during the 0.75 V cooldown in comparison to the 0 V cooldown, and during a 22-cooldown campaign the measured median of the total noise power was reduced by a factor of 6 for the 0.7 V cooldown in comparison to the 0 V value. Our measurements show that a significant variation of the noise level can occur as a function of cooldown-bias and that this variation is not a random fluctuation from cooldown to cooldown. While a cooldown bias of 0.7 V leads to good results on all four devices considered, more statistics would be needed to tell if this value reflects a device-independent optimum, and how the optimal cooldown strategy depends on the device design. Another important implication of the significant variation between cooldowns and bias voltages is that a lot of statistics is needed to draw

reliable conclusions from noise measurements. In addition, we present the results of a three-dimensional Schrödinger-Poisson simulation, based on measured working points. Here, we find that samples cooled down with a 0.7 V bias show a by seven orders of magnitude reduced tunneling current from the channel into the cap. While the direct proof remains elusive, we correlate the simulation to our noise measurement results, and find a bunching of datapoints in the high noise, high tunneling as well as in the low noise, low tunneling quadrants. As a next step, bias cooling could be extended to qubit samples, investigating the effect on coherence. Furthermore, tunneling in the cap has been proposed as one of the root causes of the quantum dot instabilities.

This work has been funded by the German Research Foundation (DFG) under Germany's Excellence Strategy - Cluster of Excellence Matter and Light for Quantum Computing" (ML4Q) EXC 2004/1 – 390534769 and the Gottfried Wilhelm Leibniz-Award, ZVN-2020\_WE 4458-5. Project Si-QuBus received funding from the QuantERA ERA-NET Cofund in Quantum Technologies implemented within the European Union's Horizon 2020 Programme. The device fabrication has been done at HNF - Helmholtz Nano Facility, Research Center Juelich GmbH<sup>32</sup>. Furthermore the authors wish to thank Malte Neul for the organization of our meetings and for helpful discussions.

- <sup>1</sup>J. Yoneda, K. Takeda, T. Otsuka, T. Nakajima, M. R. Delbecq, G. Allison, T. Honda, T. Kodera, S. Oda, Y. Hoshi, N. Usami, K. M. Itoh, and S. Tarucha, "A quantum-dot spin qubit with coherence limited by charge noise and fidelity higher than 99.9%," Nature Nanotechnology 13, 102–106 (2018).

- <sup>2</sup>A. Noiri, K. Takeda, T. Nakajima, T. Kobayashi, A. Sammak, G. Scappucci, and S. Tarucha, "Fast universal quantum gate above the fault-tolerance threshold in silicon," Nature 601, 338–342 (2022).

- <sup>3</sup>R. Xue, M. Beer, I. Seidler, S. Humpohl, J.-S. Tu, S. Trellenkamp, T. Struck, H. Bluhm, and L. R. Schreiber, "Si/sige qubus for single electron information-processing devices with memory and micron-scale connectivity function," Nature Communications **15**, 2296 (2024).

- <sup>4</sup>K. Takeda, A. Noiri, T. Nakajima, T. Kobayashi, and S. Tarucha, "Quantum error correction with silicon spin qubits," Nature 608, 682–686 (2022).

- <sup>5</sup>I. Seidler, T. Struck, R. Xue, N. Focke, S. Trellenkamp, H. Bluhm, and L. R. Schreiber, "Conveyor-mode single-electron shuttling in si/sige for a scalable quantum computing architecture," npj Quantum Information **8**, 100 (2022).

- <sup>6</sup>V. Langrock, J. A. Krzywda, N. Focke, I. Seidler, L. R. Schreiber, and L. Cywiński, "Blueprint of a scalable spin qubit shuttle device for coherent mid-range qubit transfer in disordered si/sige/sio<sub>2</sub>," PRX Quantum 4, 020305 (2023).

- <sup>7</sup>M. Künne, A. Willmes, M. Oberländer, C. Gorjaew, J. D. Teske, H. Bhardwaj, M. Beer, E. Kammerloher, R. Otten, I. Seidler, R. Xue, L. R. Schreiber, and H. Bluhm, "The spinbus architecture: Scaling spin qubits with electron shuttling," (2023), arXiv:2306.16348 [quant-ph].

- <sup>8</sup>L. Kranz, S. K. Gorman, B. Thorgrimsson, Y. He, D. Keith, J. G. Keizer, and M. Y. Simmons, "Exploiting a single-crystal environment to minimize the charge noise on qubits in silicon," Adv. Mater. 32, 2003361 (2020).

- <sup>9</sup>T. Struck, A. Hollmann, F. Schauer, O. Fedorets, A. Schmidbauer, K. Sawano, H. Riemann, N. V. Abrosimov, L. Cywiński, D. Bougeard, and L. R. Schreiber, "Low-frequency spin qubit energy splitting noise in highly purified 28si/sige," npj Quantum Information **6**, 40 (2020).

- <sup>10</sup>E. J. Connors, J. Nelson, L. F. Edge, and J. M. Nichol, "Charge-noise spectroscopy of si/sige quantum dots via dynamically-decoupled exchange oscillations," Nature Communications 13, 940 (2022).

- <sup>11</sup>K. Takeda, T. Obata, Y. Fukuoka, W. M. Akhtar, J. Kamioka, T. Kodera, S. Oda, and S. Tarucha, "Characterization and suppression of low-frequency noise in Si/SiGe quan-

- tum point contacts and quantum dots," Applied Physics Letters **102**, 123113 (2013), https://pubs.aip.org/aip/apl/article-pdf/doi/10.1063/1.4799287/13222126/123113\_1\_online.pdf.

- <sup>12</sup>M. Pioro-Ladrière, J. H. Davies, A. R. Long, A. S. Sachrajda, L. Gaudreau, P. Zawadzki, J. Lapointe, J. Gupta, Z. Wasilewski, and S. Studenikin, "Origin of switching noise in GaAs/Al<sub>1-x</sub>Ga<sub>x</sub>As lateral gated devices," PRB 72, 115331 (2005).

- <sup>13</sup>T. Struck, A. Hollmann, F. Schauer, O. Fedorets, A. Schmidbauer, K. Sawano, H. Riemann, N. V. Abrosimov, L. Cywiński, D. Bougeard, and L. R. Schreiber, "Spin-epr-pair separation by conveyor-mode single electron shuttling in si/sige," Nature Communications 15, 1325 (2024).

- <sup>14</sup>B. Hoex, J. J. H. Gielis, M. C. M. van de Sanden, and W. M. M. Kessels, "On the c-si surface passivation mechanism by the negative-charge-dielectric al2o3," Journal of Applied Physics 104, 113703 (2008).

- <sup>15</sup>J. J. H. Gielis, B. Hoex, M. C. M. van de Sanden, and W. M. M. Kessels, "Negative charge and charging dynamics in al2o3 films on si characterized by second-harmonic generation," Journal of Applied Physics **104**, 073701 (2008).

- <sup>16</sup>D. Hiller, P. M. Jordan, K. Ding, M. Pomaska, T. Mikolajick, and D. König, "Deactivation of silicon surface states by al-induced acceptor states from al-o monolayers in sio2," Journal of Applied Physics 125, 015301 (2019).

- <sup>17</sup>D. Hiller, D. Tröger, M. Grube, D. König, and T. Mikolajick, "The negative fixed charge of atomic layer deposited aluminium oxide—a two-dimensional sio2/alox interface effect," Journal of Physics D: Applied Physics 54, 275304 (2021).

- <sup>18</sup>A. Elsayed, M. Shehata, C. Godfrin, S. Kubicek, S. Massar, Y. Canvel, J. Jussot, G. Simion, M. Mongillo, D. Wan, B. Govoreanu, I. P. Radu, R. Li, P. V. Dorpe, and K. D. Greve, "Low charge noise quantum dots with industrial cmos manufacturing," (2022), arXiv:2212.06464 [cond-mat.mes-hall].

- <sup>19</sup>R. Hanson, L. P. Kouwenhoven, J. R. Petta, S. Tarucha, and L. M. K. Vandersypen, "Spins in few-electron quantum dots," RMP 79, 1217–1265 (2007).

- $^{20}$ E. Paladino, Y. M. Galperin, G. Falci, and B. L. Altshuler, "1/f noise: Implications for solid-state quantum information," RMP **86**, 361–418 (2014).

- <sup>21</sup>J. A. Barnes and D. W. Allan, "A statistical model of flicker noise," Proceedings of the IEEE **54**, 176–178 (1966).

- <sup>22</sup>C.-T. Huang, J.-Y. Li, K. S. Chou, and J. C. Sturm, "Screening of remote charge scattering sites from the oxide/silicon interface of strained si two-dimensional electron gases by an intermediate tunable shielding electron layer," Appl. Phys. Lett. **104**, 243510 (2014).

- <sup>23</sup>C.-T. Huang, Electrical and Material Properties of Strained Silicon/Relaxed Silicon Germanium Heterostructures for Single-Electron Quantum Dot Applications, Ph.D. thesis, Princeton University (2015).

- <sup>24</sup>Z. Wilamowski, N. Sandersfeld, W. Jantsch, D. Többen, and F. Schäffler, "Screening breakdown on the route toward the metal-insulator transition in modulation doped si /sige quantum wells," PRL 87, 026401 (2001).

- <sup>25</sup>L. A. Tracy, E. H. Hwang, K. Eng, G. A. Ten Eyck, E. P. Nordberg, K. Childs, M. S. Carroll, M. P. Lilly, and S. Das Sarma, "Observation of percolation-induced two-dimensional metal-insulator transition in a si mosfet," PRB 79, 235307 (2009).

- <sup>26</sup>L. H. Thomas, "The calculation of atomic fields," Mathematical Proceedings of the Cambridge Philosophical Society 23, 542–548 (1927).

- <sup>27</sup>E. Fermi, "Eine statistische methode zur bestimmung einiger eigenschaften des atoms und ihre anwendung auf die theorie des periodischen systems der elemente," Zeitschrift für Physik 48, 73–79 (1928).

- <sup>28</sup>T.-W. Tang, T. O'Regan, and B. Wu, "Thomas-fermi approximation for a two-dimensional electron gas at low temperatures," J. Appl. Phys. 95, 7990–7997 (2004).

- <sup>29</sup>E. O. Kane, "The semi-empirical approach to band structure," Journal of Physics and Chemistry of Solids 8, 38–44 (1959).

- <sup>30</sup>A. Trellakis, T. Andlauer, and P. Vogl, "Efficient solution of the schrödinger-poisson equations in semiconductor device simulations," in *Large-Scale Scientific Computing*, edited by I. Lirkov, S. Margenov, and J. Waśniewski (Springer Berlin Heidelberg, Berlin, Heidelberg, 2006) pp. 602–609.

- <sup>31</sup>R. H. Fowler and L. Nordheim, "Electron emission in intense electric fields," Proceedings of the Royal Society of London. Series A, Containing Papers of a Mathematical and Physical Character 119, 173–181 (1928), https://royalsocietypublishing.org/doi/pdf/10.1098/rspa.1928.0091.

- <sup>32</sup>W. Albrecht, J. Moers, and B. Hermanns, "HNF Helmholtz Nano Facil-

ity," Journal of large-scale research facilities JLSRF  ${f 3}$ , A112 (2017).

FIG. 1. (a) False colored scanning electron micrograph. Bottommost gate layer in blue, topmost layer in green. The path of the current  $I_{meas}$  used in the measurements is denoted in red. (b) Schematic cross-section with layer thicknesses to scale. The 2DEG is defined in the 10 nm strained Si layer. The SiGe spacer layer is protected from oxidation by a 2 nm silicon cap layer. The dashed line in (a) represents the corresponding position of the schematic cross-section in (b).

FIG. 2. Turn-on voltage of the device over applied bias voltage during cooldown for four nominally equal devices. In between  $-1 \, V$  and  $1 \, V$  all samples behave linearly showing similar slopes. Below  $-1 \, V$  the behavior differs. This might be due to different defect densities in the heterostructure. The inset shows an exemplary accumulation curve. The red-dashed line indicates the turn-on voltage, which is defined by the channel conductivity G crossing a value of  $0.4 \, \mu S$ .

FIG. 3. (a) Tuning workflow which was performed after each cooldown. The red square in step 2 denotes where the cutout shown in steps 3 to 5 lies within sample. The sample is accumulated to the reference conductance of  $G_{sat}/3$  (step 1). The voltages applied to all but the SET-gates are reduced by 500 mV to confine the 2DEG (step 2). Using the SET gates a closed conducting channel is formed (step 3). A  $100x100 \, \text{mV}^2$  sweep is performed with both barrier gates (step 4). Step 3 and 4 are repeated iteratively until a Coulomb oscillation is observed (step 5). The barrier gates are tuned to the first Coulomb peak (step 6) and a plunger trace is recorded. (b) Simplified chronogram of the voltages applied to the SET-gates. Numbers 1-6 correspond to the tuning steps in panel (a).

FIG. 4. (a) Peaktracking measurement, performed on sample A with a  $V_{BC}$  of 0 V. The colorplot consists of Coulomb peak traces recorded back to back. The red line indicates the position of the peak maxima. b) Noise power spectral density, fitted with a  $\beta/f^{\alpha}$  power spectrum. To calculate the total noise power, the spectrum is integrated over the highlighted frequency range. The conversion of  $V_{SET}$  to the chemical potential of the SET is done by a static leverarm of 0.039 eV/V.

FIG. 5. (a) - (c) Peaktracking measurements performed on Sample B for 0 V, 0.625 V and 0.825 V. (b) Shows a vanishing side peak, which might indicate the presence of a parasitic dot. (d) Noise power spectral densities fitted with a  $\beta/f^{\alpha}$  power spectrum. e) Integrated noise power versus bias cooling voltage. While the noise increases towards negative biases for most samples, a local minimum at 0.7 V is found in each trace. The dashed line denotes the 0 V noise level. (f) Boxplot of the integrated noise power of 22 peaktrackings performed in alternating 0 V/0.7 V cooldowns. The box includes the interquartile (IQR) range and the whiskers extend up to 1.5 times the IQR. The orange solid line displays the median value. The median value of 0.7 V is almost an order of magnitude lower than for 0 V.

FIG. 6. Simulated band structure alignment at the working point of a sample cooled down with  $V_{BC}=0.7\,V.~E_{\Delta3}$  is the energy of the lowest conduction band. The violet region indicates the assumed position of the interface charges. They were distributed in a 1 nm thick sheet located 1.2 nm above the Si-cap-oxide interface. The orange arrow indicates the direction of the Fowler-Nordheim tunneling current density  $J_{FN}$ . The electron density n is plotted in blue.

FIG. 7. a) Simulated tunneling current from silicon channel into the silicon cap for a sample cooled with a 0 V bias (a) and 0.7 V bias (b). Simulated electric field distribution at the channel-spacer interface of a sample cooled with a 0 V bias (c) and 0.7 V bias (d).

FIG. 8. Measured integrated noise density versus simulated peak tunneling current. The datapoint belonging to the  $0.7\,\mathrm{V}$  dataset in the high-tunneling, high-noise quadrant shows an excess of telegraph noise which was only recorded once.