# Basilisk: Achieving Competitive Performance with Open EDA Tools on an Open-Source Linux-Capable RISC-V SoC

Phillippe Sauter<sup>1</sup>\*, Thomas Benz<sup>1</sup>, Paul Scheffler<sup>1</sup>, Zerun Jiang<sup>1</sup>, Beat Muheim<sup>1</sup>, Frank K. Gürkaynak<sup>1</sup>, Luca Benini<sup>1,2</sup>

<sup>1</sup>Integrated Systems Laboratory, ETH Zurich

<sup>2</sup>Department of Electrical, Electronic, and Information Engineering, University of Bologna

#### Abstract

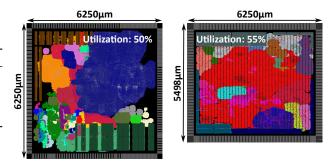

We introduce Basilisk, an optimized application-specific integrated circuit (ASIC) implementation and design flow building on the end-to-end open-source Iguana system-on-chip (SoC). We present enhancements to synthesis tools and logic optimization scripts improving quality of results (QoR), as well as an optimized physical design with an improved power grid and cell placement integration enabling a higher core utilization. The tapeout-ready version of Basilisk implemented in IHP's open 130 nm technology achieves an operation frequency of 77 MHz (51 logic levels) under typical conditions, a  $2.3\times$  improvement compared to the baseline open-source EDA design flow presented in Iguana, and a higher 55% core utilization compared to 50% in the baseline design. Through collaboration with EDA tool developers and domain experts, Basilisk exemplifies a synergistic effort towards competitive open-source electronic design automation (EDA) tools for research and industry applications.

### Introduction

Recently, Benz et al. [1] presented and released Iguana, an end-to-end open-source Linux-capable SoC created with open tools and implemented in IHP's open 130 nm technology. Iguana is based on the Cheshire platform [2] and combines an RV64GC core with a HyperRAM DRAM controller and a rich set of peripherals, completing a Linux-capable system. The authors released all source files and scripts necessary to run the RTL-to-GDS flow using only freely available open-source tools, enabling others to reproduce and build on their work.

Iguana proved that a completely open-source design flow can be used to implement a Linux-capable SoC, but the authors did not optimize their design for performance or reduce design rule check (DRC) violations to a minimal level desirable for tapeout.

In this work, we extend the previous work on Iguana by optimizing the synthesis and the physical implementation of the Cheshire SoC with open-source EDA tools; we call the resulting ASIC Basilisk.

As was done for Iguana, we avoid simplifications to the original RTL description utilizing complex SystemVerilog and instead focus on improving the EDA tools, their flow scripts, and the overall physical implementation and constraints. In the spirit of open-source, we actively foster international and cross-institutional exchange, collecting knowledge and building on existing efforts on cutting-edge algorithms and open EDA tools. We update the SoC to the newest version of Cheshire, adding new features such

as a USB OHCI controller to increase the capabilities of the resulting ASIC. Finally, we focus our efforts toward a single, integrated tool flow, using critical parts of Basilisk, such as the FPU or scoreboard, as realistic benchmarks for all steps in synthesis and place and route (P&R).

In particular, we present the following contributions:

- An extensive study on the state-of-the-art opensource EDA flow using Yosys for logic synthesis and OpenROAD for P&R, with a focus on identifying suboptimal QoR in individual flow steps.

- Improving existing EDA tools by communicating the identified tool and flow issues with the maintainers and collaborating on developing solutions.

- Providing an optimized open silicon implementation flow, including feedback from various tool authors and domain experts.

- Improving upon Iguana's physical design by optimizing the power grid and adding a manual RTL change to facilitate automatic inference of multiply—accumulate (MAC) operations.

- Routability improvements to the standard cells in the IHP 130 nm open PDK.

We will further improve Basilisk until the second week of May when we plan to tape the resulting ASIC in IHP's 130 nm node.

## Synthesis

Yosys [3] is a leading open-source synthesis engine used in open-source EDA flows. At the time of writing, it offers only limited support for SystemVerilog language

$<sup>{}^*\</sup>mathrm{Corresponding}$  author:  $\mathtt{phsauter@iis.ee.ethz.ch}$

**Table 1:** Cumulative synthesis improvements from left to right; large impacts of each step are highlighted.

|                           | Iguana [1] | MUX     | ABC     | MAC           |

|---------------------------|------------|---------|---------|---------------|

| Logic area                | 1.8 MGE    | 1.4 MGE | 1.1 MGE | 1.1 MGE       |

| Timing                    | 33 MHz     | 37 MHz  | 71 MHz  | <b>77 MHz</b> |

| Logic levels <sup>a</sup> | 182 LL     | 149 LL  | 54 LL   | <b>51 LL</b>  |

| Runtime <sup>b</sup>      | 5.4 h      | 2.8 h   | 2.2 h   | 2.2 h         |

| Peak RAM <sup>c</sup>     | 217 GB     | 105 GB  | 76 GB   | 75 GB         |

<sup>&</sup>lt;sup>a</sup> Number of logic gates in longest path b 2.5 GHz Xeon E5-2670

constructs; as a result, additional work is needed to convert SystemVerilog, constituting the majority of Cheshire's openly available RTL, to simpler Verilog that Yosys can parse. We use a chain of tools [1] to achieve this: Morty merges all dependencies into a single compile context, SVase propagates parameters and simplifies some constructs, and SV2V converts the remaining SystemVerilog constructs to pure Verilog. After elaboration, Yosys first represents the design's structure using high-level constructs and then progressively transforms it to generic standard cells. Finally, Yosys calls ABC, a logic optimization and mapping tool. To improve QoR, we improved three distinct aspects of this synthesis chain; their cumulative effects are summarized in Table 1.

Part-select operations (MUX) Yosys versions prior to our improvements ( $\theta$ .34 and older) use shift operations to represent indexed part-select operations instead of more efficient block-multiplexer trees. Thus, for any part select, a barrel shifter is inferred at elaboration. This unnecessary generalization of part selects significantly inflates area and logic levels and increases runtime and peak memory usage. Logic optimizations in later stages are unable to simplify these shifters to the desired multiplexer trees, impacting QoR.

Overhaul of the ABC scripts (ABC) In cooperation with logic synthesis researchers and ABC developers, we overhaul the ABC script, leveraging Yang et al.'s work [4] to improve the QoR at the cost of minimal additional runtime.

Multiply-accumulate operations (MAC) Yosys automatically instantiates optimized implementations of arithmetic operations. This also works for MAC operations, which are implemented as a Booth multiplier followed by an adder. A more efficient solution is to integrate adders into the CSA tree of preceding multipliers, creating fused multiply-add (FMA) units; a hand-written FMA unit reduces our critical path by 9%. An update to the existing Booth multiplier transformation automatically inferring FMA instances is currently in the works.

### Place & Route

We use OpenRoad [5] to implement Basilisk's synthesized netlist. Analyzing Iguana's P&R, we identify improvement steps mainly in the EDA tool flow (how

Figure 1: Amoeba view; Iguana (left) and Basilisk(right).

the individual components of OpenRoad are invoked) and the physical constraints of the ASIC. We improve the routability of the design by redesigning the power grid; we reduce the width and increase the count of the power stripes on the top metal layer to ease routing congestion underneath the stripes. Very dense modules with random routing patterns, such as the boot ROM, were a particular source of issues. As OpenRoad currently only accepts global (as opposed to region- or instance-based) settings, we tune several hyper-parameters of the routability-driven global placement engine to improve the placement of dense blocks and get a routable design without DRC violations.

### Conclusion and Outlook

Synthesizing and implementing Basilisk, we optimize the design's clock frequency by  $2.3 \times$  from 33 MHz to 77 MHz compared to Iguana, reducing the logic area from 1.8 MGE to 1.1 MGE. The physical implementation increases the core utilization from 50 % to 55 % while reducing the number of post-routing DRC violations. We contribute to improving open-source EDA tools by reporting and fixing tool issues and by releasing our optimized flow scripts and implementation of Basilisk [6]. Basilisk is not only a theoretical exercise; we will submit our optimized design for fabrication with IHP in their 130nm shuttle run in mid-May.

### References

- T. Benz et al. Iguana: An End-to-End Open-Source Linuxcapable RISC-V SoC in 130nm CMOS. 2023.

- [2] A. Ottaviano et al. "Cheshire: A Lightweight, Linux-Capable RISC-V Host Platform for Domain-Specific Accelerator Plug-In". In: IEEE TCAS II (2023).

- [3] C. Wolf et al. Yosys A Free Verilog Synthesis Suite. 2013.

- [4] W. Yang et al. "Lazy man's logic synthesis". In: IEEE/ACM ICCAD. 2012.

- [5] T Ajayi et al. "OpenROAD: Toward a Self-Driving, Open-Source Digital Layout Implementation Tool Chain". In: Proc. GOMACTECH (2019), pp. 1105–1110.

- [6] PULP Platform contributors. Iguana. https://github. com/pulp-platform/iguana. 2024.